半导体器件及其制备方法

文献发布时间:2023-06-19 12:05:39

技术领域

本发明涉及半导体技术领域,尤其涉及一种半导体器件及其制备方法。

背景技术

随着技术的发展,半导体工业不断寻求新的方式生产,以使得存储器装置中的每一存储器裸片具有更多数目的存储器单元。为了进一步提高存储器的存储密度,已经开发出三维结构的存储器件,三维存储器包括沿着垂直方向堆叠的多个存储单元,在单位面积的晶片上可以成倍地提高集成度,并且可以降低成本。在非易失性存储器中,已设计出具有32层、64层,甚至更高的层数的3D NAND Flash(三维NAND闪存)存储器。

在现有技术中,通常会使用相变存储器(Phase Change Memory,PCM)作为3D NANDFlash存储器的缓冲器,以提高3D NAND Flash存储器的速度和性能。这种设计下的混合型存储器,具有两个控制器(PCM控制器以及NAND控制器),分别用以控制相变存储器以及3DNAND Flash存储器。一般情况下,混合型存储器的PCM控制器接收到外部主机传输的数据后,会根据该数据使用的场景,选择将数据发送至相变存储器或NAND控制器。当该数据被发送至NAND控制器后,NAND控制器再将该数据发送至3D NAND Flash存储器。

但是,现有设计下,由于相变存储阵列以及NAND存储阵列分别被不同的驱动器所控制,不同的驱动器再被不同的控制器所控制,且数据是透过外部电路被选择送到PCM控制器以及NAND控制器,因而要变更存储器时,要透过外部电路以及不同的控制器来进行转移,这将增加操作步骤与操作时间,且通常将相变存储阵列(及其控制器)与NAND存储阵列(及其控制器)分别制造于一块主板中的两块芯片上,这两块芯片之间通过主板上的走线进行数据通信,从而会导致不同存储阵列之间的数据通信较为缓慢的问题出现,同时,也带来了半导体器件具有较高的制造成本的问题。

发明内容

本发明提供了一种半导体器件及其制备方法,用以解决因半导体器件中不同存储阵列的驱动器由不同的控制器所控制,而导致半导体器件制造成本较高、不同存储阵列之间的数据通信较为缓慢的问题。

为了解决上述问题,本发明提供了一种半导体器件,所述半导体器件包括:

外围电路芯片,所述外围电路芯片包括依次层叠设置的第一衬底、器件层以及第一键合层,所述器件层包括控制器以及多个驱动器;

存储阵列芯片,所述存储阵列芯片包括依次层叠设置的第二键合层、存储阵列层以及第二衬底,所述存储阵列层包括与每个所述驱动器对应的多个存储阵列,所述存储阵列芯片通过所述第二键合层以及所述第一键合层电连接所述外围电路芯片;

其中,所述控制器用以通过控制所述多个驱动器、并经由所述第一键合层以及所述第二键合层,而控制与所述多个驱动器相对应的所述多个存储阵列进行读写操作。

进一步优选的,所述多个驱动器包括第一驱动器以及第二驱动器,所述存储阵列层包括第一存储阵列以及第二存储阵列,所述第一存储阵列以及所述第一驱动器共同构成第一存储器,所述第二存储阵列以及所述第二驱动器共同构成第二存储器,其中,所述第二存储器具有比所述第一存储器更快的读写操作速度,且所述第二存储器用以保存编程程序运行时的数据。

进一步优选的,所述控制器用以将所述第二存储器保存的所述数据写入所述第一存储器。

进一步优选的,所述第一存储阵列为NAND存储阵列,所述第二存储阵列为相变存储阵列,且所述相变存储阵列位于所述NAND存储阵列远离所述第二衬底的一侧上。

进一步优选的,所述NAND存储阵列包括存储区以及阶梯区,所述相变存储阵列位于所述阶梯区的纵向投影下方。

进一步优选的,所述第一存储阵列包括至少一个NAND阵列叠层,每个所述NAND阵列叠层包括堆叠层、垂直贯穿所述堆叠层的多个沟道柱、多条第一字线以及多条第一位线,且每个所述NAND阵列叠层通过所述多条第一字线和所述多条第一位线与所述外围电路芯片中的所述第一驱动器电连接。

进一步优选的,所述第二存储阵列包括至少一个相变存储阵列叠层,每个所述相变存储阵列叠层包括多条第二字线、多条第二位线以及设置于所述多条第二字线和所述多条第二位线的交叉点处的多个第二存储单元,且每个所述相变存储阵列叠层通过所述多条第二字线和所述多条第二位线与所述外围电路芯片中的所述第二驱动器电连接。

进一步优选的,所述外围电路芯片还包括覆盖所述器件层的第一互连层,所述第一互连层用以电连接所述器件层和所述第一键合层。

进一步优选的,所述半导体器件还包括设置于所述第一衬底相反于所述器件层的一侧的第一绝缘层,以及设置于所述第一绝缘层中的第一引出结构,所述第一引出结构包括第一焊盘以及第一垂直引出触点,所述第一焊盘用以电连接外部电路,所述第一互连层包括第一垂直互连触点,所述第一垂直引出触点与所述第一垂直互连触点电连接。

进一步优选的,所述存储阵列芯片还包括覆盖所述存储阵列层的第二互连层,所述第二互连层用以电连接所述存储阵列层中的所述多个存储阵列和所述第二键合层。

进一步优选的,所述半导体器件还包括设置于所述第二衬底相反于所述存储阵列层的一侧的第二绝缘层,以及设置于所述第二绝缘层中的第二引出结构,所述第二引出结构包括第二焊盘以及第二垂直引出触点,所述第二焊盘用以电连接外部电路,所述第二互连层包括第二垂直互连触点,所述第二垂直引出触点与所述第二垂直互连触点电连接。

另一方面,本发明还提供了一种半导体器件的制备方法,所述制备方法包括:

提供第一衬底,并在所述第一衬底上依次形成器件层以及第一键合层而形成外围电路晶圆,其中,所述器件层包括控制器以及多个驱动器;

提供第二衬底,并在所述第二衬底上依次形成存储阵列层以及第二键合层而形成存储阵列晶圆,其中,所述存储阵列层包括与每个所述驱动器对应的多个存储阵列;

将所述存储阵列晶圆翻转,并通过所述第一键合层以及所述第二键合层对所述外围电路晶圆以及所述存储阵列晶圆进行键合;

其中,所述控制器用以通过控制所述多个驱动器、并经由所述第一键合层以及所述第二键合层,而控制与所述多个驱动器相对应的所述多个存储阵列进行读写操作。

进一步优选的,所述制备方法还包括:

在所述第一衬底上形成覆盖所述器件层的第一互连层;

其中,所述第一互连层用以电连接所述器件层和所述第一键合层。

进一步优选的,所述制备方法还包括:

在所述第二衬底上形成覆盖所述存储阵列层的第二互连层;

其中,所述第二互连层用以电连接所述存储阵列层中的所述存储阵列和所述第二键合层。

进一步优选的,所述制备方法还包括:

在所述第二衬底上形成绝缘层;

在所述绝缘层中形成引出结构;

其中,所述引出结构包括焊盘以及垂直引出触点,所述焊盘用以电连接外部电路,所述第二互连层包括垂直互连触点,所述垂直引出触点与所述垂直互连触点电连接。

本发明的有益效果为:本发明提供了一种半导体器件,包括:依次层叠设置第一衬底、器件层以及第一键合层的外围电路芯片,器件层包括控制器以及多个驱动器,依次层叠设置第二键合层、存储阵列层以及第二衬底的存储阵列芯片,存储阵列层包括与每个驱动器对应的多个存储阵列,且存储阵列芯片通过第一键合层以及第二键合层电连接外围电路芯片,其中,控制器用以通过控制多个驱动器、并经由第一键合层以及第二键合层,而控制与多个驱动器相对应的多个存储阵列进行读写操作,且由于控制器与多个驱动器形成于同一芯片上,从而有效地通过提高控制器与多个驱动器之间的通信速度,而提高了多个存储阵列之间的数据通信速度,同时,降低了半导体器件的制造成本。

附图说明

为了更清楚地说明本发明的技术方案,下面将对根据本发明而成的各实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

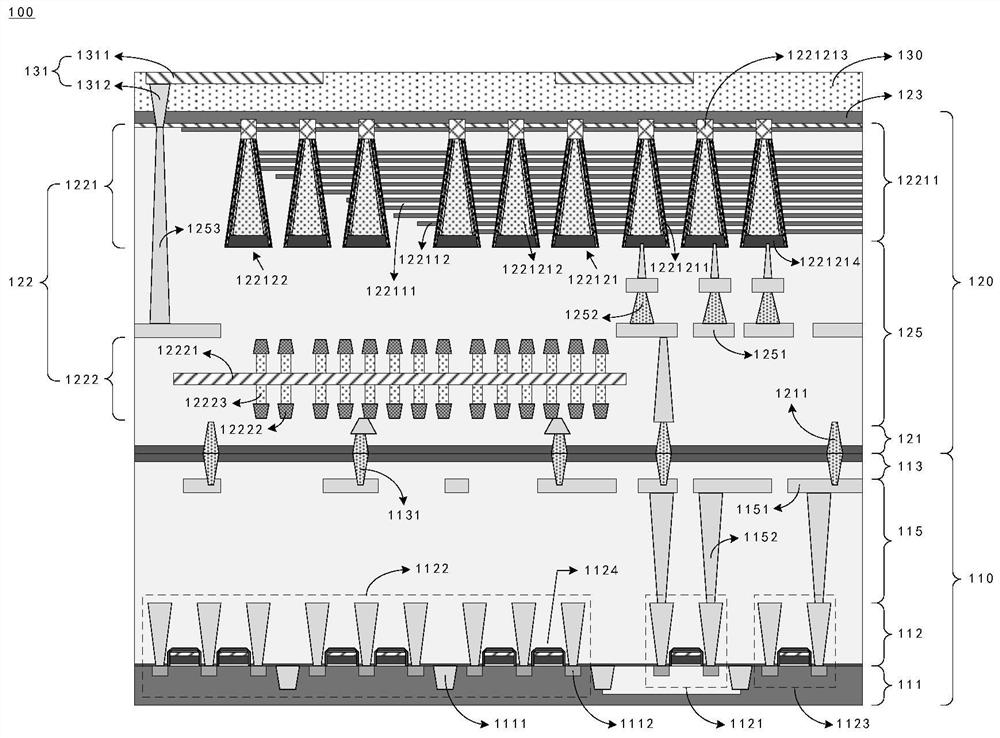

图1是根据本发明而成的实施例所提供的半导体器件的结构示意图。

图2是根据本发明而成的实施例所提供的半导体器件的进一步结构示意图。

图3是根据本发明而成的实施例所提供的半导体器件的制备方法的流程示意图。

图4a-图4j是根据本发明而成的实施例所提供的半导体器件的制备方法的工艺流程示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接或可以相互通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

在本发明中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

下文的公开提供了许多不同的实施方式或例子用来实现本发明的不同结构。为了简化本发明的公开,下文中对特定例子的部件和设置进行描述。当然,它们仅仅为示例,并且目的不在于限制本发明。此外,本发明可以在不同例子中重复参考数字和/或参考字母,这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施方式和/或设置之间的关系。此外,本发明提供了的各种特定的工艺和材料的例子,但是本领域普通技术人员可以意识到其他工艺的应用和/或其他材料的使用。

本发明针对现有的半导体器件,因半导体器件中不同存储阵列的驱动器由不同的控制器所控制,而导致半导体器件制造成本较高、不同存储阵列之间的数据通信较为缓慢的问题,本发明实施例用以解决该问题。

请参阅图1,图1示出了根据本发明而成的实施例所提供的半导体器件100的结构示意图,从图中可以很直观的看到根据本发明而成的实施例的各组成部分,以及各组成部分的相对位置关系。

如图1所示,该半导体器件100包括外围电路芯片110以及存储阵列芯片120,其中:

外围电路芯片110包括依次层叠设置的第一衬底111、器件层112以及第一键合层113,其中,器件层112包括第一驱动器1121、第二驱动器1122以及控制器1123;

存储阵列芯片120包括依次层叠设置的第二键合层121、存储阵列层122以及第二衬底123,且存储阵列芯片120设置于外围电路芯片110上方,并通过第一键合层113以及第二键合层121电连接外围电路芯片110,且其中,存储阵列层122包括多个存储阵列,亦即第一存储阵列1221以及第二存储阵列1222。

需要说明的是,第一驱动器1121用以驱动第一存储阵列1221进行读写操作,第二驱动器1122用以驱动第二存储阵列1222进行读写操作,控制器1123用以控制第一驱动器1121以及第二驱动器1122。进一步地,因为控制器1123位于外围电路芯片110上,第一存储阵列1221与第二存储阵列1222位于存储阵列芯片120上,所以,控制器1123通过控制第一驱动器1121、并经由第一键合层113以及第二键合层121而控制第一存储阵列1221,控制器1123通过控制第二驱动器1122、并经由第一键合层113以及第二键合层121而控制第二存储阵列1222。

进一步地,第一存储阵列1221以及第一驱动器1121共同构成第一存储器(图中未示出),第二存储阵列1222以及第二驱动器1122共同构成第二存储器(图中未示出),第二存储器具有比第一存储器更快的读写操作速度。具体地,与半导体器件100电连接的外部主机在运行编程程序时,会将产生的数据发送至半导体器件100的控制器1123,控制器1123会先控制第二存储器保存该数据,之后,再根据该数据的使用场景,选择性地将第二存储器保存的数据写入第一存储器。

请参阅图2,图2示出了根据本发明而成的实施例所提供的半导体器件100的进一步结构示意图,从图中可以很直观的看到根据本发明而成的实施例的各组成部分,以及各组成部分的相对位置关系。

如图2所示,在本实施例中,第一存储阵列1221为NAND存储阵列,第二存储阵列1222为相变存储阵列,且第二存储阵列1222以及第一存储阵列1221以完成品观看是依次层叠于第二键合层121的上方(实际上是先层叠于第二衬底123上再进行翻转),也即,第二存储阵列1222位于第一存储阵列1221远离第二衬底123的一侧上,第一驱动器1121为NAND存储阵列驱动器、第二驱动器1122为相变存储阵列驱动器。需要说明的是,在由本发明而成的其它变形例中,可以是第一存储阵列1221(NAND存储阵列)以及第二存储阵列1222(相变存储阵列)依次层叠于第二键合层121的上方;也可以是第一存储阵列1221(NAND存储阵列)以及第二存储阵列1222(相变存储阵列)位于同一水平面所在的层,并层叠于第二键合层121的上方。

进一步地,在本实施例中,第一驱动器1121、第二驱动器1122以及控制器1123位于器件层112,且在水平面方向上,位于相同层。需要说明的是,在由本发明而成的其它变形例中,器件层112可以包括至少一个子器件层,第一驱动器1121、第二驱动器1122以及控制器1123可以分别位于至少一个子器件层其中之一,举例来说,器件层112包括第一子器件层以及第二子器件层,第一驱动器1121位于第一子器件层中,第二驱动器1122以及控制器1123位于第二子器件层中,且其中,第一子器件层以及第二子器件层在水平面方向上,位于不同层。

进一步地,在本实施例中,可以将会频繁存取的数据存储在由相变存储阵列与相变存储阵列驱动器共同构成的相变存储器中,因为相变存储器具有比闪存更快的读写速度,以使半导体器件100能够进行随机存取和高速存取。且可以将较少使用的数据存储在由与NAND存储阵列驱动器共同构成的NAND闪存存储器中,因为相比于相变存储器,NAND闪存存储器的读写速度较慢,但NAND闪存存储器的存储密度较高,将较少使用的数据存储在NAND闪存存储器中,可以在提高半导体器件100存储容量的前提下,实现存储速度的增加以及半导体器件100的制造成本的降低。

请继续参阅图2,外围电路芯片110中除了包括依次层叠设置的第一衬底111、器件层112以及第一键合层113之外,还包括覆盖器件层112的第一互连层115。

第一衬底111可以为半导体衬底,包括但不限于硅(例如,单晶硅)、硅锗(SiGe)、砷化镓(GaAs)、锗(Ge)、绝缘体上硅(SOI)或其他任何合适的材料。进一步地,在第一衬底111中形成有隔离结构1111以及掺杂结构1112,隔离结构1111可以为浅沟槽隔离结构(STI,Shallow Trench Isolation)。

器件层112设置于第一衬底111的上方,器件层112包括形成于第一衬底111上的第一驱动器1121、第二驱动器1122以及控制器1123,其中,第一驱动器1121、第二驱动器1122以及控制器1123分别包括多个晶体管1124。进一步地,第一衬底111中的掺杂结构1112可以为晶体管1124的源极区域和漏极区域。

第一互连层115用以电连接器件层112和第一键合层113。进一步地,第一互连层115包括多个第一横向互连线1151以及多个第一垂直过孔触点1152。需要说明的是,第一互连层115还可以包括一个或多个层间电介质层(图中未示出)(Inter Level Dielectric,ILD,也称为“金属间电介质层(Inter Metal Dielectric,IMD)”),在层间电介质层中也可以形成第一横向互连线1151和第一垂直过孔触点1152,第一互连层115可以包括在多个层间电介质层中的第一横向互连线1151和第一垂直过孔触点1152。具体地,第一横向互连线1151以及第一垂直过孔触点1152的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合,第一互连层115中的层间电介质层可以包括电介质材料,包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

第一键合层113设置于第一互连层115的上方,包括多个第一键合触点1131以及电隔离多个第一键合触点1131的电介质(图中未示出),第一键合触点1131贯穿第一键合层113,并与第一互连层115电连接。具体地,第一键合触点1131的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合。进一步地,在第一键合层113中,除多个第一键合触点1131以外的部分可以用电介质形成,该电介质包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

请继续参阅图2,存储阵列芯片120中除了包括依次层叠设置的第二键合层121、第二存储阵列1222、第一存储阵列1221以及第二衬底123,还包括覆盖第一存储阵列1221以及第二存储阵列1222的第二互连层125。

第二键合层121设置于外围电路芯片110的第一键合层113的上方,包括多个第二键合触点1211以及电隔离多个第二键合触点1211的电介质(图中未示出),第二键合触点1211贯穿第二键合层121,并与第二互连层125电连接。具体地,第二键合触点1211的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合。进一步地,在第二键合层121中,除多个第二键合触点1211以外的部分可以用电介质形成,该电介质包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

第二存储阵列1222设置于第二键合层121上方,在本实施例中,第二存储阵列1222为相变存储阵列(Phase Change Memory,PCM),包括多条第二字线(Word Line,WL)12221、多条第二位线(Bit Line,BL)12222以及设置于多条第二字线12221和多条第二位线12222的交叉点处的多个第二存储单元12223(相变存储单元)。其中,第二字线12221以及第二位线12222为导电材料,包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合。第二存储阵列1222(相变存储阵列)是通过第二存储单元12223中的相变材料在晶态和非晶态之间相互转化时所表现出来的电阻差异来存储数据。具体地,第二存储单元12223的材料包括基于硫属化物的合金(硫属化物玻璃),例如GST(Ge-Sb-Te)合金,或任何其他合适的相变材料、电阻氧化物材料或导电桥材料。

需要说明的是,在本实施例中,第二存储阵列1222包括两个相变存储阵列叠层,而在由本发明而成的其它变形例中,第二存储阵列1222也可以只包括一层相变存储阵列、或包括两个以上的相变存储阵列叠层,每个相变存储阵列叠层包括多条第二字线、多条第二位线以及设置于多条第二字线和多条第二位线的交叉点处的多个第二存储单元,且每个相变存储阵列叠层通过多条第二字线和多条第二位线与外围电路芯片110电连接。举例来说,在一个可能的变形例中,第二存储阵列1222包括依次层叠设置于第二键合层121上方的第一相变存储阵列叠层以及第二相变存储阵列叠层,其中,第一相变存储阵列叠层包括多条第一字线、多条第一位线以及设置于多条第一字线和多条第一位线的交叉点处的多个第一相变存储单元,第一相变存储阵列叠层通过多条第一字线以及多条第一位线电连接至外围电路芯片110中的第二驱动器1122,以使第二驱动器1122可以驱动第一相变存储单元进行读写操作;第二相变存储阵列叠层包括多条第二字线、多条第二位线以及设置于多条第二字线和多条第二位线的交叉点处的多个第二相变存储单元,第二相变存储阵列叠层通过多条第二字线以及多条第二位线电连接至外围电路芯片110中的第二驱动器1122,以使第二驱动器1122可以驱动第二相变存储单元进行读写操作。

第一存储阵列1221设置于第二存储阵列1222上方,在本实施例中,第一存储阵列1221为NAND存储阵列,包括堆叠层12211以及垂直贯穿堆叠层12211的多个沟道柱。

需要说明的是,第一存储阵列1221包括存储区以及阶梯区,为了使第一存储阵列1221与第二存储阵列1222之间的读写不会互相干扰,在本实施例中,第二存储阵列1222设置于第一存储阵列1221的阶梯区的纵向投影下方。

其中,堆叠层12211由绝缘层122111和栅极层122112交替层叠而成,绝缘层122111由绝缘材料制成,包括但不限于氧化硅、氮化硅、氮氧化硅或以上材料的组合,栅极层122112由导电材料制成,包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(AL)、掺杂硅、硅化物或以上材料的组合。进一步地,堆叠层12211包括底部选择管层(图中未示出),该底部选择管层包括交替层叠的2个绝缘层122111和2个栅极层122112,其中,该底部选择管层的栅极层122112至少为1个,也可以为2个或3个或其他数量。

进一步地,垂直贯穿堆叠层12211的多个沟道柱可以包括多个存储沟道柱122121、多个虚拟沟道柱122122,以及设置于多个存储沟道柱122121和多个虚拟沟道柱122122之间的多个过渡沟道柱(图中未示出)。需要说明的是,在本实施例中,每个存储沟道柱122121是“电荷捕获”类型的NAND存储器串,且在每个存储沟道柱122121内壁依次形成有功能层1221211和沟道层1221212,功能层1221211由存储沟道柱122121内部至存储沟道柱122121外表面依次包括堆叠的隧穿层、储存层(也称为“电荷捕获层”)和阻挡层。其中,隧穿层的示例性材料可以包括氧化硅、氮氧化硅或以上材料的组合,储存层的示例性材料可以包括氮化硅、氮氧化硅、硅或以上材料的组合,阻挡层的示例性材料可以包括氧化硅、氮氧化硅、高介电常数电介质或以上材料的组合,沟道层1221212的示例性材料可以包括非晶硅、多晶硅或单晶硅。

进一步地,存储沟道柱122121还包括多个控制栅极,在本实施例中,堆叠层12211中的每个栅极层122112作为存储沟道柱122121中每个存储单元的控制栅极。

进一步地,每个存储沟道柱122121还包括外延层1221213以及插塞1221214,外延层1221213用以作为存储沟道柱122121源选择栅极控制的通道,外延层1221213设置存储沟道柱122121靠近第二衬底123的端部,并且与存储沟道柱122121的沟道层1221212相接触,插塞1221214用以作为存储沟道柱122121的漏极,且在本实施例中,插塞1221214也用以作为存储沟道柱122121的蚀刻停止层,以防止对填充在存储沟道柱122121中的电介质(例如氧化硅和氮化硅)的蚀刻。进一步地,外延层1221213的示例性材料可以包括从第二衬底123外延生长的半导体材料,例如单晶硅,插塞1221214的示例性材料可以包括多晶硅。

需要说明的是,在由本发明而成的其他实施例中,存储沟道柱122121也可以是“浮栅”类型的NAND存储器串。应当理解的是,存储阵列芯片120中可以具有多层堆叠层12211,具有多层堆叠层12211的存储阵列芯片120中会具有位于不同堆叠层12211之间的层间插塞,以实现不同堆叠层12211中存储沟道柱122121的电连接。

需要说明的是,在本实施例中,第一存储阵列1221只包括一层NAND存储阵列,而在由本发明而成的其它变形例中,第一存储阵列1221可以包括多个NAND阵列叠层,每个NAND阵列叠层分别包括堆叠层、垂直贯穿堆叠层的多个沟道柱、多条第一字线以及多条第一位线,且每个NAND阵列叠层通过多条第一字线和多条第一位线与外围电路芯片110电连接。举例来说,在一个可能的变形例中,第一存储阵列1221包括依次层叠设置于第二存储阵列1222上方的第一NAND阵列叠层以及第二NAND阵列叠层,其中,第一NAND阵列叠层包括第一堆叠层、垂直贯穿第一堆叠层的多个第一存储沟道柱、多条第三字线以及多条第三位线,第一NAND阵列叠层通过多条第三字线以及多条第三位线电连接至外围电路芯片110中的第一驱动器1121,以使第一驱动器1121可以驱动第一存储沟道柱中的存储单元进行读写操作;第二NAND阵列叠层包括第二堆叠层、垂直贯穿第二堆叠层的多个第二存储沟道柱、多条第四字线以及多条第四位线,第二NAND阵列叠层通过多条第四字线以及多条第四位线电连接至外围电路芯片110中的第一驱动器1121,以使第一驱动器1121可以驱动第二存储沟道柱中的存储单元进行读写操作。

第二互连层125用以电连接第一存储阵列1221和第二键合层121、并电连接第二存储阵列1222和第二键合层121。进一步地,第二互连层125包括多个第二横向互连线1251以及多个第二垂直过孔触点1252。需要说明的是,第二互连层125还可以包括一个或多个层间电介质层(图中未示出)(Inter Level Dielectric,ILD,也称为“金属间电介质层(InterMetal Dielectric,IMD)”),在层间电介质层中也可以形成第二横向互连线1251和第二垂直过孔触点1252,第二互连层125可以包括在多个层间电介质层中的第二横向互连线1251和第二垂直过孔触点1252。具体地,第二横向互连线1251以及第二垂直过孔触点1252的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合,第二互连层125中的层间电介质层可以包括电介质材料,包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

第二衬底123设置于第一存储阵列1221上,可以为半导体衬底,具体包括至少一个单质半导体材料(例如:为硅(Si)衬底、锗(Ge)衬底)、至少一个III-V化合物半导体材料、至少一个II-VI化合物半导体材料、至少一个有机半导体材料或者在本领域已知的其他半导体材料。

进一步地,请继续参阅图2,在本实施例中,半导体器件100还包括设置于第二衬底123相反于存储阵列层122的一侧的第二绝缘层130,以及设置于第二绝缘层130中的第二引出结构131。具体地,第二引出结构131包括第二焊盘1311以及第二垂直引出触点1312,第二焊盘1311用以电连接外部电路,以传输半导体器件100与外部电路之间的电信号,且第二互连层125包括至少一个第二垂直互连触点1253,第二垂直引出触点1312与第二垂直互连触点1253电连接。

需要说明的是,在由本发明而成的其它变形例中,还可以将第二绝缘层130设置于第一衬底111相反于器件层112的一侧,或是在所述一侧另设置和上述第二绝缘层130以及设置于第二绝缘层130中的第二引出结构131一样功能的第一绝缘层及第一引出结构(图中未示出),设置于第一绝缘层中的第一引出结构包括第一焊盘以及第一垂直引出触点,第一焊盘用以电连接外部电路,以传输半导体器件100与外部电路之间的电信号,且第一互连层115包括至少一个第一垂直互连触点(图中未示出),第一垂直引出触点与第一垂直互连触点电连接。

在本实施例中,第一驱动器1121、第二驱动器1122以及控制器1123可以通过第一横向互连线1151、第一垂直过孔触点1152、第一键合触点1131、第二键合触点1211、第二横向互连线1251以及第二垂直过孔触点1252电连接到第一存储阵列1221以及第二存储阵列1222。

区别于现有技术,本发明提供了一种半导体器件100,包括:依次层叠设置第一衬底111、器件层112以及第一键合层113的外围电路芯片110,器件层112包括第一驱动器1121、第二驱动器1122以及控制器1123,依次层叠设置第二键合层121、第二存储阵列1222、第一存储阵列1221以及第二衬底123的存储阵列芯片120,且存储阵列芯片120设置于外围电路芯片110上方,并通过第一键合层113以及第二键合层121电连接外围电路芯片110,其中,控制器1123用以通过控制第一驱动器1121以及第二驱动器1122、并经由第一键合层113以及第二键合层121,而控制第一存储阵列1221以及第二存储阵列1222进行读写操作,且由于控制器1123与第一驱动器1121以及第二驱动器1122形成于同一芯片上,从而有效地通过提高控制器1123与第一驱动器1121以及第二驱动器1122之间的通信速度,而提高了第一存储阵列1221与第二存储阵列1222之间的数据通信速度,同时,降低了半导体器件100的制造成本。

请参阅图3以及图4a-图4j,图3是根据本发明而成的实施例所提供的半导体器件200的制备方法的流程示意图,图4a-图4j是根据本发明而成的实施例所提供的半导体器件200的制备方法的工艺流程示意图。

如图3所示,该半导体器件200的制备方法具体包括:

外围电路晶圆形成步骤S101:提供第一衬底211,并在第一衬底211上依次形成器件层212以及第一键合层213而形成外围电路晶圆210,其中,器件层212包括第一驱动器2121、第二驱动器2122以及控制器2123。

具体地,请参阅图4a,在本实施例中,第一衬底211可以为半导体衬底,包括但不限于硅(例如,单晶硅)、硅锗(SiGe)、砷化镓(GaAs)、锗(Ge)、绝缘体上硅(SOI)或其他任何合适的材料,且第一衬底211中形成有隔离结构2111以及掺杂结构2112,且隔离结构2111可以为浅沟槽隔离结构(STI,Shallow Trench Isolation)。

器件层212设置于第一衬底211的上方,器件层212包括形成于第一衬底211上的第一驱动器2121、第二驱动器2122以及控制器2123,其中,第一驱动器2121、第二驱动器2122以及控制器2123分别包括多个晶体管2124。进一步地,第一衬底211中的掺杂结构2112可以为晶体管2124的源极区域和漏极区域。

容易理解的是,在本实施例中,晶体管2124可以通过多种工艺形成,包括但不限于光刻、干法/湿法蚀刻、薄膜沉积、热生长、注入、化学机械抛光(Chemical MechanicalPolishing,CMP)和任何其他合适的工艺;掺杂结构1112可以通过离子注入和/或热扩散在第一衬底211中形成;隔离结构2111可以通过湿法/干法蚀刻和薄膜沉积在第一衬底211中形成。

需要说明的是,因为外围电路晶圆210中还会包括用以电连接器件层212和第一键合层213的第一互连层215,所以,在外围电路晶圆形成步骤S101中,还包括:

在第一衬底211上形成覆盖器件层212的第一互连层215。

具体地,请参阅图4b,第一互连层215包括多个第一横向互连线2151以及多个第一垂直过孔触点2152。需要说明的是,第一互连层215还可以包括一个或多个层间电介质层(图中未示出)(Inter Level Dielectric,ILD,也称为“金属间电介质层(Inter MetalDielectric,IMD)”),在层间电介质层中也可以形成第一横向互连线2151和第一垂直过孔触点2152,第一互连层215可以包括在多个层间电介质层中的第一横向互连线2151和第一垂直过孔触点2152。具体地,第一横向互连线2151以及第一垂直过孔触点2152的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合,第一互连层215中的层间电介质层可以包括电介质材料,包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

容易理解的是,在本实施例中,第一互连层215中的多个第一横向互连线2151以及多个第一垂直过孔触点2152可以包括通过一种或多种薄膜沉积工艺沉积的导电材料,薄膜沉积工艺包括但不限于化学气相沉积(Chemical Vapor Deposition,CVD)、物理气相沉积(Physical Vapour Deposition,PVD)、原子层沉积(Atomic Layer Deposition,ALD)、电镀、无电镀敷或其任何组合。用于形成互连的制造工艺还可以包括光刻、化学机械抛光(Chemical Mechanical Polishing,CMP)、湿法/干法蚀刻或任何其他合适的工艺。上述层间电介质层(ILD层)可以包括通过一种或多种薄膜沉积工艺沉积的电介质材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。

进一步地,请参阅图4c,第一键合层213设置于第一互连层215的上方,包括多个第一键合触点2131以及电隔离多个第一键合触点2131的电介质(图中未示出),第一键合触点2131贯穿第一键合层213,并与第一互连层215电连接。具体地,第一键合触点2131的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合。进一步地,在第一键合层213中,除多个第一键合触点2131以外的部分可以用电介质形成,该电介质包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

容易理解的是,在本实施例中,可以通过一种或多种薄膜沉积工艺在第一互连层215的顶表面上沉积电介质层,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,通过使用图案化工艺(例如,对电介质层中的电介质材料进行光刻和干法/湿法蚀刻)首先穿过电介质层图案化第一接触孔(图中未示出),可以形成穿过电介质层并且与第一互连层115中的第一横向互连线2151以及第一垂直过孔触点2152接触的第一接触孔,并在第一接触孔内填充导体(例如,铜)以形成第一键合触点2131。在一些实施例中,填充第一接触孔的工艺步骤还包括在沉积导体之前沉积阻挡层、粘合层和/或种子层。

存储阵列晶圆形成步骤S102:提供第二衬底223,并在第二衬底223上依次形成第一存储阵列2221、第二存储阵列2222以及第二键合层221而形成存储阵列晶圆220。

具体地,请参阅图4d,在本实施例中,第二衬底223可以为半导体衬底,具体包括至少一个单质半导体材料(例如:为硅(Si)衬底、锗(Ge)衬底)、至少一个III-V化合物半导体材料、至少一个II-VI化合物半导体材料、至少一个有机半导体材料或者在本领域已知的其他半导体材料。

第一存储阵列2221设置于第二衬底223上,在本实施例中,第一存储阵列2221为NAND存储阵列,包括堆叠层22211以及垂直贯穿堆叠层22211的多个沟道柱。其中,堆叠层22211先由绝缘层222111和牺牲层交替层叠而成,在形成多个沟道柱之后,再将牺牲层置换为栅极层222112。具体地,绝缘层222111由绝缘材料制成,包括但不限于氧化硅、氮化硅、氮氧化硅或以上材料的组合,栅极层222112由导电材料制成,包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(AL)、掺杂硅、硅化物或以上材料的组合。

容易理解的是,交替层叠的绝缘层222111和牺牲层可以通过一种或多种薄膜沉积工艺形成,包括但不限于CVD、PVD、ALD或其任何组合。且将牺牲层置换为栅极层222112的置换步骤可以通过栅极替换工艺形成,例如,对牺牲层进行湿法/干法蚀刻出凹槽,之后,用导电材料填充所得到的凹槽以将牺牲层置换为栅极层222112。且形成多个沟道柱的工艺方法可以包括:使用干法蚀刻和/或湿法蚀刻(例如深反应离子蚀刻(DeepReaction IonEtching,DRIE))形成垂直贯穿堆叠层22211并进入第二衬底223中的沟道孔(图中未示出),然后在沟道孔的下部中从第二衬底223外延生长外延层2221213。在本实施例中,用于形成NAND存储阵列的制造工艺还包括:使用诸如ALD、CVD、PVD或其任何组合之类的薄膜沉积工艺,用多个层(功能层2221211和沟道层2221212)填充沟道孔;且用于形成NAND存储阵列的制造工艺还包括:通过在沟道柱22212的上端处蚀刻凹部,并使用诸如ALD、CVD、PVD或其任何组合之类的薄膜沉积工艺,用半导体材料填充凹部,而在沟道孔的上部中形成插塞2221214。

具体地,请参阅图4e,在本实施例中,第二存储阵列2222为相变存储阵列(PhaseChange Memory,PCM),包括多条第二字线(Word Line,WL)22221、多条第二位线(Bit Line,BL)22222以及设置于多条第二字线22221和多条第二位线22222的交叉点处的多个第二存储单元22223(相变存储单元)。其中,第二字线22221以及第二位线22222为导电材料,包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合。第二存储阵列2222(相变存储阵列)是通过第二存储单元22223中的相变材料在晶态和非晶态之间相互转化时所表现出来的导电性差异来存储数据。具体地,第二存储单元22223的材料包括基于硫属化物的合金(硫属化物玻璃),例如GST(Ge-Sb-Te)合金,或任何其他合适的相变材料、电阻氧化物材料或导电桥材料。

容易理解的是,第二存储单元22223(相变存储单元)可以通过多种工艺形成,包括但不限于光刻、干法/湿法蚀刻、薄膜沉积、热生长、注入、化学机械抛光(ChemicalMechanical Polishing,CMP)和任何其他合适的工艺。

需要说明的是,存储阵列晶圆210中还包括覆盖第一存储阵列2221以及第二存储阵列2222的第二互连层225,在存储阵列晶圆形成步骤S102中,还包括:

在第二衬底223上形成覆盖第一存储阵列2221以及第二存储阵列2222的第二互连层225。

具体地,请参阅图4f,第二互连层225用以电连接第一存储阵列2221和第二键合层221、并电连接第二存储阵列2222和第二键合层221。进一步地,第二互连层225包括多个第二横向互连线2251以及多个第二垂直过孔触点2252。需要说明的是,第二互连层225还可以包括一个或多个层间电介质层(图中未示出)(Inter Level Dielectric,ILD,也称为“金属间电介质层(Inter Metal Dielectric,IMD)”),在层间电介质层中也可以形成第二横向互连线2251和第二垂直过孔触点2252,第二互连层225可以包括在多个层间电介质层中的第二横向互连线2251和第二垂直过孔触点2252。具体地,第二横向互连线2251以及第二垂直过孔触点2252的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合,第二互连层225中的层间电介质层可以包括电介质材料,包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

容易理解的是,在本实施例中,第二互连层225中的多个第二横向互连线2251以及多个第二垂直过孔触点2252可以包括通过一种或多种薄膜沉积工艺沉积的导电材料,薄膜沉积工艺包括但不限于化学气相沉积(Chemical Vapor Deposition,CVD)、物理气相沉积(Physical Vapour Deposition,PVD)、原子层沉积(Atomic Layer Deposition,ALD)、电镀、无电镀敷或其任何组合。用于形成互连的制造工艺还可以包括光刻、化学机械抛光(Chemical Mechanical Polishing,CMP)、湿法/干法蚀刻或任何其他合适的工艺。上述层间电介质层(ILD层)可以包括通过一种或多种薄膜沉积工艺沉积的电介质材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。

进一步地,请参阅图4g,第二键合层221包括多个第二键合触点2211以及电隔离多个第二键合触点2211的电介质(图中未示出),第二键合触点2211贯穿第二键合层221,并与第二互连层225电连接。具体地,第二键合触点2211的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、硅化物或以上材料的组合。进一步地,在第二键合层221中,除多个第二键合触点2211以外的部分可以用电介质形成,该电介质包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数电介质或以上材料的组合。

容易理解的是,在本实施例中,可以通过一种或多种薄膜沉积工艺在第一互连层215的顶表面上沉积电介质层,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,通过使用图案化工艺(例如,对电介质层中的电介质材料进行光刻和干法/湿法蚀刻)首先穿过电介质层图案化第一接触孔(图中未示出),可以形成穿过电介质层并且与第一互连层215中的第一横向互连线2151以及第一垂直过孔触点2152接触的第一接触孔,并在第一接触孔内填充导体(例如,铜)以形成第一键合触点1131。在一些实施例中,填充第一接触孔的工艺步骤还包括在沉积导体之前沉积阻挡层、粘合层和/或种子层。

键合步骤S103:将存储阵列晶圆220翻转,并通过第一键合层213以及第二键合层221对外围电路晶圆210以及存储阵列晶圆220进行键合。

具体地,请参阅图4h-图4i,第一键合层213中的第一键合触点2131与第二键合层221中的第二键合触点2211一一对应。

需要说明的是,为了使半导体器件200与外部电路之间的电信号可以进行传输,在键合步骤S103之后,还包括:

在第二衬底223上形成绝缘层230;

在绝缘层230中形成引出结构231。

具体地,请参阅图4j,引出结构231包括第二焊盘2311以及第二垂直引出触点2312,第二焊盘2311用以电连接外部电路,以传输半导体器件200与外部电路之间的电信号,且第二互连层225包括至少一个第二垂直互连触点2253,第二垂直引出触点2312与第二垂直互连触点2253电连接。

容易理解的是,在本实施例中,第一驱动器2121、第二驱动器2122以及控制器2123可以通过第一横向互连线2151、第一垂直过孔触点2152、第一键合触点2131、第二键合触点2211、第二横向互连线2251以及第二垂直过孔触点2252电连接到第一存储阵列2221以及第二存储阵列2222。

区别于现有技术,本发明提供了一种半导体器件200的制备方法,包括:提供第一衬底211,并在第一衬底211上依次形成器件层212以及第一键合层213而形成外围电路晶圆210,其中,器件层212包括第一驱动器2121、第二驱动器2122以及控制器2123,提供第二衬底223,并在第二衬底223上依次形成第一存储阵列2221、第二存储阵列2222以及第二键合层221而形成存储阵列晶圆220,之后,将存储阵列晶圆220翻转,并通过第一键合层213以及第二键合层221对外围电路晶圆210以及存储阵列晶圆220进行键合,其中,存储阵列晶圆220通过第一键合层213以及第二键合层221电连接外围电路晶圆210,其中,控制器2123用以通过控制第一驱动器2121以及第二驱动器2122、并经由第一键合层213以及第二键合层221,而控制第一存储阵列2221以及第二存储阵列2222进行读写操作,且由于控制器2123与第一驱动器2121以及第二驱动器2122形成于同一芯片上,从而有效地通过提高控制器2123与第一驱动器2121以及第二驱动器2122之间的通信速度,而提高了第一存储阵列2221与第二存储阵列2222之间的数据通信速度,同时,降低了半导体器件200的制造成本。

除上述实施例外,本发明还可以有其他实施方式。凡采用等同替换或等效替换形成的技术方案,均落在本发明要求的保护范围。

综上所述,虽然本发明已将优选实施例揭露如上,但上述优选实施例并非用以限制本发明,本领域的普通技术人员,在不脱离本发明的精神和范围内,均可作各种更动与润饰,因此本发明的保护范围以权利要求界定的范围为准。

- 半导体器件中孔、半导体器件的制备方法及半导体器件

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置