一种内存颗粒多维测试方法、装置、系统和可读存储介质

文献发布时间:2023-06-19 12:13:22

技术领域

本发明属于内存测试技术领域,具体涉及一种内存颗粒多维测试方法、装置、系统和可读存储介质。

背景技术

内存条是用于储存数据的一个重要计算机部件,由于计算机的广泛普及,内存条的使用也越来越多,在使用前都要对内存条进行性能测试。

现有的内存颗粒的测试主要分为ATE(Automated Testing Equipment,自动化测试设备)测试以及SLT(System Level Testing,系统级别测试)测试。其中,ATE测试是指通过给内存颗粒的输入管道施加所需的激励信号,同时监测内存颗粒的输出管脚,观察输出信号是否是预期的值;SLT测试是指在ATE之后,执行系统软件程序,测试内存颗粒各个模块的功能是否正常的测试。

为了测试的准确性,通常会将待测内存条插入测试装置主板的内存条插槽中模拟内存条的使用情况来进行测试。然而,现有的测试装置不能多个产品同时插入到通用主板上面小间隙的排布的插槽内,现有的软件测试方法也无法模拟出内存颗粒真实应用场景下的Multi-Chip(多颗粒)、Multi-Rank(多Rank)状况,以至于有些在"重负载"下才失效的DRAM颗粒难以在芯片测试阶段被筛选出来,进而导入进入市场的内存颗粒的性能不够高。

发明内容

本发明的目的在于提供一种内存颗粒多维测试方法、装置、系统和可读存储介质,用以解决现有技术中在"重负载"下才失效的DRAM颗粒难以在内存颗粒测试阶段被筛选出来的技术问题。

为了解决上述技术问题,本发明采用以下技术方案:

本发明第一方面提供一种内存颗粒多维测试方法,所述方法应用于待测试内存颗粒以多Rank颗粒组合形式运行的测试场景中,所述方法包括:

在测试板两面的内存颗粒插槽中同时装载多个待测试内存颗粒,以使所述多个待测试内存颗粒以多Rank颗粒组合形式运行;

将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境;

基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址。

进一步的,所述将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境,具体包括:

在BIOS的配置中设置地址映射模式为交错映射模式。

进一步的,所述基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址,具体包括:

根据所述多Rank颗粒的物理地址,对每一Rank颗粒同时进行访问;

在每一所述Rank颗粒中分别执行不同的测试算法,对所述Rank颗粒进行ATE和/或SLT测试;

根据所述交错映射模式对每一内存颗粒单元进行精确定位,以获取错误内存颗粒单元的物理地址。

进一步的,所述根据所述交错映射模式对每

一内存颗粒单元进行精确定位,以获取错误内存颗粒单元的物理地址,具体包括:

获取错误内存颗粒单元的线性地址;

读取内存控制器的地址映射寄存器组;

根据所述地址映射寄存器组的设置值,计算得出所述错误内存颗粒单元的Rank值,以得到所述错误内存颗粒单元的初步物理地址;

根据所述初步物理地址中的Rank信息,得到所述错误内存颗粒单元的最终物理地址。

本发明第二方面还提供一种内存颗粒多维测试装置,所述装置应用于待测试内存颗粒以多Rank颗粒组合形式运行的测试场景中,所述装置包括:

内存颗粒装载模块,用于在测试板两面的内存颗粒插槽中同时装载多个待测试内存颗粒,以使所述多个待测试内存颗粒以多Rank颗粒组合形式运行;

测试环境设置模块,用于将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境;

错误颗粒获取模块,用于基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址。

进一步的,所述测试环境设置模块,具体包括:

地址映射模式设置单元,用于在BIOS的配置中设置地址映射模式为交错映射模式。

进一步的,所述错误颗粒获取模块,具体包括:

Rank同时访问单元,用于根据所述多Rank颗粒的物理地址,对每一Rank颗粒同时进行访问;

Rank颗粒测试单元,用于在每一所述Rank颗粒中分别执行不同的测试算法,对所述Rank颗粒进行ATE和/或SLT测试;

错误颗粒获取单元,用于根据所述交错映射模式对每一内存颗粒单元进行精确定位,以获取错误内存颗粒单元的物理地址。

进一步的,所述错误颗粒获取单元,具体包括:

线性地址获取子单元,用于获取错误内存颗粒单元的线性地址;

寄存器组的读取子单元,用于读取内存控制器的地址映射寄存器组;

初步物理地址获取子单元,用于根据所述地址映射寄存器组的设置值,计算得出所述错误内存颗粒单元的Rank值,以得到所述错误内存颗粒单元的初步物理地址;

最终物理地址获取子单元,用于根据所述初步物理地址中的Rank信息,得到所述错误内存颗粒单元的最终物理地址。

本发明第三方面还提供一种内存颗粒多维测试系统,所述系统包括:测试控制模块以及如第一方面所述的内存颗粒多维测试装置,所述测试控制模块与所述内存颗粒多维测试装置通信连接;所述测试控制模块用于进行内存颗粒测试参数的配置、构建测试模型以及测试过程控制;所述内存颗粒多维测试装置用于对所述内存颗粒进行性能测试并获取错误内存颗粒单元的物理地址。

本发明第四方面还提供一种可读存储介质,所述可读存储介质上存储有指令,当所述指令在计算机上运行时,执行如第一方面或第一方面中任意一种所述的内存颗粒多维测试方法。

本发明第五方面还提供一种包含指令的计算机程序产品,当所述指令在计算机上运行时,使所述计算机执行如上第一方面或第一方面中任意一种所述的内存颗粒多维测试方法。

本发明的有益效果为:通过在测试板两面的内存颗粒插槽中同时装载多个待测试内存颗粒,以使所述多个待测试内存颗粒以多Rank颗粒组合形式运行;然后将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境;最后基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址。本发明能够将“有负载才失效"、"内存颗粒互相干扰"等由于多Rank颗粒组合形式引起的问题在产品SMT(Surface MountingTechnology,表面组装技术)前筛选出来,提高了内存颗粒电性能负载压力测试的能力,进而提高了内存颗粒测试的效能。

附图说明

图1是本发明实施例中应用的测试装置的结构示意图;

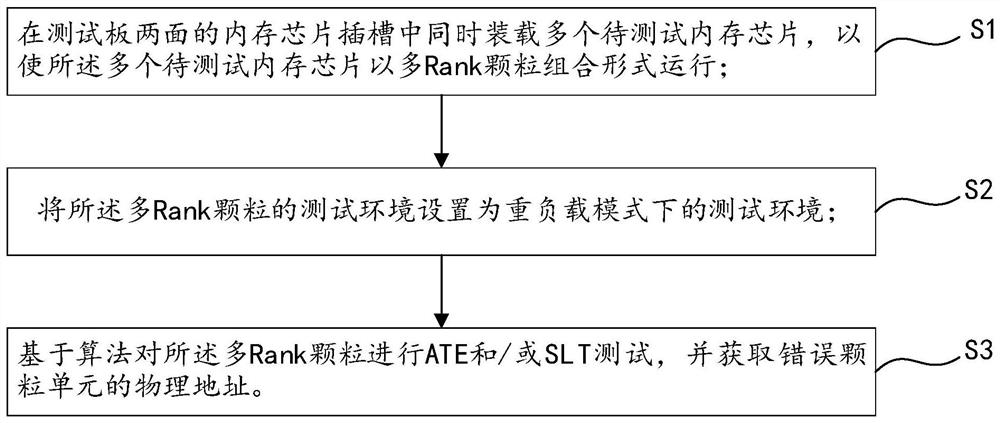

图2是本发明实施例中一种内存颗粒多维测试方法的流程示意图;

图3是本发明实施例中步骤S3的流程示意图;

图4是本发明实施例中步骤S32一种实施方式的流程示意图;

图5是本发明实施例中步骤S33的流程示意图;

图6是本发明实施例中一种内存颗粒多维测试装置的结构示意图;

图7是本发明实施例中一种内存颗粒多维测试系统的结构示意图。

具体实施方式

为使本说明书实施例的目的、技术方案和优点更加清楚,下面将结合本说明书实施例中的附图,对本说明书实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本说明书一部分实施例,而不是全部的实施例。基于本说明书中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本说明保护的范围。

首先,为了便于理解,参见图1,示出了支持实施本发明实施例中的内存颗粒多维测试方法的内存测试装置,其中,所述内存测试装置包括有测试板,测试板的上下两面均设置有多个用于连接芯片的安装位,多个安装位排成一排,使用时,在所述测试板的上下两面的安装位中均满载插入多个内存颗粒,以使多个内存颗粒形成多Rank组合,以使待测试内存颗粒以多Rank颗粒组合形式运行。

实施例一

为了解决上述技术问题,本发明采用以下技术方案:

参见图2,本发明第一方面提供一种内存颗粒多维测试方法,所述方法应用于待测试内存颗粒以多Rank颗粒组合形式运行的测试场景中,所述方法包括:

步骤S1,在测试板两面的内存颗粒插槽中同时装载多个待测试内存颗粒,以使所述多个待测试内存颗粒以多Rank颗粒组合形式运行;

作为一种可实现的方式,如图1所示,所述测试板每一面均包括9个安装位,则在每一安装位中均装载待测试内存颗粒,则此时每一面的内存颗粒组合形成一个Rank,则整个测试板上装载的内存颗粒组合形成为多Rank颗粒组合,以模拟内存颗粒在实际使用情况下的负载,让多Rank重负载的测试成为可能。

步骤S2,将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境;

其中,优选的,所述将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境,具体包括:

在BIOS(Basic Input Output System,基本输入输出系统)的配置中设置地址映射模式为交错映射模式(rank-interleaved);通过将地址映射模式设置为交错映射模式,CPU(Central Processing Unit,中央处理器)在进行内存访问时,能够同时打开多个Rank进行访问,从而造成内存颗粒动态的“重负载模式”。而如果不将地址映射模式设置为交错映射模式,CPU在进行内存访问时,依然会对Rank进行依次访问,从而无法形成内存颗粒的“重负载模式”。

步骤S3,基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址。

作为一种可选的实施方式,参见图3,所述基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址,具体包括:

步骤S31,根据所述多Rank颗粒的物理地址,对每一Rank颗粒同时进行访问;

步骤S32,在每一所述Rank颗粒中分别执行不同的测试算法,对所述Rank颗粒进行ATE和/或SLT测试;

其中,作为一种可实现的实施的方式,所述在每一所述Rank颗粒中分别执行不同的测试算法可以是:例如,测试板上有两个Rank颗粒,分别为Rank0,Rank1,系统采用两种测试算法,分别为MarchC算法和DataRetention算法,则两种算法的执行流程如图4所示。

通过在不同的Rank中执行不同的测试算法,能够提高对Rank的访问强调以及Rank间的相互干扰,以进一步造成多Rank颗粒运行时内存颗粒的重负载。

步骤S33,根据所述交错映射模式对每一内存颗粒单元进行精确定位,以获取错误内存颗粒单元的物理地址。

作为一种可选的实施方式,参见图5,所述根据所述交错映射模式对每一内存颗粒单元进行精确定位,以获取错误内存颗粒单元的物理地址,具体包括:

步骤S331,获取错误内存颗粒单元的线性地址;

其中,通过在Rank上执行的测试算法能够有效获取错误内存颗粒单元的线性地址。

步骤S332,读取内存控制器的地址映射寄存器组;

其中,需要说明的是,所述地址映射寄存器中存储有线性地址相关位与Rank间的对应关系。

步骤S333,根据所述地址映射寄存器组的设置值,计算得出所述错误内存颗粒单元的Rank值,以得到所述错误内存颗粒单元的初步物理地址;

其中,作为一种可选的实现方式,在所述地址映射寄存器中读取线性地址(二进制)相关位(bit)与Rank间的对应关系,例如:线性地址的第6bit代表Rank位,以此获得该Rank位上对应的内存颗粒的物理地址。但值得注意的是,由于以多Rank颗粒组合形式运行,此时获取到物理地址的内存颗粒尚无法确定处于测试板哪一面上的Rank中,因此,需要进入步骤S334。

步骤S334,根据所述初步物理地址中的Rank信息,得到所述错误内存颗粒单元的最终物理地址。

其中,作为一种可选的实现方式,例如,在装载了两面Rank的情况下,根据内存颗粒物理地址的Rank信息,就能获知具体是哪一面上的Rank中的内存颗粒,并最终确定出错误内存颗粒单元。

本发明实施例通过在测试板两面的内存颗粒插槽中同时装载多个待测试内存颗粒,以使所述多个待测试内存颗粒以多Rank颗粒组合形式运行;然后将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境;最后基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址。本发明能够将“有负载才失效"、"内存颗粒互相干扰"等由于多Rank颗粒组合形式引起的问题在产品SMT(Surface Mounting Technology,表面组装技术)前筛选出来,提高了内存颗粒电性能负载压力测试的能力,进而提高了内存颗粒测试的效能。

实施例二

参见图6,本发明第二方面还提供一种内存颗粒多维测试装置,所述装置应用于待测试内存颗粒以多Rank颗粒组合形式运行的测试场景中,所述装置包括:

内存颗粒装载模块,用于在测试板两面的内存颗粒插槽中同时装载多个待测试内存颗粒,以使所述多个待测试内存颗粒以多Rank颗粒组合形式运行;

作为一种可实现的方式,如图1所示,所述测试板每一面均包括9个安装位,则在每一安装位中均装载待测试内存颗粒,则此时每一面的内存颗粒组合形成一个Rank,则整个测试板上装载的内存颗粒组合形成为多Rank颗粒组合,以模拟内存颗粒在实际使用情况下的负载,让多Rank重负载的测试成为可能。

测试环境设置模块,用于将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境;

其中,优选的,所述测试环境设置模块,具体包括:

在BIOS的配置中设置地址映射模式为交错映射模式(rank-interleaved));通过将地址映射模式设置为交错映射模式,CPU在进行内存访问时,能够同时打开多个Rank进行访问,从而造成内存颗粒动态的“重负载模式”。而如果不将地址映射模式设置为交错映射模式,CPU在进行内存访问时,依然会对Rank进行依次访问,从而无法形成内存颗粒的“重负载模式”。

错误颗粒获取模块,用于基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址。

进一步的,所述错误颗粒获取模块,具体包括:

Rank同时访问单元,用于根据所述多Rank颗粒的物理地址,对每一Rank颗粒同时进行访问;

Rank颗粒测试单元,用于在每一所述Rank颗粒中分别执行不同的测试算法,以对所述Rank颗粒进行ATE和/或SLT测试;

其中,作为一种可实现的实施的方式,所述在每一所述Rank颗粒中分别执行不同的测试算法可以是:例如,测试板上有两个Rank颗粒,分别为Rank0,Rank1,系统采用两个测试算法,分别为MarchC算法和DataRetention,则算法的执行流程如图4所示。

错误颗粒获取单元,用于根据所述交错映射模式对每一内存颗粒单元进行精确定位,以获取错误内存颗粒单元的物理地址。

进一步的,所述错误颗粒获取单元,具体包括:

线性地址获取子单元,用于获取错误内存颗粒单元的线性地址;

寄存器组的读取子单元,用于读取内存控制器的地址映射寄存器组;

其中,需要说明的是,所述地址映射寄存器中存储有线性地址相关位与Rank间的对应关系。

初步物理地址获取子单元,用于根据所述地址映射寄存器组的设置值,计算得出所述错误内存颗粒单元的Rank值,以得到所述错误内存颗粒单元的初步物理地址;

其中,作为一种可选的实现方式,在所述地址映射寄存器中读取线性地址(二进制)相关位(bit)与Rank间的对应关系,例如:线性地址的第6bit代表Rank位,以此获得该Rank位上对应的内存颗粒的物理地址。但值得注意的是,由于以多Rank颗粒组合形式运行,此时获取到物理地址的内存颗粒尚无法确定处于测试板哪一面上的Rank中,因此,需要进入最终物理地址获取子单元。

最终物理地址获取子单元,用于根据所述初步物理地址中的Rank信息,得到所述错误内存颗粒单元的最终物理地址。

其中,作为一种可选的实现方式,例如,在装载了两面Rank的情况下,根据内存颗粒物理地址的Rank信息,就能获知具体是哪一面上的Rank中的内存颗粒,并最终确定出错误内存颗粒单元。

本发明实施例通过在测试板两面的内存颗粒插槽中同时装载多个待测试内存颗粒,以使所述多个待测试内存颗粒以多Rank颗粒组合形式运行;将所述多Rank颗粒的测试环境设置为重负载模式下的测试环境;基于算法对所述多Rank颗粒进行ATE和/或SLT测试,并获取错误颗粒单元的物理地址;能够将“有负载才失效"、"内存颗粒互相干扰"等由于多Rank颗粒组合形式引起的问题在产品SMT(Surface Mounting Technology,表面组装技术)前筛选出来,提高了内存颗粒电性能负载压力测试的能力,进而提高了内存颗粒测试的效能。

实施例三

参见图7,本发明第三方面还提供一种内存颗粒多维测试系统,所述系统包括:测试控制模块以及如第一方面所述的内存颗粒多维测试装置,所述测试控制模块与所述内存颗粒多维测试装置信连接;所述测试控制模块用于进行内存颗粒测试参数的配置、构建测试模型以及测试过程控制;所述内存颗粒多维测试装置用于对所述内存颗粒进行性能测试并获取错误内存颗粒单元的物理地址。

实施例四

本发明第四方面还包括一种执行终端,所述执行终端包括依次通信连接的存储器、处理器和收发器,其中,所述存储器用于存储计算机程序,所述收发器用于收发信息,执行如上所述的内存颗粒多维测试方法。具体可以举例的是,所述存储器可以但不限于包括随机存取存储器(Random-Access Memory,RAM)、只读存储器(Read-Only Memory,ROM)、闪存(Flash Memory)、先进先出存储器(First Input First Output,FIFO)和/或先进后出存储器(First Input Last Output,FILO)等等;所述收发器可以但不限于为WiFi(无线保真)无线收发器、蓝牙无线收发器、GPRS(General Packet Radio Service,通用分组无线服务技术)无线收发器和/或ZigBee(紫蜂协议,基于IEEE802.15.4标准的低功耗局域网协议)无线收发器等;所述处理器可以不限于采用型号为STM32F105系列的微处理器。此外,所述执行终端还可以但不限于包括有电源模块、显示屏和其它必要的部件。

实施例五

本发明第五方面还提供一种可读存储介质,所述可读存储介质上存储有指令,当所述指令在计算机上运行时,执行如上述的内存颗粒多维测试方法。其中,所述可读存储介质是指存储数据的载体,可以但不限于包括软盘、光盘、硬盘、闪存、优盘和/或记忆棒(Memory Stick)等,所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。

其中,前述可读存储介质的工作过程、工作细节和技术效果,可以参见上述的商户高效进驻电商平台的方法,于此不再赘述。

实施例六

本实施例第六方面提供了一种包含指令的计算机程序产品,当所述指令在计算机上运行时,使所述计算机执行如上述的内存颗粒多维测试方法。其中,所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。

最后应说明的是,本发明不局限于上述可选的实施方式,任何人在本发明的启示下都可得出其他各种形式的产品。上述具体实施方式不应理解成对本发明的保护范围的限制,本发明的保护范围应当以权利要求书中界定的为准,并且说明书可以用于解释权利要求书。

- 一种内存颗粒多维测试方法、装置、系统和可读存储介质

- 一种业务系统测试方法、装置、电子设备和可读存储介质