半导体存储装置及其制造方法

文献发布时间:2023-06-19 12:24:27

[相关申请案]

本申请案享有以日本专利申请案2020-34068号(申请日:2020年2月28日)为基础申请案的优先权。本申请案通过参照该基础申请案而包含基础申请案的全部内容。

技术领域

本实施方式涉及一种半导体存储装置及其制造方法。

背景技术

近年来,开发了一种具有立体型存储单元阵列的半导体存储装置,所述立体型存储单元阵列是三维配置存储单元而成。这种半导体存储装置中,为了将选择栅极分割而在存储单元阵列的上部设有狭缝。

所述狭缝形成于绝缘层与导电层的积层膜、以及存储器孔内的柱状部。但,导电层及柱状部使用的是金属材料等不易进行蚀刻控制的材料。因此,为了将邻接的选择栅极充分地电分离而扩大狭缝底部的宽度时,狭缝的上部开口部会变得过大,且狭缝的深度会变得过深。这与存储单元阵列的小型化相悖。另外,蚀刻控制性较差导致了导电层与柱状部中的狭缝深度偏差。

另外,导电层及柱状部因为蚀刻控制性较差,所以狭缝内壁具有倾斜,狭缝底部逐渐变细。为了将位于逐渐变细的狭缝底部的选择栅极确实地分割,必须加深狭缝,并在某种程度上扩大狭缝底部的宽度。这样一来,狭缝的倾斜形状也会导致狭缝加深。如果狭缝较深,那么必须在积层体上准备多个虚设的导电层(虚设字线)。这也与存储单元阵列的小型化相悖。

发明内容

实施方式提供一种能够确实地将位于存储单元阵列上部的多个选择栅极分割,使存储单元阵列小型化的半导体存储装置及其制造方法。

本实施方式的半导体存储装置具备衬底。积层体设置在衬底的上方,是将多个第1绝缘层与多个导电层交替地积层而构成。多个柱状部贯通积层体而设置,包含设置在中心部的核心层、设置在核心层周围的半导体层、及设置在该半导体层周围的存储膜。狭缝将位于积层体上部的上部导电层分割。在与狭缝重叠的柱状部中,核心层或存储膜从半导体层突出。

附图说明

图1A是例示第1实施方式的半导体装置的示意立体图。

图1B是表示积层体的示意俯视图。

图2A是例示三维构造的存储单元的示意剖视图。

图2B是例示三维构造的存储单元的示意剖视图。

图3是例示第1实施方式的半导体存储装置的示意俯视图。

图4是更详细地表示图3的框B4的构成的俯视图。

图5是沿着图4的5-5线的剖视图。

图6是沿着图4的6-6线的剖视图。

图7~20是表示第1实施方式的半导体存储装置的制造方法的一例的剖视图。

具体实施方式

以下,参照附图对本发明的实施方式进行说明。本实施方式不限定本发明。以下实施方式中,半导体衬底的上下方向表示使设有半导体元件的一面朝上时的相对方向,与依据重力加速度的上下方向有时不同。附图是示意性或概念性的图,各部分的比率等未必与实物相同。说明书与附图中,对以上关于附图所描述的要素相同的要素附上相同符号并适当省略详细说明。

(第1实施方式)

图1A是例示第1实施方式的半导体存储装置100a的示意立体图。图1B是表示积层体2的示意俯视图。本说明书中,将积层体2的积层方向设为Z方向。将与Z方向交叉,例如正交的1个方向设为Y方向。将与Z及Y方向分别交叉,例如正交的1个方向设为X方向。图2A及图2B分别为例示三维构造的存储单元的示意剖视图。图3是例示第1实施方式的半导体存储装置100a的示意俯视图。

如图1A~图3所示,第1实施方式的半导体存储装置100a是具有三维构造的存储单元的非易失性存储器。

半导体存储装置100a包含基体部1、积层体2、深狭缝ST(板状部3)、浅狭缝SHE及多个柱状部CL。

基体部1包含衬底10、绝缘膜11、导电膜12及半导体部13。绝缘膜11设置在衬底10上。导电膜12设置在绝缘膜11上。半导体部13设置在导电膜12上。衬底10为半导体衬底,例如硅衬底。硅(Si)的导电型例如为p型。在衬底10的表面区域,例如设有元件分离区域10i。元件分离区域10i例如为包含氧化硅的绝缘区域,在衬底10的表面区域划分工作区域AA。在工作区域AA设有晶体管Tr的源极及漏极区域。晶体管Tr构成非易失性存储器的周边电路(CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)电路)。绝缘膜11例如包含氧化硅(SiO

积层体2设置在衬底10的上方,相对于半导体部13位于Z方向。积层体2是沿着Z方向将多个导电层21及多个绝缘层22交替地积层而构成。导电层21包含导电性金属,例如钨。绝缘层22例如包含氧化硅。绝缘层22使导电层21彼此绝缘。导电层21及绝缘层22各自的积层数是任意的。绝缘层22例如也可以是气隙。积层体2与半导体部13之间,例如设有绝缘膜2g。绝缘膜2g例如包含氧化硅(SiO

导电层21包含至少1个源极侧选择栅极SGS、多条字线WL及至少1个漏极侧选择栅极SGD。源极侧选择栅极SGS为源极侧选择晶体管STS的栅极电极。字线WL为存储单元MC的栅极电极。漏极侧选择栅极SGD为漏极侧选择晶体管STD的栅极电极。源极侧选择栅极SGS设置在积层体2的下部区域。漏极侧选择栅极SGD设置在积层体2的上部区域。下部区域是指积层体2的靠近基体部1侧的区域,上部区域是指积层体2的远离基体部1侧的区域。字线WL设置在源极侧选择栅极SGS与漏极侧选择栅极SGD之间。

多个绝缘层22中的将源极侧选择栅极SGS与字线WL绝缘的绝缘层22的Z方向的厚度例如可以比将字线WL与字线WL绝缘的绝缘层22的Z方向的厚度厚。进而,也可以在距基体部1最远的最上层的绝缘层22之上设置覆盖绝缘膜(未图示)。覆盖绝缘膜例如包含氧化硅。

半导体存储装置100a具有在源极侧选择晶体管STS与漏极侧选择晶体管STD之间串联连接的多个存储单元MC。源极侧选择晶体管STS、存储单元MC及漏极侧选择晶体管STD串联连接的构造被称作“存储器串”或“NAND(Not AND,与非)串”。存储器串例如经由接点Cb连接于位线BL。位线BL设置在积层体2的上方,在Y方向上延伸。

积层体2内分别设有多个深狭缝ST及多个浅狭缝SHE。深狭缝ST在X方向上延伸,从积层体2的上端贯通积层体2直到基体部1,且设置在积层体2内。板状部3设置在深狭缝ST内(图1B)。板状部3例如至少包含绝缘物。该绝缘物例如为氧化硅。板状部3通过绝缘物与积层体2电绝缘,且也可以包含与半导体部13电连接的导电物。浅狭缝SHE在X方向上延伸,从积层体2的上端设置到积层体2的中途。浅狭缝SHE内例如设有绝缘物4(图1B)。绝缘物4例如为氧化硅。

如图1B所示,积层体2包含阶梯部分2s及存储单元阵列2m。阶梯部分2s设置在积层体2的缘部。存储单元阵列2m由阶梯部分2s夹着或者包围。深狭缝ST从积层体2一端的阶梯部分2s,经过存储单元阵列2m,设置到积层体2另一端的阶梯部分2s。浅狭缝SHE至少设置在存储单元阵列2m。

如图3所示,存储单元阵列2m包含单元区域(Cell)及分接头区域(Tap)。阶梯部分2s包含阶梯区域(Staircase)(图3)。分接头区域例如设置在单元区域与阶梯区域之间。图3中虽未图示,但分接头区域也可以设置在单元区域彼此之间。阶梯区域是设有多条配线37a的区域。分接头区域是设有配线37b及37c的区域。配线37a~37c各自例如在Z方向上延伸。配线37a分别例如与导电层21电连接。配线37b例如与导电膜12电连接。配线37c例如与配线11a电连接。

图1B所示的由2个板状部3夹着的积层体2的部分被称作块(BLOCK)。块例如构成数据抹除的最小单位。绝缘物4设置在块内。板状部3与绝缘物4之间的积层体2被称作指状部。漏极侧选择栅极SGD被划分到每个指状部。因此,在数据写入及读出时,能够利用漏极侧选择栅极SGD使块内的1个指状部为选择状态。

多个柱状部CL分别设置在存储器孔MH内,所述存储器孔M设置在积层体2内。各柱状部CL沿着Z方向从积层体2的上端贯通积层体2,一直设置到积层体2内及半导体部13内。多个柱状部CL分别包含半导体主体210、存储膜220及核心层230。柱状部CL包含设置在其中心部的核心层230、设置在该核心层230周围的半导体主体210、及设置在该半导体主体210周围的存储膜220。半导体主体210与半导体部13电连接。存储膜220在半导体主体210与导电层21之间具有电荷捕获部。从各指状部分别逐一选择的多个柱状部CL经由接点Cb共通连接于1条位线BL。柱状部CL分别例如设置在单元区域(Cell)(图3)。

如图2A及图2B所示,X-Y平面中的存储器孔MH的形状例如为圆或椭圆。导电层21与绝缘层22之间也可以设有构成存储膜220的一部分的块绝缘膜21a。块绝缘膜21a例如为氧化硅膜或金属氧化物膜。金属氧化物的一例为氧化铝。导电层21与绝缘层22之间及导电层21与存储膜220之间也可以设有阻挡膜21b。例如导电层21为钨时,阻挡膜21b可选择例如氮化钛与钛的积层构造膜。块绝缘膜21a抑制电荷从导电层21向存储膜220侧的反向穿隧。阻挡膜21b使导电层21与块绝缘膜21a的密接性提高。

半导体主体210的形状例如为具有底的筒状。半导体主体210例如包含硅。硅例如为使非晶硅结晶化所得的多晶硅。半导体主体210例如为非掺杂硅。另外,半导体主体210也可以是p型硅。半导体主体210成为漏极侧选择晶体管STD、存储单元MC及源极侧选择晶体管STS各自的通道。

存储膜220的除块绝缘膜21a以外的部分设置在存储器孔MH的内壁与半导体主体210之间。存储膜220的形状例如为筒状。多个存储单元MC在半导体主体210与成为字线WL的导电层21之间具有存储区域,且在Z方向上积层。存储膜220例如包含覆盖绝缘膜221、电荷捕获膜222及隧道绝缘膜223。半导体主体210、电荷捕获膜222及隧道绝缘膜223各自在Z方向上延伸。

覆盖绝缘膜221设置在绝缘层22与电荷捕获膜222之间。覆盖绝缘膜221例如包含氧化硅。覆盖绝缘膜221是在将牺牲膜(未图示)替换成导电层21时(替换步骤),保护电荷捕获膜222不被蚀刻。覆盖绝缘膜221在替换步骤中,可以从导电层21与存储膜220之间去除。该情况下,如图2A及图2B所示,导电层21与电荷捕获膜222之间例如设有块绝缘膜21a。另外,在形成导电层21时未利用到替换步骤的情况下,也可以不要覆盖绝缘膜221。

电荷捕获膜222设置在块绝缘膜21a、及覆盖绝缘膜221与隧道绝缘膜223之间。电荷捕获膜222例如包含氮化硅,膜中具有捕获电荷的捕获部位。电荷捕获膜222中的夹在成为字线WL的导电层21与半导体主体210之间的部分作为电荷捕获部而构成存储单元MC的存储区域。存储单元MC的阈值电压是根据电荷捕获部中有无电荷、或电荷捕获部中所捕获的电荷的量而发生变化。由此,存储单元MC保持信息。

隧道绝缘膜223设置在半导体主体210与电荷捕获膜222之间。隧道绝缘膜223例如包含氧化硅、或氧化硅与氮化硅。隧道绝缘膜223是半导体主体210与电荷捕获膜222之间的电位障壁。例如在从半导体主体210向电荷捕获部注入电子时(写入动作)、及从半导体主体210向电荷捕获部注入电洞时(抹除动作),电子及电洞分别通过(隧穿过)隧道绝缘膜223的电位障壁。

核心层230埋入筒状半导体主体210的内部空间。核心层230的形状例如为柱状。核心层230例如包含氧化硅,且为绝缘性。

图3的多个柱状部CLHR分别设置在积层体2内所设有的孔HR内。孔HR沿着Z方向从积层体2的上端贯通积层体2,一直设置到积层体2内及半导体部13内。各柱状部CLHR至少包含绝缘物5。绝缘物5例如为氧化硅。另外,各柱状部CLHR也可以分别为与柱状部CL相同的构造。各柱状部CLHR例如设置在阶梯区域(Staircase)及分接头区域(Tap)。柱状部CLHR作为在将牺牲膜(未图示)替换成导电层21时(替换步骤),用来保持阶梯区域及分接头区域中所形成的空隙的支持部件发挥功能。在积层体2的分接头区域(Tap)、绝缘膜32及绝缘膜31内形成多个柱状部CLC4。各柱状部CLC4包含配线37c。配线37c通过绝缘物36c与积层体2电绝缘。配线37c与配线11a等任一配线电连接。

柱状部CL即存储器孔MH在平面布局中,以六方最密配置的方式配置在Y方向上邻接的2个狭缝ST间。如图4所示,浅狭缝SHE以重叠在一部分柱状部CL之上的方式设置。位于浅狭缝SHE之下的柱状部CL不构成存储单元。

图1A的半导体部13例如包含n型半导体层131、n型半导体层132、n型或非掺杂的半导体层133。半导体层131与导电膜12相接。半导体层132与半导体层131及半导体主体210分别相接。例如,半导体层132延伸到存储膜220被去除的部分,与半导体主体210相接。另外,半导体层132在X-Y平面中,以包围半导体主体210的方式设置。半导体层133与半导体层132相接。

半导体存储装置100a进而包含半导体部14。半导体部14位于积层体2与半导体部13之间。半导体部14包含半导体层134。半导体层134设置在绝缘层22中的最靠近半导体部13的绝缘层22b与绝缘膜2g之间。半导体层134的导电型例如为n型。半导体层134例如作为源极侧选择栅极SGS发挥功能。

图4是更详细地表示图3的框B4的构成的俯视图。图4中示出柱状部CL(即存储器孔MH)及浅狭缝SHE的配置关系。柱状部CL例如呈六方最密配置。浅狭缝SHE在X方向延伸,且设置成与排列在X方向的1列柱状部CL重叠。

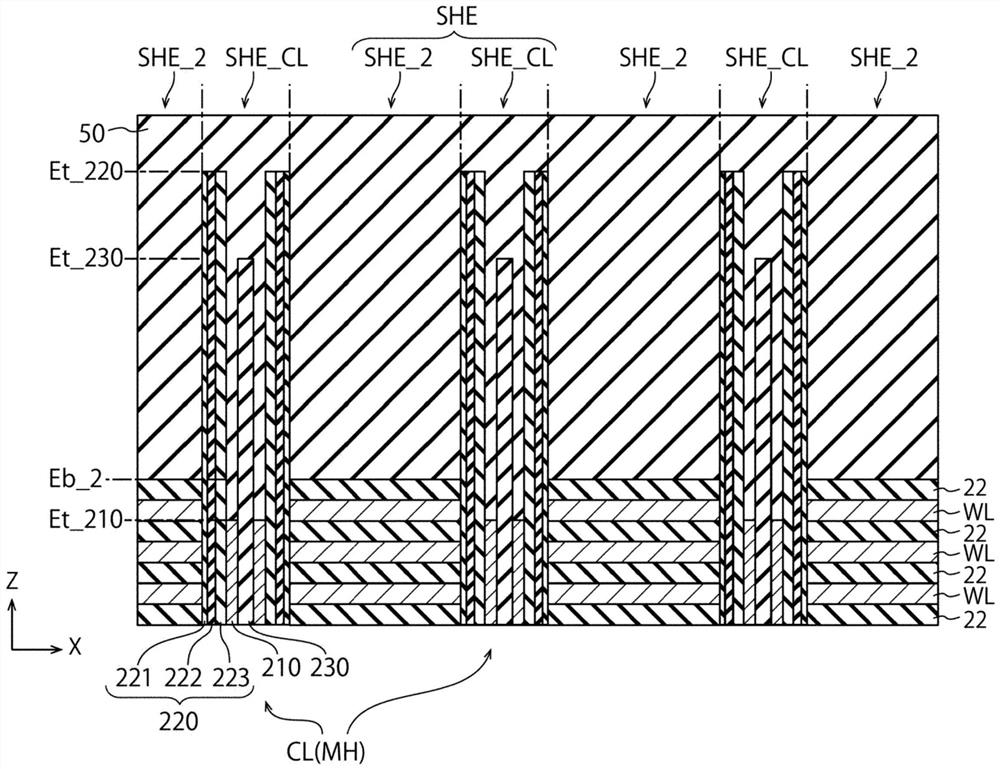

图5是沿着图4的5-5线的剖视图。图6是沿着图4的6-6线的剖视图。柱状部CL的基本构成如参照图2A及图2B所作说明。

如图5所示,狭缝SHE设置在积层体2的积层方向(Z方向),贯通积层体2中的位于上部的上部导电层(SGD0、SGD1、WLDD0)及上部绝缘层(22u)。上部导电层(SGD0、SGD1、WLDD0)中的SGD0、SGD1为漏极侧选择栅极。本实施方式中,积层体2的导电层21中的上部五层作为漏极侧选择栅极SGD0、SGD1发挥功能。WLDD0为虚设字线。虚设字线WLDD0具有与存储单元阵列的字线相同的构成,但不作为字线发挥功能,而设置作为狭缝SHE的蚀刻区域。因此,狭缝SHE的沟槽的蚀刻被控制为在虚设字线WLDD0的任一位置停止。本实施方式中,积层体2的导电层21中的漏极侧选择栅极SGD0、SGD1的正下方4层被设置作为虚设字线WLDD0。狭缝SHE设置到虚设字线WLDD0为止。狭缝SHE也随之贯通位于上部导电层(SGD0、SGD1、WLDD0)间的上部绝缘层22u。此外,漏极侧选择栅极的数量及虚设字线的数量无特别限定。

如图3及图4所示,狭缝SHE在X方向上连续地设置,且设置为将漏极侧选择栅极SGD0、SGD1分别于Y方向上分割。经狭缝SHE分割的一漏极侧选择栅极SGD0、SGD1与另一漏极侧选择栅极SGD0、SGD1分别对应于不同的指状部。例如,位于狭缝SHE右侧的漏极侧选择栅极SGD0、SGD1(以下,统称为SGD_R)对应于位于狭缝SHE右侧的多个柱状部(未图示),能够选择该指状部。即,与漏极侧选择栅极SGD_R对应的漏极侧选择晶体管成为导通状态后,会选择与之对应的指状部FNG。所选择的指状部FNG的柱状部CL连接于位线BL。另外,位于狭缝SHE左侧的漏极侧选择栅极SGD0、SGD1(以下,统称为SGD_L)与位于狭缝SHE左侧的多个柱状部CL对应,能够选择该指状部。即,与漏极侧选择栅极SGD_L对应的漏极侧选择晶体管成为导通状态后,会选择与之对应的指状部FNG。所选择的指状部FNG的柱状部CL连接于位线BL。此外,图5的柱状部CL是由漏极侧选择栅极SGD_L选择。

为了使Y方向上邻接的漏极侧选择栅极SGD_R与漏极侧选择栅极SGD_L不会因电容耦合而相互影响,狭缝SHE优选将各漏极侧选择栅极SGD0、SGD1以某种程度上较宽的宽度分割。即,漏极侧选择栅极SGD_R与漏极侧选择栅极SGD_L之间的间隔优选某种程度上扩大。

但,漏极侧选择栅极SGD0、SGD1及虚设字线WLDD0例如使用的是诸如钨等不易蚀刻的金属材料。因此,用来形成狭缝SHE的沟槽的蚀刻步骤耗费较长时间,并且狭缝SHE的内壁形成为倾斜状。由此,狭缝SHE的宽度在上部较宽,随着从上部接近底部而变窄。

通过使狭缝SHE的内壁成为倾斜状,狭缝SHE上部的宽度W0相对较宽,但底部宽度W1变窄。因此,位于上部的漏极侧选择栅极SGD0尽管因狭缝SHE而充分分离,仍担心下部的漏极侧选择栅极SGD1的分离宽度不充分。如果为了应对所述情况而进行过蚀刻以使狭缝SHE的底部的分割宽度变宽,那么狭缝SHE的沟槽的上部开口部会变得过宽,狭缝SHE的布局面积变大。这与存储单元阵列2m的小型化相悖。另外,如果对狭缝SHE的沟槽进行过蚀刻,那么狭缝SHE的沟槽的深度会变得过深,必须增加虚设字线的层数。这与存储单元阵列2m的小型化相悖。

进而,如图4所示,从积层体2的积层方向(Z方向)观察时,狭缝SHE重叠在积层体2及柱状部CL(存储器孔MH)上而形成。例如,当使用RIE(Reactive Ion Etching,反应性离子蚀刻)法等各向异性蚀刻同时形成积层体2上的狭缝SHE及柱状部CL上的狭缝SHE的沟槽时,狭缝SHE的深度因积层体2与柱状部CL的材质而异。狭缝SHE的深度偏差还是会牵涉到虚设字线的层数增加。

因此,本实施方式中,将狭缝SHE的形成步骤分成积层体2的蚀刻步骤(第1蚀刻步骤)与柱状部CL的蚀刻步骤(第2蚀刻步骤)。以下,如图6所示,为方便起见,将形成于积层体2的狭缝设为SHE_2,将形成于柱状部CL的狭缝设为SHE_CL。

在积层体2的第1蚀刻步骤中,使用RIE法等在积层体2中选择性地形成狭缝SHE_2的沟槽,在柱状部CL的第2蚀刻步骤中,利用湿式蚀刻选择性地对柱状部CL的半导体主体210进行蚀刻。在第2蚀刻步骤中,选择性地对半导体主体210进行蚀刻,保留柱状部CL中的存储膜220及核心层230。

第1蚀刻步骤与第2蚀刻步骤之间不进行光刻步骤,不变更掩模。由此,在第1及第2蚀刻步骤中,通过改变蚀刻方法而自对准地形成狭缝SHE_2、SHE_CL。

如图6所示,与狭缝SHE_CL重叠的柱状部CL中,存储膜220及核心层230虽某种程度上被蚀刻,但仍朝积层方向(Z方向)的上方从半导体主体210突出。换句话说,狭缝SHE_CL内的存储膜220的上端Et_220及核心层230的上端Et_230位于比狭缝SHE_CL内的半导体主体210的上端Et_210靠上方。因此,在狭缝SHE_CL内的柱状部CL中,存储膜220与核心层230之间被埋入绝缘膜50。在核心层230的周围及其上,设置绝缘膜50。即,狭缝SHE_CL内的半导体主体210的上部被替换成绝缘膜50。由此,半导体主体210虽连接于作为源极层发挥功能的导电膜12及半导体部13,但能够抑制读出动作等中的电荷进入狭缝SHE内的半导体主体210。

另外,与狭缝SHE_CL重叠的柱状部CL中,存储膜220的上端Et_220及核心层230的上端Et_230位于比积层体2的狭缝SHE_2的底部Eb_2靠上方。另一方面,狭缝SHE_CL内的半导体主体210的上端Et_210位于比设置在积层体2的狭缝SHE_2的底部Eb_2深的位置(下方)。即,本实施方式中,狭缝SHE_2、SHE_CL按照存储膜220区域、核心层230区域、积层体2区域、半导体主体210区域的顺序变深。

如图6所示,狭缝SHE_2、SHE_CL作为一体狭缝SHE在X方向上连续地设置。因此,狭缝SHE_2、SHE_CL内填充着相同绝缘膜50。即,参照图6可知,图5的柱状部CL内的绝缘膜50与狭缝SHE内的绝缘膜50为相同材料。绝缘膜50例如使用氧化硅膜等绝缘膜。

像这样,在本实施方式中,将狭缝SHE的形成步骤分成积层体2的蚀刻步骤与柱状部CL的蚀刻步骤这两个阶段,狭缝SHE_2与狭缝SHE_CL是利用不同的蚀刻方法进行蚀刻。由此,狭缝SHE_2及狭缝SHE_CL的蚀刻控制变得容易。例如,狭缝SHE_2及狭缝SHE_CL各自的深度控制变得容易。结果,得以抑制狭缝SHE_2或狭缝SHE_CL被蚀刻得过深。这种方法能够使狭缝SHE的开口宽度变窄,能够减小狭缝SHE的布局面积。另外,由于狭缝SHE_2或狭缝SHE_CL不会过深,所以也能够减少虚设字线的层数。结果,能实现存储单元阵列2m的小型化。

此外,虽未图示,但狭缝SHE可并非完全由绝缘膜50埋入。即,狭缝SHE内也可以存在空腔(孔隙)。

图7~图20是表示第1实施方式的半导体存储装置的制造方法的一例的剖视图。图7~图20对应于沿着图3的7-7线的剖面。

如图7所示,在衬底10内形成元件分离区域10i,在工作区域AA内形成晶体管Tr。然后,在衬底10上形成绝缘膜11。绝缘膜11例如为层间绝缘膜,包含配线11a。此外,配线11a例如为多层配线,图7中,例示配线11aa、及设置在配线11aa上方的配线11ab。然后,在配线11ab上形成绝缘膜11d。绝缘膜11d例如包含氧化硅。然后,在绝缘膜11d上形成导电膜12。

其次,如图8所示,在导电膜12上形成半导体层131。半导体层131例如包含n型掺杂硅。导电膜12及半导体部13可以设为一体的半导体部12、13。然后,在半导体层131上形成中间膜13a。中间膜13a例如包含氧化硅。然后,在中间膜13a上形成牺牲膜13b。牺牲膜13b例如包含n型掺杂硅或非掺杂硅。然后,在牺牲膜13b上形成中间膜13c。中间膜13c例如包含氧化硅。然后,在中间膜13c上形成半导体层133。半导体层133例如包含n型掺杂硅或非掺杂硅。由此,例如能获得制造过程中的基体部1的基础构造。

其次,在半导体层133及绝缘膜32上形成绝缘膜2g。绝缘膜2g例如包含氧化硅或金属氧化物。然后,在绝缘膜2g上形成半导体层134。半导体层134例如包含n型掺杂硅。由此,形成半导体部14。然后,在半导体层134上形成绝缘层22b。接着,在绝缘层22b上交替地积层牺牲膜23与绝缘层22。绝缘层22及22b例如分别包含氧化硅。牺牲膜23例如包含氮化硅。由此,能获得相对于半导体部13位于Z方向的制造过程中的积层体2的基础构造。

其次,虽未图示,但将绝缘层22及牺牲膜23加工成阶梯状,形成阶梯区域(Staircase)。另外,形成柱状部CLHR。

其次,如图9所示,在单元区域(Cell)中,对积层体2、半导体层134、绝缘膜2g、半导体层133、中间膜13c、牺牲膜13b、中间膜13a及半导体层131进行各向异性蚀刻,形成存储器孔MH。存储器孔MH从积层体2的上端形成到半导体层131的中途。此外,也可以经由存储器孔MH对半导体层134、绝缘膜2g、半导体层133、中间膜13c、牺牲膜13b、中间膜13a及半导体层131进行各向同性蚀刻,在对应于半导体部13的部分(例如半导体层131、牺牲膜13b及半导体层133)、以及对应于半导体部14的部分(例如半导体层134),扩大存储器孔MH的直径。

其次,如图10所示,在存储器孔MH内形成存储膜220。存储膜220包含氮化硅及氧化硅。然后,在存储膜220上形成半导体主体210。半导体主体210例如包含非掺杂硅或p型掺杂硅。然后,在半导体主体210上形成核心层230。核心层230例如包含氧化硅。由此,存储器孔MH由半导体主体210、存储膜220及核心层230埋入。

其次,如图11所示,对积层体2、半导体层134、绝缘膜2g、半导体层133、中间膜13c及牺牲膜13b进行各向异性蚀刻,形成深狭缝ST。深狭缝ST从积层体2的上端形成到牺牲膜13b的中途。

其次,如图12所示,在深狭缝ST的侧壁上形成终止膜3s。终止膜3s例如包含氮化硅。

其次,如图13所示,经由深狭缝ST对牺牲膜13b进行各向同性蚀刻,去除牺牲膜13b。在该各向同性蚀刻步骤中,例如与氧化硅及氮化硅相比,选择能够更快地蚀刻n型掺杂硅或非掺杂硅的蚀刻剂。由此,在中间膜13a与中间膜13c之间形成空间S1。进而,经由深狭缝ST,对存储膜220的覆盖绝缘膜221(图2A及图2B)进行各向同性蚀刻,去除覆盖绝缘膜221。在该各向同性蚀刻步骤中,例如与氮化硅相比,选择能够更快地蚀刻氧化硅的蚀刻剂。然后,经由深狭缝ST,对存储膜220的电荷捕获膜222(图2A及图2B)进行各向同性蚀刻,去除电荷捕获膜222。在该各向同性蚀刻步骤中,例如与氧化硅相比,选择能够更快地蚀刻氮化硅的蚀刻剂。然后,经由深狭缝ST,去除存储膜220的隧道绝缘膜223((图2A及图2B)。在该过程中,中间膜13a及中间膜13c也被去除。在该各向同性蚀刻步骤中,例如与氮化硅相比,选择能够更快地蚀刻氧化硅的蚀刻剂。由此,空间S1扩大到半导体层131与半导体层133之间,在柱状部CL中,半导体主体210露出到空间S1。半导体主体210露出的部位成为接触部位210c。

其次,如图14所示,经由深狭缝ST,以半导体埋入空间S1内,形成半导体层132。半导体层132例如为n型掺杂硅。

其次,如图15所示,经由深狭缝ST,对终止膜3s及牺牲膜23进行各向同性蚀刻,去除终止膜3s及牺牲膜23。由此,在绝缘层22间形成空间S2。在该各向同性蚀刻步骤中,例如与氧化硅及多晶硅相比,选择能够更快地蚀刻氮化硅的蚀刻剂。

其次,如图16所示,经由深狭缝ST,以导电物埋入空间S2内,形成导电层21。导电层21例如包含钨。

其次,如图17所示,以绝缘物埋入深狭缝ST,形成板状部3。板状部3例如包含氧化硅。

其次,如图18所示,堆积绝缘膜后,为了形成浅狭缝SHE而在积层体2的积层方向(Z方向)上,对与位于积层体2上部的上部导电层(图5的SGD0、SGD1、WLDD0)对应的导电层21及绝缘层22进行蚀刻。狭缝SHE例如以贯通图5的上部导电层SGD0、SGD1、虚设字线WLDD0的方式形成。此时,不仅对绝缘层22进行蚀刻,也对包含钨等金属材料的导电层21进行蚀刻,因此,如图18所示,狭缝SHE以其宽度随着接近底部而变窄的方式具有倾斜。

此处,更详细地说明狭缝SHE的形成步骤。

图19~图20是更详细地说明狭缝SHE的形成步骤的剖视图。图19~图20表示与图6对应的剖面,对应于沿着图18的19-19线的剖面。

首先,使用光刻技术,利用抗蚀剂(未图示)被覆狭缝SHE以外的区域,使抗蚀剂成形为狭缝SHE的图案。其次,将抗蚀剂作为掩模,使硬掩模HM图案化。

其次,如图19所示,使用硬掩模HM作为掩模,利用RIE法等对位于积层体2上部的上部导电层(SGD0、SGD14、WLDD0)进行各向异性蚀刻,形成狭缝SHE_2的沟槽TR_2(第1蚀刻步骤)。此时,蚀刻气体例如使用的是氯系与氟系的混合气体。例如,上部导电层(例如钨)是在提高氯系气体的混合比率后进行蚀刻,绝缘层22(例如氧化硅膜)是在提高氟系气体的混合比后进行蚀刻。由此,能够选择性地对上部导电层及它们之间的绝缘层22进行蚀刻。半导体主体210(例如多晶硅)虽然在加工狭缝SHE_2时能稍许去除,但仍会残留到比狭缝SHE_2的底高的位置。即,本实施方式中,不使用将积层体2及柱状部CL这两者蚀刻的气体(例如仅氯系气体),而使用选择性地对积层体2进行蚀刻的气体(例如氯系与氟系的混合气体)。由此,如图19所示,狭缝SHE_2的沟槽TR_2形成得较深,狭缝SHE_CL的沟槽TR_CL形成得较浅,到半导体主体210为止。

其次,如图20所示,使用同一硬掩模HM作为掩模,利用湿式蚀刻法对柱状部CL内的半导体主体210各向同性地进行蚀刻(第2蚀刻步骤)。由此,狭缝SHE_CL的沟槽TR_CL在半导体主体210这一部分被选择性地蚀刻得较深。相反,核心层230及存储膜220未被蚀刻太多,而从半导体主体210朝Z方向突出。蚀刻液例如使用的是DHF(DilutedHydrofluoric Acid,稀氢氟酸)及TMY(三甲基-2羟乙基氢氧化铵)。能够利用该蚀刻液选择性地对半导体主体210(例如多晶硅)进行蚀刻。

另外,半导体主体210的蚀刻进行到与狭缝SHE_2的底相同程度或从狭缝SHE_2到位于其下的字线WL的深度。

此外,在第1及第2蚀刻步骤中,使用相同掩模执行蚀刻。即,在形成使狭缝SHE_2、SHE_CL这两者露出的硬掩模HM后,不变更硬掩模HM而继续执行第1及第2蚀刻步骤。在第1蚀刻步骤中,利用RIE法各向异性地进行蚀刻,利用蚀刻气体选择性地对积层体2进行蚀刻。在第2蚀刻步骤中,利用湿式蚀刻各向同性地对半导体主体210进行选择性蚀刻。由此,在第1及第2蚀刻步骤中,也能够使用相同掩模,控制性良好地对积层体2或半导体主体210进行蚀刻。狭缝SHE能够偏差较少且自对准地形成。

其次,将绝缘膜50埋入沟槽TR_CL、TR_2。由此,如图6所示,形成狭缝SHE_CL、SHE_2。

之后,虽未图示,但按照周知的方法,在积层体2的上方形成层间绝缘膜、接触插塞及位线BL等。由此,完成图1A所示的半导体存储装置100a。

像这样,根据本实施方式,将狭缝SHE的形成步骤分成积层体2的第1蚀刻步骤与柱状部CL的第2蚀刻步骤这两个阶段,狭缝SHE_2与狭缝SHE_CL是使用相同掩模,利用不同蚀刻方法形成。由此,容易控制狭缝SHE_2及狭缝SHE_CL各自的蚀刻。结果,得以抑制狭缝SHE_2或狭缝SHE_CL被蚀刻得过深。这种方法能够使狭缝SHE的开口宽度变窄,能够减小狭缝SHE的布局面积。另外,由于狭缝SHE_2或狭缝SHE_CL不会过深,所以也能够减少虚设字线的层数。结果,能实现存储单元阵列2m的小型化。

对本发明的若干个实施方式进行了说明,但这些实施方式是作为例子提出的,并不意图限定发明的范围。这些实施方式能以其它各种方式实施,能在不脱离发明主旨的范围内进行各种省略、替换、变更。这些实施方式及其变化包含在发明的范围或主旨中,且同样包含在权利要求书所记载的发明及其均等的范围内。

[符号的说明]

2 积层体

CL 柱状部

SHE 狭缝

SGD0、SGD1 漏极侧选择栅极

WLDD0 虚设字线

22、22u 绝缘层

50 绝缘膜

210 半导体主体

220 存储膜

230 核心层。

- 制造半导体存储装置的方法及用该方法制造的半导体存储装置

- 存储元件、半导体存储装置、存储元件的制造方法及半导体存储装置的读出方法