一种SPI NOR及NAND闪存传输模式识别方法

文献发布时间:2023-06-19 12:24:27

技术领域

本发明涉及闪存传输技术领域,具体是一种SPI NOR及NAND闪存传输模式识别方法。

背景技术

SPI NOR及SPI NAND Flash芯片只有8个引脚,因此占用的CPU引脚少,占用PCB面积也少,是当今嵌入式系统广泛采用的存储芯片。其生产厂商众多,规格也各式各样。由于采用SPI传输,标准SPI模式输入输出各只有一个引脚,因此传输速率并不高,没有使用多引脚传输的并行NOR/NAND Flash速度快。为了克服标准SPI传输模式速率慢的限制,各厂商在原基础上通过复用SI,SO,WP和HOLD引脚,新增了双线传输,及四线传输模式。因此传输速率可以得到2倍/4倍的提高。如图1所示的SPI NOR/NAND Flash的引脚图。

其中VCC和GND用于供电。CS#为芯片选择引脚。SCLK为SPI时钟信号。SI为标准SPI单线模式下的输入信号,SO为标准SPI单线模式下的输出信号。SIO0和SIO1为双线模式下的输入输出信号,SIO0-SIO3为四线模式下的输入输出信号,WP#和HOLD#为单线和双线模式下的写保护和挂起功能引脚。

通常嵌入式系统代码如果需要支持一颗新的Flash,则需要根据厂商提供的器件手册来编写代码,首先读取厂商及器件标识,根据标识来判断芯片支持那种传输模式。最终通过更新固件版本的方式来支持这一新Flash。此种方式不利于产品软件版本的管控,每增加一种新的Flash就要重新发布版本。为了减少版本的发布,更多的做法是内置一套默认的参数以标准SPI传输模式来支持未知Flash。但标准SPI模式,无法利用多线传输模式来达到Flash的最大传输速度,从而导致系统启动变慢,响应慢等问题

发明内容

本发明的目的在于提供一种SPI NOR及NAND闪存传输模式识别方法,利用各厂商间通用的2线/4线传输命令,通过特定代码判断逻辑来识别芯片支持那种传输模式,达到自动适配Flash芯片传输模式,以解决上述背景技术中提出的问题。

为实现上述目的,本发明提供如下技术方案:

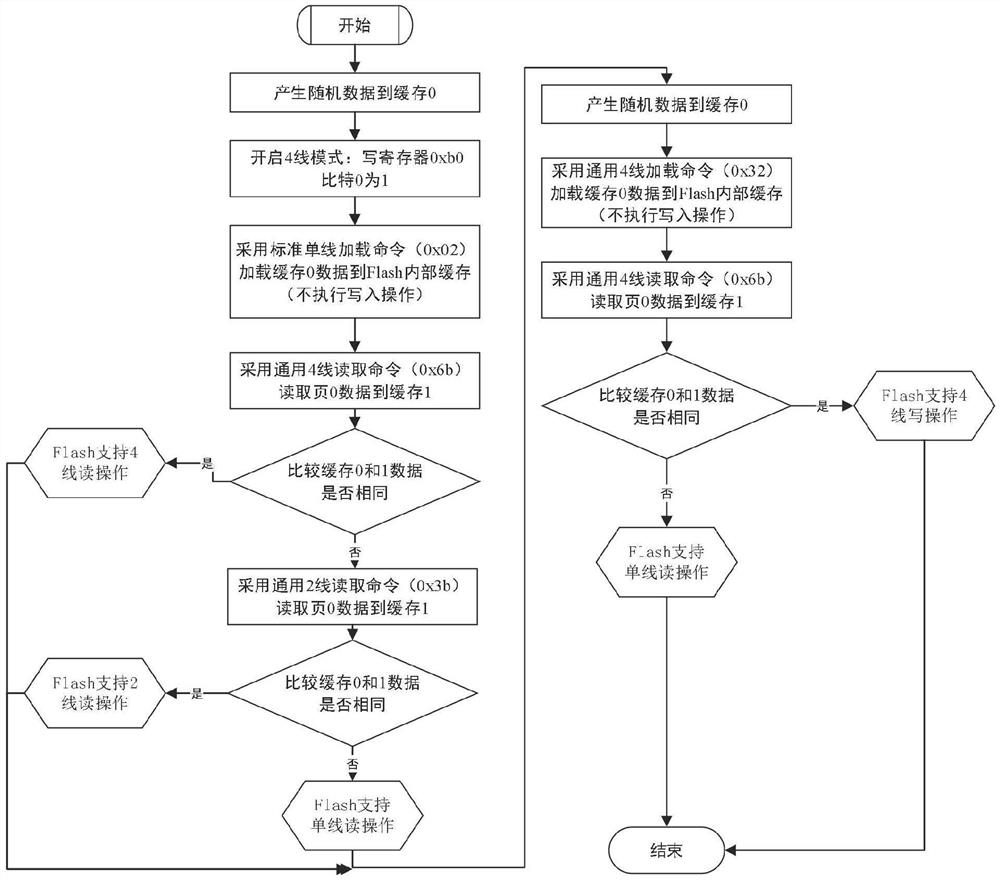

一种SPI NAND闪存传输模式识别方法,其具体识别步骤如下:

步骤1:需要开启SPI NAND flash的4线模式;4线模式开启后;Flash的WP和HOLD引脚用于4线传输中的IO2和IO3;目前各厂家都采用了功能寄存器(Feature Register)0xb0的第0位作为四线的开启位;

步骤2:产生随机数到缓存0;

步骤3:使用标准SPI单线模式加载命令(0x02)加载缓存0数据到Flash内部写缓存;不使用写操作以防破坏Flash内容;

步骤4:使用通用4线读命令(0x6b)读取页0数据到缓存1;

步骤5:比较缓存0和1内容是否相同,如果相同则代表Flash支持4线读操作;跳到步骤8继续执行;

步骤6:使用通用2线读命令(0x3b)读取页0数据到缓存1;

步骤7:比较缓存0和1内容是否相同,如果相同则代表Flash支持2线读操作。否则Flash仅支持单线读操作;

步骤8:产生随机数据到缓存0;

步骤9:使用通用4线加载命令(0x32)加载缓存0数据到Flash内部缓存,不执行写入操作;这样不会破坏Flash里数据内容;

步骤10:使用通用4线读命令(0x6b)读取页0数据到缓存1(通常支持4线写操作的Flash必定支持4线读操作,因此此步采用4线读命令而非标准单线读命令);

步骤11:比较缓存0和1内容是否相同,如果相同代表Flash支持4线写入操作;否则Flash仅支持单线写入操作。

此外,因目前Flash均没有2线写入的功能,因此不再判断。

一种SPI NOR闪存传输模式识别方法,其具体识别步骤如下:

步骤1:需要开启SPI NOR Flash的4线模式;4线模式开启后,Flash的WP和HOLD引脚用于4线传输中的IO2和IO3;有的厂家不需要特定命令,有的需要发送通用命令0xb7;

步骤2:使用标准SPI单线模式读命令(0x0b)读取flash特定地址内容到缓存0;

步骤3:使用通用4线读命令(0x6b)读取页0数据到缓存1;

步骤4:比较缓存0和1内容是否相同,如果相同则代表Flash支持4线读操作;跳到步骤7继续执行;

步骤5:使用通用2线读命令(0x3b)读取页0数据到缓存1;

步骤6:比较缓存0和1内容是否相同,如果相同则代表Flash支持2线读操作;否则Flash仅支持单线读操作;

步骤7:由于SPI Nor Flash没有内部缓存用于加载数据,要实现自动识别写入是否支持4线需要实际写入数据才能判断;因此需要找一块没有使用的数据块用于测试,因此此步需要判断是否有空余数据块用于测试,如果有则可继续测试,否则只能按照单线写来识别;

步骤8:擦除特定地址数据块;

步骤9:产生随机数据到缓存0;

步骤10:使用通用4线写命令(0x32)写缓存0数据到Flash内部缓存;

步骤11:使用通用4线读命令(0x6b)读取页0数据到缓存1(通常支持4线写操作的Flash必定支持4线读操作,因此此步采用4线读命令而非标准单线读命令);

步骤12:比较缓存0和1内容是否相同,如果相同代表Flash支持4线写入操作;否则Flash仅支持单线写入操作。

与现有技术相比,本发明的优点是:

1.可以自动识别所有SPI NOR/NAND Flash所支持的传输模式。

2.即可不用变更软件版本来支持未知新Flash,亦可以最大化发挥Flash的性能。

附图说明

图1为SPI NOR/NAND Flash引脚图。

图2为本发明中SPI NAND Flash自动识别流程图。

图3为本发明中SPI NOR Flash自动识别流程图。

具体实施方式

下面结合具体实施方式对本专利的技术方案作进一步详细地说明。

请参阅图2,一种SPI NOR及NAND闪存传输模式识别方法,其具体识别步骤如下:

步骤1:需要开启SPI NAND flash的4线模式;4线模式开启后;Flash的WP和HOLD引脚用于4线传输中的IO2和IO3;目前各厂家都采用了功能寄存器(Feature Register)0xb0的第0位作为四线的开启位。

步骤2:产生随机数到缓存0。

步骤3:使用标准SPI单线模式加载命令(0x02)加载缓存0数据到Flash内部写缓存;不使用写操作以防破坏Flash内容。

步骤4:使用通用4线读命令(0x6b)读取页0数据到缓存1。

步骤5:比较缓存0和1内容是否相同,如果相同则代表Flash支持4线读操作;跳到步骤8继续执行。

步骤6:使用通用2线读命令(0x3b)读取页0数据到缓存1。

步骤7:比较缓存0和1内容是否相同,如果相同则代表Flash支持2线读操作。否则Flash仅支持单线读操作。

步骤8:产生随机数据到缓存0

步骤9:使用通用4线加载命令(0x32)加载缓存0数据到Flash内部缓存,不执行写入操作;这样不会破坏Flash里数据内容。

步骤10:使用通用4线读命令(0x6b)读取页0数据到缓存1(通常支持4线写操作的Flash必定支持4线读操作,因此此步采用4线读命令而非标准单线读命令)。

步骤11:比较缓存0和1内容是否相同,如果相同代表Flash支持4线写入操作;否则Flash仅支持单线写入操作。

此外,因目前Flash均没有2线写入的功能,因此不再判断。

一种SPI NOR闪存传输模式识别方法,其具体识别步骤如下:

步骤1:需要开启SPI NOR Flash的4线模式;4线模式开启后,Flash的WP和HOLD引脚用于4线传输中的IO2和IO3;有的厂家不需要特定命令,有的需要发送通用命令0xb7;

步骤2:使用标准SPI单线模式读命令(0x0b)读取flash特定地址内容到缓存0;

步骤3:使用通用4线读命令(0x6b)读取页0数据到缓存1;

步骤4:比较缓存0和1内容是否相同,如果相同则代表Flash支持4线读操作;跳到步骤7继续执行;

步骤5:使用通用2线读命令(0x3b)读取页0数据到缓存1;

步骤6:比较缓存0和1内容是否相同,如果相同则代表Flash支持2线读操作;否则Flash仅支持单线读操作;

步骤7:由于SPI NOR Flash没有内部缓存用于加载数据。要实现自动识别写入是否支持4线需要实际写入数据才能判断;因此需要找一块没有使用的数据块用于测试,因此此步需要判断是否有空余数据块用于测试,如果有则可继续测试,否则只能按照单线写来识别;

步骤8:擦除特定地址数据块;

步骤9:产生随机数据到缓存0;

步骤10:使用通用4线写命令(0x32)写缓存0数据到Flash内部缓存。

步骤11:使用通用4线读命令(0x6b)读取页0数据到缓存1(通常支持4线写操作的Flash必定支持4线读操作,因此此步采用4线读命令而非标准单线读命令);

步骤12:比较缓存0和1内容是否相同,如果相同代表Flash支持4线写入操作;否则Flash仅支持单线写入操作。

上面对本专利的较佳实施方式作了详细说明,但是本专利并不限于上述实施方式,在本领域的普通技术人员所具备的知识范围内,还可以在不脱离本专利宗旨的前提下作出各种变化。

- 一种SPI NOR及NAND闪存传输模式识别方法

- 一种下行传输模式识别方法及系统