用于集成电路时序设计中的自动修正系统及方法

文献发布时间:2023-06-19 13:26:15

技术领域

本发明涉及半导体芯片技术领域,具体涉及一种用于集成电路时序设计中的自动修正系统及方法。

背景技术

数字物理设计在整个芯片设计中占据了很大的比重,数字物理设计流程复杂、环节长。

随着芯片规模的越来越大,对数字物理设计的要求也越来越高。通常,在数字物理设计时,需要进行ECO(Engineer Changing Order)不断迭代进行修复设计中所存在的问题。其中,端口最大负载以及端口信号转换时间是逻辑收敛的重要目标,端口最大负载以及端口信号转换时间违约会造成该级时序不准确,影响建立时间和保持时间的准确性,从而使电路不能正常工作。

通常解决这类违约的手段一般是,根据报告手动进行修复。当面对违约数目较大时,手动修复效率较低,且设计人员容易误操作增大修复难度。

现今EDA软件如ICC2(IC Compiler 2)、FC(Fusion Compiler)等在数字物理设计阶段,并不能完全解决端口最大负载以及端口信号转换时间违约问题,并且对ECO支持方面有欠缺。

发明内容

针对现有技术的不足,本发明公开了一种用于集成电路时序设计中的自动修正系统及方法,用于精确快速修复端口最大负载以及端口信号转换时间违约,进而减少设计人员手动操作,加速逻辑收敛,提高物理设计的效率与准确性。

本发明通过以下技术方案予以实现:

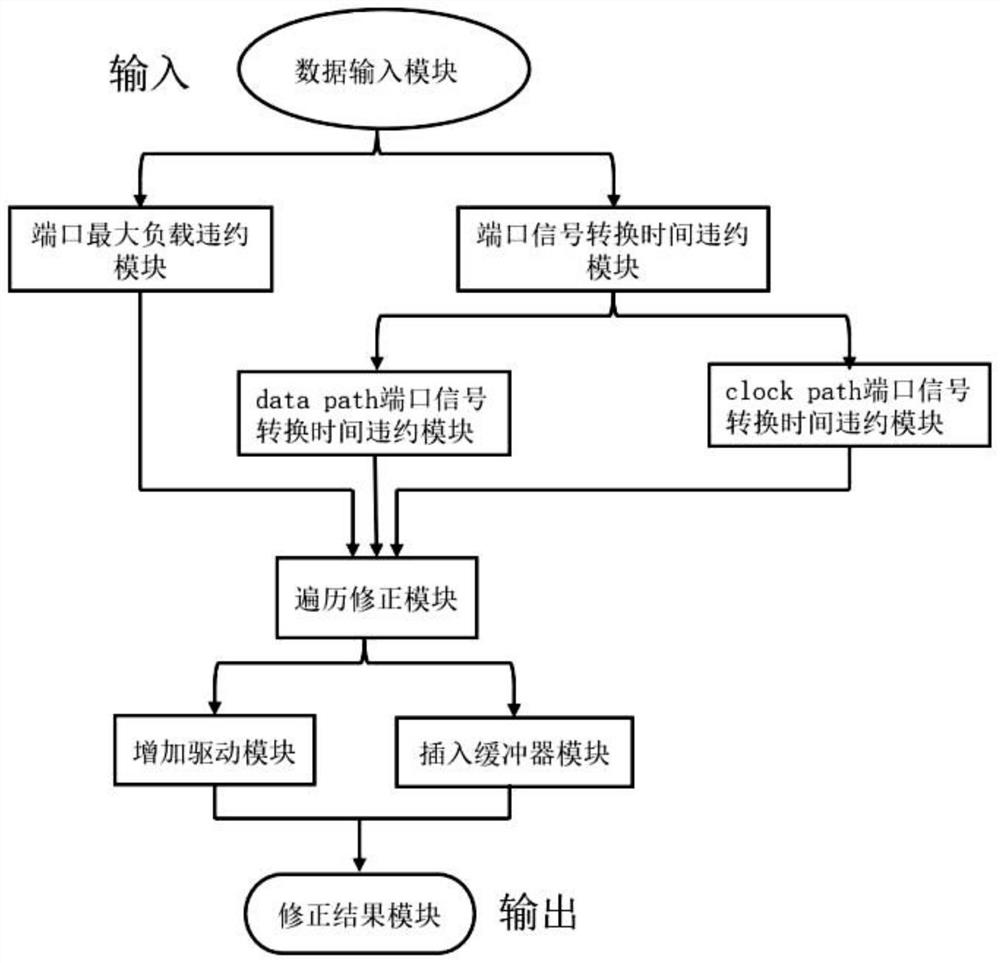

第一方面,本发明提供一种用于集成电路时序设计中的自动修正系统,包括:

数据输入模块,用于提供端口最大负载或端口信号转换时间违约端口的全称和违约端口的裕量参数,并通过选择违约模块类型进行违约分类修复;

遍历修正模块,用于精确获得所述数据输入模块输入的端口相关驱动、互联线、负载及物理位置的实际信息,并将该实际信息进行实时显示;

修正模块,用于根据所述遍历修正模块获得的实际信息,选择通过正则匹配进行增大驱动修复或调用EDA工具修复命令在指定位置处插入缓冲器修复;

修正结果模块,用于将所述修正模块修复的违约数据进行详细输出。

更进一步的,所述数据输入模块通过选择违约模块类型进行违约分类修复时,当选择端口信号转换时间违约模块,将数据输入模块中端口信号转换时间违约端口分为datapath上端口和clock path上两种类型端口并分别导入到data path端口信号转换时间违约模块和clock path端口信号转换时间违约模块中后进入遍历修正模块。

更进一步的,所述数据输入模块通过选择违约模块类型进行违约分类修复时,当选择端口最大负载违约模块,则将数据输入模块中端口最大负载违约端口以及裕量进行处理并导入到本模块中后进入遍历修正模块。

更进一步的,所述修正模块根据遍历修正模块显示精确实时数据信息,选用最优解决方式,当选用增加驱动模块进行修复时,通过正则匹配进行增大驱动。

更进一步的,所述修正模块根据遍历修正模块显示精确实时数据信息,选用最优解决方式,当选用插入缓冲器模块进行修复时,调用EDA工具修复命令在指定位置处插入缓冲器进行修复。

第二方面,本发明提供一种用于集成电路时序设计中的自动修正方法,所述方法使用第一方面所述的用于集成电路时序设计中的自动修正系统,包括以下步骤:

S1将数据模块中的违约端口全称和裕量分类到端口最大负载违约模块和端口信号转换时间违约模块;

S2根据数据或时钟违约类型,将端口信号转换时间违约端口违约信息送入datapath端口信号转换时间违约模块或clock path端口信号转换时间违约模块;

S3遍历端口最大负载违约模块,data path端口信号转换时间违约模块和clockpath端口信号转换时间违约模块中的违约信息;

S4将违约信息经过增加驱动模块和插入缓冲器模块的修正,输出到修正结果模块。

更进一步的,所述方法通过遍历违约端口,精确获得端口相关驱动、互联线、负载、物理位置等实际信息并实时显示出来。

更进一步的,所述方法对遍历修正模块输出信息用增加驱动模块进行正则匹配进行增大驱动修复或用插入缓冲器模块调用EDA工具修复命令在指定位置处插入缓冲器进行修复。

更进一步的,所述方法分别遍历端口最大负载违约模块、data path端口信号转换时间违约模块或clock path端口信号转换时间违约模块中违约端口,抓取与引脚相关驱动、互联线、负载等信息并输出。

更进一步的,所述方法采用TCL处理逻辑部分并用TK图形化交互界面

本发明的有益效果为:

本发明基于EDA软件的初始设置,与EDA软件相结合,可精确快速修复端口最大负载以及端口信号转换时间违约,且仅需提供违约端口和裕量两个参数,可批量进行修复,大大提高了修复效率,减少了手动操作,提高了修复可靠性,同时,节约芯片设计时间,使芯片更具竞争力。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是本发明用于集成电路时序设计中的自动修正系统的原理图;

图2是本发明实施例模块图形化界面图;

图3是本发明实施例修复前违约端口全称以及裕量图;

图4是本发明实施例EDA软件高亮标记图;

图5是本发明实施例EDA软件对话框显示信息图;

图6是本发明实施例修复后违约端口全称以及裕量。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例1

参照图1所示,本实施例提供一种用于集成电路时序设计中的自动修正系统,包括:

数据输入模块,用于提供端口最大负载或端口信号转换时间违约端口的全称和违约端口的裕量参数,并通过选择违约模块类型进行违约分类修复;

遍历修正模块,用于精确获得所述数据输入模块输入的端口相关驱动、互联线、负载及物理位置的实际信息,并将该实际信息进行实时显示;

修正模块,用于根据所述遍历修正模块获得的实际信息,选择通过正则匹配进行增大驱动修复或调用EDA工具修复命令在指定位置处插入缓冲器修复;

修正结果模块,用于将所述修正模块修复的违约数据进行详细输出。

本实施例中,首先,数据输入模块提供端口最大负载或端口信号转换时间违约端口的全称、违约端口的裕量两个参数。随后,通过图形化按钮进行选择违约模块。

本实施例中,当选择端口信号转换时间模块,将端口分为data path上端口和clock path上端口两种类型后进入遍历修正模块;当选择端口最大负载违约模块,将数据输入模块中端口最大负载违约端口以及裕量进行处理并导入到本模块中。

接着,本实施例执行遍历修正模块,精确获得引脚相关驱动、互联线、负载实际信息。根据遍历修正模块显示精确实时数据信息,选用最优解决方式。

当选用增加驱动模块进行修复时,通过正则匹配进行增大驱动。当选用插入缓冲器模块进行修复时,调用EDA工具修复命令在指定位置处插入缓冲器进行修复。

本实施例逻辑处理部分使用TCL语言进行编写以实现其功能,图形化交互界面使用TK进行编写。

本实施例解决了端口最大负载或端口信号转换时间违约,仅需提供违约端口和裕量两个参数,可批量进行修复,大大提高了修复效率,减少了手动操作,提高了修复可靠性。

实施例2

在具体实施层面,本实施例提供一种Linux系统的具体实施,首先,在Linux系统工作目录下启动FC工具,在FC对话框中读取修复程序源文件。此时,修复模块图形化交互界面显示出来,如图2所示。

将实例中端口信号转换时间违约的端口全称以及对应裕量放入到当前工作目录中show_drv/trans.tcl文件中。

如图3所示。先点击图形化界面split trans按钮进入端口信号转换时间违约模块对端口信号转换时间违约的端口进行分类,然后点击ck_trans按钮进入clock path端口信号转换时间违约模块或点击data_trans按钮进入data path端口信号转换时间违约模块,接着进入遍历修正模块进行修复。

本实施例以引脚scrypt_top/salsa_mem_wrapper_1/COM_OPT_COM_OPT_ctmTdsLR_1_473769/A1为例进行修复方法说明。

本实施例中当点击图形化界面split trans按钮进入端口信号转换时间违约模块后,该引脚被分为data path类型端口,随后我们点击data_trans按钮进入data path端口信号转换时间违约模块,接着我们点击Next按钮进入遍历修正模块。

本实施例中,当遍历到此引脚时,FC显示出违约端口所关联的驱动(红色高亮)、互联线(黄色高亮)、负载(绿色高亮)物理信息,软件对话框显示驱动大小、负载数目、互联线、裕量,如图4、图5所示。

本实施例中,根据FC对话框显示信息以及FC高亮显示,发现违约原因互联线过长,选用进入插入缓冲器模块进行修复,对缓冲器插入点进行选择如图5所示,选中互联线附近任意标准单元,随后点击add_buf_user按钮进行修复。

本实施例中,修复之后端口信号转换时间违约的端口的报告如图6所示,该违约引脚scrypt_top/salsa_mem_wrapper_1/COM_OPT_COM_OPT_ctmTdsLR_1_473769/A1已被成功修复。

实施例3

本实施例提供一种用于集成电路时序设计中的自动修正方法,包括以下步骤:

S1将数据模块中的违约端口全称和裕量分类到端口最大负载违约模块和端口信号转换时间违约模块;

S2根据数据或时钟违约类型,将端口信号转换时间违约端口违约信息送入datapath端口信号转换时间违约模块或clock path端口信号转换时间违约模块;

S3遍历端口最大负载违约模块,data path端口信号转换时间违约模块和clockpath端口信号转换时间违约模块中的违约信息;

S4将违约信息经过增加驱动模块和插入缓冲器模块的修正,输出到修正结果模块。

本实施例通过遍历违约端口,精确获得端口相关驱动、互联线、负载、物理位置等实际信息并实时显示出来。本实施例采用TCL处理逻辑部分并用TK图形化交互界面。

本实施例对遍历修正模块输出信息用增加驱动模块进行正则匹配进行增大驱动修复或用插入缓冲器模块调用EDA工具修复命令在指定位置处插入缓冲器进行修复。

本实施例分别遍历端口最大负载违约模块、data path端口信号转换时间违约模块或clock path端口信号转换时间违约模块中违约端口,抓取与引脚相关驱动、互联线、负载等信息并输出。

综上,本发明基于EDA软件的初始设置,与EDA软件相结合,可精确快速修复端口最大负载以及端口信号转换时间违约,且仅需提供违约端口和裕量两个参数,可批量进行修复,大大提高了修复效率,减少了手动操作,提高了修复可靠性,同时,节约芯片设计时间,使芯片更具竞争力。

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

- 用于集成电路时序设计中的自动修正系统及方法

- 用于电路设计中的静态时序分析的方法和系统