信号端口的静电浪涌防护电路及电子设备

文献发布时间:2023-06-19 13:45:04

技术领域

本发明实施例涉及保护电路技术领域,尤其涉及一种信号端口的静电浪涌防护电路及电子设备。

背景技术

电子设备与外部设备的有线通信是通过电子设备内置集成电路芯片(IntegratedCircuit,IC)的信号端口建立连接,例如通过IO口(输入输出端口)建立连接。信号端口若暴露在电子设备的外部,容易遭受来自人体等带电体的ESD(Electro-Static Discharge,静电放电)与浪涌冲击,存在损坏集成电路芯片的风险。因此,需要对集成电路芯片的信号端口进行静电浪涌防护。

现有技术中,静电浪涌防护电路作为由浪涌或静电引起的尖峰电压的泄放模块,通常与集成电路芯片为并联关系;但浪涌或静电带来的干扰信号通常是瞬时作用,若防护电路不能及时响应,该瞬时尖峰还是会施加在集成电路芯片的信号端口,影响防护效果。即使防护电路中包含串联在信号发送端与集成电路芯片的信号端口之间的部分,由于传输至信号端口的信号必须满足信号端口的电压门限值才能被正确识别,为了减小输入信号在防护电路中的衰减,该串联部分的阻抗也不能设置的太高。那么,总体而言,信号输出端口与集成电路芯片的信号端口之间为低阻抗通路,在防护电路响应静电或浪涌而动作之前,尖峰电压仍会对集成电路芯片造成冲击。因此,现有技术中集成电路芯片信号端口的静电浪涌防护电路存在防护可靠性低的问题。

发明内容

本发明实施例提供了一种信号端口的静电浪涌防护电路及电子设备,以提高对信号端口的静电浪涌防护效果,提高集成电路芯片的通信可靠性。

第一方面,本发明实施例提供了一种信号端口的静电浪涌防护电路。信号端口的静电浪涌防护电路包括:

防护模块,包括输入端、接地端和输出端;所述防护模块的输入端作为所述信号端口的静电浪涌防护电路的输入端,所述防护模块的接地端接入地信号;所述防护模块用于在发生静电和/或浪涌时,导通其输入端和接地端之间的传输路径;

电平转换模块,包括控制端、第一输入端、第二输入端和输出端;所述电平转换模块的控制端与所述防护模块的输出端电连接,所述电平转换模块的第一输入端接入电源信号,所述电平转换模块的第二输入端接入地信号,所述电平转换模块的输出端与集成电路芯片的信号端口电连接;所述电平转换模块用于在所述防护模块的输出信号的控制下,将所述电源信号转换为第一控制信号输出,或将所述地信号转换为第二控制信号输出。

可选地,所述防护模块包括:

防护单元,包括输入端、输出端和接地端;所述防护单元的第一端作为所述防护模块的输入端,所述防护单元的接地端作为所述防护模块的接地端;

高阻抗单元,包括输入端、输出端和接地端;所述高阻抗单元的输入端与所述防护单元的输出端电连接,所述高阻抗单元的接地端接入所述地信号,所述高阻抗单元的输出端作为所述防护模块的输出端。

可选地,所述防护单元包括:第一保护元件和电抗性元件;所述第一保护元件的第一端与所述电抗性元件的第一端电连接,并作为所述防护单元的输入端;所述第一保护元件的第二端作为所述防护单元的接地端;所述电抗性元件的第二端作为所述防护单元的输出端。

可选地,所述防护单元还包括:第二保护元件;所述第二保护元件的第一端与所述电抗性元件的第二端电连接,所述第二保护元件的第二端接入所述地信号。

可选地,所述高阻抗单元包括:第一电阻和第二电阻;所述第一电阻的第一端作为所述高阻抗单元的输入端;所述第一电阻的第二端与所述第二电阻的第一端电连接,并作为所述高阻抗单元的输出端;所述第二电阻的第二端作为所述高阻抗单元的接地端。

可选地,所述第一电阻的阻值大于或等于20kΩ。

可选地,所述电平转换模块包括:

第一转换单元,包括控制端、第一输入端、第二输入端和输出端;所述第一转换单元的控制端作为所述电平转换模块的控制端,所述第一转换单元的第一输入端接入所述电源信号,所述第一转换单元的第二输入端接入所述地信号;

第二转换单元,包括控制端、第一输入端、第二控制端和输出端;所述第二转换单元的控制端与所述第一转换单元的输出端电连接,所述第二转换单元的第一输入端接入所述电源信号,所述第二转换单元的第二输入端接入所述地信号,所述第二转换单元的输出端作为所述电平转换模块的输出端。

可选地,所述第一转换单元包括:第一晶体管和第三电阻;所述第一晶体管的控制极作为所述第一转换单元的控制端,所述第一晶体管的第一极作为所述第一转换单元的第二输入端;所述第一晶体管的第二极与所述第三电阻的第二端电连接,并作为所述第一转换单元的输出端;所述第三电阻的第一端作为所述第一转换单元的第一输入端;

所述第二转换单元包括:第二晶体管、第四电阻和第五电阻;所述第四电阻的第一端作为所述第二转换单元的控制端,所述第四电阻的第二端与所述第二晶体管的控制极电连接;所述第二晶体管的第一极作为所述第二转换单元的第二输入端;所述第二晶体管的第二极与所述第五电阻的第二端电连接,并作为所述第二转换单元的输出端;所述第五电阻的第一端作为所述第二转换单元的第一输入端。

第二方面,本发明实施例还提供了一种电子设备。电子设备包括:集成电路芯片和如本发明任意实施例所提供的信号端口的静电浪涌防护电路。

可选地,所述电子设备还包括:主板;所述主板包括:输入接口;所述集成电路芯片和所述信号端口的静电浪涌防护电路集成于所述主板上;所述信号端口的静电浪涌防护电路的输入端与所述输入接口电连接。

本发明实施例提供的信号端口的静电浪涌防护电路中,设置有防护模块和电平转换模块。防护模块可以为输入信号中在发生静电或浪涌时产生的干扰信号提供泄放路径,使输入信号中的有效信号向后级电路传输。电平转换模块可以将传输至其控制端的信号转换为第一控制信号或第二控制信号输出,即对有效信号在传输过程中的衰减进行有效的补偿和还原,为有效信号提供了更多的衰减余量,使得防护模块的输入端和输出端之间的传输路径可以设置为更高的阻抗。那么,即使防护模块的输入端与接地端之间的导通存在延时,干扰信号也会更多的衰减在到达电平转换模块的控制端之前,进一步提高静电浪涌防护能力。并且,电平转换模块的控制端和输出端之间并无直接连通的传输路径,因此,电平转换模块可以起到对干扰信号的阻挡作用,使干扰信号无法传输至信号端口,提供更进一步的保护。因此,本发明实施例可以提高对信号端口的静电浪涌防护效果,提高集成电路芯片的通信可靠性。

附图说明

图1是现有的一种信号端口的静电浪涌防护电路的结构示意图;

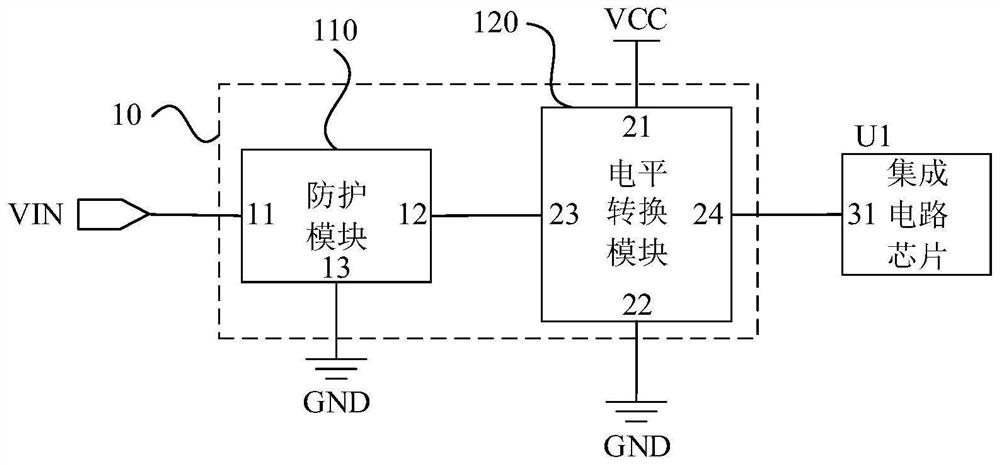

图2是本发明实施例提供的一种信号端口的静电浪涌防护电路与集成电路芯片的连接关系示意图;

图3是本发明实施例提供的一种信号端口的静电浪涌防护电路的结构示意图;

图4是本发明实施例提供的一种电子设备与外部设备的连接关系示意图。

具体实施方式

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

正如背景技术所述,现有技术中集成电路芯片信号端口的静电浪涌防护电路存在防护可靠性低的问题。经发明人研究,具体原因如下:

集成电路芯片信号端口的静电浪涌防护电路主要是通过晶体管等元器件堆叠而成。要求的防护等级越高,防护电路需要的元器件越多,防护电路的体积和成本越大;过大的体积并不利于下游公司PCBA(Printed Circuit Board Assembly,印刷电路板组件)设计中元件位置的灵活摆放和走线,因此大多集成电路芯片的信号端口(例如IO端口)自带的防护结构并不能满足电子设备产成品的浪涌与ESD标准要求,需要在下游公司设计的PCBA上增加额外的防护电路。

图1是现有的一种信号端口的静电浪涌防护电路的结构示意图。参见图1,示例性地,现有技术中信号端口的静电浪涌防护电路100包括防护模块101、电阻R01、电阻R02和电容C01。其中,防护模块101与集成电路芯片U01为并联关系;电阻R01、电容C01和电阻R02串联连接在接口J01和集成电路芯片U01的信号端口01之间。该静电浪涌防护电路的缺陷在于:

1)防护模块101与被保护集成电路芯片U01是并联关系,当浪涌或ESD事件发生后,防护模块101需要响应时间,响应前尖峰电压同时施加在防护模块101和信号端口01上,尖峰电压仍会对信号端口01造成冲击。

2)集成电路芯片U01需要通过识别来自发送端的信号的高低电平来建立正确的通信逻辑0或1,传输至信号端口01的信号必须满足电压门限值才能被正确识别。现有技术中,电阻R01和电阻R02串联在通信回路中,这必然限制了其阻值不能太大,阻值太大必然会分压太大,造成信号损失,不能满足信号端口01的门限电压值,从而影响通信。

综上两点,从接口J01到信号端口01之间仍然是低阻抗通路,在防护模块101响应前,当集成电路芯片U01的信号端口01不能承受浪涌或ESD的尖峰电压时就会击穿烧毁。其次,浪涌和ESD事件还会产生震荡与电磁干扰源(Electromagnetic Interference,EMI),现有技术的低阻抗通路给干扰源提供了友好的传导路径,使其能很容易地进入信号端口01,进而耦合到集成电路芯片U01的内部系统之中,可能引起系统的某些单元时序错乱导致信号端口01不能通讯,需要断电重启才能恢复。

图1中示例性地给出了单端通信的电路结构,但上述问题并不仅存在于单端通信结构中。对于差分通信电路,相当于在接口和集成电路芯片之间再增加一条电容和电阻构成的缓冲路径以及一个防护模块。但为保证通信正确性,接口与通信端口间仍为低阻抗路径,在防护模块动作之前,静电或浪涌造成的尖峰电压仍会对通信端口造成冲击,干扰源仍容易进入通信端口。

再者,针对现有技术中用于电源保护的防护电路,其防护思路与图1中类似,将接口J01替换为供电端口,集成电路芯片U01替换为用电设备即为电源防护电路。而由于该防护电路设置于电源的供电路径中,为保证供电效率和减小损耗,防护电路串联在电流传输路径中的部分也需要为低阻抗路径,难以保证防护效果。

在上述基础上,无论采用热敏电阻、电子保险丝和晶体管中任何一种保护元件作为防护模块101,都需要一定的响应时间,难以对纳秒级浪涌、ESD的纳秒级或微秒级高能信号进行及时的反应。

基于以上研究,本发明实施例提供了一种信号端口的静电浪涌防护电路,可设置于主板的输入结构与集成电路芯片的信号端口之间,实现对静电和浪涌的有效防护。图2是本发明实施例提供的一种信号端口的静电浪涌防护电路与集成电路芯片的连接关系示意图。参见图2,该信号端口的静电浪涌防护电路10包括:防护模块110和电平转换模块120。

其中,防护模块110包括输入端11、接地端13和输出端12;防护模块110的输入端11作为信号端口的静电浪涌防护电路10的输入端,接地端13接入地信号GND;防护模块110用于在发生静电和/或浪涌时,导通其输入端11和接地端13之间的传输路径。电平转换模块120包括控制端23、第一输入端21、第二输入端22和输出端24;电平转换模块120的控制端23与防护模块110的输出端12电连接,第一输入端21接入电源信号VCC,第二输入端22接入地信号GND,输出端24与集成电路芯片U1的信号端口31电连接;电平转换模块120用于在防护模块110的输出信号的控制下,将电源信号VCC转换为第一控制信号输出,或将地信号GND转换为第二控制信号输出。

示例性地,电源信号VCC可以是直流电压信号;信号端口31可以是IO端口。信号端口的静电浪涌防护电路10和集成电路芯片U1可以集成于电子设备的主板上;输入信号VIN可以是由外部设备输出的通信信号,经由主板上的输入接口向集成电路芯片U1传输。

示例性地,该信号端口的静电浪涌防护电路10的工作过程包括:

当无静电或浪涌时,输入信号VIN为有效信号,不包含干扰信号。防护模块110的输入端11和输出端12之间的传输路径导通,且防护模块110的输入端11和接地端13之间的传输路径关断;输入信号VIN经由防护模块110的输入端11和输出端12向电平转换模块120的控制端23传输。防护模块110的输出信号(记为中间信号)控制电平转换模块120的工作状态。例如,当中间信号为高电平时,控制电平转换模块120的第一输入端21和输出端24之间的传输路径导通,将电源信号VCC转换为第一控制信号输出,第一控制信号例如是较高的高电平;当中间信号为低电平时,控制电平转换模块120的第二输入端22和输出端24之间的传输路径导通,将地信号GND转换为第二控制信号输出,第二控制信号例如是较低的低电平。上述过程仅为示例性的解释,并不作为对本发明的限定,电平转换模块120内部的转换逻辑可以根据实际需求进行设定。

当出现静电或浪涌时,会造成短时过压过流或振荡等现象,体现在输入信号VIN中为:使输入信号VIN包含有效信号和干扰信号两部分。此时,防护模块110的输入端11和接地端13之间的传输路径导通,提供干扰信号的泄放通路,使干扰信号经由防护模块110的输入端11和接地端13泄放到地,不向后级电路传输;同时,防护模块110的输入端11和输出端12之间的传输路径保持导通,使有效信号正常向后传输。经过防护模块110的防护作用,使得电平转换模块120的工作过程不受静电或浪涌的影响,维持正常工作状态。

其中,电平转换模块120的控制端23的电平识别范围可以大于信号端口31的电平识别范围;第一控制信号和第二控制信号可以设置在信号端口的电平识别能力范围内。这样,电平转换模块120根据传输至其控制端23的信号输出第一控制信号或第二控制信号,相当于对输入信号VIN中的有效信号在传输过程中的衰减进行补偿和还原,使第一控制信号和第二控制信号可以指示有效信号所代表的电平高低,被信号端口31正确有效识别。也就是说,电平转换模块120的设置,为输入信号VIN中的有效信号提供了更多的衰减裕度,使得相比于现有技术,在保证信号识别准确性的基础上,防护模块110的输入端11与输出端12之间的传输路径可以设置为更高的阻抗;那么,即使防护模块110的输入端11至接地端13之间的导通存在延时,干扰信号也会更多的衰减在防护模块110输入端11与输出端12之间的传输路径中,不会对信号端口31造成冲击,不会影响信号端口31的信号识别。

具体地,电平转换模块120的控制端23的高电平识别下限可以低于信号端口31的高电平识别下限,电平转换模块120的控制端23的低电平识别上限可以高于信号端口31的低电平识别上限;且第一控制信号可以高于信号端口31的高电平识别下限,第二控制信号可以低于信号端口31的低电平识别上限。例如,电平转换模块120的控制端23可将大于1V的电平时可识别为高电平,低于0.7V的电平识别为低电平;信号端口31可将大于1.5V的电平识别为高电平,低于0.3V的电平识别为低电平。第一控制信号为2V,第二控制信号为0.1V。假设有效信号为1.8V,经防护模块110后衰减至1.2V,若直接传输至信号端口31,无法被有效识别;但电平转换模块120的控制端23可将1.2V识别为高电平,从而控制第一输入端21和输出端24之间的传输路径导通,控制2V的第一控制信号输出;信号端口31可以将2V的第一控制信号识别为高电平,从而完成信号的正确识别。因此,电平转换模块120可以对衰减后的有效信号进行有效的补偿、还原甚至放大。

本发明实施例提供的信号端口的静电浪涌防护电路10中,设置有防护模块110和电平转换模块120。防护模块110可以为输入信号VIN中在发生静电或浪涌时产生的干扰信号提供泄放路径,使输入信号VIN中的有效信号向后级电路传输。电平转换模块120可以将传输至其控制端23的信号转换为第一控制信号或第二控制信号输出,即对有效信号在传输过程中的衰减进行有效的补偿和还原,为有效信号提供了更多的衰减余量,使得防护模块110的输入端11和输出端12之间的传输路径可以设置为更高的阻抗。那么,即使防护模块110的输入端11与接地端13之间的导通存在延时,干扰信号也会更多的衰减在到达电平转换模块120的控制端之前,进一步提高静电浪涌防护能力。并且,电平转换模块120的控制端23和输出端24之间并无直接连通的传输路径,因此,电平转换模块120可以起到对干扰信号的阻挡作用,使干扰信号无法传输至信号端口31,提供更进一步的保护。因此,本发明实施例可以提高对信号端口31的静电浪涌防护效果,提高集成电路芯片U1的通信可靠性。

图3是本发明实施例提供的一种信号端口的静电浪涌防护电路的结构示意图。参见图3,在一种实施方式中,可选地,防护模块包括:防护单元111和高阻抗单元112。防护单元111的第一端作为防护模块110的输入端,接入输入信号VIN;防护单元111的接地端作为防护模块的接地端,接入地信号GND。高阻抗单元112的输入端与防护单元111的输出端电连接,高阻抗单元112的接地端接入地信号GND,高阻抗单元112的输出端作为防护模块110的输出端。

其中,防护单元111用于在发生静电或浪涌时,提供干扰信号的泄放通路;高阻抗单元112提供了防护单元110至电平转换模块120之间的高阻抗传输路径,可以在保证电平转换模块120识别能力的基础上,在防护单元111响应之前,尽可能多的使干扰信号衰减。

继续参见图3,在上述各实施方式的基础上,可选地,电平转换模块120包括:第一转换单元121和第二转换单元122。第一转换单元121的控制端作为电平转换模块120的控制端,与防护模块110的输出端电连接;第一转换单元121的第一输入端接入电源信号VCC,第一转换单元121的第二输入端接入地信号GND。第二转换单元122的控制端与第一转换单元121的输出端电连接,第二转换单元122的第一输入端接入电源信号VCC,第二转换单元122的第二输入端接入地信号GND,第二转换单元122的输出端作为电平转换模块120的输出端。

本实施例中,第一转换单元121用于将防护模块110的输出信号转换为中间控制信号,第二转换单元122用于将中间控制信号转换为输出信号VOUT。其中,根据中间控制信号的电平高低,输出信号VOUT为第一控制信号或第二控制信号。示例性地,根据信号传输和布线等实际需求,第一转换单元121的第一输入端和第二转换单元122的第一输入端也可以连接不同的电源端,接入不同的电源信号。

上述各实施例示例性地给出了信号端口的静电浪涌防护电路10的功能单元结构,下面,对信号端口的静电浪涌防护电路10可能具有的具体结构进行说明,但不作为对本发明的限定。

继续参见图3,在上述各实施方式的基础上,可选地,防护单元111包括:第一保护元件T1和电抗性元件B1;第一保护元件T1的第一端与电抗性元件B1的第一端电连接,并作为防护单元111的输入端;第一保护元件T1的第二端作为防护单元111的接地端;电抗性元件B1的第二端作为防护单元111的输出端。

示例性地,第一保护元件T1可以是压敏电阻、稳压二极管或瞬态二极管(Transient Voltage Suppressor,TVS),用于对电压进行钳位。电抗性元件B1可以为电感,用于抑制电流突变。其中,电抗性元件B1可根据防护级别的不同进行选择;防护等级低时可以不设置电抗性元件B1;防护等级高时可以设置为磁珠,以更好的抑制ESD震荡。

继续参见图3,上述各实施方式的基础上,可选地,防护单元111还包括:第二保护元件T2;第二保护元件T2的第一端与电抗性元件B1的第二端电连接,第二保护元件T2的第二端接入地信号GND。

第二保护元件T2用于泄放经第一保护元件T1后传输来的残余能量,与第一保护元件T1构成双重防护。这样设置,可以提高该防护电路的防护等级,或者,降低对电平转换模块120的控制端的耐压能力要求。示例性地,第二保护元件T2可以是压敏电阻、稳压二极管或瞬态二极管。

继续参见图3,在一种实施方式中,可选地,高阻抗单元112包括:第一电阻R1和第二电阻R2;第一电阻R1的第一端作为高阻抗单元112的输入端;第一电阻R1的第二端与第二电阻R2的第一端电连接,并作为高阻抗单元112的输出端;第二电阻R2的第二端作为高阻抗单元112的接地端。

其中,第一电阻R1的阻值大于或等于20kΩ。第二电阻R2的阻值可以根据实际需求进行选择,例如第二电阻R2的阻值大于或等于20kΩ,或者,第二电阻R2也可以不设置。

继续参见图3,在上述各实施方式的基础上,可选地,第一转换单元121包括:第一晶体管Q1和第三电阻R3;第一晶体管Q1的控制极作为第一转换单元121的控制端;第一晶体管Q1的第一极作为第一转换单元121的第二输入端,接入地信号GND;第一晶体管Q1的第二极与第三电阻R3的第二端电连接,并作为第一转换单元121的输出端;第三电阻R1的第一端作为第一转换单元121的第一输入端,接入电源信号VCC。

可选地,高阻抗单元112中的第一电阻R1和第二电阻R2可以复用为第一晶体管Q1控制极的分压电路。可以根据输入信号VIN的电平,结合第一晶体管Q1的控制极的耐压值,调整第一电阻R1和第二电阻R2的阻值,可以控制传输至第一晶体管Q1控制极的电压大小,从而控制第一晶体管Q1的开关状态。

继续参见图3,在上述各实施方式的基础上,可选地,第二转换单元122包括:第二晶体管Q2、第四电阻R4和第五电阻R5;第四电阻R4的第一端作为第二转换单元122的控制端,第四电阻R4的第二端与第二晶体管Q2的控制极电连接;第二晶体管Q2的第一极作为第二转换单元122的第二输入端,接入地信号GND;第二晶体管Q2的第二极与第五电阻R5的第二端电连接,并作为第二转换单元122的输出端;第五电阻R5的第一端作为第二转换单元的第一输入端,接入电源信号VCC。其中,若集成电路芯片内部设置有上拉电阻,可以不设置第五电阻R5。

下面,结合图3的具体结构,对该防护电路的工作原理进行说明:

示例性地,第一电阻R1和第二电阻R2的阻值可达20kΩ及以上级别,第三电阻R3和第五电阻R5的阻值可达50kΩ及以上级别,第四电阻R4的阻值可达10kΩ及以上级别。第一晶体管Q1与第二晶体管Q2可以是NMOS管,也可以是NPN三极管;那么,晶体管的控制极可以是NPN三极管的基极或NMOS管的栅极,晶体管的第一极可以是NMOS的源极或NPN三极管的发射极,晶体管的第一极可以是NMOS晶体管的漏极或NPN三极管的集电极。将第一晶体管Q1的第二极定义为节点N1,将第二晶体管Q2的第二极定义为节点N2。

对于电平转换模块120:当输入信号VIN为高电平时,第一晶体管Q1响应高电平导通,节点N1到第一转换单元121的第二输入端之间呈现低阻态几欧姆级别,电源信号VCC主要施加在第三电阻R3上,节点N1呈现低电平,第二晶体管Q2的控制极被拉低,第二晶体管Q2截止,节点N2到第二转换单元122的第二输入端呈现高阻态兆欧姆级别,节点N2输出高电平。当输入信号VIN为低电平时,第一晶体管Q1响应低电平截止,节点N1到第一转换单元121的第二输入端之间呈现高阻态兆欧姆级别,电源信号VCC主要施加在第一晶体管Q1上,第二晶体管Q2的控制极被拉高;第二晶体管Q2导通,呈现低阻态几欧姆级别,节点N2输出低电平。电平转换模块120通过以上过程实现电平的转换。

对于防护模块110:当输入信号VIN的输入端口发生浪涌或ESD事件,第一保护元件T1将主要电流泄放到地,第二保护元件T2将残余电流释放到地,浪涌或ESD经第一保护元件T1和第二保护元件T2释放后残余的能量较弱。从输入端口到地来看,第一保护元件T1、第二保护元件T2与高阻抗单元112属于并联关系;这三条支路的施加电压(记为U)相等时,通信路径上的电流(即第一电阻R1所在支路的电流,记为I)通过如下公式计算:I=U/Rt1+U/Rt2+U/(R1+R2)。其中,Rt1为第一保护元件T1的等效阻值,Rt1为第二保护元件T2的等效阻值。浪涌或ESD事件发生时,Rt1与Rt2呈现低阻抗毫欧级,第一电阻R1阻值在20kΩ或以上,可知第一电阻R1阻碍并迫使电流I通过第一保护元件T1和第二保护元件T2泄放到地;浪涌或ESD电压可看作被第一保护元件T1和第二保护元件T2短路到地,因此浪涌或ESD的电压电流几乎没有进入第一晶体管Q1的控制极,使得第一晶体管Q1的控制极得到很好的保护,避免被浪涌或ESD击穿烧毁。

并且,输入信号VIN经高阻抗路径传输,无论浪涌和ESD的产生多么迅速,或两保护元件的响应有无延时,高阻抗路径都会阻碍干扰信号的传输,不会因为防护单元111响应慢而使信号端口31受到冲击。具体地,假设由浪涌或ESD产生的震荡、EMI干扰源等干扰信号在防护单元111动作前向后传输,那么其传输路径为:经由电抗性元件B1、第一电阻R1、第一晶体管Q1、第三电阻R3和第五电阻R5传输至信号端口31;或者,经由电抗性元件B1、第一电阻R1、第一晶体管Q1、第四电阻R4和第二晶体管Q2传输至信号端口31。那么,干扰信号传输到信号端口31的传输路径中的串联阻抗达至少会达到30kΩ,干扰信号主要被串联电阻消耗和阻隔,很好的避免了集成电路芯片U1的信号端口31遭受干扰,进而耦合到系统,可以使系统稳定地工作、确保正常通信。

综上所述,该信号端口的静电浪涌防护电路10的优点包括:

1)使输入信号VIN中有效信号的衰减得到很好的补偿。举例说明如下:传输到第一晶体管Q1控制极的信号衰减过低(例如自1.8V衰减到1V),若直接传输值信号端口,信号端口可能无法识别是高电平还是低电平;然而本实施例中,通过选择第一晶体管Q1和第二晶体管Q2为具有较低开启电压的器件(例如选NMOS管,栅极电压1V开启,NPN三极管基极电压0.7V开启),可对衰减后的信号正常反应,进而将传输至信号端口还原到原本的电平高低,提升通信的可靠性。

2)本防护电路具有极高的输入阻抗,配合两保护元件能提供极佳的ESD防护,在设计产品过程中误选信号端口抗ESD较弱的集成电路芯片时,本防护电路相当于给信号端口打了补丁,不必重新评估其他集成电路芯片再设计产品,大大节省产品开发时间。或者说,本防护电路为使用方(如电子产品设计公司)提供了更多选择范围,使得使用方可选用信号端口抗ESD较弱的集成电路芯片,节省集成电路成本,使产品更具有竞争力;同时,可以使已生产的集成电路芯片更好的销售,没有后顾之忧。

3)本防护电路极高的输入阻抗能很好的对抗浪涌与ESD产生的干扰,能极好的抑制浪涌与ESD产生的震荡、EMI干扰源,避免集成电路芯片信号端口遭受干扰进而耦合到系统,可以使系统稳定地工作、确保正常通信。并且高阻抗配合保护元件可以给集成电路芯片的信号端口提供极高的防护等级,防止信号端口被浪涌与ESD事件烧毁;给集成电路芯片信号端口的稳定工作提供了必要条件。

本发明实施例还提供了一种电子设备,包括集成电路芯片和如本发明任一实施例所提供的信号端口的静电浪涌防护电路,具有相应的有益效果。其中,信号端口的静电浪涌防护电路中,电平转换模块的输出端与集成电路芯片的信号端口电连接,该信号端口可以是IO端口。

图4是本发明实施例提供的一种电子设备与外部设备的连接关系示意图。参见图4,在一种实施方式中,可选地,电子设备还包括:主板1;主板1包括输入接口J1。集成电路芯片U1和信号端口的静电浪涌防护电路10集成于主板1上;信号端口的静电浪涌防护电路10的输入端与输入接口J1电连接。外部传输来的输入信号通过接口J1向信号端口的静电浪涌防护电路10传输。

示例性地,外部设备U2包括输出端41和接地端42,外部设备U2的输出端41与接口J1电连接,用于向接口J1提供输入信号;外部设备U2的接地端42接入地信号GND。

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

- 信号端口的静电浪涌防护电路及电子设备

- 一种HDMI接口静电浪涌防护电路、PCB走线、PCB板及电子设备