一种氮化镓光导半导体开关及其制备方法

文献发布时间:2023-06-19 13:46:35

技术领域

本发明涉及固态化高功率微波产生技术领域,尤其是涉及一种氮化镓光导半导体开关及其制备方法。

背景技术

在高功率微波产生应用领域中,传统气体开关和电真空器件因其系统复杂、体积大,寿命和可靠性存在重大挑战。随着半导体技术的不断进步,半导体器件的峰值功率不断提升,基于半导体器件可构建固态化的高功率微波系统。而在固态化高功率微波三大产生技术(基于快速电离开关和硅雪崩陡化开关的超宽谱高功率微波技术、基于氮化镓功率放大器的高功率微波技术、基于光导半导体开关的高功率微波技术)中,光导半导体开关因其具有结构简单、体积小、耐压高、响应速度快、抖动低的特点,已成为当前研究的国际前沿和热点。基于光导半导体开关的半导体材料通常有第一代半导体硅(Si)、第二代半导体砷化镓(GaAs)和磷化铟(InP)及第三代超宽禁带半导体碳化硅(SiC)和氮化镓(GaN),器件工作电压可达数十千伏甚至百千伏。而氮化镓(GaN)光导半导体开关因其响应速度快、导通电阻小及触发激光能量低等优势具有极大的发展潜力。尽管氮化镓(GaN)光导半导体开关在理论上具有优异的性能,但在应用中仍然存在峰值功率不够高的问题。

发明内容

为解决现有技术中存在的问题,本发明的目的在于提供一种氮化镓光导半导体开关及其制备方法,本发明氮化镓光导半导体开关从光吸收特性角度出发,提升了氮化镓光导半导体开关的峰值功率高,使得该氮化镓光导半导体开关能够满足固态化高功率微波系统应用需求。

本发明采用的技术方案如下:

一种氮化镓光导半导体开关,包括氮化镓层,氮化镓层的正面和反面分别设有阳极和阴极,氮化镓层的正面和阳极的表面设有增透膜,增透膜在阳极的正面设有第一空白区域,第一空白区域沿增透膜的表面从增透膜的厚度方向延伸至阳极的正面,第一空白区域得宽度不大于阳极的宽度;

氮化镓层的背面和阴极的表面设有高反膜,高反膜在阴极的正面设有第二空白区域,第二空白区域沿高反膜的表面从高反膜的厚度方向延伸至阴极的正面,第二空白区域的宽度不大于阴极的宽度。

优选的,所述增透膜包括第一氮化硅层和第一氮化铝层,第一氮化铝层设置于氮化镓层的正面和阳极的表面,第一氮化硅层设置于第一氮化铝层的表面。

优选的,第一氮化硅层的厚度为60-70nm,第一氮化铝层的厚度为5-10nm。

优选的,高反膜包括第一二氧化硅层、第一氧化钽层、第二二氧化硅层、第二氧化钽层、第三二氧化硅层和第三氧化钽层,第一二氧化硅层设置于氮化镓层的背面和阴极的表面,第一氧化钽层设置于第一二氧化硅层的表面,第二二氧化硅层设置于第一氧化钽层的表面,第二氧化钽层设置于第二二氧化硅层的表面,第三二氧化硅层设置于第二氧化钽层的表面,第三氧化钽层设置于第三二氧化硅层的表面。

优选的,第一二氧化硅层、第一氧化钽层、第二二氧化硅层、第二氧化钽层、第三二氧化硅层和第三氧化钽层的厚度范围分别为63-67nm、63-67nm、63-67nm、63-67nm、63-67nm和63-67nm。

优选的,阳极包括第一金层、第一镍层、第一铝层和第一钛层,第一钛层设置于氮化镓层的正面,第一铝层设置于第一钛层的表面,第一镍层设置于第一铝层的表面,第一金层设置于第一镍层的表面;

阴极包括第二金层、第二镍层、第二铝层和第二钛层,第二钛层设置于氮化镓层的背面,第二铝层设置于第二钛层的表面,第二镍层设置于第二铝层的表面,第二金层设置于第二镍层的表面。

优选的,第一金层的厚度为40-45nm,第一镍层的厚度为50-55nm,第一铝层的厚度为120-125nm,第一钛层的厚度为15-20nm,第二金层的厚度为40-45nm,第二镍层的厚度为50-55nm,第二铝层的厚度为120-125nm,第二钛层的厚度为15-20nm。

优选的,氮化镓层采用厚度为325-375μm的铁掺杂半绝缘氮化镓层。

本发明如上所述氮化镓光导半导体开关的制备方法,包括如下过程:

在氮化镓层的正面阳极所在的区域光刻图形化,形成阳极欧姆接触区,之后处理掉残留的光刻胶,再在氮化镓层的正面制备阳极层,再去除氮化镓层的正面上阳极欧姆接触区之外的阳极层,在氮化镓层的正面形成阳极;在氮化镓层的背面阴极所在的区域光刻图形化,形成阴极欧姆接触区,之后处理掉残留的光刻胶,再在氮化镓层的背面制备阴极层,再去除氮化镓层的背面上阴极欧姆接触区之外的阴极层,在氮化镓层的正面形成阴极,得到器件一;

将对器件一进行退火,使阳极与氮化镓层之间以及阴极与氮化镓层之间形成欧姆接触,得到器件二;

对器件二进行清洗;

在清洗后的器件二上氮化镓层正面的一侧制备增透膜,在清洗后的器件二上氮化镓层背面的一侧制备高反膜,得到器件三;

在器件三上的增透膜上刻蚀出第一空白区域,在器件三上的高反膜上刻蚀出第二空白区域,得到器件四;

将器件四进行退火处理,得到所述氮化镓光导半导体开关。

优选的,当阳极包括第一金层、第一镍层、第一铝层和第一钛层、阴极包括第二金层、第二镍层、第二铝层和第二钛层、第一金层的厚度为40-45nm、第一镍层的厚度为50-55nm、第一铝层的厚度为120-125nm、第一钛层的厚度为15-20nm、第二金层的厚度为40-45nm、第二镍层的厚度为50-55nm、第二铝层的厚度为120-125nm、第二钛层的厚度为15-20nm时:对器件一进行退火的温度为850-860℃,保温时间为30-35秒,保温结束后30-35秒冷却至室温;

对器件四退火的温度为300-350℃,时间为10-15分钟,保温结束后30-60分钟冷却至室温。

本发明具有如下有益效果:

本发明氮化镓光导半导体开关中,通过设置增透膜,能够提高氮化镓层的光透射率,通过设置高反膜,利用高反膜能够将穿过光尽可能限制在氮化镓层里面,从而使得氮化镓层杂质能级激发产生更多的载流子,最终提高光量子效率,增大了氮化镓光导半导体开关的输出电流及峰值功率,使得该氮化镓光导半导体开关能够满足固态化高功率微波系统应用需求。

附图说明

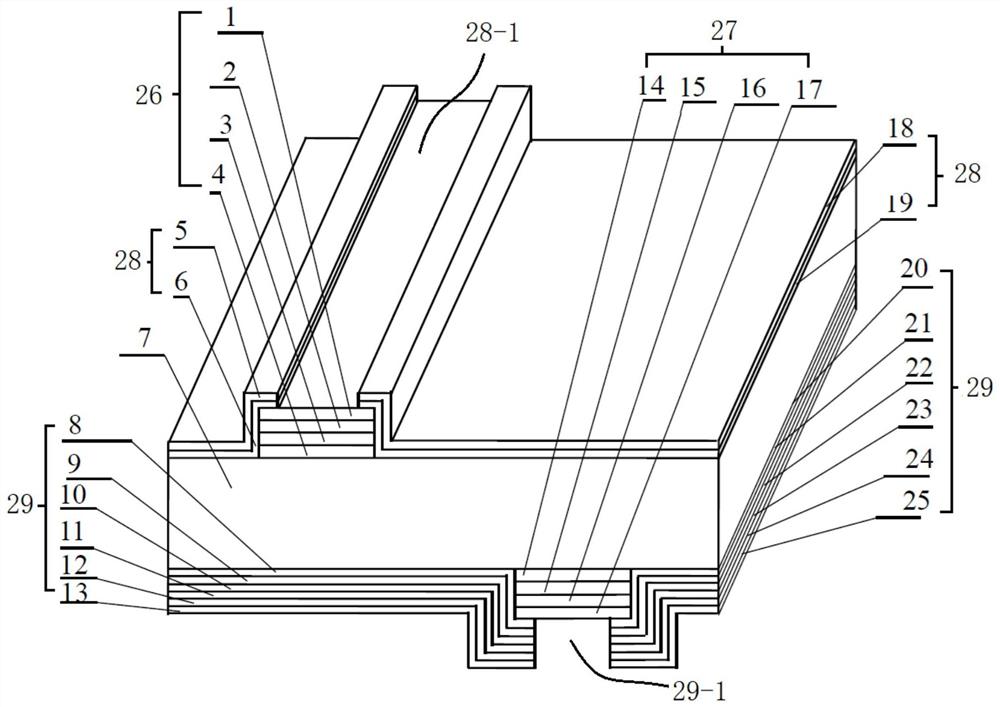

图1是本发明氮化镓光导半导体开关的基本结构三维立体图;

图2是本发明氮化镓光导半导体开关的基本结构剖面示意图;

图3是本发明实施例中20nm/120nm/50nm/40nm的钛(Ti)/铝(Al)/镍(Ni)/金(Au)多层金属欧姆接触特性曲线;

图4是本发明实施例中氮化铝(AlN)和氮化硅(Si

图5是本发明实施例中二氧化硅(SiO

附图标号说明

1-第一金层;2-第一镍层;3-第一铝层;4-第一钛层;5-第一氮化硅层;18-第二氮化硅层;6-第一氮化铝层;19-第二氮化铝层;7-氮化镓层;8-第一二氧化硅层;20-第四二氧化硅层;9-第一氧化钽层;21-第四氧化钽层;10-第二二氧化硅层;22-第五二氧化硅层;11-第二氧化钽层;23-第五氧化钽层;12-第三二氧化硅层;24-第六二氧化硅层;13-第三氧化钽层;25-第六氧化钽层;14-第二钛层;15-第二铝层;16-第二镍层;17-第二金层;26-阳极,27-阴极,28-增透膜,28-1-第一空白区域,29-高反膜,29-1-第二空白区域。

具体实施方式

下面结合附图和实施例来对本发明做进一步的说明。

本发明设计给出一种氮化镓光导半导体开关,该氮化镓光导半导体开关的结构包括:用于光导半导体基底材料的厚度为350±25μm的铁掺杂半绝缘氮化镓(Fe-SI/GaN)、用于光导半导体开关欧姆接触的厚度为20nm/120nm/50nm/40nm的钛(Ti)/铝(Al)/镍(Ni)/金(Au)多层金属;用于提升光透射率的厚度为5nm/65±5nm的氮化铝(AlN)/氮化硅(Si

该氮化镓光导半导体开关是通过紫外光刻、电子束沉积、磁控溅射、高温快速退火、原子层沉积(ALD)、等离子体增强化学气相沉积(PECVD)及高温慢速退火等关键工艺实现制作。利用钛(Ti)/铝(Al)/镍(Ni)/金(Au)多层金属堆栈在高温快速退火下实现良好的欧姆接触特性;利用氮化铝(AlN)/氮化硅(Si

本发明解决了半绝缘氮化镓(GaN)良好的欧姆接触实现比较困难,较大的比接触电阻率会导致器件阴阳电极在高压下容易发生烧蚀脱落的问题;还解决了在高压下阴阳电极边缘处存在极大的边缘电场,阴阳电极同样会被烧蚀损坏的问题;还解决了氮化镓(GaN)光导半导体开关光吸收特性较差,在波长为532nm的触发光照射下,30%光能被反射,70%被透射、光子利用率低的问题。本发明研究了如何提升氮化镓光导半导体开关欧姆接触特性、提高耐压能力及触发光能利用率的技术手段,以满足高功率微波系统应用需求具有重大的意义。

实施例

如图1和图2所示,本实施例的氮化镓光导半导体开关包括氮化镓层7,氮化镓层7的正面和反面分别设有阳极26和阴极27,氮化镓层7的正面和阳极26的表面设有增透膜28,增透膜28在阳极26的正面设有第一空白区域28-1,第一空白区域28-1沿增透膜28的表面从增透膜28的厚度方向延伸至阳极26的正面,第一空白区域28-1得宽度不大于阳极26的宽度,以图1和图2所示的方位为例,该结构中,增透膜28对阳极26的侧面全部包裹以及阳极26顶面靠近边缘的区域包裹;氮化镓层7的背面和阴极27的表面设有高反膜29,高反膜29在阴极27的正面设有第二空白区域29-1,第二空白区域29-1沿高反膜29的表面从高反膜29的厚度方向延伸至阴极27的正面,第二空白区域29-1的宽度不大于阴极27的宽度,以图1和图2所示的方位为例,该结构中,高反膜29对阴极27的侧面全部包裹以及阴极27顶面(图2所示阴极27的下表面)靠近边缘的区域包裹。阴阳电极局部包裹的原因:光导半导体开关在数十千伏甚至上百千伏的高压下,电极边缘处会存在很高的电场,高电场会烧蚀损坏电极致使其脱落,因此采用介质层局部包裹的方式可降低电极边缘电场,提高器件耐压能力及寿命。

具体的,增透膜28包括第一氮化硅层5和第一氮化铝层6,第一氮化铝层6设置于氮化镓层7的正面和阳极26的表面,第一氮化硅层5设置于第一氮化铝层6的表面。

高反膜29包括第一二氧化硅层8、第一氧化钽层9、第二二氧化硅层10、第二氧化钽层11、第三二氧化硅层12和第三氧化钽层13,第一二氧化硅层8设置于氮化镓层7的背面和阴极27的表面,第一氧化钽层9设置于第一二氧化硅层8的表面,第二二氧化硅层10设置于第一氧化钽层9的表面,第二氧化钽层11设置于第二二氧化硅层10的表面,第三二氧化硅层12设置于第二氧化钽层11的表面,第三氧化钽层13设置于第三二氧化硅层12的表面。

阳极26包括第一金层1、第一镍层2、第一铝层3和第一钛层4,第一钛层4设置于氮化镓层7的正面,第一铝层3设置于第一钛层4的表面,第一镍层2设置于第一铝层3的表面,第一金层1设置于第一镍层2的表面;

阴极27包括第二金层17、第二镍层16、第二铝层15和第二钛层14,第二钛层14设置于氮化镓层7的背面,第二铝层15设置于第二钛层14的表面,第二镍层16设置于第二铝层15的表面,第二金层17设置于第二镍层16的表面。

本实施例氮化镓光导半导体开关的具体制备工艺包括以下步骤:

步骤一:取厚度为350±25μm的铁掺杂半绝缘单晶氮化镓(Fe-SI/GaN)晶片;

步骤二:将步骤一所述铁掺杂半绝缘单晶氮化镓晶片浸泡在浓度为35%的盐酸溶液中40秒,去除表面自然氧化层,并采用大量去离子水冲洗3分钟;采用丙酮超声清洗3分钟;采用异丙醇超声清洗3分钟;采用无水乙醇超声清洗3分钟;采用大量去离子水冲洗5分钟,并用高纯氮气(N

步骤三:对步骤二所述晶片进行阳极光刻图形化,采用紫外光刻机进行一次紫外光刻,紫外光刻工艺流程为匀胶、前烘、反转烘、曝光、显影和坚膜。紫外光刻形成光导半导体开关欧姆接触区,选用光刻胶为AZ-5214-E,匀胶机转速4000rpm,时间30秒;采用温控加热板前烘,温度110℃,时间50秒;采用紫外光刻机对准曝光,曝光时间6.5秒;采用温控加热板反转烘,温度120℃,时间2分钟;采用紫外光刻机裸曝光,曝光时间65秒;采用AZ-400K显影液显影,AZ-400K:去离子水=1:4;采用温控加热板后烘坚膜,温度120℃,时间300秒;

步骤四:将步骤三所述晶片采用紫外臭氧处理残留光刻胶,时间2分钟;

步骤五:将步骤四所述晶片采用电子束蒸发法(E-Beam)沉积钛(Ti)金属,功率7.3%,镀率0.1nm/秒,厚度20nm,作为欧姆接触阳极黏附金属层;

步骤六:将步骤五所述晶片采用电子束蒸发法(E-Beam)沉积铝(Al)金属,功率22.5%,镀率0.2nm/秒,厚度120nm,作为欧姆接触阳极势垒金属层;

步骤七:将步骤六所述晶片采用电子束蒸发法(E-Beam)沉积镍(Ni)金属,功率10.3%,镀率0.2nm/秒,厚度50nm,作为欧姆接触阳极阻挡金属层;

步骤八:将步骤七所述晶片采用电子束蒸发法(E-Beam)沉积金(Au)金属,功率10.7%,镀率0.2nm/秒,厚度40nm,作为欧姆接触阳极导电金属层;

步骤九:将步骤八所述晶片采用剥离工艺(Lift-off)去除除欧姆接触区外的多层金属;采用丙酮超声清洗3分钟,异丙醇超声清洗3分钟,无水乙醇超声清洗3分钟,大量去离子水冲洗5分钟,高纯氮气(N

步骤十:将步骤九所述晶片采用紫外光刻机进行阴极光刻图形化,紫外光刻工艺流程同步骤三;

步骤十一:将步骤十所述晶片采用紫外臭氧处理残留光刻胶,时间2分钟;

步骤十二:将步骤十一所述晶片采用电子束蒸发法(E-Beam)沉积钛(Ti)金属,功率7.3%,镀率0.1nm/秒,厚度20nm,作为欧姆接触阴极黏附金属层;

步骤十三:对步骤十二所述晶片进行背面光刻图形化,采用电子束蒸发法(E-Beam)沉积铝(Al)金属,功率22.5%,镀率0.2nm/秒,厚度120nm,作为欧姆接触阴极势垒金属层;

步骤十四:将步骤十三所述晶片采用电子束蒸发法(E-Beam)沉积镍(Ni)金属,功率10.3%,镀率0.2nm/秒,厚度50nm,作为欧姆接触阴极阻挡金属层;

步骤十五:将步骤十四所述晶片采用电子束蒸发法(E-Beam)沉积金(Au)金属,功率10.7%,镀率0.2nm/秒,厚度40nm,作为欧姆接触阴极导电金属层;

步骤十六:将步骤十五所述晶片采用剥离工艺(Lift-off)去除除欧姆接触区外的多层金属;采用丙酮超声清洗3分钟,异丙醇超声清洗3分钟,无水乙醇超声清洗3分钟,大量去离子水冲洗5分钟,高纯氮气(N

步骤十七:将步骤十六所述晶片采用高温快速退火实现钛(Ti)/铝(Al)/镍(Ni)/金(Au)多层金属与铁掺杂半绝缘单晶氮化镓之间的良好欧姆接触,在形成铁掺杂半绝缘单晶氮化镓上形成阳极26和阴极27,温度850℃,时间35秒;

步骤十八:将步骤十七所述晶片依次采用丙酮、异丙醇、无水乙醇超声清洗3分钟,采用大量去离子水冲洗5分钟,并用高纯氮气(N

步骤十九:将步骤十八所述晶片采用原子层沉积法(ALD)沉积氮化铝(AlN)薄膜,厚度5nm,作为光导半导体开关第一层光增透薄膜;

步骤二十:将步骤十九所述晶片采用等离子体增强化学的气相沉积法(PECVD)沉积氮化硅(Si

步骤二十一:将步骤二十所述晶片采用磁控溅射法沉积二氧化硅(SiO

步骤二十二:将步骤二十一所述晶片采用磁控溅射法沉积氧化钽(Ta

步骤二十三:将步骤二十二所述晶片采用磁控溅射法沉积二氧化硅(SiO

步骤二十四:将步骤二十三所述晶片采用磁控溅射法沉积氧化钽(Ta

步骤二十五:将步骤二十四所述晶片采用磁控溅射法沉积二氧化硅(SiO

步骤二十六:将步骤二十五所述晶片采用磁控溅射法沉积氧化钽(Ta

步骤二十七:将步骤二十六所述晶片依次采用丙酮、异丙醇、无水乙醇超声清洗3分钟,采用大量去离子水冲洗5分钟,并用高纯氮气(N

步骤二十七:将步骤二十六所述晶片采用紫外光刻机光刻阳极图形化窗口,紫外光刻工艺流程同步骤三;

步骤二十八:将步骤二十七所述晶片采用电感耦合等离子体(ICP)刻蚀氮化铝(AlN)/氮化硅(Si

步骤二十九:将步骤二十八所述晶片采用紫外光刻机光刻阴极图形化窗口,紫外光刻工艺流程同步骤三;

步骤三十:将步骤二十九所述晶片采用电感耦合等离子体(ICP)刻蚀二氧化硅(SiO

步骤三十一:将步骤三十所述晶片采用高温慢速退火炉进行退火处理,温度350℃,时间10分钟,得到所述氮化镓光导半导体开关;

步骤三十二:将步骤三十一所述晶片进行耐压及波长为532nm的光触发测试。

本发明中,由于厚度为350±25μm的半绝缘GaN,其折射率约为2.29,在波长为532nm的触发下,其反射率约为30%,透射率约为70%,其光吸收率极低。当入射触发光垂直入射到光导半导体阳极一侧时,30%的光能被反射浪费,本发明通过在阳极一侧增加Si

当入射触发光以大于90%的透射率通过Si

本发明氮化镓光导半导体开关具有如下结构特点:

(1)本发明将在厚度为350±25μm的铁掺杂半绝缘单晶氮化镓(Fe-SI/GaN)上制备20nm/120nm/50nm/40nm的钛(Ti)/铝(Al)/镍(Ni)/金(Au)多层金属欧姆接触阴阳电极,在850℃/35s高温快速退火下,具有良好欧姆接触特性(见图3),比接触电阻率达到10

(2)本发明将在厚度为350±25μm的铁掺杂半绝缘单晶氮化镓(Fe-SI/GaN)上制备5nm的氮化铝(AlN)和65±5nm的氮化硅(Si

(3)本发明将在厚度为350±25μm的铁掺杂半绝缘单晶氮化镓(Fe-SI/GaN)上制备65±2nm/65±2nm/65±2nm/65±2nm/65±2nm/65±2nm的二氧化硅(SiO

(4)该氮化铝(AlN)和氮化硅(Si

(5)该二氧化硅(SiO

- 一种氮化镓光导半导体开关及其制备方法

- 一种砷化镓光导开关的制备方法