引线框架及封装体

文献发布时间:2023-06-19 13:49:36

技术领域

本发明涉及半导封装领域,特别涉及一种封装体及封装方法。

背景技术

封装产品通常是将芯片贴装于引线框架上并以塑封料封装。

图1所示是本领域中一常规封装产品的结构示意图。如图1所示,所述封装产品是将一芯片2贴装于引线框架1的基岛11上,通过一金属引线(尤其是一铝线)3使得所述芯片2与所述引线框架1的引脚12连接,最后以塑封料4封装。

在图1所示的封装产品中,如图1中所示的,由于所述金属引线3的线弧是扁平的,线弧最高点(即图1中所述金属引线3与所述芯片2的上表面之间距离最大值H处)过于靠近所述芯片2的表面,使得所述金属引线3非常容易接触所述芯片2的边缘,而具有极高的短路风险。其次,在图1所示的封装产品的结构中,由于所述引线框架1的所述引脚12在所述金属引线3的第二焊点(即图1中所述金属引线3与所述引脚12的接触位置)会进行下表面蚀刻,且所述金属引线3很粗,打线力量较大,因而如图1所示,所述引脚2因难以承受该打线力量而极易发生变形。

因此,有必要提供一种新的引线框架,以克服上述缺陷。

发明内容

本申请的目的在于提供一种引线框架和利用该引线框架的封装体。通过所述引线框架的结构设计,使得在粗金属引线打线时,所述引线框架不会因打线力量而发生变形,并且,形成的粗金属引线的线弧最高点位于芯片的表面之外,从而不会发生引线接触芯片边缘的情况,因而可以避免短路风险。

为了达到上述目的,根据本申请的一方面,提供一种引线框架,包括至少一个基岛及复数个引脚,每一引脚具有一靠近所述基岛的第一端,每一引脚被配置为:每一引脚的表面在所述第一端突出于所述基岛贴装一芯片的表面。

在一些实施例中,所述引线框架的厚度具有一最大值,每一引脚的厚度等于该最大值。

在一些实施例中,所述复数个引脚形成至少一组引脚组,每一基岛对应一组引脚组。

根据本申请的另一方面,提供一种封装体,包括一引线框架及贴装于所述引线框架上的芯片,所述芯片通过复数条引线与所述引线框架电性连接;每一引线具有与所述芯片连接的一第一端,以及,与所述引线框架连接的一第二端,所述第一端与所述第二端被配置为:所述第一端所在的平面不超过所述第二端所在的平面。

在一些实施例中,每一引线与所述芯片的表面之间具有一垂直距离,所述垂直距离的最大值为该引线与所述芯片的表面的边缘之间的垂直距离。

在一些实施例中,所述引线框架包括至少一个基岛及复数个引脚,其特征在于,所述芯片贴装于所述基岛上,并且,每一引线的所述第二端与一个引脚连接。

在一些实施例中,每一引脚具有一靠近所述基岛的第一端,每一引脚被配置为:每一引脚的表面在所述第一端突出于所述基岛贴装用于贴装所述芯片的表面。

在一些实施例中,一引线的所述第二端与一引脚在该引脚的所述第一端处连接。

在一些实施例中,所述封装体还包括塑封所述引线框架、所述芯片及所述引线的塑封料。

在一些实施例中,塑封料包覆所述芯片及所述引线框架并暴露所述引线框架的部分表面。

在本申请中,通过所述引线框架的结构设计,使得在粗金属引线打线时,所述引线框架不会因打线力量而发生变形,并且,形成的粗金属引线的线弧最高点位于芯片的表面之外,从而不会发生引线接触芯片边缘的情况,因而可以避免短路风险。

附图说明

图1是现有封装产品的结构示意图;

图2是根据本发明一实施例的一引线框架的结构示意图;

图3是根据本发明一实施例的所述框架单元的结构示意图;

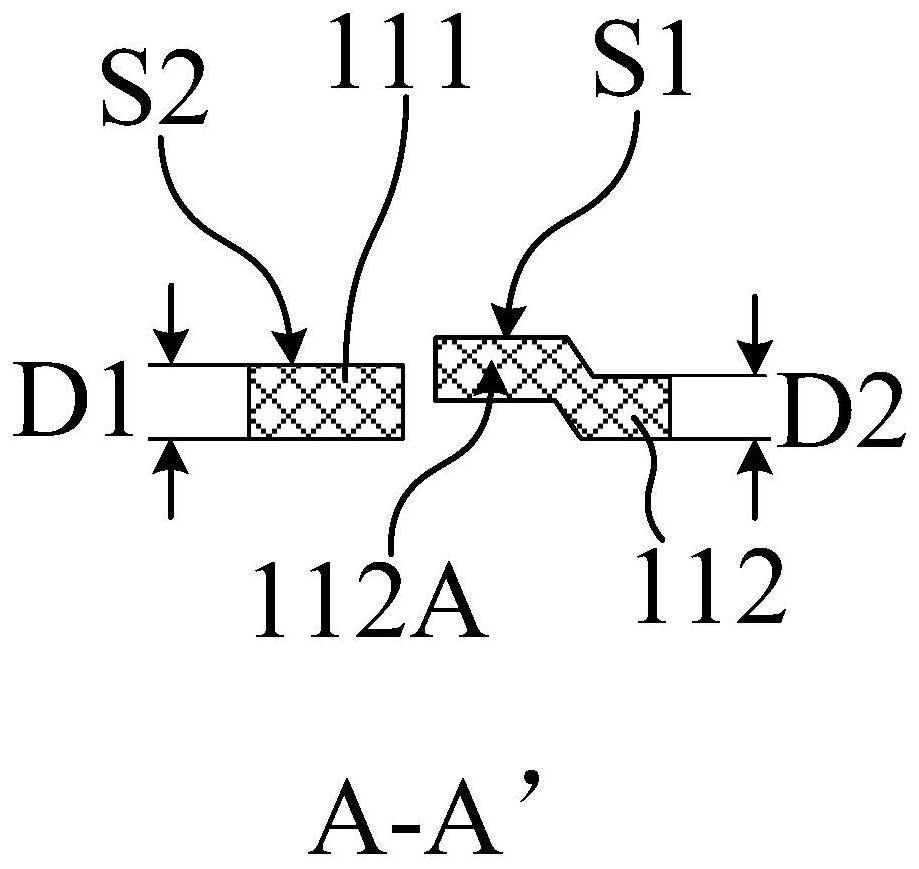

图4是图3中A-A’截面图;

图5是根据本发明一实施例的一封装体的内部结构示意图。

具体实施方式

以下,结合具体实施方式,对本申请的技术进行详细描述。应当知道的是,以下具体实施方式仅用于帮助本领域技术人员理解本申请,而非对本申请的限制。

如图2所示,在本实施例中,首先提供一种引线框架100。本领域技术人员可以理解的是,所述引线框架100包括复数个框架单元110,所述复数个框架单元110通过一外框120连接而形成一体。每一所述框架单元110通过一封装线W界定,相邻的框架单元110之间为一切割道。也就是说,封装线W圈示的区域为框架单元110的区域。在图2中示意性绘示四个框架单元110,本领域技术人员可以理解的是,所述引线框架100可以包含任意多个所述框架单元110。

以下,结合图3及图4,以一个框架单元110作为示范例,详细描述本发明所述引线框架100的具体结构。

如图3所示,所述引线框架100的每一框架单元110包括至少一个基岛111及复数个引脚112。如图3所示,在本实施例中,一框架单元110具有两个所述基岛111,所述复数个引脚112形成两组引脚组,每一基岛111对应一组引脚组。例如,图3中左侧两个引脚112形成一组引脚组并对应左侧所述基岛111,而右侧两个引脚112形成另一组引脚组并对应右侧所述基岛111。

如图3和图4所示,每一引脚112具有一靠近所述基岛111的第一端112A。如图4所示,每一引脚112被配置为:每一引脚112的表面S1在所述第一端112A突出于所述基岛111用于贴装一芯片的表面S2。例如,在图4中所述基岛111的上表面为用于贴装一芯片的表面S2,每一引脚112在所述第一端112A的上表面S1高于所述基岛111用于贴装一芯片的表面S2。

在本实施例中,所述引线框架100的厚度具有一最大值,每一引脚112的厚度等于该最大值。例如,在图4中,所述引线框架100的厚度的最大值等于所述基岛111的厚度D1,即,所述基岛111为全金属结构(非半蚀刻结构),则每一引脚112的厚度D2等于该最大值D1。也就是说,与图1中所示现有封装体使用的引线框架1不同的是,本申请所述引线框架100的每一引脚112均为全金属结构,而非图1中所示的下表面半蚀刻的引脚12。这样,使得本申请所述引线框架100在粗金属引线打线时,所述引脚112能够承受打线力量,因而本申请所述引线框架100的所述引脚112不易发生变形。

如图5所示,在本申请中,提供利用上述引线框架100形成的封装体200。所述引线框架100具有图2和图3所示结构,并且在所述引线框架100上贴装一芯片300,尤其是在所述引线框架100的基岛111上贴装所述芯片300。所述芯片300通过至少一引线400电性连接。本领域技术人员可以理解的是,所述引线400与所述引线框架100的引脚112是对应的,每一引脚112对应一条所述引线400。所述封装体200还包括塑封所述引线框架100、所述芯片300及所述引线400的塑封料500。

本领域技术人员可以理解的是,本申请所述封装体200还具有其他封装体的常规结构,例如,利用所述塑封料500进行封装并切割后,所述封装体200的表面会暴露所述引线框架的部分表面,以形成所述封装体200的引脚。该结构是本领域公知的,在此不再赘述。

如图5所示,所述引线400具有与所述芯片300连接的一第一端401以及与所述引线框架100连接的一第二端402,所述第一端401与所述第二端402被配置为:所述第一端401所在的平面不超过所述第二端402所在的平面。也就是说,在本申请所述的封装体200中,由于如图2和图3所示的结构配置所述引线框架100,使得在形成引线400后,所述引线框架100的引脚112与基岛111的表面落差能够满足在贴装所述芯片300后,所述引线400的第一端401与第二端402基本保持齐平。从而,如图5所示的本申请所述的封装体200不会发生如图1所示现有封装体中金属引线3的接触芯片2的一端明显高于接触引脚12的一端。

如图5所示,所述引线400与所述芯片300的表面之间具有一垂直距离,所述垂直距离的最大值H为该引线400与所述芯片300的表面的边缘之间的垂直距离。也就是说,在本申请所述的封装体200中,所述引线400与所述芯片300之间的距离从两者的接触点开始,在沿着朝向所述芯片300边缘的方向上是逐渐增大的,使得所述引线400的线弧最高处是位于所述芯片300边缘与所述引线框架100的基岛111边缘之间。这样,与图1中所示现有封装体使用的引线框架1不同的是,本申请所述封装体200中的所述引线400的线弧最高点位于所述芯片300的表面之外,因而不会发生如图1所示的引线400存在接触芯片300边缘的情况,因而可以避免短路风险。

本申请已由上述相关实施例加以描述,然而上述实施例仅为实施本申请的范例。必需指出的是,已公开的实施例并未限制本申请的范围。相反地,包含于权利要求书的精神及范围的修改及均等设置均包括于本申请的范围内。

- 引线框架、引线框架的形成方法及引线框架封装体

- 引线框架、QFN封装体、及形成QFN封装体的方法