可调节击穿电压的PN结结构及其制作方法

文献发布时间:2023-06-19 19:35:22

技术领域

本发明涉及半导体技术领域,尤其涉及一种可调节击穿电压的PN结结构及其制作方法。

背景技术

二极管作为半导体技术发展之路的开山鼻祖,目前在集成电路中已经变得边缘化,只有少量模拟电路、传感电路仍会用到二极管。但二极管所包含的半导体势垒结构是所有半导体器件、集成电路必不可少的基础元素。在二极管技术的根基上,不仅发展出了集成电路,二极管还被广泛应用于光电领域。半导体二极管所具有的PN结、肖特基结构是集成电路中必不可少的基础结构。

对于集成电路常用的普通二极管,一般芯片制作完成后,芯片中二极管的击穿电压就已经确定,在实际应用中就无法对二极管的击穿电压进行调整。

发明内容

本发明的目的在于提供一种可调节击穿电压的PN结结构及其制作方法,通过制作电位控制端接不同的电位来调节PN结耗尽区宽度,从而改变PN结的击穿电压。

为达到上述目的,本发明提供一种可调节击穿电压的PN结结构,包括:

PN结的P型区域或者N型区域上依次设置有隔离层和电位控制端,通过电位控制端接不同的电位来调节PN结耗尽区的宽度,改变PN结的击穿电压。

可选的,所述隔离层为栅氧层,所述电位控制端为多晶硅栅极。

可选的,所述隔离层和所述电位控制端形成在N型区域。

可选的,所述N型区域为形成在衬底上的N阱,所述P型区域为形成在所述N阱表面区域的P型离子掺杂区。

可选的,所述N阱表面区域还形成有N型离子掺杂区,作为所述N型区域的引出端。

可选的,所述隔离层和所述电位控制端形成所述N阱上,并位于所述N型离子掺杂区和所述P型离子掺杂区之间。

可选的,所述电位控制端接不同的电位的范围包括-5V~2V。

相应的,本发明还提供一种可调节击穿电压的PN结结构的制作方法,包括:

在衬底的N阱的表面区域形成P型离子掺杂区,形成PN结结构;

在所述N阱上依次形成有隔离层和电位控制端,通过电位控制端接不同的电位来调节PN结耗尽区的宽度,改变PN结的击穿电压。

可选的,其特征在于,所述隔离层为栅氧层,所述电位控制端为多晶硅栅极。

可选的,其特征在于,所述隔离层和所述电位控制端的形成,与CMOS工艺的栅极制作同步。

可选的,其特征在于,还包括:在所述N阱表面区域形成N型离子掺杂区,作为PN结结构的N型区域的引出端。

可选的,其特征在于,所述隔离层和所述电位控制端形成所述N阱上,并位于所述N型离子掺杂区和所述P型离子掺杂区之间。

综上,本发明提供一种可调节击穿电压的PN结结构及其制作方法,通过在PN结的P型区域或者N型区域设置隔离层和电位控制端,通过电位控制端接不同的电位来调节PN结耗尽区宽度,从而改变PN结的击穿电压。且所述隔离层和所述电位控制端,可以通过在集成电路CMOS工艺做栅极时,在二极管PN结的P型或者N型低浓度区域增加栅氧层和多晶硅栅极来实现,通过多晶硅栅极接不同的电位来调节PN结耗尽区宽度,改变PN结击穿电压。

附图说明

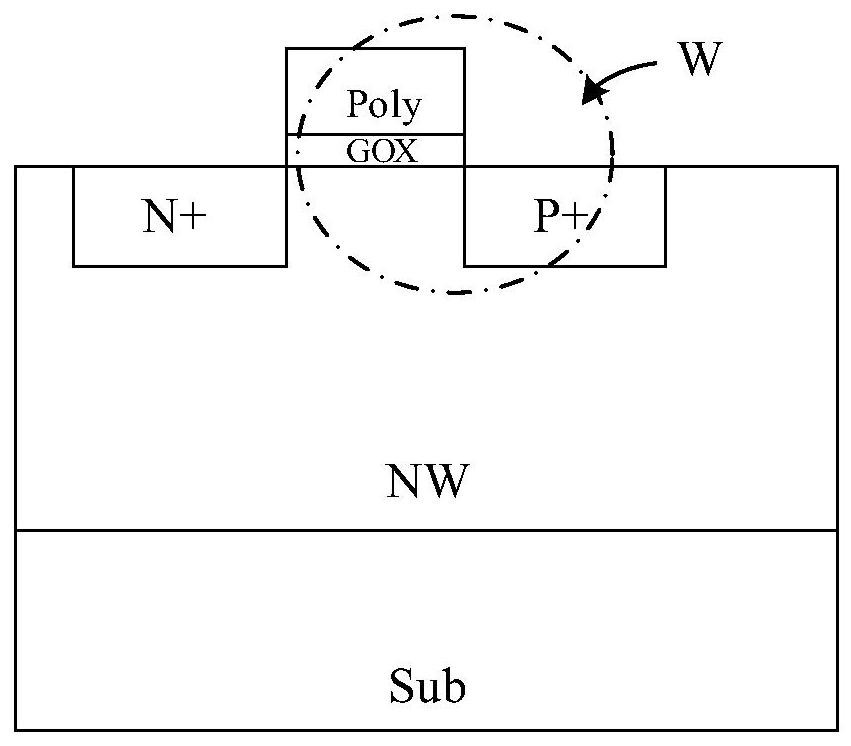

图1为本发明一实施例提供的可调节击穿电压的PN结结构的示意图;

图2为图1中W处的放大图;

图3为PN结的击穿电压随PN结电位控制端接不同电位的变化图。

具体实施方式

为使本发明的内容更加清楚易懂,以下结合说明书附图,对本发明的内容做进一步说明。当然本发明并不局限于该具体实施例,本领域的技术人员所熟知的一般替换也涵盖在本发明的保护范围内。

其次,本发明利用示意图进行了详细的表述,在详述本发明实例时,为了便于说明,示意图不依照一般比例局部放大,不应对此作为本发明的限定。

为了便于描述,本发明一些实施例可以使用诸如“在…上方”、“在…之下”、“顶部”、“下方”等空间相对术语,以描述如实施例各附图所示的一个元件或部件与另一个(或另一些)元件或部件之间的关系。应当理解的是,除了附图中描述的方位之外,空间相对术语还旨在包括装置在使用或操作中的不同方位。例如若附图中的装置被翻转,则被描述为在其它元件或部件“下方”或“之下”的元件或部件,随后将被定位为在其它元件或部件“上方”或“之上”。下文中的术语“第一”、“第二”、等用于在类似要素之间进行区分,且未必是用于描述特定次序或时间顺序。

本实施例提供一种可调节击穿电压的PN结结构,如图1所示,PN结的P型区域或者N型区域上依次形成有隔离层和电位控制端,通过电位控制端接不同的电位来调节PN结耗尽区的宽度,改变PN结的击穿电压。

具体的,所述隔离层为栅氧层(GOX),例如为氧化硅层,所述电位控制端为多晶硅栅极(Poly)。所述隔离层和所述电位控制端可以在集成电路CMOS工艺制作栅极(Gate)时,在普通二极管的PN结的P型区域或者N型区域增加栅氧层和多晶硅栅极,作为隔离层和电位控制端,并通过电位控制端(Poly)接不同的电位来调节PN结的耗尽区宽度,从而改变PN结的击穿电压。

以所述隔离层和所述电位控制端形成在N型区域形成的PN结结构为例,如图1所示,所述N型区域为形成在衬底(Sub)上的N阱(NW),所述P型区域为形成在所述N阱表面区域的P型离子掺杂区(P+)。

进一步的,所述N阱表面区域还形成有N型离子掺杂区(N+),作为所述N型区域的引出端。所述隔离层和所述电位控制端形成所述N阱上,并位于所述N型离子掺杂区(N+)和所述P型离子掺杂区(P+)之间。所述隔离层和所述电位控制端在分布位置和范围可以根据实际需求作相应的调整。

所述电位控制端可以接不同的电位,通过电位控制端(Poly)接不同的电位来调节PN结的耗尽区宽度,进而来改变PN结的击穿电压

如图2所示,当所述电位控制端接0电位(对应A曲线),PN结0偏置时NW耗尽区边界受表面态影响表面载流子浓度高于体内,表面耗尽区较窄;

当所述电位控制端(Poly)接高电位(对应B曲线)时,NW表面电子浓度增加,耗尽区变窄,表面PN结反向击穿电压变低,表面优先击穿;

当所述电位控制端(Poly)接低电位(对应C曲线)时,NW表面电子浓度降低,耗尽区变宽,表面PN结反向击穿电压变高,体内优先击穿。

本实施例中,所述电位控制端接的电位的范围包括-5V~2V,例如为-5V、-3V、2V等,图3为本实例提供的PN结的击穿电压随PN结电位控制端接不同电位的变化图。如图3所示,随着PN结的电位控制端接的电位不同,PN结的击穿电压相应变化。

本实施例提供的可调节击穿电压的PN结结构,通过在PN结的P型区域或者N型区域设置隔离层和电位控制端,通过电位控制端接不同的电位来调节PN结耗尽区宽度,从而改变PN结的击穿电压。

相应的,本实施例还提供一种可调节击穿电压的PN结结构的制作方法,参考图1所示,包括:

在衬底(Sub)的N阱(NW)的表面区域形成P型离子掺杂区(P+),形成PN结结构;

在所述N阱(NW)上依次形成有隔离层和电位控制端,通过电位控制端接不同的电位来调节PN结耗尽区的宽度,改变PN结的击穿电压。

进一步的,PN结结构的制作方法还包括:在所述N阱表面区域形成N型离子掺杂区(N+),作为PN结结构的N型区域的引出端。所述隔离层和所述电位控制端形成所述N阱上,并位于所述N型离子掺杂区(N+)和所述P型离子掺杂区(P+)之间。

进一步的,所述隔离层为栅氧层(GOX),所述电位控制端为多晶硅栅极(Poly),且所述隔离层和所述电位控制端的形成,可以与CMOS工艺的栅极制作同步,节省工艺流程。

综上,本实施例提供的可调节击穿电压的PN结结构的制作方法,通过在集成电路CMOS工艺做栅极,在管PN结的P型或者N型低浓度区域增加栅氧和poly控制端,通过poly端接不同的电位来调节PN结耗尽区宽度,从而改变PN结击穿电压。

需要说明的是,本实施例中仅是在N阱形成P型离子掺杂区,形成PN结结构,在本发明其他实施例中也可以在P阱形成N型离子掺杂区,形成PN结结构,或采用其他方法形成的PN结结构,例如PN结是P+/N-结,还是P-/N+结,本发明不作限制。另外,所述隔离层和所述电位控制端也可以采用其他材和其他工艺方法制成,本发明不作限制。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

- 具有高击穿电压的锗硅异质结双极晶体管结构及其制作方法

- 具有高击穿电压的锗硅异质结双极晶体管结构及其制作方法