用于存储器的驱动电路及存储器

文献发布时间:2024-01-17 01:17:49

技术领域

本发明涉及集成电路技术领域,特别涉及一种用于存储器的驱动电路及存储器。

背景技术

目前,在汽车电子、工业控制等高端应用领域,对芯片的工作可靠性要求越来越高,存储器的读取速度和读取可靠性具有重要意义。

存储器的读取主要是由控制电路和驱动电路实现,控制电路产生的使能信号和驱动电路产生的多路驱动电流均提供给存储电路,而使能信号控制驱动电流与存储电路的路径是否导通,即在使能信号有效的情况下,才能进行数据的读取。在数据读取过程中,要求参考电压稳定,不能有太大波动。但是在读操作开始时刻,即控制使能信号的开关进行切换时,参考电压会受到开关切换噪声的影响,使的参考电压产生波动进而影响驱动电流,而参考电压从这种波动中恢复过来需要一定时间,且恢复时间大于1个读周期时间,因此初始的读操作会基于受干扰的参考电压进行,从而影响读的可靠性。

发明内容

鉴于上述问题,本发明的目的在于提供一种用于存储器的驱动电路及存储器,可以降低使能信号切换时参考电压受到的波动干扰和减少参考电压恢复到目标值的时间,进而提高读取数据的可靠性。

根据本发明的一方面,提供一种用于存储器的驱动电路,包括:参考电压模块,根据电源电压产生参考电压并输出;镜像模块,根据所述参考电压、电源电压产生多路驱动电流;补偿控制模块,在使能信号变为有效状态开始的预设时间内根据所述使能信号产生控制信号;以及补偿模块,与所述参考电压的输出端连接,根据所述控制信号调节所述输出端处的电流,以调节所述参考电压。

可选地,所述补偿控制模块包括:延时单元,其输入端与使能信号连接,用于输出反相延迟信号;第一逻辑单元,用于根据所述使能信号和所述延迟信号产生脉冲信号;第二逻辑单元,用于根据所述脉冲信号产生所述控制信号,其中,所述延时单元对所述使能信号进行预设时间的延迟后反相获得所述反相延迟信号;所述控制信号的有效时间为所述预设时间,在所述使能信号从无效切换到有效时所述控制信号开始有效。

可选地,所述第一逻辑单元包括或非门。

可选地,所述第二逻辑单元包括非门。

可选地,所述补偿模块包括:上拉单元,用于根据所述控制信号产生预设时间的补偿电流。

可选地,所述补偿模块还包括:下拉单元,与所述上拉单元和所述参考电压模块连接,用于降低所述补偿电流。

可选地,所述下拉单元的下拉能力小于所述上拉单元的上拉能力。

可选地,所述上拉单元包括:第一晶体管,所述第一晶体管的第一通路端与电源电压连接,第二通路端与控制端连接;第二晶体管,所述第二晶体管的第一通路端与所述第一晶体管的第二通路端连接,第二通路端与所述参考电压模块的输出端连接,控制端与所述补偿控制模块的输出端连接。

可选地,所述下拉单元包括:第三晶体管,所述第三晶体管的第一通路端和控制端与所述参考电压模块的输出端连接,第二通路端接地。

可选地,所述预设时间不大于一个读周期时间。

可选地,所述参考电压模块包括:电流源,所述电流源的第一通路端与电源电压连接;第四晶体管,所述第四晶体管的第一通路端与所述电源电压连接,第二通路端与控制端连接;第五晶体管,所述第五晶体管的第一通路端与所述电流源的第二通路端连接,第二通路端接地,控制端与第一通路端连接;第六晶体管,所述第六晶体管的第一通路端与所述第四晶体管的第二通路端连接,第二通路端接地,控制端与所述第五晶体管的控制端连接,其中,所述第四晶体管的控制端为所述参考电压模块的输出端。

可选地,所述镜像模块包括:多个镜像晶体管,所述镜像晶体管的第一通路端与电源电压连接,第二通路端输出驱动电流,控制端接收所述参考电压。

可选地,晶体管的第一通路端和第二通路端为源极和漏极或漏极和源极,控制端为栅极。

根据本发明的另一方面,提供一种存储器,包括控制电路,存储电路和如前述所述的驱动电路。

本发明提供的用于存储器的驱动电路及存储器,补偿控制模块根据使能信号从无效切换到有效时的上升沿或下降沿产生的预设时间的控制信号,补偿模块根据控制信号产生补偿电流,通过补偿节点K处的电流进而对节点K处的参考电压进行补偿,从而降低使能信号切换时参考电压受到的波动干扰和减少参考电压恢复到目标值的时间,进而提高读取数据的可靠性。

本发明提供的用于存储器的驱动电路及存储器,补偿控制模块对使能信号进行预设时间的延迟反相,并通过第一逻辑单元产生预设时间的控制信号,以使补偿模块仅在接收到预设时间的控制信号时才产生补偿电流进而对参考电压进行补偿,从而避免了其他时间补偿模块对参考电压的影响。

本发明提供的用于存储器的驱动电路及存储器,补偿模块包括上拉单元和下拉单元,且下拉单元的下拉能力小于上拉单元的上拉能力。通过上拉单元对参考电压进行上拉,通过下拉单元用于对参考电压进行下拉,从而不仅可以实现对参考电压的上拉,同时降低参考电压被上拉单元上拉过高的问题,进一步减少使能信号切换时参考电压受到的波动干扰,进而提高读取数据的可靠性。

附图说明

通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

图1示出了一种用于存储存储器驱动电路的结构示意图;

图2示出了一种用于存储器的参考电压和使能信号的电压波形图;

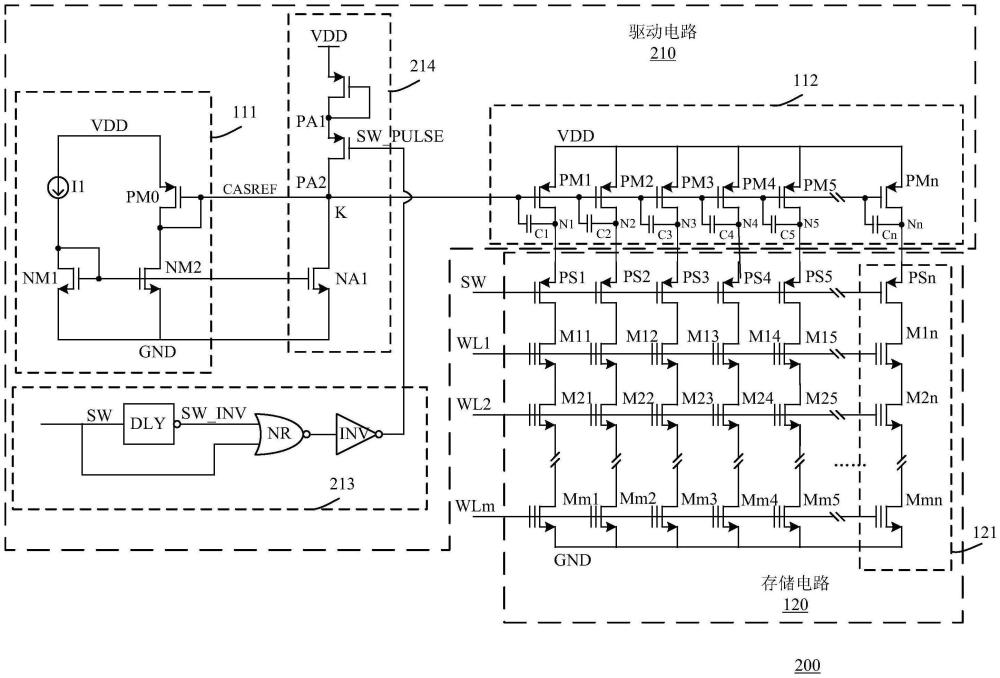

图3示出了根据本发明实施例的一种用于存储器的驱动电路的结构示意图;

图4示出了根据本发明实施例的一种用于存储器的参考电压和使能信号的电压波形图。

具体实施方式

以下将参照附图更详细地描述本发明的各种实施例。在各个附图中,相同的元件采用相同或类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。

下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。

图1示出了一种用于存储存储器驱动电路的结构示意图。参考图1,存储器100包括驱动电路110和存储电路120。

其中,驱动电路110用于根据输入电压DVV产生阵列驱动电流,以驱动存储电路120。存储电路120用于根据驱动电流和使能信号SW进行数据的读取。

具体地,驱动电路110包括参考电压模块111和镜像模块112。参考电压模块111用于产生参考电压CASREF,镜像模块112用于根据参考电压CASREF和电源电压VDD产生多路驱动电流。

镜像模块112包括多个镜像晶体管PM。每个镜像晶体管PM的第一通路端与电源电压连接,第二通路端分别与存储电路120连接,用于给存储电路120提供多路驱动电流,第三通路端与参考电压模块111连接。具体地,镜像晶体管PM的第一通路端和第二通路端例如为源漏端,第三通路端例如为控制端。

存储电路120包括多个存储单元串121,多个存储单元串121组成存储阵列。以图1中的一个存储单元串121为例,存储单元串121的第一通路端连接至驱动电路110的驱动电流,第二通路端接地GND。存储单元串121包括在第一通路端和第二通路端之间串联连接的多个晶体管,包括选择晶体管PS和多个存储晶体管M1至Mm。其中,选择晶体管PS位于驱动电路110与多个存储晶体管M之间,选择晶体管PS的控制端连接至使能信号SW,存储晶体管M1至Mm的控制端分别连接至字线WL1至WLm的相应字线。使能信号SW控制选择晶体管PS的导通与关断。具体地,使能信号SW用于控制数据读取路径的导通与关断,当使能信号SW有效时,存储电路120根据驱动电流进行数据的读取;当使能信号SW无效时,存储电路120不能进行数据的读取。

在该实施例中,驱动电路110产生的多路驱动电流,并提供给存储电路120中存储单元串121,当存储单元串121中选择晶体管PS控制端连接的使能信号SW有效时,选择晶体管PS导通,而镜像晶体管PM与存储电路120的中间节点N被拉低,并通过镜像晶体管PM第二通路端与第三通路端之间的寄生电容C使参考电压CASREF也被拉低,进而导致驱动电路110输出的多路驱动电流发生变化,如图2所示。参考电压CASREF在时间段T内低于目标稳定值,而从这种波动中恢复过来需要一定时间,恢复时间大于1个读周期时间,所以第1个读动作会基于受干扰的参考电压CASREF进行,影响了读的可靠性。在该实施例中,使能信号SW控制选择晶体管PS的导通与关断,在以下内容中,采用使能信号SW的开关切换来表示使能信号SW有效或无效变换时控制选择晶体管PS的导通与关断变换的状态。

本申请的发明人注意到上述问题,提出了一种存储器驱动电路及存储器,以降低使能信号SW切换中参考电压CASREF受到波动干扰。

图3示出了根据本发明实施例的一种用于存储器的驱动电路的结构示意图。参考图3,本申请的存储器200包括控制电路,驱动电路210和存储电路120。

其中,驱动电路210用于根据输入电压DVV产生阵列驱动电流,以驱动存储电路120。控制电路用于提供使能信号和字线电压。存储电路120用于根据驱动电流和使能信号SW进行数据的读取。

具体地,驱动电路210包括参考电压模块111,镜像模块112,补偿控制模块213以及补偿模块214。参考电压模块111用于产生参考电压CASREF。补偿控制模块213以及补偿模块214用于产生补偿电流以调节参考电压CASREF。镜像模块112用于根据调节后的参考电压CASREF和电源电压VDD产生多路驱动电流。在该实施例中,参考电压CASREF例如为节点K的电压,即节点K既与参考电压模块111的输出端和镜像模块112的输入端连接,还与补偿模块214的输出端连接。

在该实施例中,参考电压模块111包括电流源I1,第四晶体管PM0,第五晶体管NM1和第六晶体管NM2。电流源I1的第一通路端和第四晶体管PM0的第一通路端均与输入电压VDD连接;电流源I1的第二通路端与第五晶体管NM1的第一通路端连接;第四晶体管PM0的第二通路端与第六晶体管NM2的第一通路端连接,第四晶体管PM0的控制端与第二通路端连接;第五晶体管NM1的第二通路端和第六晶体管NM2的第二通路端连接且接地,同时第五晶体管NM1的控制端和第六晶体管NM2的控制端连接,以使第五晶体管NM1和第六晶体管NM2采用共源共栅结构,从而将第五晶体管NM1所在支路中的电流镜像到第六晶体管NM2所在的之路中。第五晶体管NM1的第一通路端与第二段连接。在该实施例中,第四晶体管PM0的控制端例如为参考电压模块111的输出端,其输出的信号为参考电压CASREF。其中,第四晶体管PM0,第五晶体管NM1和第六晶体管NM2的第一通路端和第二通路端例如为源漏极,控制端例如为栅极。

镜像模块112包括多个镜像晶体管PM。每个镜像晶体管PM的第一通路端与电源电压连接,第二通路端分别与存储电路120连接,用于给存储电路120提供多路驱动电流,第三通路端与参考电压模块111连接,接收参考电压CASREF。镜像模块112的每个镜像晶体管PM均与第四晶体管PM0采用共源共栅结构,从而将第四晶体管所在支路中的电流镜像到镜像晶体管PM所在的之路中,形成驱动电流。具体地,镜像晶体管PM的第一通路端和第二通路端例如为源漏端,第三通路端例如为控制端。

补偿控制模块213用于根据使能信号SW产生控制信号SW_PULSE,具体地,补偿控制模块213包括延时单元DLY,第一逻辑单元NR和第二逻辑单元INV。其中,参考图4,所述延时单元DLY用于将使能信号SW延迟预设时间T并反相从而获得延迟反相信号SW_INV;第一逻辑单元NR用于根据使能信号SW和延迟反相信号SW_INV产生脉冲信号;第二逻辑单元INV用于根据脉冲信号产生控制信号SW_PULSE。

在该实施例中,所述延时单元DLY例如为一个延时反相器,其输入端与使能信号SW连接,输出信号为延迟反相信号SW_INV;第一逻辑单元NR例如为一个与非门,其第一输入端与延时单元DLY的输出端连接,第二输入端与使能信号SW连接,输出信号为脉冲信号;第二逻辑单元INV例如为一个非门,其输入端与第一逻辑单元NR的输出端连接,用于将第一逻辑单元NR输出的第一控制信号进行反相,输出信号为控制信号SW_PULSE。

进一步地,延时单元DLY对使能信号SW进行预设时间T的延迟,该预设时间T例如不大于参考电压CASREF在使能信号SW开关操作中受到干扰而进行回复所需的时间。在其他实施例中,预设时间T也可以根据具体情况进行调节。

补偿模块214包括上拉单元和下拉单元,上拉单元包括第一晶体管PA1和第二晶体管PA2。第一晶体管PA1的第一通路端与电源电压VDD连接,第二通路端与第二晶体管PA2的第一通路端连接,同时第一晶体管PA1的控制端与第二通路端连接;第二晶体管PA2的第二通路端与中点节点K连接,控制端与补偿控制模块213的输出端连接。在该实施例中,第一晶体管PA1和第二晶体管PA2的第一通路端和第二通路端例如为源漏极,控制端例如为栅极。

在该实施例中,当使能信号SW进行开关切换时,补偿控制模块213根据使能信号SW从无效切换到有效时的上升沿或下降沿产生预设时间T的控制信号SW_PULSE,补偿模块214根据预设时间T的控制信号SW_PULSE产生对应的补偿电流,补偿电流改变节点K的电流值,从而对节点K的参考电压CASREF进行补偿。

进一步地,补偿模块214的下拉单元的下拉能力小于上拉单元的上拉能力,用于降低节点K的参考电压CASREF被补偿后电压值过高的几率。

具体地,下拉单元例如包括第三晶体管NA1,第三晶体管NA1的第一通路端与节点K连接,第二通路端接地,控制端与参考电压模块111中第六晶体管NM2的控制端连接。在该实施例中,第三晶体管NA1的第一通路端和第二通路端例如为源漏极,控制端例如为栅极。

本申请的用于存储器的驱动电路,补偿控制模块213根据使能信号产生预设时间的控制信号SW_PULSE,补偿模块214根据控制信号SW_PULSE产生补偿电流,通过补偿电流调节节点K的电流值从而对参考电压CASREF进行补偿,以降低参考电压CASREF在使能信号SW的开关操作中受到的干扰,从而提高数据读取的可靠性。

在该实施例中,第一晶体管PA1,第二晶体管PA2和第四晶体管PM0例如为P型晶体管,第三晶体管NA1,第五晶体管NM1和第六晶体管NM2例如为N型晶体管。

存储电路120包括多个存储单元串121,多个存储单元串121组成存储阵列。以图3中的一个存储单元串121为例,存储单元串121的第一通路端连接至驱动电路110的驱动电流,驱动电流为镜像模块112的输出电流,第二通路端接地GND。存储单元串121包括在第一通路端和第二通路端之间串联连接的多个晶体管,包括选择晶体管PS和多个存储晶体管M1至Mm。其中,选择晶体管PS位于驱动电路110与多个存储晶体管M之间,选择晶体管PS的控制端连接至使能信号SW,存储晶体管M1至Mm的控制端分别连接至字线WL1至WLm的相应字线。使能信号SW控制选择晶体管PS的导通与关断。具体地,使能信号SW用于控制数据读取路径的导通与关断,当使能信号SW有效时,存储电路120根据驱动电流进行数据的读取;当使能信号SW无效时,存储电路120不能进行数据的读取。

在该实施例中,当参考电压CASREF受到使能信号SW的开关切换影响后,若自行恢复需要的时间为T1,而本申请的补偿控制模块和补偿模块可以根据使能信号SW产生一个预设时间T2的补偿电流,不仅降低参考电压CASREF受到的影响,而且降低了参考电压CASREF恢复到目标值的时间。在该实施例中,时间T1大于一个读周期时间,预设时间T2小于一个读周期时间。

本申请还提供一种存储器,包括控制电路,驱动电路210以及存储电路120。控制电路用于产生使能信号SW和字线WL电压等,驱动电路210用于产生多路驱动电流,存储电路120用于根据使能信号SW、字线WL电压以及多路驱动电流进行数据的读取。

本发明提供的存储器驱动电路及存储器,补偿控制模块根据使能信号从无效切换到有效时的上升沿或下降沿产生的预设时间的控制信号,补偿模块根据控制信号产生补偿电流,通过补偿节点K处的电流进而对节点K处的参考电压进行补偿,从而减少使能信号切换时参考电压受到的波动干扰,进而提高读取数据的可靠性。

本发明提供的存储器驱动电路及存储器,补偿控制模块对使能信号进行预设时间的延迟反相,并通过第一逻辑单元产生预设时间的控制信号,以使补偿模块仅在接收到预设时间的控制信号时才产生补偿电流进而对参考电压进行补偿,从而避免了其他时间补偿模块对参考电压的影响。

本发明提供的存储器驱动电路及存储器,补偿模块包括上拉单元和下拉单元,且下拉单元的下拉能力小于上拉单元的上拉能力。通过上拉单元对参考电压进行上拉,通过下拉单元用于对参考电压进行下拉,从而不仅可以实现对参考电压的上拉,同时降低参考电压被上拉单元上拉过高的问题,进一步减少使能信号切换时参考电压受到的波动干扰,进而提高读取数据的可靠性。

依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

- 用于分布式存储器危险检测和错误恢复的存储器电路和方法

- 一种存储器及其数据读出驱动电路

- 集成电路系统、包括存储器单元串的存储器阵列、用于形成集成电路系统的方法和用于形成包括存储器单元串的存储器阵列的方法

- 半导体存储器件的子字线驱动器电路和包括该子字线驱动器电路的半导体存储器件