用于3D NAND应用的存储单元制造

文献发布时间:2023-06-19 11:55:48

技术领域

本公开内容的实施方式大体涉及制造垂直型存储单元半导体装置的方法,并且更具体地涉及制造用于半导体制造应用的具有阶梯状(stair-like)结构的垂直型存储单元半导体装置的方法。

背景技术

对于半导体装置的下一代超大规模集成电路(very large scale integration,VLSI)和极大规模集成电路(ultra large-scale integration,ULSI)而言,可靠地产生亚半微米(sub-halfmicron)和较小的特征是关键的技术挑战之一。然而,随着电路技术的极限的不断推进,VLSI和ULSI互连技术的缩小尺寸对处理能力提出了额外的要求。在基板上可靠地形成栅极结构对于VLSI和ULSI的成功以及对提高电路密度和单个基板和裸片(die)品质的持续努力至关重要。

图案化的掩模(诸如光刻胶层)通常用于藉由蚀刻处理在基板上形成结构(诸如栅极结构、浅槽隔离(shallow trench isolation,STI)、咬合线(bite line)和类似者)。图案化的掩模传统地藉由使用光刻处理将具有期望的临界尺寸的图案光学转移到光刻胶层上来制造。将光刻胶层接着显影,以移除光刻胶的不期望部分,从而在剩余的光刻胶中产生开口。

为了使得能够制造下一代装置和结构,通常利用半导体存储芯片(memory chip)的三维(3D)堆叠来提高晶体管的性能。藉由以三维尺寸代替传统的二维尺寸布置晶体管,可将多个晶体管彼此非常靠近地放置在集成电路(IC)中。半导体芯片的三维(3D)堆叠可减少导线长度并保持较低的布线延迟(wiring delay)。在制造半导体芯片的三维(3D)堆叠中,通常利用阶梯状结构以允许在其上设置多个互连结构,从而形成高密度的垂直晶体管装置。

当在设置于基板上的膜堆叠中形成阶梯状结构时,重复执行蚀刻处理以及光刻胶修整(trimming)处理,以藉由顺序地修整的光刻胶层作为蚀刻掩模来蚀刻膜堆叠。在图1A中描绘的示例性实施方式中,修整的光刻胶层(未示出)可用作蚀刻掩模层,以将结构转移到设置在基板104上的膜堆叠120上,以在基板104上形成阶梯状结构110,用于形成半导体装置100。膜堆叠120通常包括层120a、120b(显示为120a

在基板104上制造阶梯状结构110期间,在阶梯状结构110中形成的每个阶梯都具有其预期的宽度,以允许在其上形成沟道(channel)125(如,开口),如图1A和图1B所示。在需要更高的装置性能的一些实施方式中,可利用不同材料的交替层120a、120b。例如,当需要更高的装置性能的电迁移率时,通常在阶梯状结构110中使用金属导电材料。在一个实例中,可从阶梯状结构110中移除交替层120a、120b的第二层120b(在图1B中显示为120b

因此,存在有用于形成具有精确轮廓和尺寸控制的阶梯状结构,以用于半导体装置的三维(3D)堆叠的改进方法和设备的需求。

发明内容

本公开内容的实施方式提供一种用于形成具有精确轮廓和尺寸控制的阶梯状结构的设备和方法,用于制造三维(3D)堆叠的存储单元半导体装置。在一个实施方式中,一种存储单元装置包括:膜堆叠,所述膜堆叠包括在基板上水平地形成的交替对的介电层和导电结构;和开口,所述开口形成在膜堆叠中,其中开口填充有金属介电层、多层结构和中心填充层,其中开口中的金属介电层与导电结构界面连接(interfaced)。

在另一个实施方式中,一种在基板上的存储装置的方法,包括以下步骤:在包括第一层和第二层的膜堆叠中形成开口;选择性地氧化第一层,以在第一层的侧壁上形成氧化层;用包括金属介电层的一个或多个层填充开口;从膜堆叠选择性地移除第一层,以暴露氧化层;从膜堆叠选择性地移除氧化层,以在膜堆叠中界定空间;和以导电结构填充空间。

在又一个实施方式中,一种在基板上形成阶梯状结构的方法,包括以下步骤:选择性地氧化包括第一层和第二层的膜堆叠中的第一层;形成与氧化层接触的金属介电层;选择性地移除第一层,以暴露氧化层;从膜堆叠移除氧化层;和形成与金属介电层接触的导电结构。

附图说明

为了可详细地理解本公开内容的上述特征的方式,可藉由参考实施方式来对上文简要概述的本公开内容进行更详细的描述,其中一些实施方式显示在随图中。然而,应当注意随图仅显示了本公开内容的典型实施方式且因此不应被认为是对其范围的限制,因为本公开内容可允许其他等效的实施方式。

图1A描绘了形成在基板上的传统阶梯状结构的示意性截面图;

图1B和图1C描绘了在图1A的基板上形成的传统阶梯状结构的局部示意性截面图;

图2描绘了根据本公开内容的一个实施方式的用于以阶梯状结构在基板上形成含金属层的设备;

图3描绘了根据本公开内容的一个实施方式的用于在基板上形成阶梯状结构的设备;

图4描绘了包括图2和图3的设备的群集处理系统的示意图;

图5描绘了根据本公开内容的一个实施方式的用于在基板上形成的存储单元结构的方法的流程图;和

图6A-图6B、图7、图8A-图8B、图9A-图9B、图10A-图10B、图11A-图11B、图12A-图12B、图13A-图13C和图14A-图14C描绘了根据图5所描绘的实施方式的用于制造在基板上形成的存储单元结构的顺序。

为促进理解,在可能的情况下使用了相同的元件符号来表示各图共有的相同元件。可预期的是一个实施方式的元件和特征可被有益地并入其他实施方式中,而无需进一步叙述。

然而,要注意的是,随图仅显示了本公开内容的示例性实施方式,且因此不应被认为是对其范围的限制,因为本公开内容可允许其他等效的实施方式。

具体实施方式

本公开内容提供了用于在基板上形成阶梯状结构的方法,用于半导体装置的三维(3D)存储单元。在一个实例中,可藉由在界面处利用保护性氧化层(如,牺牲氧化层)以及选择性沉积和选择性图案化/蚀刻处理来获得在制造期间的良好的界面管理、优异的电性能和良好的处理控制。在一个实例中,一种形成用于三维(3D)堆叠的半导体装置的存储单元的方法可在当从膜堆叠移除某种类型的材料以形成阶梯状结构时,利用保护/牺牲氧化层。因此,在移除处理期间,界面可保持受保护和完整,从而提供界面轮廓和形貌的良好控制。结果,当随后在其中形成导电结构时,可在界面处获得良好的电接触,从而为存储单元提供期望的电性能。

图2是适合用于执行等离子体沉积处理(如,等离子体增强CVD或金属有机CVD)的等离子体处理腔室232的截面图,等离子体沉积处理可用作半导体装置制造的半导体互连结构。处理腔室232可为可从加州圣克拉拉市的应用材料公司购得的适合的

处理腔室232包括腔室主体251。腔室主体251包括界定内部容积226的盖225、侧壁201和底壁222。

在腔室主体251的内部容积126中提供了基板支撑基座250。基座250可由铝、陶瓷、氮化铝和其他合适的材料制成。在一个实施方式中,基座250由陶瓷材料(诸如氮化铝)制成,陶瓷材料是适合在高温环境(诸如等离子体处理环境)中使用的材料,而不会引起基座250的热损坏。可使用升降机构(未示出)使基座250在腔室主体251内侧沿垂直方向移动。

基座250可包括适于控制支撑在基座250上的基板290的温度的嵌入式加热器元件270。在一个实施方式中,可藉由将来自电源206的电流施加到加热器元件270而电阻式加热基座250。在一个实施方式中,加热器元件270可由封装在镍铁铬合金(如,

温度传感器272(诸如热电偶)可嵌入在基板支撑基座250中,以传统方式监控基座250的温度。控制器210使用测得的温度来控制供应给加热器元件270的功率,以将基板保持在期望的温度。

基座250通常包括穿过其中设置的多个升降销(未示出),升降销被配置成从基座250升降基板290,并以传统方式促进与机械手(未示出)交换基板290。

基座250包括用于将基板290保持在基座250上的至少一个电极292。电极292由吸附功率源(chucking power source)208驱动,以产生将基板290保持到基座表面的静电力,如众所皆知地。或者,可藉由夹持(clamping)、真空或重力将基板290保持到基座250。

在一个实施方式中,基座250被配置成具有嵌入其中的电极292的阴极,电极292耦合到至少一个RF偏压功率源,在图2中显示为两个RF偏压功率源284、286。尽管图2中描绘的实例显示了两个RF偏压功率源284、286,但应注意RF偏压功率源的数量可根据需要为任意数量。RF偏压功率源284、286耦合在设置在基座250中的电极292与另一电极(诸如处理腔室232的气体分配板242或盖225)之间。RF偏压功率源284、286激发并维持由设置在处理腔室232的处理区域中的气体所形成的等离子体放电。

在图2所描绘的实施方式中,双RF偏压功率源284、286通过匹配电路204耦合到设置在基座250中的电极292。RF偏压功率源284、286产生的信号是通过单次馈送而通过匹配电路204输送到基座250,以使提供在等离子体处理腔室232中的气体混合物离子化,从而提供用于执行沉积或其他等离子体增强处理所需的离子能量。RF偏压功率源284、286通常能够产生具有从约50kHz到约200MHz的频率及在约0瓦与约5000瓦之间的功率的RF信号。

真空泵202耦合到形成在腔室主体251的底部222中的端口(port)。真空泵202用于维持腔室主体251中的期望气体压力。真空泵202还从腔室主体251排空后处理气体和处理的副产物。

处理腔室232包括通过处理腔室232的盖225耦合的一个或多个气体输送通道244。气体输送通道244和真空泵202位于处理腔室232的相对端以在内部容积226内引起层流,以最小化颗粒污染。

气体输送通道244通过远程等离子体源(RPS)248耦合到气体面板293,以将气体混合物提供到内部容积226中。在一个实施方式中,通过气体输送通道244供应的气体混合物可进一步通过设置在气体输送通道244下方的气体分配板242输送。在一个实例中,具有多个孔243的气体分配板242在基座250上方耦合至腔室主体251的盖225。气体分配板242的孔243用于将来自气体面板293的处理气体引入到腔室主体251中。孔243可具有不同的尺寸、数量、分布、形状、设计和直径,以促进用于不同处理要求的各种处理气体的流动。等离子体由离开气体分配板242的处理气体混合物形成,以增强处理气体的热分解,从而导致材料沉积在基板290的表面291上。

气体分配板242和基板支撑基座250可在内部容积226中形成一对间隔开的电极。一个或多个RF源247通过匹配网络245向气体分配板242提供偏压电势,以促进在气体分配板242和基座250之间产生等离子体。或者,RF源247和匹配网络245可耦合到气体分配板242、基板支撑基座250,或耦合到气体分配板242和基板支撑基座250两者,或耦合到设置在腔室主体251外部的天线(未示出)。在一个实施方式中,RF源247可以约30kHz至约13.6MHz的频率在约10瓦与约3000瓦之间提供。或者,RF源247可为微波发生器,其向气体分配板242提供微波功率,微波功率有助于在内部容积226中产生等离子体。

可从气体面板293供应的气体的实例可包括含硅气体、氟连续气体、含氧气体、含氢气体惰性气体和载气。反应气体的合适实例包括含硅气体(诸如SiH

在一个实施方式中,远程等离子体源(RPS)248可被替代地耦合到气体输送通道244,以帮助从由气体面板293供应到内部容积226中的气体形成等离子体。远程等离子体源248将由气体面板293提供的气体混合物形成的等离子体提供给处理腔室232。

控制器210包括中央处理单元(CPU)212、存储器216和支持电路214,其用于控制处理顺序并调节来自气体面板293的气体流量。CPU 212可为可在工业环境中使用的任何形式的通用计算机处理器。软件程序可存储在存储器216(诸如随机存取存储器、只读存储器)、软盘或硬盘驱动器,或其他形式的数字存储器中。支持电路214按传统方式耦合到CPU 212,并且可包括高速缓冲存储器(cache)、时钟电路、输入/输出系统、电源和类似者。在控制器210和处理腔室232的各个部件之间的双向通信通过统称为信号总线(signal bus)218的众多信号电缆进行处理,其中一些信号电缆如图2所示。

图3是用于蚀刻金属层的示例性处理腔室300的简化剖视图。示例性处理腔室300适于从基板290移除一个或多个膜层。可适于从本发明中受益的处理腔室的一个实例是可从位于加州圣克拉拉市的应用材料公司获得的AdvantEdge Mesa Etch处理腔室。预期其他处理腔室(包括来自其他制造商的那些处理腔室)可适于实践本发明的实施方式。

处理腔室300包括腔室主体305,腔室主体305中界定有腔室容积301。腔室主体305具有耦合至接地326的侧壁312和底部318。侧壁312具有衬里315以保护侧壁312并延长在处理腔室300的维护周期之间的时间。处理腔室300的腔室主体305和相关部件的尺寸不受限制,并且通常成比例地大于要在其中处理的基板290的尺寸。基板尺寸的实例包括200mm的直径、250mm的直径、300mm的直径和450mm的直径及其他。

腔室主体305支撑腔室盖组件310以封闭腔室容积301。腔室主体305可由铝或其他合适的材料制成。基板进入端口313通过腔室主体105的侧壁312而形成,以促进基板290进出处理腔室300的传送。进入端口313可耦合到传送腔室和/或基板处理系统(未示出)的其他腔室。

泵送端口345通过腔室主体305的侧壁312而形成,并连接到腔室容积301。泵送装置(未示出)通过泵送端口345耦合到腔室容积301,以抽空并控制其中的压力。泵送装置可包括一个或多个泵和节流阀。

气体面板360藉由气体管线367耦合到腔室主体305,以将处理气体供应到腔室容积301中。气体面板360可包括一个或多个处理气体源361、362、363、364,并且若需要的话,还可包括惰性气体、非反应性气体和反应性气体。气体面板360可提供的处理气体的实例包括(但不限于)含烃气体(包括甲烷(CH

阀366控制来自气体面板360的源361、362、363、364的处理气体的流量,并由控制器365管理。从气体面板360供应给腔室主体305的气体的流量可包括气体的组合。

盖组件310可包括喷嘴314。喷嘴314具有一个或多个端口,用于将来自气体面板360的源361、362、364、363的处理气体引入腔室容积301中。在处理气体被引入处理腔室300中之后,气体被能量化(energized)以形成等离子体。可在处理腔室300附近提供天线348,诸如一个或多个感应线圈。天线电源342可通过匹配电路341为天线348供电,以将能量(诸如RF能量)感应耦合到处理气体,以保持由处理腔室300的腔室容积301中的处理气体所形成的等离子体。替代地,或者除了天线电源342之外,基板290下方和/或基板290上方的处理电极可用于将RF功率电容耦合到处理气体,以保持腔室容积301内的等离子体。天线电源342的操作可由控制器(诸如控制器365)控制,控制器还控制处理腔室300中的其他部件的操作。

基板支撑基座335设置在腔室容积301中,以在处理期间支撑基板290。基板支撑基座335可包括用于在处理期间保持基板290的静电吸盘322。静电吸盘(ESC)322利用静电吸引力将基板290保持到基板支撑基座335。ESC 322由集成有匹配电路324的RF电源325供电。ESC 322包括嵌入介电主体内的电极321。RF电源325可向电极321提供约200伏特至约2000伏特的RF吸附电压。RF电源325还可包括系统控制器,用于藉由将DC电流引导至电极321来控制电极321的操作,用于吸附和解吸附(de-chucking)基板290。

ESC 322还可包括设置在其中的电极351。电极351耦合到功率源350,并且提供偏压,该偏压将由腔室容积301中的处理气体所形成的等离子体离子吸引到ESC 322和位于其上的基板290。功率源350可在基板290的处理期间循环打开和关闭,或者脉冲。ESC 322具有隔离器328,其目的是使ESC 322的侧壁对等离子体的吸引力较小,从而延长了ESC 322的维护寿命循环。另外,基板支撑基座335可具有阴极衬里336,以保护基板支撑基座335的侧壁免受等离子体气体的影响并延长在处理腔室300的维护之间的时间。

ESC 322可包括设置在其中的加热器,并且所述加热器连接到功率源(未示出),用于加热基板,而支撑ESC 322的冷却基座329可包括用于使传热流体循环的导管,以维持ESC322和设置在其上的基板290的温度。ESC 322被配置为在被制造在基板290上的装置的热预算所要求的温度范围中执行。例如,对于某些实施方式而言,ESC 322可被配置为将基板290维持在约负25摄氏度到约500摄氏度的温度下。

提供冷却基座329以帮助控制基板290的温度。为了减轻处理漂移和时间,在基板290在处理腔室300中的整个时间内,可藉由冷却基座329将基板290的温度保持实质上恒定。在一个实施方式中,在整个随后的蚀刻处理中,基板290的温度保持在约70至90摄氏度下。

盖环330设置在ESC 322上并沿着基板支撑基座335的外围。盖环330被配置成将蚀刻气体限制到基板290的暴露顶表面的期望部分,同时使基板支撑基座335的顶表面与处理腔室300内侧的等离子体环境屏蔽。升降销(未示出)选择性地移动通过基板支撑基座335,以将基板290提升到基板支撑基座335上方,以促进藉由传送机械手(未示出)或其他合适的传送机构存取基板290。

控制器365可用于控制处理顺序、调节从气体面板360进入处理腔室300中的气体流量和其他处理参数。软件程序(当由CPU执行时)将CPU转换成控制处理腔室300的专用计算机(控制器),使得根据本发明执行处理。软件程序也可由与处理腔室300并置的第二控制器(未示出)存储和/或执行。

基板290具有设置在其上的各种膜层,各种膜层可包括至少一个金属层。各种膜层可能需要对于基板290中其他膜层的不同组成而言是唯一的蚀刻配方(recipe)。位于VLSI和ULSI技术核心的多层互连件(multilevel interconnect)可能需要制造高深宽比的特征,诸如过孔(via)和其他互连件。构建多层互连件可能需要一种或多种蚀刻配方,以在各种膜层中形成图案。这些配方可在单个蚀刻处理腔室中或经由若干蚀刻处理腔室执行。每个蚀刻处理腔室可被配置成利用一种或多种蚀刻配方进行蚀刻。在一个实施方式中,处理腔室300被配置成至少蚀刻金属层,以形成导电结构。对于本文提供的处理参数而言,处理腔室300被配置成处理300的直径的基板,亦即,具有约0.0707m

图4描绘了可实践本文描述的方法的半导体处理系统400的平面图。可适于从本发明中受益的一个处理系统是300mm或450mm的

串联处理腔室406的每一个包括两个用于处理基板的处理区域。两个处理区域共享共同的气体供应、共同的压力控制和共同的处理气体排气/抽气系统。系统的模块化设计实现从一种配置到任何其他配置的快速转换。为了执行特定处理步骤,可改变腔室的布置和组合。串联处理腔室406中的任一个都可包括如下所述的根据本发明的方面的盖,盖包括以上参照图2和/或图3中描绘的处理腔室232、300描述的一个或多个腔室配置。应注意处理系统400可被配置成根据需要执行沉积处理、蚀刻处理、固化处理或加热/退火处理。在一个实施方式中,可将处理腔室232、300(显示为图2和图3中设计的单个腔室)结合到半导体处理系统400中。

在一个实施方式中,处理系统400可适配一个或多个串联处理腔室,串联处理腔室具有支撑腔室硬件,支撑腔室硬件已知可适应各种其他已知处理,诸如化学气相沉积(CVD)、物理气相沉积(PVD)、蚀刻、固化或加热/退火和类似者。例如,系统400可被配置有图2中的处理腔室232之一作为用于沉积(诸如金属膜)的等离子体沉积腔室,或图3中描绘的处理腔室300之一作为用于蚀刻形成在基板上的材料层的等离子体蚀刻腔室。此种配置可最大程度地提高研究和开发制造的利用率,且若需要的话,可消除当膜被蚀刻时暴露于大气。

控制器440(包括中央处理单元(CPU)444、存储器442和支持电路446)耦合到半导体处理系统400的各个部件,以促进控制本发明的处理。存储器442可为在半导体处理系统400或CPU 444本地或远程的任何计算机可读介质(诸如随机存取存储器(RAM)、只读存储器(ROM)、软盘、硬盘或任何其他形式的数字存储器)。支持电路446耦合到CPU 444,用于以传统方式支持CPU。这些电路包括高速缓冲存储器、电源、时钟电路、输入/输出电路和子系统和类似者。当由CPU 444执行时,存储在存储器442中的软件程序或一系列程序指令执行串联处理腔室406。

图5是用于在设置在基板上的膜堆叠中形成存储单元结构的方法500的一个实施方式的流程图,方法可在处理腔室(诸如并入系统400中的图2中描绘的处理腔室232和图3中描绘的处理腔室300,或根据需要的其他合适的处理腔室和系统)中执行。图6A-图6B、图7、图8A-图8B、图9A-图9B、图10A-图10B、图11A-图11B、图12A-图12B、图13A-图13B和图14A-图14B是示意性截面图,显示了根据方法500用于形成设置在基板上的膜堆叠中的存储单元结构的顺序。尽管下文将参照用于在三维半导体装置的膜堆叠中制造存储单元结构的基板来描述方法500,但方法500也可以用于在其他装置制造应用中获利。

方法500藉由提供基板(诸如其上形成有膜堆叠604的基板602)开始于操作502处,如图6A所示。基板602可为硅基材料或根据需要的任何合适的绝缘材料或导电材料,具有设置在基板602上的膜堆叠604,膜堆叠604可用于在膜堆叠604中形成存储单元结构。

如图6A中描绘的示例性实施方式所示,基板602可具有实质上平坦的表面、不平坦表面或具有在其上形成的结构的实质上平坦的表面。膜堆叠604形成在基板602上。在一个实施方式中,膜堆叠604可在前端或后端处理中用于形成栅极结构、接触结构或互连结构。方法500可形成在膜堆叠604上,以在其中形成用于存储单元结构(诸如,VNAND结构)中的阶梯状结构。在一个实施方式中,基板602可为诸如晶体硅(如,Si<100>或Si<111>)、氧化硅、应变硅、硅锗、掺杂或未掺杂的多晶硅、掺杂或未掺杂的硅晶片和图案化或未图案化的绝缘体上硅晶片(SOI)、碳掺杂的氧化硅、氮化硅、掺杂的硅、锗、砷化镓、玻璃、蓝宝石的材料。基板602可具有各种尺寸,诸如200mm、300mm、450mm或其他直径的晶片,以及矩形或正方形面板。除非另有说明,否则本文描述的实施方式和实例是在具有200mm直径、300mm直径、450mm直径基板的基板上进行的。在其中SOI结构用于基板602的实施方式中,基板602可包括设置在硅晶体基板上的掩埋介电层(buried dielectric layer)。在本文描述的实施方式中,基板602可为晶体硅基板。

在一个实施方式中,设置在基板600上的膜堆叠604可具有有着多个垂直堆叠层的膜堆叠604。膜堆叠604可包括成对,成对包括重复地形成在膜堆叠604中的第一层604a和第二层604b。成对包括重复地形成的交替第一层604a和第二层604b,直到达到期望数量的成对的第一层和第二层。

膜堆叠604是存储单元装置(诸如三维(3D)存储装置)的一部分。尽管在图6A中显示了第一层604a和第二层604b的十一个重复层,但是要注意的是,根据需要可使用任何期望数量的重复成对的第一层和第二层。

在一个实施方式中,膜堆叠604可用于形成三维(3D)存储装置的多个栅极结构。形成在膜堆叠604中的第一层604a可为第一介电层,且第二层604b可为第二介电层。可利用合适的介电层来形成第一层604a和第二层604b,包括氧化硅、氮化硅、氮氧化硅、碳化硅、碳氧化硅、氮化钛、氧化物和氮化物的复合物、夹着氮化物层的至少一个或多个氧化物层及其组合等。

在一个具体实例中,第一层604a是氮化硅层,而第二层604b是氧化硅层或多晶硅层。在一个实施方式中,第一层604a的厚度可被控制在约

在基板602上形成氮化硅层的第一层604a和氧化硅层的第二层604b的膜堆叠604。将膜堆叠604形成并图案化成由绝缘结构610围绕的阶梯状结构。可在膜堆叠604上形成硬掩模层608,以促进在膜堆叠604中形成开口606(如,或称为沟槽、过孔、孔或孔洞(hole))。当制造处理完成时,可利用开口606以形成作为在装置结构中的沟道。在膜堆叠604中形成开口606之后,执行外延沉积处理以在开口606的底部部分中生长含硅柱612(诸如硅材料或SiGe材料)。应注意,对于不同的装置性能要求,可根据需要改变装置结构和配置。

图6B描绘了膜堆叠604的一部分的放大图,如圆圈所指示,描绘了被第一层604a和第二层606b包围的开口606。为了便于解释,在下文的描述中将利用膜堆叠604的放大视图,而不是图6A中描绘的膜堆叠604的整体截面图。

在操作503处,可任选地在开口606中形成控制层或蚀刻终止层702,如图7所示。当从膜堆叠604中移除第一层604a时,控制层/蚀刻终止层702可在随后蚀刻处理或移除处理中辅助界面管理。控制层/蚀刻终止层702藉由开口606所暴露的侧壁704a、704b与第一层604a和第二层604b直接接触。控制层/蚀刻终止层702可防止侵蚀性蚀刻剂在随后的蚀刻处理潜入开口606中,从而不期望地攻击随后在开口606中形成的结构或膜层。在一个实施方式中,控制层/蚀刻终止层702可藉由绝缘材料(诸如SiN、SiON或其他合适材料)形成。控制层702可具有小于

在操作504处,执行选择性氧化处理以从开口606中的侧壁704a选择性地氧化第一层604a,如图8A和图8B所示,从而形成氧化层802。图8A中描绘的实例描绘了在开口606中存在控制层702,而图8B中描绘的实例描绘了在开口606中不存在控制层702。以下以“A”标记结尾的图显示了在开口606中存在控制层702的处理的各种情况下的截面图,且以下以“B”标记结尾的图显示了在开口606中不存在控制层702的处理的各种情况下的截面图。在一些图中,可省略本文所示的部件或特征的一些元件符号,以避免混淆其他部件或特征;这是为了方便描绘各图。

应注意接着形成控制层/蚀刻终止层702(特别是当形成蚀刻终止层时),可移除氧化层802,因为蚀刻终止层本身可用作提供高蚀刻选择性的阻挡层,以便防止侵蚀性蚀刻剂潜入开口606中以攻击开口606中的层。

由于第一层604a是含硅材料(诸如SiN层),因此在选择性氧化处理期间所供应的氧元素与来自第一层604a的硅元素反应,从而在第一层604a的侧壁704a处形成氧化层802。应注意由于来自第二层604b的硅源,可能在第二层604b中形成相对少量的氧化层。

在一个实例中,选择性氧化处理是用于氧化第一层604a的侧壁704a的自由基等离子体氧化处理。选择性氧化处理在第一层604a的侧壁704a上形成氧化层802。在一个实例中,可在各个氧化腔室中执行选择性氧化(诸如自由基等离子体氧化处理)。在某些实施方式中,氧化腔室可耦合至集成处理工具(诸如图4中描绘的群集系统400)或为集成处理工具的一部分。预期本文所描述的方法可使用其他处理腔室和具有与其耦合的合适处理腔室的群集工具来实践。

在一个实例中,本文所描述的选择性氧化处理可在配置用于自由基氧化的任何合适的腔室中执行,也称为原位蒸气产生(in-situ steam generation,ISSG)或类似者。合适的氧化腔室可包括(但不限于)可从加州圣克拉拉市的应用材料公司购得的

在操作504处的选择性氧化处理是自由基等离子体氧化处理或“原位蒸气产生”(ISSG)处理。选择性氧化处理可在氧化环境中在热控制的第一层604a上提供氧化物生长。原位蒸气产生(ISSG)处理包括在待氧化的基板所处的相同腔室中形成蒸气(H

在一个实例中,在约2托和约30托之间的压力(诸如约14托)下,对于大于900度的温度(诸如在约1000摄氏度和约1200摄氏度之间的温度,诸如约1050℃)而言,执行表面氧化达约30秒与约300秒之间(诸如约130秒)的时段。在选择性氧化处理期间,使用以流量体积计具有33%氢气和67%氧气的总气体流量。选择性地形成的氧化层802可具有在约2nm与约100nm之间的厚度。

所形成的氧化层802可在随后的蚀刻处理期间用作牺牲层和/或保护层,以保护形成在开口606中的膜层,从而改善和增强蚀刻处理期间的蚀刻选择性。

在操作506处,金属介电层902在开口606中垂直地形成,从而加衬里在控制层/蚀刻终止层702上,如图9A所示,或与氧化层802和第二层604b直接接触,如图9B所示。在图9A所描绘的实例中,金属介电层902与控制层/蚀刻终止层702直接接触。在图9B所描绘的实例中,金属介电层902在开口606中垂直地形成,与第二层604b的侧壁704b和氧化层802接触。

金属介电层902可为具有介电常数大于4的高k材料。高k材料的合适实例包括二氧化铪(HfO

在一个实例中,金属介电层902是藉由合适的沉积处理(诸如CVD处理、ALD处理、溅射处理或其他合适的沉积处理)形成的。在一个具体实例中,藉由ALD处理形成金属介电层902。据信当利用金属介电层902作为NAND或VNAND三维半导体存储装置中的栅极结构时,垂直地形成在膜堆叠604中的开口606中的金属介电层902可有效地改善电性能,诸如增强的保留要求(retention requirement)以及抑制膜堆叠604中的反向隧穿电流(backtunneling current)。与具有高k材料围绕在相邻第二层之间的第一层的传统结构不同,将金属介电层902重新定位到开口606中可在每个单位单元中允许额外的空间(如,允许将第一层替换为在相邻第二层之间的导电结构的空间),从而为沉积处理、蚀刻处理或用于第一层到金属层替换处理的其他相关处理提供了更宽的处理窗口(process window)。

在操作508处,在形成金属介电层902之后,多层结构904可接着在开口606中形成,从而加衬里在金属介电层902上,如图10A和图10B所描绘的。多层结构904可包括一种或多种介电材料。在图10A-图10B中描绘的一个实例中,多层结构904包括第一氧化物层904a、第一氮化物层904b、第二氧化物层904c和多晶硅层904d。第一氧化物层904a和第二氧化物层904c是氧化硅层,且第一氮化物层904b是氮化硅层或氮氧化硅(SiON)层。

在操作510处,中心填充层906形成在开口606中,从而填充了由多层结构904留下的剩余空间,如图11A-图11B所示。中心填充层906也可为介电层(诸如SiO

在操作512处,在用金属介电层902、多层结构904和中心填充层906填充开口606之后,执行横向(lateral)选择性蚀刻处理,以从膜堆叠604选择性地移除第一层604a,如图12A和图12B所示。从膜堆叠604移除第一层604a在膜堆叠604中产生第一层604a所处的空间910a,从而形成仅氧化硅层的第二层604b保留在基板602上的悬浮膜堆叠。空间910a暴露出氧化层802。位于在第一层604a与金属介电层902之间的界面处的氧化层802可在横向选择性蚀刻处理期间有效地保护金属介电层902。藉由氧化层802的阻挡,可在横向选择性蚀刻处理期间有效地阻挡来自横向选择性蚀刻处理的侵蚀性蚀刻剂并使其远离金属介电层902,以便提高蚀刻选择性并改善界面控制和管理。在利用控制层/蚀刻终止层702的实例中,控制层/蚀刻终止层702和氧化层802的组合可提供稳固的界面保护,以防止损坏在开口606中形成的金属介电层902。在一些实例中,当形成蚀刻终止层702时,可消除氧化层802,因为蚀刻终止层本身可提供高蚀刻选择性以有效地在界面处提供蚀刻控制。

在操作514处,在第二层604b之间界定空间910a之后,可接着从基板602移除氧化层802,如图13A和图13B所示。在操作512处的横向选择性蚀刻处理期间,氧化层802用作保护和牺牲层,以保护金属介电层902。在移除第一层604a,有效地界定空间910a之后,氧化层802的功能就完成了,使得随后在操作514处移除氧化层802。应注意可在图3所描绘的处理腔室300中移除氧化层802。应注意可根据需要藉由适当的蚀刻处理来移除氧化层802。

在一个实例中,当移除氧化层802时,也可移除与氧化层802接触的控制层/蚀刻终止层702的一部分,如图13C所示,从而产生了暴露金属介电层902的侧壁表面952a的额外空间952a。当控制层/蚀刻终止层702的一部分时,控制层/蚀刻终止层702的另一部分仍保留在开口中,与第二层604b的侧壁704b接触。

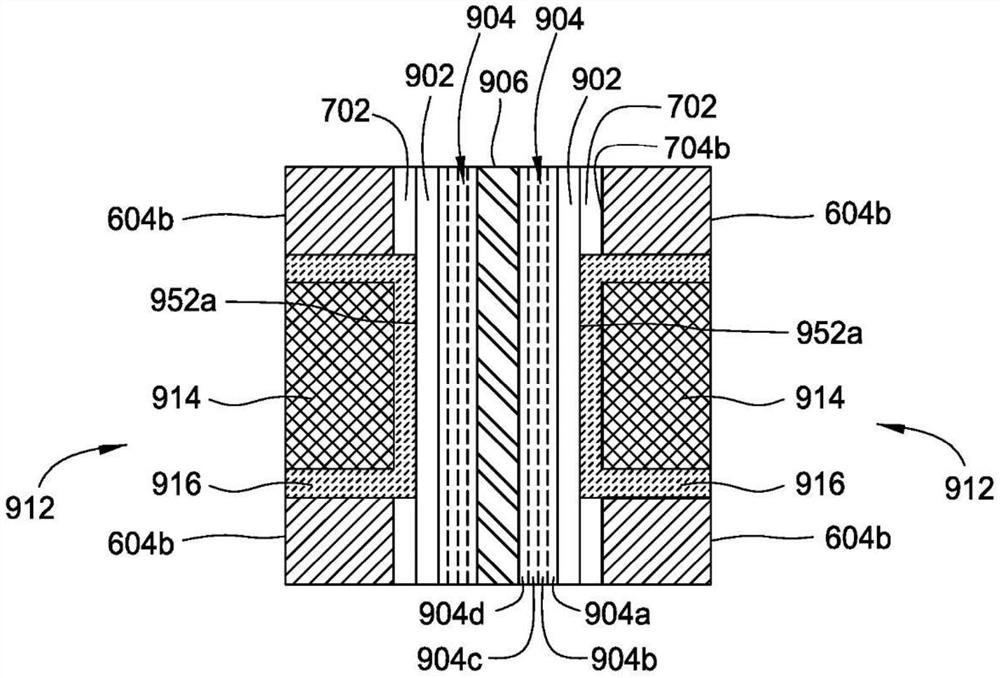

在操作516处,在移除氧化层802之后,接着形成导电结构912,并将其填充在膜堆叠604中的空间910a中,如图14A、图14B和图14C所示。导电结构912填充在相邻第二层604b之间界定的空间910a中,具有相对较大的接触面积和较大的量。在传统实践中,空间910a不仅被导电结构912填充,而且还被金属介电层填充(如,金属介电层902现在被重新放置到本公开内容中的开口606中)。金属介电层在空间910a中的占据通常导致在界面处的较差的蚀刻选择性,以及减小接触面积和可在空间910a中形成的导电结构912的量。因此,藉由将金属介电层902重新定位到开口606中,而不是在第二层604b之间的空间910a中,可获得较大尺寸的空间910a,以允许在其中形成较大量的导电结构912。此外,当用导电结构912替换第一层604a到空间910a中时,空间910a的较大尺寸还可减小制造限制和复杂性。此外,空间910a的较大尺寸允许在其中替换更大量的导电结构912,使得可获得增加的金属导电性和减小的电阻率,从而在其完成时提供装置结构的增强电性能。

据信膜堆叠604中利用的导电结构912中的金属材料在当以后用作NAND或VNAND三维半导体存储装置中的栅极结构时,可有效地改善膜堆叠604中的电性能(诸如电导率和迁移率及类似者)。沉积处理可为金属有机化学气相沉积(MOCVD)处理或溅射物理气相沉积处理,或根据需要的其他合适的处理。可在图2所描绘的处理腔室232中执行沉积处理。在图14A、图14B和图14C所描绘的实例中,导电结构912包括形成在阻挡层916上的金属材料914。阻挡层916由与金属介电层902不同的材料制成。由于移除了氧化层802和/或控制层/蚀刻终止改变702的一部分(若有的话),阻挡层916可直接与金属介电层902接触或界面连接,以便根据需要增强电性能。

金属材料914的合适实例可选自由钨(W)、硅化钨(WSi)、钨多晶硅(W/poly)、钨合金、钽(Ta)、钛(Ti)、铜(Cu)、钌(Ru)、镍(Ni)、钴(Co)、铬(Cr)、铁(Fe)、锰(Mn)、铝(Al)、铪(Hf)、钒(V)、钼(Mo)、钯(Pd)、金(Au)、银(Au)、铂(Pt)、其合金或其组合所组成的组。阻挡层916的合适实例可为金属氮化物层或金属氮化硅层,诸如氮化钛(TiN)、氮化钽(TaN)、TaSiN、TiSiN及其组合等。

在一个具体实例中,金属材料914可为含钨(W)层,且阻挡层916可为氮化钛(TiN)、氮化钽(TaN)、TaSiN或TiSiN。应注意,导电结构912可根据需要仅具有金属材料914而没有阻挡层916。

因此,提供了用于形成用于制造半导体装置的存储单元的三维(3D)堆叠的阶梯状结构的方法和设备。在界面处的保护性氧化层(如,牺牲性氧化层)以及选择性沉积和选择性蚀刻处理用于用导电结构代替膜堆叠中的介电层。在用于半导体装置的存储单元的三维(3D)堆叠的膜堆叠中的开口(如,沟道)中形成金属介电材料。保护/牺牲氧化层可在移除处理期间保护界面和金属介电层,从而提供对界面轮廓和形貌的良好控制。结果,当随后在其中形成导电结构时,可在界面处获得良好的电接触,从而为存储单元提供期望的电性能。

尽管前述内容涉及本公开内容的实施方式,但是在不背离本公开内容的基本范围的情况下,可设计本公开内容的其他和进一步的实施方式,并且本公开内容的范围由以下权利要求书来确定。

- 用于3D NAND应用的存储单元制造

- 应用于制造漏斗胸矫正板的3D打印模拟板的制造方法