一种多透明度视频叠加装置及方法

文献发布时间:2023-06-19 11:39:06

技术领域

本发明属于图像处理技术领域,具体涉及一种多透明度视频叠加装置及方法。

背景技术

为了更好的用户体验,超高分辨率视频越来越普及,视频叠加,是一种将多个媒体文件叠加在一个背景媒体文件上,在屏幕里同时呈现多个视频同时播放的效果。该效果被广泛应用于教程视频、产品展示或游戏视频中。

但复杂的视频叠加大幅增加了输出延迟,提高了处理需求,且显示效果单一,应用场景单一。

发明内容

本发明所要解决的技术问题是针对上述现有技术的不足,提供一种多透明度视频叠加装置及方法。

为实现上述技术目的,本发明采取的技术方案为:

一种多透明度视频叠加装置,包括控制端、DDR单元和叠加计算单元;

控制端,用于配置视频叠加需求,并判断当前输入像素所属亮度、色彩和位置区域,选择该像素叠加百分比;

DDR单元,用于根据叠加需求将低帧率视频拓展、缩放或裁剪至高帧率视频;

叠加计算单元,用于以高帧率视频为基础,叠加DDR单元输出视频。

为优化上述技术方案,采取的具体措施还包括:

上述的控制端配置视频叠加需求,包括:

配置叠加门限,叠加门限包含亮度、色彩、图像坐标区域;

配置不同色域、不同图像区域、不同亮度的叠加百分比设定。

上述的控制端中,判断模块的数量最多设置为2

上述的控制端为ARM,单片机或FPGA模块。

上述的控制端通过FPGA并行进行当前输入像素所属亮度、色彩、位置区域判断,实现该像素叠加百分比的选择,实现方式包含查找表,分布式并行判断逻辑。

上述的叠加计算单元包含两个DSP。

一种多透明度视频叠加方法,包括:

步骤一、控制端配置视频叠加需求,并判断当前输入像素所属亮度、色彩和位置区域,选择该像素叠加百分比;

步骤二、DDR单元根据叠加需求将低帧率视频拓展、缩放或裁剪至高帧率视频;

步骤三、叠加计算单元以高帧率视频为基础,叠加DDR单元输出视频。

本发明具有以下有益效果:

本发明提出的针对不同帧率,不同高分辨率,多透明度可配置的视频叠加方法,具有极低的叠加延迟,支持不同视频叠加,可实时灵活配置叠加视屏不同区域的透明度,同时具有对输入源兼容性强,应用场景广泛的特点。

附图说明

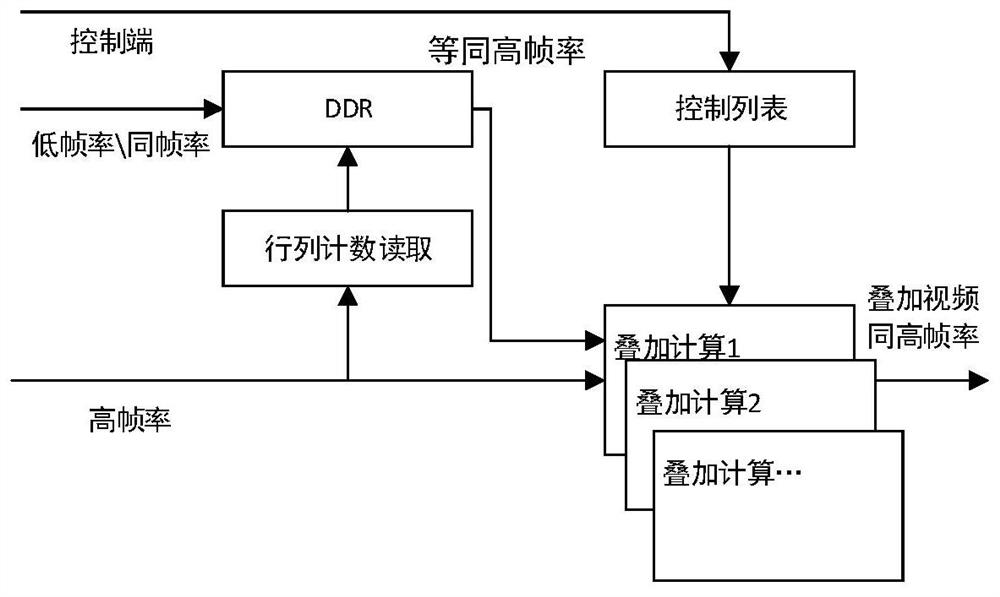

图1为本发明装置构成图;

图2为叠加计算单元构成图;

图3为本发明装置应用场景示例;

图4为本发明方法应用场景示例。

具体实施方式

以下结合附图对本发明的实施例作进一步详细描述。

参见图1,一种多透明度视频叠加装置,包括控制端、DDR单元和叠加计算单元;

控制端,用于配置视频叠加需求,并判断当前输入像素所属亮度、色彩和位置区域,选择该像素叠加百分比;

DDR单元,用于根据叠加需求将低帧率视频拓展、缩放或裁剪至高帧率视频;

实施例中,本发明通过DDR重组,将低帧率视频拓展到高帧率视频,支持不同帧率视频叠加;通过DDR重组,低帧率视频根据叠加需求,拓展,或缩放、或裁剪至与高帧率视频一致,支持不同分辨率视频叠加;

叠加计算单元,用于以高帧率视频为基础,叠加DDR单元输出视频。

实施例中,因为超大分辨率视频数据吞吐量大,一般使用多像素点或多画面分块并发传输方式,通过在FPGA内例化多个叠加计算单元,可支持多并发超大分辨率视频叠加处理。

实施例中,控制端配置视频叠加需求,包括:

配置叠加门限,叠加门限包含亮度、色彩、图像坐标区域等图像要素;

配置不同色域(可精确到指定颜色)、不同图像区域、不同亮度的叠加百分比设定。

实施例中,控制端在资源允许的情况下,判断模块的数量最多设置为2

实施例中,控制端为ARM,单片机或FPGA模块。

实施例中,控制端通过FPGA并行进行当前输入像素所属亮度、色彩、位置区域判断,实现该像素叠加百分比的选择,实现方式包含查找表,分布式并行判断逻辑。

实施例中,叠加计算单元包含两个DSP。

参见图2,通过FPGA流水化叠加子单元,以高帧率视频为基础,叠加DDR输出视频,不用缓存视频图像,具有极低的叠加处理延迟。

叠加计算单元仅包含两个DSP(FPGA逻辑单元,包含乘法与加减法运算),消耗资源少。以高帧率视频为4K分辨率,60Hz视频为例,包含视频接口的输入输出延迟,该图像叠加设备的插入延迟低至7.5us。

本发明叠加装置可应用于包含但不限于画中画叠加(区域内透明度为0),荧光彩色视频叠加,OSD叠加,3D视频隔行/隔列重组等场景;

本发明叠加装置可实施为独立视频叠加装置(图3.a);可作为图像处理设备的内部组成模块,(图3.b),虚线为可选视频源可来自外部,也可来自处理单元,叠加输出视频可送至外部,也可送至处理单元;也可作为FPGA内部计算单元(图3.c);以及不限于以上所述的其他实施方式;

一种多透明度视频叠加方法,包括:

步骤一、控制端配置视频叠加需求,并判断当前输入像素所属亮度、色彩和位置区域,选择该像素叠加百分比;

步骤二、DDR单元根据叠加需求将低帧率视频拓展、缩放或裁剪至高帧率视频;

步骤三、叠加计算单元以高帧率视频为基础,叠加DDR单元输出视频。

叠加方法实施示意如图4。

图4.a表述在图片内可支持任意不规则图片叠加,一般可用于画中画等,

图4.b表述的非连续多色彩叠加可用于色彩的伪彩替换,

图4.c中表述的整幅行列交错叠加,可用于3D视频合成,

图4.d中多区域不同透明度可用于水印或OSD菜单。

上述实施在同一装置内同时有效,如多不规则区域叠加(a)后,根据叠加多种不同透明度(b)的伪彩上色(d),可用于提升关注区域的视觉效果,并保留部分原有图像特征。

综上所述,本发明基于FPGA可编程逻辑平台,以高帧率视频为基础,实现了待叠加视频的帧率与分辨率适配;实现了低至微秒级的高帧率视频叠加输出延迟;实现了多色彩或亮度区域视频的不同透明度叠加效果;适用复杂显示效果OSD(On Screen Display)叠加,荧光和彩色视频叠加,画中画叠加,3D视频叠加等多种不同的应用场景。

以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

- 一种多透明度视频叠加装置及方法

- 视频图像叠加方法、叠加装置、编码装置和存储介质