背照式图像传感器及其形成方法

文献发布时间:2024-01-17 01:18:42

技术领域

本发明属于半导体制造领域,尤其涉及一种背照式图像传感器及其形成方法。

背景技术

互补金属氧化物半导体图像传感器(CMOS Image Sensor,CIS)是将光学图像转化为电信号的半导体器件。CIS包括用于感光的光接收部件(通常称为光电二极管)和用于将所感测的光处理为电信号的逻辑电路。

一种在光学成像器件中常见的类型是背照式(Back-Sideilluminated, BSI)图像传感器。BSI图像传感器制造可以集成至传统的半导体工艺内以用于更低的成本、更小的尺寸和更高的集成度。此外,BSI图像传感器具有低操作电压、低功耗、高量子效率、低读出噪声并且允许随机存取。

对于BSI图像传感器,为了获得单个芯片,需要对晶圆进行激光切割或机械切割。然而在对晶圆切割时,晶圆容易产生崩缺,从而破坏芯片。

发明内容

本发明解决的技术问题是提供一种背照式图像传感器及其形成方法,通过在晶圆的切割道边缘形成空腔,可以在对晶圆进行切割时,防止晶圆产生崩缺现象。该方法包括:提供衬底,并定义芯片区和切割道;在切割道的边缘形成多个第一沟槽;在栅极形成前,在所述多个第一沟槽中形成第一空腔;在背面工艺中,从背面打开所述第一空腔,用于对切割道进行切割时防止崩缺。

可选的,所述在所述多个第一沟槽中形成第一空腔包括:通过沉积至少一层介质层,使所述第二沟槽的开口封闭,并形成第一空腔。

可选的,所述在切割道的边缘形成多个第一沟槽包括:在衬底上形成图案化的第一掩膜层;通过刻蚀工艺,同时在芯片区形成第三沟槽,以形成多个光电二极管的感光单元,以及在切割道的边缘形成多个第一沟槽。

可选的,所述在栅极形成前,所述在所述多个第一沟槽中形成第一空腔包括:在所述多个第一沟槽的表面形成至少一层外延层,使所述第一沟槽线宽变窄,形成多个第二沟槽;在所述多个第二沟槽的下部表面形成至少一层介质层;通过外延工艺,在所述多个第二沟槽的上部,形成第一外延层,使所述多个第二沟槽的开口封闭,并形成第一空腔。

可选的,所述在所述多个第一沟槽的表面形成至少一层外延层,使所述第一沟槽线宽变窄,形成多个第二沟槽包括:同时在所述第三沟槽的表面形成至少一层外延层,使所述第三沟槽线宽变窄,形成第四沟槽,以及在所述多个第一沟槽的表面形成至少一层外延层,使所述第一沟槽线宽变窄,形成多个第二沟槽;所述在所述多个第二沟槽的下部表面形成至少一层介质层包括:同时在所述第四沟槽的下部表面形成至少一层介质层,以及在所述多个第二沟槽的下部表面形成至少一层介质层;所述通过外延工艺,在所述多个第二沟槽的上部,形成第一外延层,使所述多个第二沟槽的开口封闭,并形成第一空腔包括:通过外延工艺,同时在所述第四沟槽的上部,形成所述第一外延层,使所述第四沟槽的开口封闭,并形成第二空腔,以及在所述多个第二沟槽的上部,形成第一外延层,使所述多个第二沟槽的开口封闭,并形成第一空腔。

可选的,所述至少一层介质层包括第一介质层或第二介质层中的至少一种;所述同时在所述第四沟槽的下部表面形成至少一层介质层,以及在所述多个第二沟槽的下部表面形成至少一层介质层包括:在所述多个第二沟槽表面和所述第四沟槽表面形成所述第一介质层;通过沉积所述第二介质层,使所述多个第二沟槽和所述第四沟槽开口封闭;去除所述多个第二沟槽和所述第四沟槽开口处的部分所述第二介质层;去除所述多个第二沟槽和所述第四沟槽开口处的部分所述第一介质层,从而在所述多个第二沟槽和所述第四沟槽的下部表面形成所述至少一层介质层。

可选的,所述第一介质层包括第一子介质层和第二子介质层。

可选的,所述第一子介质层为氧化硅;所述第二子介质层为氮化硅;所述第二介质层为氧化硅。

可选的,所述去除所述多个第二沟槽开口处的部分所述第二介质层包括:通过氢氟酸去除所述多个第二沟槽开口处的部分第二介质层,从而暴露出所述第二子介质层。

可选的,所述去除所述多个第二沟槽开口处的部分所述第一介质层包括:通过热磷酸去除所述多个第二沟槽和所述第四沟槽开口处的部分第二子介质层;通过氢氟酸去除多个第二沟槽和所述第四沟槽开口处的部分第一子介质层。

可选的,所述通过外延工艺,在所述多个第二沟槽的上部,形成第一外延层,使所述多个第二沟槽的开口封闭,并形成第一空腔之后还包括:去除所述第一掩膜层;对所述衬底进行化学机械研磨;在所述衬底上形成第二外延层;在所述第二外延层上形成晶体管。

可选的,所述多个第一沟槽沿切割道的边缘至中心形成至少两排分布。

本发明还提供了一种背照式图像传感器,通过上述背照式图像传感器的形成方法形成。

与现有技术相比,本发明实施例的技术方案具有以下有益效果:

在本发明实施例中,通过提供衬底,并定义芯片区和切割道;在切割道的边缘形成多个第一沟槽;在栅极形成前,在所述多个第一沟槽中形成第一空腔;在背面工艺中,从背面打开所述第一空腔,用于对切割道进行切割时防止晶圆崩缺。本发明通过在切割道边缘形成空腔结构,并从衬底背面打开空腔结构,在对晶圆进行切割时可以防止晶圆崩缺。

进一步,本发明一实施例可以在芯片区和切割道同步进行相关工艺,并在切割道形成空腔结构,从而可以减少工艺步骤,节省成本。

进一步,本发明另一实施例可以在芯片区完成部分或全部相关工艺后,再在切割道形成空腔结构。

附图说明

本发明附图构成本说明书的一部分、用于进一步理解本发明,附图示出了本发明的实施例,并与说明书一起用来说明本发明的原理。

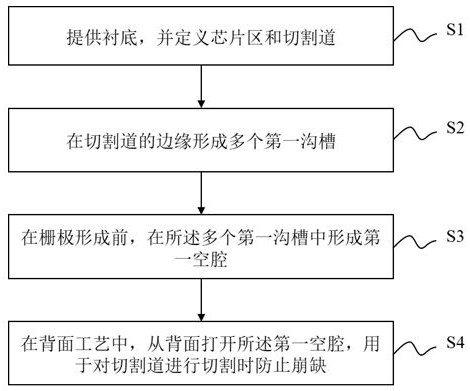

图1为本发明一实施例的一种BSI图像传感器的形成方法;

图2为本发明一实施例的一种BSI图像传感器的俯视图;

图3至图15为本发明一实施例的一种BSI图像传感器的截面示意图;

图16至图19为本发明的另一实施例的一种BSI图像传感器的形成方法。

具体实施方式

以下详细说明都是例示性的,旨在对本发明提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本发明所属技术领域的普通技术人员通常理解的相同含义。

图1为本发明一实施例的一种BSI图像传感器的形成方法1的流程图,该方法包括:

步骤S1:提供衬底,并定义芯片区和切割道;

步骤S2:在切割道的边缘形成多个第一沟槽;

步骤S3:在栅极形成前,在所述多个第一沟槽中形成第一空腔;

步骤S4:在背面工艺中,从背面打开所述第一空腔,用于对切割道进行切割时防止崩缺。

实施例一

以下结合附图2至图15对图1的BSI图像传感器的形成方法进行详细描述。

图2为本发明一实施例的一种BSI图像传感器的俯视图。

图3至图15为本发明一实施例的一种BSI图像传感器的截面示意图。

对于步骤S1:提供衬底,并定义芯片区和切割道,参考图2和图3。衬底11具有正面和背面。衬底11可以被划分为芯片区101和将芯片区101分隔开的切割道102。芯片区101可以包括逻辑区和像素区。衬底11可以是掺杂或未掺杂的半导体材料,诸如硅、锗、硅锗、绝缘体上锗硅(SGOI)或其组合。衬底11可以包括多层外延层的衬底。仅作为示例说明,在该实施例中,衬底11可以在硅晶圆111上形成外延层112、外延层113。其中,外延层112可以是低掺杂的P型缓冲层;外延层113可以是N型外延层,用于形成感光单元,即光电二极管的N型区域。

参考图4,对于步骤S2:在切割道的边缘形成多个第一沟槽可以包括以下步骤:

在衬底11上形成图案化的第一掩膜层12;

通过刻蚀工艺,同时在芯片区102形成第三沟槽13b,以形成多个光电二极管的感光单元11a,以及在切割道的边缘形成多个第一沟槽13a。

其中,第一掩膜层12可以为光阻材料。第一掩膜层12也可以为硬掩膜材料,例如,氧化硅、氮化硅、氮氧化硅等中的一种或多种。可选的,所述多个第一沟槽13a沿切割道102的边缘至中心可以形成至少两排或多排分布。

参考图5至图14,对于步骤S3:在栅极形成前,在所述多个第一沟槽中形成第一空腔可以包括以下步骤:

在所述多个第一沟槽13a的表面形成至少一层外延层,使所述第一沟槽13a线宽变窄,形成多个第二沟槽13c;

在所述多个第二沟槽13c的下部表面形成至少一层介质层;

通过外延工艺,在所述多个第二沟槽13c的上部,形成第一外延层17,使所述多个第二沟槽13c的开口封闭,并形成第一空腔17a。

具体地,参考图5,所述在所述多个第一沟槽13a的表面形成至少一层外延层,使所述第一沟槽13a线宽变窄,形成多个第二沟槽13c可以包括:同时在所述第三沟槽13b的表面形成至少一层外延层14,使所述第三沟槽13b线宽变窄,形成第四沟槽13d,以及在所述多个第一沟槽13a的表面形成至少一层外延层14,使所述第一沟槽13a线宽变窄,形成多个第二沟槽13b。

在该实施例中,所述在所述多个第二沟槽13c的下部表面形成至少一层介质层包括:同时在所述第四沟槽13d的下部表面形成至少一层介质层,以及在所述多个第二沟槽13c的下部表面形成至少一层介质层。

具体地,参考图6至图10,所述同时在所述第四沟槽13d的下部表面形成至少一层介质层,以及在所述多个第二沟槽13c的下部表面形成至少一层介质层包括以下步骤:

参考图6,在所述多个第二沟槽13c表面和所述第四沟槽13d表面形成所述第一介质层15;在该实施例中,第一介质层15可以包括第一子介质层151和第二子介质层152。可选的,第一子介质层151可以为氧化硅;第二子介质层可以为氮化硅。

参考图7,通过沉积第二介质层16,使所述多个第二沟槽13c和所述第四沟槽13d开口封闭;在该实施例中,第二介质层16可以为氧化硅。

参考图8,去除所述多个第二沟槽13c和所述第四沟槽13d开口处的部分所述第二介质层16。在该实施例中,可以通过氢氟酸去除所述多个第二沟槽13c和所述第四沟槽13d开口处的部分第二介质层16,从而暴露出所述第二子介质层152。

参考图9和图10,去除所述多个第二沟槽13c和所述第四沟槽13d开口处的部分所述第一介质层15,从而在所述多个第二沟槽13c和所述第四沟槽13d的下部表面形成所述至少一层介质层。具体地,参考图10,可以通过热磷酸去除所述多个第二沟槽13c和所述第四沟槽13d开口处的部分第二子介质层152。参考图10,可以通过氢氟酸去除所述多个第二沟槽13c和所述第四沟槽13d开口处的部分第一子介质层151。需要说明的是,在该实施例中,第二介质层16为氧化硅。因此,通过氢氟酸去除所述多个第二沟槽13c和所述第四沟槽13d开口处的部分第一子介质层151时,第二介质层16也会被消耗,从而暴露出第二子介质层152的侧壁。在该实施例中,所述多个第二沟槽13c和所述第四沟槽13d的底部可能残留部分第二介质层16未被氢氟酸完全去除。

具体地,参考图11,通过外延工艺,在所述多个第二沟槽13c的上部,形成第一外延层17,使所述多个第二沟槽13c的开口封闭,并形成第一空腔17a包括:参考图11,通过外延工艺,同时在所述第四沟槽13d的上部,形成所述第一外延层17,使所述第四沟槽13d的开口封闭,并形成第二空腔17b,以及在所述多个第二沟槽13c的上部,形成所述第一外延层17,使所述多个第二沟槽13c的开口封闭,并形成第一空腔17a。

进一步地,在所述通过外延工艺,在所述多个第二沟槽13c的上部,形成第一外延层17,使所述多个第二沟槽13c的开口封闭,并形成第一空腔17a之后还可以包括:

参考图12,去除所述第一掩膜12;

参考图13,对所述衬底11进行化学机械研磨;

参考图14,在所述衬底11上形成第二外延层18;以及在所述第二外延层18上形成晶体管18a的栅极、源极、漏极、侧墙,从而形成晶体管18a。

在一些实施例中,在衬底11的正面还可以形成金属互联层等结构,在此不再赘述。

对于步骤S4:在背面工艺中,从背面打开所述第一空腔,用于对切割道进行切割时防止崩缺,可以参考图15。

如图15所示,在背面工艺中,可以通过对衬底11的背面进行化学机械研磨、通过刻蚀工艺等从背面打开所述第一空腔17a。由于第一空腔17a从背面被打开,因此,通过激光或切刀19对切割道102进行切割时,可以防止晶圆发生崩缺。

实施例二

图16至图19为本发明的另一实施例的一种BSI图像传感器的形成方法。

在该实例中,可以先完成芯片区的相关工艺后,通过在切割道中形成沟槽,并通过介质材料填充形成空腔结构。进一步地,在背面工艺中,从背面打开该空腔结构,从而在对晶圆切割时,防止晶圆产生崩缺。

具体地,以下结合附图16至图19对图1的BSI图像传感器的形成方法进行详细描述。

对于步骤S1:提供衬底,并定义芯片区和切割道。参考图16,提供衬底21,其具有正面和背面,并可以在衬底21表面形成第一掩膜层22。其中,第一掩膜层12可以为光阻材料。第一掩膜层12也可以为硬掩膜材料,例如,氧化硅、氮化硅、氮氧化硅等中的一种或多种。衬底21可以被划分为芯片区(图中未示出)和将芯片区分隔开的切割道202。芯片区可以包括逻辑区和像素区。衬底21可以是掺杂或未掺杂的半导体材料,诸如硅、锗、硅锗、绝缘体上锗硅(SGOI)或其组合。衬底21可以包括多层外延层的衬底。仅作为示例说明,在该实施例中,衬底21可以在硅晶圆211上形成外延层212、外延层213。其中,外延层212可以是低掺杂的P型缓冲层;外延层213可以是N型外延层,用于形成感光单元,即光电二极管的N型区域。

对于步骤S2:在切割道的边缘形成多个第一沟槽。参考图17,可以形成图案化的第一掩膜层22,再通过刻蚀工艺,可以在切割道202的边缘形成多个第一沟槽23a。可选的,所述多个第一沟槽23a沿切割道202的边缘至中心可以形成至少两排或多排分布。

对于步骤S3:在栅极形成前,在所述多个第一沟槽中形成第一空腔。参考图18,通过沉积至少一层介质层23,并使多个第一沟槽23a开口封闭形成第一空腔25。其中,至少一层介质层23可以包括氧化硅。氮化硅、氮氧化硅等材料中的一种或者多种。

对于步骤S4:在背面工艺中,从背面打开所述第一空腔,用于对切割道进行切割时防止崩缺。参考图19,在背面工艺中,可以通过对衬底21的背面进行化学机械研磨、通过刻蚀工艺等从背面打开所述第一空腔25。由于第一空腔25从背面被打开,因此,通过激光或切刀26对切割道202进行切割时,可以防止晶圆发生崩缺。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。