并行输入串行输出电路及采用该电路的存储器

文献发布时间:2023-06-19 09:44:49

技术领域

本发明涉及电路设计领域,特别是关于数据输入输出电路领域以及采用该数据输入输出电路的存储器。

背景技术

在存储器系统内,通常包括多个存储单元阵列,在对多个存储单元阵列进行读写操作控制时,需要通过各种信号传输电路来实现信号的传输。因为涉及多个存储单元,有时信号传输电路的输入信号为同时并行输入多个信号,但输出时需要逐个输出,例如存储器系统读信号的输出,在读取的时候是同时读取多个存储单元的信号,但输出时是需要单个存储单元的存储信息逐个输出,因此需要设计一种结构简单,数据传输快速的输入输出电路。

发明内容

本发明的目的在于提供一种结构简单,传输速率快的并行输入串行输出电路。

本发明的另一目的在于提供一种具有结构简单,传输速率快的并行输入串行输出电路的存储器。

为达成前述目的,本发明一种并行输入串行输出电路,其包括:

计数器电路单元,其接受时钟信号,根据不同周期数量的时钟信号计数输出不同频率的计数信号;

译码器电路单元,其接受计数器单元输出的不同计数信号,根据不同的计数信号的组合输出选择信号;

多路复用器电路,其包括多路选择开关电路,多路选择开关电路的每一路的输入端输入并行输入信号,多路选择开关电路的每一路的输出端共同连接同一公共输出端,其中每一路选择开关分别由译码器电路单元输出的选择信号控制以将并行输入信号转换为串行输入信号;

D触发器,其输入端连接多路复用器电路的多路选择开关的公共输出端,其时钟信号端与前述计数器电路的时钟信号的反相信号连接,D触发器在反相时钟信号的控制下将串行输入信号输出为串行输出信号。

根据本发明的一个实施例,其中计数器电路单元每一个时钟周期计数产生第一计数信号,每两个时钟周期计数产生第二计数信号,每三个时钟周期计数产生第三计数信号,计数信号为高低电平脉冲信号。

根据本发明的一个实施例,其中第一计数信号是时钟信号的一个周期的上升沿发生变化,第二计数信号是在第一计数信号的一个周期的下降沿发生变化,第三计数信号是在第二计数信号的一个周期的下降沿发生变化。

根据本发明的一个实施例,其中译码器电路单元包括反相器电路和若干与门电路,与门电路的输入端连接计数器单元输出的计数信号和经过反相器电路反相后的反相计数信号,该若干与门电路在同一时刻只有一个与门电路输出的选择信号与其他与门电路输出的选择信号的电平不同。

根据本发明的一个实施例,其中多路复用器电路,每一路选择开关电路包括一对相互并联的PMOS晶体管和NMOS晶体管构成的传输门电路,译码器电路的输出选择信号连接其中一个晶体管的门极,译码器电路的输出选择信号经反相器后连接另一晶体管的门极,PMOS晶体管的源极和NMOS晶体管的漏极共同连接输入信号,PMOS晶体管的漏极和NMOS晶体管的源极共同连接输出端,每一路选择开关电路的输出端共同连接一个公共输出端。

为达成前述另一目的,本发明一种存储器,其包括:

若干存储单元,每个存储单元用于存储数据;

读写控制电路,其控制存储单元数据的读写,其中所述读写控制电路包括前述的并行输入串行输出电路。

本发明的并行输入串行输出电路,只需要一个计数器单元,一个译码器单元,一个多路复用器单元以及一个D触发器,其结构简单,而且其数据传输速率较快,能够实现数据快速传输。采用该并行输入串行输出电路的存储器能够实现数据的快速读写操作。

附图说明

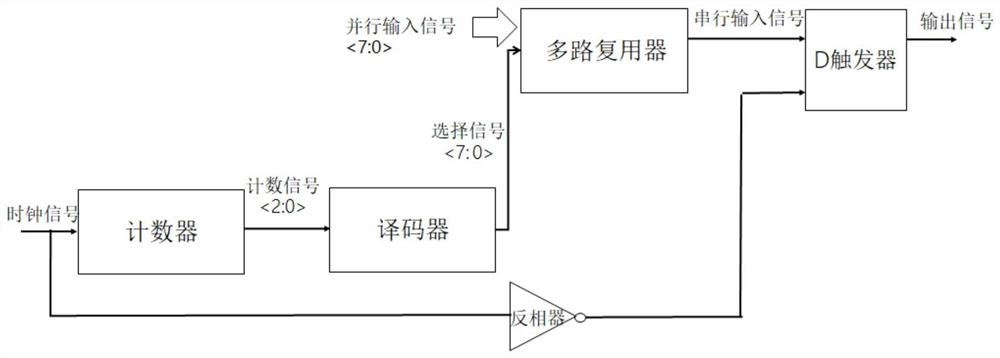

图1是本发明的数据传输电路的信号传输结构框图。

图2是本发明的数据传输电路的串行输出信号的时序图。

图3是根据本发明的一个实施例的数据传输电路的内部结构框图。

图4是根据本发明的一个实施例的数据传输电路的计数器电路单元的结构框图及计数信号脉冲时序图。

图5是根据本发明的一个实施例的数据传输电路的计数器及译码器的信号传输结构框图示意图。

图6是根据本发明的一个实施例的数据传输电路的译码器的内部结构框图。

图7是根据本发明的一个实施例的多路复用器的内部结构示意图。

图8是根据本发明的一个实施例的D触发器的结构示意图及其时钟信号脉冲时序图。

图9是根据本发明的一个实施例的各个信号的脉冲时序图。

具体实施方式

以下结合附图和具体实施例对本发明的内容做进一步详细说明。

在以下的描述中,参考各实施例对本发明进行描述。然而,本领域的技术人员将认识到可在没有一个或多个特定细节的情况下或者与其它替换和/或附加方法或组件一起实施各实施例。此外,应理解附图中示出的各实施例是说明性表示且不一定按比例绘制。

在本说明书中,对“一个实施例”或“该实施例”的引用意味着结合该实施例描述的特定特征、结构或特性被包括在本发明的至少一个实施例中。在本说明书各处中出现的短语“在一个实施例中”并不一定全部指代同一实施例。

如前所述,本发明可以是存储器中的信号传输电路,其中该存储器可以是铁电存储器、DRAM存储器、Flash存储器、磁存储器MRAM、相变存储器PCM或电阻存储器RRAM等各种存储器。各种存储器包括若干存储单元以及读写控制电路。存储单元用于存储数据,读写控制电路用于控制向每个存储单元写入和读取数据。关于各存储器的内部具体结构此处不再详细展开说明,为简化说明,此处仅对读写控制电路中的数据传输电路部分的结构进行说明。

请参阅图1所示,其显示本发明的数据传输电路的信号传输结构框图。根据本发明的一个实施例,该数据传输电路为并行输入串行输出电路,为举例说明,此处以并行输入信号为8位输入信号为例对本发明的数据传输电路进行说明,根据本发明的一个实施例,该8位并行输入信号例如可以是同时读取的8位存储单元的数据,或者可以是同时读取的存储器中的8位寄存器的数据等。其中8位并行输入信号<7:0>同时输入数据传输电路,经过数据传输电路的转换形成串行输出信号。

请参阅图2所示,其显示本发明的串行输出信号的脉冲时序图。结合图1所示,8位并行输入的信号,经过数据传输电路的转换之后变为串行输出信号,在t1时刻输出的数据为并行输入信号<0>,在t2时刻输出的数据为并行输入信号<1>,在t3时刻输出的数据为并行输入信号<2>,在t4时刻输出的数据为并行输入信号<3>,在t5时刻输出的数据为并行输入信号<4>,在t6时刻输出的数据为并行输入信号<5>,在t7时刻输出的数据为并行输入信号<6>,在t8时刻输出的数据为并行输入信号<7>。

请参阅图3所示,其显示根据本发明一个实施例的数据传输电路的内部结构框图。如图3所示,本发明的数据传输电路包括一个计数器电路单元,一个译码器电路单元,一个多路复用器电路单元以及一个D触发器。其中计数器电路单元根据输入的时钟信号进行计数,根据不同的时钟频率产生不同的计数信号,在该实施例中为与8位并行输入信号对应,计数器电路单元产生三个计数信号<2:0>(具体见后续详细说明)。计数器单元产生的三个计数信号<2:0>输入译码器电路单元的输入端,经过译码器电路单元的编译后输出8位选择信号<7:0>(具体见后续详细说明)。译码器电路单元输出的8位选择信号<7:0>输入多路复用器电路单元,其中8位并行输入信号<7:0>并行输入多路复用器的输入端,在多路复用器内,由选择信号控制选择开关,将8位并行输入信号<7:0>转换成同一时刻只输出一位数据的串行输入信号(具体见后续详细说明)。串行输入信号输入D触发器,在反相时钟信号的控制下D触发器输出串行输出信号。

请参阅图4所示,其显示根据本发明的一个实施例的图3所示的计数器的结构框图及根据时钟信号产生的计数信号的时序图。如图4中所示,时钟信号为固定频率的周期脉冲信号,计数器根据输入的时钟信号,根据不同的时钟频率产生三个不同的计数信号,其中第一计数信号<0>是统计一个时钟周期频率的计数信号,第二计数信号<1>是统计两个时钟周期频率的计数信号,第三计数信号<2>是统计四个时钟周期频率的计数信号。如图中所示,在该实施例中第一计数信号<0>是在每个周期的时钟脉冲信号的上升沿发生高低电平翻转的脉冲信号,而第一计数信号<1>是每两个时钟周期发生高低电平翻转的脉冲信号,第三计数信号<2>是每四个时钟周期发生高低电平翻转的脉冲信号。如图中所示,这样在时间周期T1内,第一计数信号<0>、第二计数信号<1>和第三计数信号<2>都为低电平,这样三个计数信号的低电平状态可以表示为000的二进制码;在时间周期T2内,第一计数信号<0>为高电平,第二计数信号<1>和第三计数信号<2>都为低电平,这样三个计数信号的电平状态可以表示为001的二进制码,依此类推,在时间周期T3内,第一计数信号<0>为低电平,第二计数信号<1>为高电平,第三计数信号<2>为低电平,这样三个计数信号的电平状态可以表示为010的二进制码;在时间周期T4内,第一计数信号<0>为高电平,第二计数信号<1>为高电平,第三计数信号<2>都为低电平,这样三个计数信号的电平状态可以表示为011的二进制码,在时间周期T5内,第一计数信号<0>为低电平,第二计数信号<1>为低电平,第三计数信号<2>为高电平,这样三个计数信号的电平状态可以表示为100的二进制码,在时间周期T6内,第一计数信号<0>为高电平,第二计数信号<1>为低电平,第三计数信号<2>为高电平,这样三个计数信号的电平状态可以表示为101的二进制码,在时间周期T7内,第一计数信号<0>为低电平,第二计数信号<1>为高电平,第三计数信号<2>为高电平,这样三个计数信号的电平状态可以表示为110的二进制码,在时间周期T8内,第一计数信号<0>为高电平,第二计数信号<1>为高电平,第三计数信号<2>为高电平,这样三个计数信号的电平状态可以表示为111的二进制码。如此重复循环。其中计数器电路单元内部的具体电路可以采用三个串联的D触发器实现,或者也可以通过其他的方式实现,只要保证产生如图4所示时序的三个脉冲计数信号即可。

请参阅图5所示,其显示图2所示的计数器与译码器的信号传输示意图。如上所述,计数器电路单元根据不同的时钟周期频率产生三个计数信号,三个计数信号输入译码器的输入端,经过译码器的转换输出为8位的选择信号<7:0>。

请参阅图6所示,其显示图5所示的译码器电路单元的内部结构示意图。如图中所示,该译码器电路单元包括三个反相器电路以及八个与门电路。其中第一反相器61的输入端连接计数器电路输出的第一计数信号<0>,第一反相器61的输出端输出反相计数信号<0>。第二反相器62的输入端连接计数器电路输出的第二计数信号<1>,第二反相器62的输出端输出反相计数信号<1>。第三反相器63的输入端连接计数器电路输出的第三计数信号<2>,第三反相器63的输出端输出反相计数信号<2>。

请继续参阅图6所示,其中反相计数信号<0>、反相计数信号<1>和反相计数信号<2>与第一与门电路601的三个输入端连接,第一与门电路的输出端输出选择信号<0>。因为是与门电路,所以与门电路的三个输入端都为高电平时输出端才为高电平。

为简化图式,图6中只示出了第一与门电路601的输入端与输入信号的具体连接,其他与门电路602-608只示出了输入的信号,并未示出输入信号的具体连接线路。如图中所示,第二与门电路602的三个输入端分别与反相计数信号<2>、反相计数信号<1>和计数信号<0>连接,第二与门电路602的输出端输出选择信号<1>。第三与门电路603的三个输入端分别与反相计数信号<2>、计数信号<1>和反相计数信号<0>连接,第三与门电路603的输出端输出选择信号<2>。第四与门电路604的三个输入端分别与反相计数信号<2>、计数信号<1>和计数信号<0>连接,第四与门电路604的输出端输出选择信号<3>。第五与门电路605的三个输入端分别与计数信号<2>、反相计数信号<1>和反相计数信号<0>连接,第五与门电路605的输出端输出选择信号<4>。第六与门电路606的三个输入端分别与计数信号<2>、反相计数信号<1>和计数信号<0>连接,第六与门电路606的输出端输出选择信号<5>。第七与门电路607的三个输入端分别与计数信号<2>、计数信号<1>和反相计数信号<0>连接,第七与门电路607的输出端输出选择信号<6>。第八与门电路608的三个输入端分别与计数信号<2>、计数信号<1>和计数信号<0>连接,第八与门电路608的输出端输出选择信号<7>。

请结合图4的计数信号的脉冲时序图,可以看到,在第一时间周期T1,第一计数信号<0>为低电平,第二计数信号<1>为低电平,第三计数信号<2>为低电平,那对应的第一反相计数信号<0>为高电平,第二反相计数信号<1>为高电平,第三反相计数信号<2>为高电平,这样在第一时间周期T1,译码器电路的第一与门电路的三个输入端均为高电平,因此其输出的选择信号<0>为高电平。而其他与门电路的输入端均至少包括一个低电平信号,所以其他与门电路的输出端均为低电平。

在第二时间周期T2,第一计数信号<0>为高电平,第二计数信号<1>为低电平,第三计数信号<2>为低电平,那对应的第一反相计数信号<0>为低电平,第二反相计数信号<1>为高电平,第三反相计数信号<2>为高电平,这样在第二时间周期T2,第一与门电路的三个输入端的第一反相计数信号<0>为低电平,所以第一与门电路的输出选择信号<0>为低电平。而第二与门电路的三个输入端第一计数信号<0>为高电平,第二反相计数信号<1>为高电平,第三反相计数信号<2>为高电平,所以第二与门电路的输出端输出的选择信号<1>为高电平。而其他与门电路的输入端均至少包括一个低电平信号,所以其他与门电路的输出端均为低电平。

依此类推,在第三时间周期T3,只有第三与门电路的输出端输出的选择信号<2>为高电平,其他与门电路的输出端均为低电平。在第四时间周期T4,只有第四与门电路的输出端输出的选择信号<3>为高电平,其他与门电路的输出端均为低电平。在第五时间周期T5,只有第五与门电路的输出端输出的选择信号<4>为高电平,其他与门电路的输出端均为低电平。在第六时间周期T6,只有第六与门电路的输出端输出的选择信号<5>为高电平,其他与门电路的输出端均为低电平。在第七时间周期T7,只有第七与门电路的输出端输出的选择信号<6>为高电平,其他与门电路的输出端均为低电平。在第八时间周期T8,只有第八与门电路的输出端输出的选择信号<7>为高电平,其他与门电路的输出端均为低电平。

请参阅图7所示,其显示根据本发明的一个实施例的图3所示的数据传输电路的多路复用器电路的内部结构示意图。根据本发明的一个实施例,该多路复用器包括8个选择开关电路单元,因为每个选择开关电路单元的结构相同,为简化图式,图中仅仅示出2个选择开关电路单元。如图中所示,以第八选择信号<7>和第八并行输入信号<7>所在的选择开关电路单元为例,该选择开关电路单元包括由两个相对并联设置的Nmos晶体管和Pmos晶体管组成的传输门电路,其中Nmos晶体管的门极与选择信号<7>连接,由选择信号<7>控制,选择信号<7>经过一个反相器与Pmos晶体管的门极连接,Pmos晶体管的门极由反相的选择信号<7>控制。两个相对并联设置的Nmos晶体管和Pmos晶体管组成的传输门的输入端与第八并行输入信号<7>连接,两个相对并联设置的Nmos晶体管和Pmos晶体管组成的传输门的输出端连接至一个共同的串行输入信号线。同样的,第一至第七选择开关电路每个都包括由两个相对并联设置的Nmos晶体管和Pmos晶体管组成的传输门电路。第一至第七并行输入信号<6:0>分别对应输入第一至第七选择开关电路单元的传输门电路的输入端,第一至第七选择开关电路的传输门电路的输出端连接至共同的串行输入信号线,第一至第七选择开关电路的传输门电路的Nmos晶体管的门极由对应的第一至第七选择信号<6:0>控制,第一至第七选择开关电路的传输门电路的Pmos晶体管的门极由对应的反相的第一至第七选择信号<6:0>控制。

请参阅图3结合图8所示,本发明的数据传输电路还包括D触发器,多路复用器电路单元的各选择开关电路单元输出端共同连接的串行输入信号线作为输出端与D触发器的输入端连接,计数器的时钟信号经过反相器之后形成反相时钟信号,该反相时钟信号作为D触发器的时钟信号输入D触发器。D触发器在反相时钟信号的脉冲的上升沿发生动作,将串行输入信号转换成输出信号。如图8所示,反相时钟信号与时钟信号的脉冲时序图,在t1时间,在时钟信号的脉冲上升沿产生选择信号,在间隔半个时钟周期的t2时间,D触发器发生动作,产生输出信号。

请参阅图9所示,其显示本发明的数据传输电路的各个信号的脉冲时序图。结合前述图1至图8所示,再次将完整的信号传输过程进行说明。参考图4所示,本发明的数据传输电路的计数器电路单元接收时钟信号,根据不同的时钟信号周期频率间隔产生三个计数信号<1:0>,参考图5及图6所示,本发明的数据传输电路的译码器电路单元接收计数器电路单元输出的三个计数信号,产生8位选择信号<7:0>,参考图7所示,8位并行输入信号<7:0>经过数据传输电路的多路复用器电路,在选择信号<7:0>的控制下每次输出一位数据形成串行输入信号,参考图8所示,串行输入信号经过数据传输电路的D触发器形成串行输出信号。这样8位的并行输入信号经过本发明的数据传输电路转换为串行输出信号。

在前述实施例中,仅仅是以8位的并行输入信号作为一个具体实施例进行说明。当并行输入信号为其他任意位的信号时,可以相应地更改具体电路的配置来满足相应的传输需求。例如当并行输入信号为4位信号时,计数器单元可以产生2个计数信号,从而产生4个选择信号,这样可以控制4位并行输入数据输出串行输出数据。当并行输入信号为16位信号时,计数器单元可以产生4个计数信号,从而产生2

本发明的并行输入串行输出电路,只需要一个计数器单元,一个译码器单元,一个多路复用器单元以及一个D触发器,其结构简单,而且其数据传输速率较快,能够实现数据快速传输。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于本发明权利要求书的保护范围。

- 并行输入串行输出电路及采用该电路的存储器

- 数字信号并行输入转串行输出电路