一种基于IEEE标准Chiplet电路测试方法

文献发布时间:2023-06-19 10:27:30

技术领域

本发明涉及超大规模数字集成电路测试领域,尤其涉及一种基于IEEE标准Chiplet电路测试方法。

背景技术

随着芯片技术的发展,超大规模集成电路(Very Large Scale IntegrationCircuit,VLSI)制造技术已经成为支撑信息社会不断发展和前进的重要因素之一。其量产工艺如今已达到7nm,而且随着工艺的提高,工艺正在向5nm和3nm迈进。但是,也随着超大规模集成电路工艺复杂度的急剧上升,相应的制造成本也急剧增加。这给多领域芯片的设计和实现带来了巨大的挑战。当多个芯片集成到一个产品中时,组件的成品率越高,最终组装时的成品率损失就越低。业界和学术界普遍认为,“超级摩尔时代”和“后摩尔时代”即将到来。近年来,随着TSV(Through Silicon Via)技术的迅速发展,它为3D技术提供了一种新的体系结构。通过使用分层技术,可以组装出最合适的产品:一种可能的解决方案是将产量低的大型单芯片分成产量更高的小型芯片。这些芯片被制造,测试,然后组装在三维介质层。在上述背景下,Chiplet(又称芯粒或小芯片)异构集成技术作为解决上述问题的关键技术受到了广泛关注。芯片技术试图通过内部互连技术将多个模块化芯片集成到一个封装中,形成具有特殊功能的异构芯片,从而解决芯片开发所涉及的规模、开发成本和成本缩短周期时间等问题。通过采用2.5D、3D等先进封装技术,芯片可以实现高性能的多芯片片上互连,提高芯片系统的集成度,拓展其性能和功耗优化空间。此外,模块化集成方法能有效提高芯片研发速度,降低研发成本和芯片开发门槛,并能将芯片研发重点放在算法和核心技术上,提高行业整体创新水平和能力。根据上述集成方式,可测试性设计是一个明显的挑战,其中测试体系结构必须允许组装前单个芯粒测试和组装后整个芯片测试,才能提高故障覆盖率。而且在这种情况下,组装前测试到组装后测试的测试向量必须易于重定向,以减少测试开发工作,易于测试各个组件,进而减少测试成本。

发明内容

本发明的目的是提供一种基于IEEE标准Chiplet电路测试方法,通过这种电路测试方法不仅能够测试芯粒上经典逻辑(数字逻辑,IO,RAM等)以及测试连接的TSV,而且还能够测试最终芯片电路。利用IEEE 1687ICL和PDL语言对测试向量重定向,该操作可以实现从芯粒重定向到芯片的测试,从而保证了各个组件在不同层次的测试操作。

本发明提供一种基于IEEE标准Chiplet电路测试方法,所述方法包含以下步骤;

步骤一:读取所有设计的ICL和PDL,使用ICL和PDL对完整的芯片进行建模,并且利用工具插入测试电路;

步骤二:执行IEEE 1687标准设计规则检查,以验证指令和其他组件(如SIB等)是否正确地连接到设计的各个层次;

步骤三:进行芯粒到芯片的测试向量重定向,生成用于测试芯片的测试向量;

步骤四:将生成的重定向的IEEE 1687标准的PDL转换为testbench和标准测试矢量格式。

进一步改进在于:所述步骤一根据已有芯片层次RTL设计电路,读入非芯片层次所有ICL和PDL,构建芯片层次网络结构,再利用tessent工具自动插入TAP控制器、SIB/TDR、边界扫描单元测试电路,最后对其各个模块的ICL、PDL提取到数据库,生成最终网表。

进一步改进在于:所述步骤二执行IEEE 1687设计规则检查:首先对芯粒之间的ICL连接规则检查,然后对介质层和芯粒的ICL连接规则检查,最后完成整个芯片ICL连接规则检查。

进一步改进在于:所述步骤三中编写PDL过程来控制测试不同层次的操作,将芯粒的PDL描述重新定位到芯片。通过将当前设计变量设置为芯粒,生成用于测试芯粒的测试向量;通过将当前设计变量设置为芯片,生成用于测试芯片的测试向量。

进一步改进在于:所述步骤四是将重新定向的IEEE 1687 标准的PDL转换成testbench和标准测试向量,所述测试向量格式为WGL或STIL或SVF进行仿真验证和机台测试。

本发明的有益效果是:提出一种基于IEEE标准Chiplet电路测试方法,所提出的电路测试方法允许在芯粒和芯片层次进行测试,通过这种电路测试方法不仅能够测试芯粒上经典逻辑(数字逻辑,IO,RAM等)以及测试连接的TSV,而且还能够测试最终芯片电路。利用IEEE 1687ICL和PDL语言不仅可以对测试向量重定向,实现从芯粒重定向到芯片的操作,从而保证了各个组件在不同层次的测试,并且该结构更加灵活,可以在不增加面积成本的情况下提高测试有效性。

附图说明

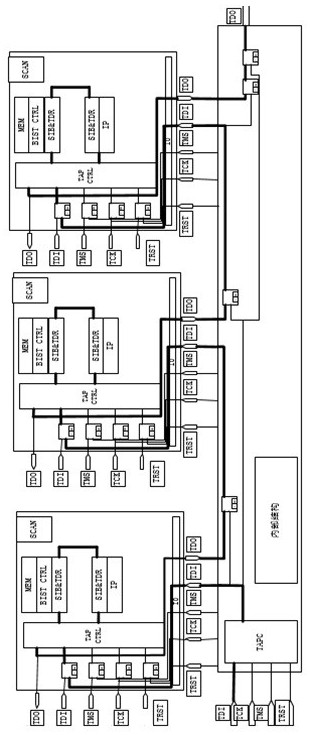

图1是本发明的基于IEEE 1687标准Chiplet电路测试设计图;

图2是本发明的基于IEEE 1687标准Chiplet测试电路的流程图;

图3是本发明的芯粒重定向芯片测试流程;

图4是本发明的基于SIB-TDR访问BIST电路控制Memory结构图。

具体实施方式

为了加深对本发明的理解,下面将结合实例对本发明作进一步详述,该实例仅用于解释本发明,并不构成对本发明保护范围的限定。

如图1-4所示,本实例提供一种基于IEEE标准Chiplet电路测试方法,所述方法步骤如下:

步骤一:读取所有设计的ICL和PDL,使用ICL和PDL对完整的芯片进行建模,并且利用工具插入测试电路;

步骤二:执行IEEE 1687标准设计规则检查,以验证指令和其他组件(如SIB等)是否正确地连接到设计的各个层次;

步骤三:进行芯粒到芯片的测试向量重定向,生成用于测试芯片的测试向量;

步骤四:将生成的重定向的IEEE 1687标准的PDL转换为testbench和标准测试矢量格式。

所述步骤一根据已有芯片层次RTL设计电路,读入非芯片层次所有ICL和PDL,构建芯片层次网络结构,再利用tessent工具自动插入TAP控制器、SIB/TDR、边界扫描单元测试电路,最后对其各个模块ICL、PDL进行提取到数据库,生成最终网表。所述步骤二中执行IEEE 1687标准设计规则检查:首先对芯粒之间的ICL连接规则检查,然后对介质层和芯粒的ICL连接规则检查,最后完成整个芯片ICL连接规则检查。所述步骤三中编写PDL过程来控制不同层次的测试,将芯粒的PDL描述重新定位到芯片,通过将当前设计变量设置为芯粒,生成用于测试芯粒的测试向量;通过将当前设计变量设置为芯片,生成用于测试芯片的测试向量。所述步骤四是将重新定向的IEEE 1687 标准的PDL转换成testbench和标准测试向量,所述测试向量格式格式为WGL或STIL或SVF进行仿真验证和机台测试。

本实例针对如何测试Chiplet结构这一技术难题进行改进,创新性地实例了一种基于IEEE 1687标准Chiplet电路测试方法,所实施的测试结构考虑到了芯粒、介质层和整个芯片的全面性。通过这种电路测试方法不仅能够测试芯粒上经典逻辑(数字逻辑,IO,RAM等)以及测试连接的TSV,而且还能够测试最终芯片电路。利用IEEE 1687ICL和PDL语言对测试向量重定向,该方法可以实现从芯粒重定向到芯片的操作,从而保证了各个组件在不同层次的测试。因此能够很好的检测出各个层次的故障,提高故障覆盖率。

图1给出了本实例基于IEEE 1687标准Chiplet电路测试设计图,如图所示,根据RTL描述构建芯片结构,即一个介质层堆积3个芯粒,形成整个芯片。读入非芯片层次所有ICL和PDL,构建芯片层次网络结构。DFT体系结构要求所有芯粒都插入作为测试访问机制的JTAG接口(TDI,TDO,TMS,TCK,可选的TRST)、TAP 控制器以及段插入位(SIB)和相关的测试数据寄存器(TDR)形成扫描链。利用tessent工具自动生成TAP 控制器通过SIB/TDR访问Mbist电路来测试内存以及测试IP模块,利用边界扫描寄存器测试端口等。芯粒中的选择器用于在芯粒和芯片之间切换测试路径。芯粒测试期间,将各自的测试数据分别输入到堆积的3个芯粒及介质层的TDI端口,通过各自的扫描链进行测试,再将测试结果分别从各自TDO端口输出,并且将输出结果和理论结果进行比较,如果输出结果和理论结果一致则测试没有问题,否则存在故障,并且测试期间,三个芯粒相互独立,互不影响。芯片测试期间,测试数据介质层的TDI传输到芯粒,使用指令寄存器配置测试路径,测试数据经过三个芯粒最后可到达介质层TDO(图1中的加粗线为路径),利用tessent工具编写测试流程从而对电路进行测试,同理,芯片测试期间通过TDI输入测试向量,通过TDO观察输出测试结果,将输出结果与理论结果对比。测试所需要的测试向量由PDL重新定向该组件生成的测试向量提供。介质层中的选择器用于旁路掉有故障的芯粒,进而更好的调整测试路径,提高测试覆盖率和节约测试时间。

图2给出了本实例基于IEEE 1687标准Chiplet电路测试流程图,如图所示,完成测试电路需要完成四大步骤,步骤一:读取所有设计的ICL和PDL,使用ICL和PDL对完整的芯片进行建模,并且利用工具插入测试电路;步骤二:执行IEEE 1687标准设计规则检查,以验证指令和其他组件(如SIB等)是否正确地连接到设计的各个层次;步骤三:进行芯粒到芯片的测试向量重定向,生成用于测试芯片的测试向量;步骤四:将生成的重定向的IEEE 1687标准的PDL转换为testbench和标准测试矢量格式。

步骤一包括根据已有芯片层次RTL设计电路,读入非芯片层次所有ICL和PDL,构建芯片层次网络结构,再利用tessent工具自动插入TAP控制器、SIB/TDR、边界扫描单元测试电路,最后对其各个模块ICL、PDL进行提取到数据库,生成最终网表。步骤二包括执行IEEE1687标准设计规则检查:首先对芯粒之间的ICL连接规则检查,然后对介质层和芯粒的ICL连接规则检查,最后完成整个芯片ICL连接规则检查。步骤三包括编写PDL过程来控制不同层次的测试,将芯粒的PDL描述重新定位到芯片,通过将当前设计变量设置为芯粒,生成用于测试芯粒的测试向量;通过将当前设计变量设置为芯片,生成用于测试芯片的测试向量。步骤四包括将重新定向的IEEE 1687 标准的PDL转换成testbench和标准测试向量,所述测试向量格式为WGL、STIL、SVF进行仿真验证和机台测试。

图3是本实例芯粒重定向芯片的测试流程。首先,对于DFT插入,TAP逻辑生成,BSR逻辑生成的所有任务都可以由工具自动完成。第一步芯粒测试,需要生成测试向量为测试芯粒提供测试输入,根据所设置的TAP chain路径,完成芯粒测试。其中TAP chain 包括SIB-TDR、内存BIST和边界扫描单元及测试模块等单元。第二步芯片测试,首先需要实现芯粒和介质层的连接形成整体芯片结构,根据所设置的TAP chain路径,完成芯片测试。其中TAP chain 包括介质层和三个芯粒内部所需要的SIB-TDR、内存BIST和边界扫描单元及测试模块等单元。测试芯粒和芯片都是通过PDL配置生成各层次所需要的测试向量。

图4是本实例基于SIB-TDR访问BIST电路控制memory结构图,提出的SIB-TDR寄存器集成到TAPchain中用于访问内建自测试电路,这些寄存器将实现不同的BIST命令寄存器,以设置和启动BIST电路,并最终读取内存BIST结果。其中,可以通过测试工具配置和处理SIB-TDR寄存器,以允许从芯粒或芯片通过Mbist对memory的测试。

以上所述仅为本发明的优选方案,并非作为对本发明的进一步限定,凡是利用本发明说明书及附图内容所作的各种等效变化均在本发明的保护范围之内。

- 一种基于IEEE标准Chiplet电路测试方法

- 一种基于TCL语言的数字电路快速测试方法