一种提高DDR仿真精度的封装模型及其建模方法

文献发布时间:2023-06-19 11:29:13

技术领域

本发明涉及电路仿真领域,具体的说,是涉及一种提高DDR仿真精度的封装模型及其建模方法。

背景技术

随着半导体集成电路的发展,DDR系统的速率越来越高,DDR的设计难度越来越大,为了节约开支,避免造成浪费,工程师会在PCB板完成设计之后、实际生产加工之前进行信号完整性的仿真,来预估最终成品的DDR系统的性能,因此仿真的精度成为能否精确预测性能的关键。

可是常见仿真方法,都是仿真人员根据供应商提供的主芯片和颗粒的模型,组合提取的PCB链路模型,进行DDR通道的仿真,此方式的仿真精度取决于主芯片的模型。而随着DDR的速率越来越高,尤其是DDR4级别,主芯片模型会出现精度下降的问题,当仿真人员对DDR数据信号DQ的同一组两个信号进行仿真时发现,两根信号差异非常大,其中一根信号的接收波形幅度衰减得很明显,基本上不满足协议的要求。

可是对该数据信号进行实际的测试后发现,示波器测试的结果不会出现幅度大幅下降的现象,与仿真结果严重不符,因此仿真结果并不能准确表示实际性能。在分析时发现,该传统仿真方法使用的主芯片模型,是通过RLC参数的形式来定义不同信号的封装链路,当RLC参数越大,根据频域分析理论可知,LC越大,高频的衰减会比较严重,从而导致仿真结果误差大,且不符合实际测试结果。

因此,在频率很高的时候,主芯片原有仿真模型已经不能准确地表征封装链路的实际情况,如何对封装模型进行重新建模,使得仿真和测试结果一致成为业内急需解决的问题。

发明内容

为了克服现有的技术的不足,本发明提供一种提高DDR仿真精度的封装模型及其建模方法。

本发明技术方案如下所述:

一方面,本发明提供一种提高DDR仿真精度的封装模型,其特征在于,包括电阻R以及具有阻抗Z和时延TD的传输线模型,所述传输线模型为:

根据上述方案的本发明,其特征在于,电阻R和传输线模型串联。

另一方面,本发明提供一种提高DDR仿真精度的封装模型建模方法,其特征在于,包括如下步骤:

步骤S1、获取供应商官网提供的主芯片的原始仿真模型;

步骤S2、提取RLC参数,即电阻R、电感L和电容C;

步骤S3、根据

步骤S4、将步骤S3所得的传输线模型串接原始封装模型的电阻R,获得修正后的封装模型;

步骤S5、利用步骤S4所得的修正后的封装模型表征主芯片与DDR颗粒之间的PCB封装链路;

步骤S6、对DDR颗粒的一组数据信号进行仿真。

根据上述方案的本发明,其特征在于,所述步骤S1中的主芯片为FPGA(FieldProgrammable Gate Array)芯片,所述FPGA芯片的原始仿真模型为IBIS(Input/OutputBuffer Information Specification)模型。

根据上述方案的本发明,其特征在于,所述步骤S2包括:

S21、打开IBIS模型文件,查看封装参数;

S22、获取供应商官网提供的主芯片的原始仿真模型电阻R、电感L和电容C电阻R、电感L和电容C。

根据上述方案的本发明,其特征在于,所述步骤S3中所得的阻抗Z和时延TD的数值均取小数点后三位。

根据上述方案的本发明,其特征在于,所述数据信号为差分信号,其包括第一数据信号和第二数据信号。

进一步的,所述第二数据信号的电阻大于两倍的所述第一数据信号的电阻。

进一步的,所述第二数据信号的电感大于两倍的所述第一数据信号的电感。

进一步的,所述第二数据信号的电容大于两倍的所述第一数据信号的电容。

根据上述方案的本发明,其特征在于,所述PCB封装链路的信号为高频信号。

根据上述方案的本发明,其有益效果在于:

本发明利用现有的主芯片仿真模型的RLC参数,进行修正,并串接现有的电阻,获得修正后的封装模型,通过修正后的封装模型仿真DDR系统的一组数据信号,获得与测试结果相符的仿真结果,可见,本发明提高了DDR仿真精度,确保了仿真结果和测试结果的一致性,为PCB板的设计和调试提供了精确的数据。

附图说明

图1为本发明的结构示意图;

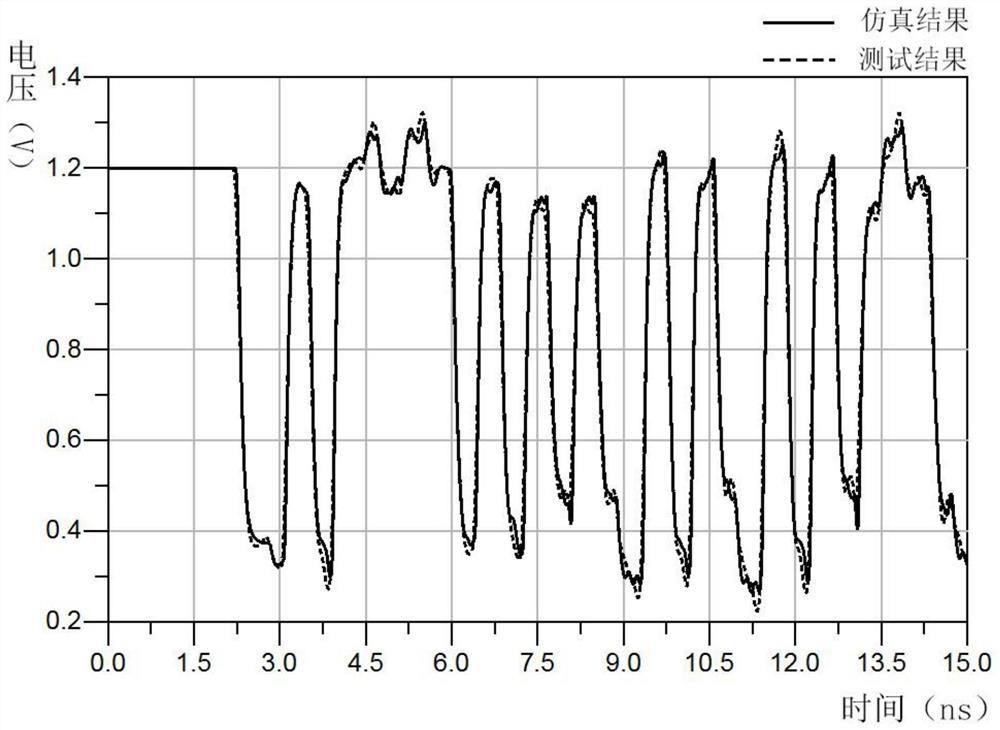

图2为本发明对第二数据信号的仿真结果与实测结果的对比图;

图3为本发明与现有技术对第二数据信号的仿真结果对比图;

图4为现有技术对第一数据信号的仿真结果;

图5为现有技术对第二数据信号的仿真结果;

图6为现有技术对第二数据信号的仿真结果与实测结果的对比图。

在图中,1、传输线模型;2、电阻。

具体实施方式

为了更好地理解本发明的目的、技术方案以及技术效果,以下结合附图和实施例对本发明进行进一步的讲解说明。同时声明,以下所描述的实施例仅用于解释本发明,并不用于限定本发明。

需要说明的是,术语“第一”、“第二”仅用于便于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明技术特征的数量。

如图1所示,一种提高DDR仿真精度的封装模型,包括电阻2以及具有阻抗Z和时延TD的传输线模型1,传输线模型1为:

电阻R、电感L和电容C的数值来源于供应商提供的主芯片IBIS(Input/OutputBuffer Information Specification)模型的RLC参数,传统的仿真模型是通过RLC参数的形式来定义,而本发明则利用RLC参数及公式

本发明提供一种提高DDR仿真精度的封装模型建模方法,包括如下步骤:

步骤S1、获取供应商官网提供的主芯片的原始仿真模型;

步骤S2、提取RLC参数,即电阻R、电感L和电容C,具体地,

S21、打开IBIS模型文件,查看封装参数;

S22、获取供应商官网提供的主芯片的原始仿真模型电阻R、电感L和电容C电阻R、电感L和电容C;

步骤S3、根据

步骤S4、将步骤S3所得的传输线模型串接原始封装模型的电阻R,获得修正后的封装模型;

步骤S5、利用步骤S4所得的修正后的封装模型表征主芯片与DDR颗粒之间的PCB封装链路;

步骤S6、对DDR颗粒的一组数据信号进行仿真。

在本实施例中,列举了业界常用的一款FPGA(Field Programmable Gate Array)芯片,其模型为IBIS(Input/Output Buffer Information Specification),对DDR数据信号DQ的同一组数据信号(该数据信号为差分信号,其包括第一数据信号和第二数据信号第一数据信号DQ1和第二数据信号DQ2)进行仿真,其中,

第一数据信号DQ1的封装参数为R1=1.02015Ω,L1=6.2553e

第二数据信号DQ2的封装参数为R2=2.70795Ω,L2=1.52655e

由上述数值可知,第二数据信号DQ2的电阻大于两倍的第一数据信号DQ1的电阻,第二数据信号DQ2的电感大于两倍的第一数据信号DQ1的电感,第二数据信号DQ2的电容大于两倍的第一数据信号DQ1的电容。

如图4、图5所示,采用RLC参数对DDR数据信号的同一组信号进行仿真,由图可知,尽管同一组信号用相同的IO-buffer输出模型,但是第一数据信号DQ1与第二数据信号DQ2的波形差异非常大,而且第二数据信号DQ2波形幅度大幅衰减。

可见,传统的仿真模型直接用RLC参数去表征封装走线,但是当PCB封装链路的信号包括高频信号时,只用一级的RLC参数不能准确表征其电性能,必须使用多级的RLC参数,但是供应商提供的模型参数只有一级的RLC参数,因此传统的仿真模型无法表征兆赫兹以上的封装走线的真实性能。因此采用传统的仿真模型,设计人员就会错误地定义该PCB板性能不佳。

如图6所示,对上述波形衰减严重的第二数据信号DQ2进行实际测试,从示波器的测试结果和仿真结果对比可知,仿真结果与测试结果并不一致,因此采用传统仿真模型在LC参数较大的情况下,仿真结果并不能准确地预测实际性能,极易造成设计人员对PCB板性能的误判。

如图2、图3所示,采用本发明的传输线模型对波形衰减严重的第二数据信号DQ2进行模型转换,得到具有阻抗Z和时延TD的传输线模型,再串联原电阻R

阻抗Z和时延TD的数值均取小数点后三位。

最后采用修正后的封装模型进行仿真,仿真结果与测试结果对比,参照图2,并将本发明的仿真结果与传统模型的仿真结果进行比较,参照图3。因此采用本发明的封装模型得到的第二数据信号DQ2并没有发声波形大幅衰减的现象,且仿真出来的结果与实测结果非常接近,仿真结果能够准确地预测实际性能。

综上所述,本发明利用现有的主芯片封装模型的RLC参数,进行修正,获得传输线模型,并串接现有的电阻R,获得新的封装模型,通过该封装模型仿真DDR系统的数据信号,提高了仿真精度,使得仿真结果和测试结果具有很好的一致性,修正了传统模型仿真结果误差大的问题,为DDR芯片的设计和调试提供了精确的数据。

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

以上实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

- 一种提高DDR仿真精度的封装模型及其建模方法

- 一种用于提高精密机床空间几何误差模型建模精度的方法