半导体装置以及其形成方法

文献发布时间:2023-06-19 11:45:49

技术领域

本发明是有关于一种半导体装置以及其形成方法,且特别是有关于半导体装置的焊垫层以及其形成方法。

背景技术

半导体集成电路产业经历快速成长,集成电路设计与材料的科技发展生产了数世代的集成电路,其中每个世代具备比上个世代更小及更复杂的电路。集成电路广泛地应用于消费性电子产品中,例如,个人电脑、智慧型手机或平板电脑等。

一般而言,半导体集成电路装置具有与外部电子元件电连接的焊垫结构,由于焊垫结构在封装工艺完成之前通常会暴露于环境之中一段时间,若工艺中有化学物质残留于焊垫结构上,化学物质与环境中的空气或水气反应,将更容易导致焊垫结构的氧化或腐蚀,进而降低最终产品的良品率。

虽然现存的焊垫结构的形成方法可大致满足它们原先预定的用途,但其仍未在各个方面皆彻底地符合需求。因此,发展出能够进一步改善焊垫结构的良品率的工艺,仍为目前业界致力研究的课题之一。

发明内容

根据本发明一些实施例,提供一种半导体装置的形成方法,包含以下步骤:提供半导体衬底(substrate);形成焊垫层于半导体衬底上;形成第一钝化层于焊垫层上;形成第二钝化层于第一钝化层上,其中第二钝化层包含多晶硅;形成氧化层于第二钝化层上;形成氮化层于氧化层上;移除氧化层的一部分以及氮化层的一部分,以暴露出第二钝化层的一部分;移除经暴露的该第二钝化层的一部分,以暴露出第一钝化层的一部分;以及移除经暴露的第一钝化层的一部分,以暴露出焊垫层的一部分。

根据本发明一些实施例,提供一种半导体装置,包含:半导体衬底、焊垫层、第一钝化层、第二钝化层、氧化层以及氮化层。焊垫层位于半导体衬底上,第一钝化层位于焊垫层上,第二钝化层位于第一钝化层上,其中第二钝化层包含多晶硅,氧化层位于第二钝化层上,且氮化层位于氧化层上。此外,半导体装置还包含开口,其贯穿第一钝化层、第二钝化层、氧化层以及氮化层,且暴露出焊垫层的顶表面。

为让本发明的特征、或优点能更明显易懂,下文特举出较佳实施例,并配合所附图式,作详细说明如下。

附图说明

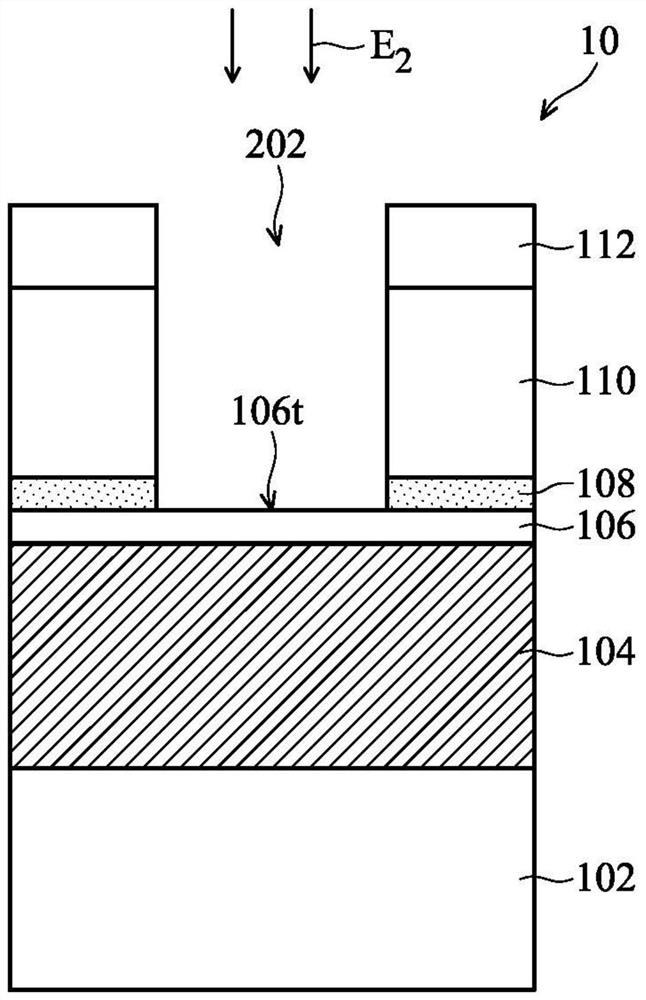

图1A至图1G显示根据本发明一些实施例中,半导体装置于其形成方法中各阶段的结构剖面示意图。

符号说明

10 半导体装置;

102 半导体衬底;

104 焊垫层;

104t 顶表面;

106 第一钝化层;

106t 顶表面;

108 第二钝化层;

108t 顶表面;

110 氧化层;

110s 侧壁;

112 氮化层;

112s 侧壁;

202 开口;

C

E

E

E

PL 高分子副产物;

PR 掩膜层;

T

具体实施方式

以下针对本发明实施例的半导体装置的形成方法以及由前述方法所形成的半导体装置作详细说明。应了解的是,以下所述特定的元件及排列方式仅为简单清楚描述本发明一些实施例,这些仅用以举例而非本发明的限定。

本发明实施例可配合图式一并理解,本发明的图式亦被视为揭露说明的一部分。应理解的是,本发明的图式并未按照比例绘制,事实上,可能任意的放大或缩小元件的尺寸以便清楚表现出本发明的特征。再者,当述及一第一材料层位于一第二材料层上或之上时,包含第一材料层与第二材料层直接接触,或者不直接接触而间隔有一或更多其它材料层的情形。

于文中,“约”或“实质上”的用语通常表示在一给定值或范围的10%内,或0.5%之内。在此给定的数量为大约的数量,亦即在没有特定说明“约”或“实质上”的情况下,仍可隐含“约”或“实质上”的含义。

根据本发明一些实施例,提供的半导体装置的形成方法包含形成含有多晶硅的钝化层于焊垫层上,使其作为刻蚀停止层。此外,根据本发明一些实施例,于半导体装置的形成方法中,用于移除钝化层的刻蚀工艺不使用含氟气体,藉此可减少刻蚀工艺残留的化学物质与焊垫层反应进而造成焊垫层容易腐蚀的问题,可有效改善作为顶部金属层(topmostmetal layer)的焊垫层的良品率。

图1A至图1G显示根据本发明一些实施例中,半导体装置10于其形成方法中各阶段的结构剖面示意图。应理解的是,可于半导体装置10的制造方法进行前、进行中及/或进行后提供额外的操作。根据一些实施例,以下所述的一些阶段可以被取代或删除。根据一些实施例,可添加额外特征于半导体装置10。根据一些实施例,以下所述的半导体装置10的部分特征可以被取代或删除。

根据一些实施例,半导体装置10可包含存储器结构,例如,易失性存储器(volatile memory)或非易失性存储器(nonvolatile memory)例如快闪存储器(flashmemory),但本发明不以此为限。

请参照图1A,首先,提供半导体衬底102。在一些实施例中,半导体衬底102中已先形成有合适的半导体元件,例如,半导体衬底102可包含晶体管元件与电容元件等。

接着,形成焊垫层104于半导体衬底102上,焊垫层104可作为与外部电子元件电连接的顶部金属层。在一些实施例中,焊垫层104可包含金属导电材料,例如可包含铝(Al)、铜(Cu)、钨(W)、铝合金、铜合金、钨金、或前述的组合,但不限于此。

再者,焊垫层104可具有厚度T

如图1A所示,接着,形成第一钝化层106于焊垫层104上,第一钝化层106可保护焊垫层104,减缓焊垫层104氧化的速度,或可降低电子迁移(electron migration)的现象。在一些实施例中,第一钝化层106的材料可包含氮化钛(titanium nitride,TiN),但不限于此。

再者,第一钝化层106可具有厚度T

接着,形成第二钝化层108于第一钝化层106上,第二钝化层108可作为刻蚀停止层,防止用于移除氧化层110及氮化层112的刻蚀工艺影响到位于第二钝化层108下方的层别,例如,第一钝化层106与焊垫层104。在一些实施例中,第二钝化层108的材料与第一钝化层106不同,且亦与位于其上方的氧化层110不同。此外,在一些实施例中,第二钝化层108的材料与氧化层110的材料具有不同的刻蚀选择比。具体而言,在一些实施例中,第二钝化层108的材料可包含多晶硅(polysilicon)。

再者,第二钝化层108可具有厚度T

值得注意的是,第二钝化层108由特定的材料形成且具有特定的厚度,且后续将由特定的刻蚀工艺进行移除,因此可有效地作为刻蚀停止层并且可避免用于移除氧化层110及氮化层112的刻蚀工艺所残留的化学物质(例如,卤素物质)与焊垫层104反应进而造成焊垫层104容易腐蚀的问题。关于移除第二钝化层108的详细工艺将于下文进行说明。

接着,形成氧化层110于第二钝化层108上。在一些实施例中,氧化层110的材料可包含氧化硅(silicon oxide),但不限于此。在一些实施例中,氧化层110的材料可为藉由高密度电浆(high density plasma,HDP)化学气相沉积(chemical vapor deposition,CVD)工艺所形成的氧化硅。

再者,氧化层110可具有厚度T

如图1A所示,接着,形成氮化层112于氧化层110上。在一些实施例中,氮化层112的材料可包含氮化物,例如氮化硅(silicon nitride)、氮氧化硅(silicon oxynitride)、或前述的组合,但不限于此。

再者,氮化层112可具有厚度T

在一些实施例中,可藉由化学气相沉积(chemical vapor deposition,CVD)工艺、物理气相沉积工艺(physical vapor deposition,PVD)、电镀工艺、无电镀工艺、旋转涂布(spin on coating)、热氧化(thermal oxidation)工艺、前述的组合、或其它合适的工艺形成前述的半导体衬底102、焊垫层104、第一钝化层106、第二钝化层108、氧化层110及氮化层112。

接着,请参照图1B,可形成掩膜层PR于氮化层112上,以定义出后续将形成于氧化层110及氮化层112中的开口202的位置。在一些实施例中,掩膜层PR可包含光阻材料。

接着,请参照图1C,移除氧化层110的一部分以及氮化层112的一部分,以暴露出第二钝化层108的一部分。详细而言,在一些实施例中,可使用经图案化的掩膜层PR作为遮罩,移除未被掩膜层PR遮蔽的氧化层110及氮化层112,以形成贯穿氧化层110及氮化层112的开口202,且开口202可暴露出第二钝化层108的一部分的顶表面108t。

再者,在一些实施例中,移除氧化层110的一部分以及氮化层112的一部分是藉由第一刻蚀工艺E

在一些实施例中,第一刻蚀工艺E

此外,如图1C所示,在一些实施例中,第一刻蚀工艺E

接着,请参照图1D,在一些实施例中,于移除氧化层110的一部分以及氮化层112的一部分之后,可移除前述经图案化的掩膜层PR。在一些实施例中,可藉由湿式剥除工艺、电浆灰化工艺、或前述的组合移除掩膜层PR。

接着,请参照图1E,在一些实施例中,于移除图案化的掩膜层PR之后,可藉由清洁工艺C

接着,请参照图1F,移除经暴露的第二钝化层108的一部分,以暴露出第一钝化层106的一部分,例如,暴露出第一钝化层106的顶表面106t。具体而言,在一些实施例中,移除经暴露的第二钝化层106的一部分是藉由第二刻蚀工艺E

在一些实施例中,第二刻蚀工艺E

在另一实施例中,第二刻蚀工艺E

接着,请参照图1G,移除经暴露的第一钝化层106的一部分,以暴露出焊垫层104的一部分,例如,暴露出焊垫层104的顶表面104t。具体而言,在一些实施例中,移除经暴露的第一钝化层106的一部分是藉由第三刻蚀工艺E

在一些实施例中,第三刻蚀工艺E

应理解的是,虽然前述实施例中,第二刻蚀工艺E

此外,在一些实施例中,于移除第一钝化层106以暴露出焊垫层104之后,可藉由清洁工艺(未标示)清除第三刻蚀工艺E

如图1G所示,于此阶段完成的半导体装置10可包含半导体衬底102、焊垫层104、第一钝化层106、第二钝化层108以及氧化层110。焊垫层104可位于半导体衬底102上,第一钝化层106可位于焊垫层104上,第二钝化层108可位于第一钝化层106上,氧化层110可位于第二钝化层108上,氮化层112可位于该氧化层上。此外,半导体装置10可具有开口202,开口202贯穿第一钝化层106、第二钝化层108、氧化层110以及氮化层112,且暴露出焊垫层104的顶表面104t。

承前述,根据一些实施例,焊垫层104可作为半导体装置10的顶部金属层,将会持续暴露于环境中直到封装工艺完成,并进一步与合适的外部电子元件进行耦接,但本发明不以此为限。根据一些实施例,本发明提供的半导体装置的形成方法亦可应用于形成接触结构的导通孔(via)的工艺。

综上所述,根据本发明一些实施例,提供的半导体装置的形成方法包含形成含有多晶硅的第二钝化层于焊垫层上,且第二钝化层可作为刻蚀停止层。此外,根据本发明一些实施例,用于移除第一钝化层及第二钝化层的刻蚀工艺不使用含氟气体(例如四氟化碳(CF

虽然本发明的实施例及其优点已揭露如上,但应该了解的是,任何所属技术领域中相关技术人员,在不脱离本发明的精神和范围内,当可作更动、替代与润饰。本发明的保护范围当视前述的权利要求书范围所界定者为准。

- 芯片封装及其形成方法、半导体器件及其形成方法、半导体装置及其形成方法、三相系统

- 半导体膜的形成方法、半导体器件的形成方法和半导体器件