全局时钟同步传输方法

文献发布时间:2023-06-19 11:55:48

技术领域

本发明涉及一种全局时钟同步传输方法,所述的全局时钟同步传输方法主要是通过主设备只发送高位计数数据,使从设备可基于高位计数数据计算出低位计数数据,据此判断是否达成时钟同步。

背景技术

全局时钟应用领域繁多,全局时钟可确保系统中各硬件设备(芯片模块或电路板)之间有完全相同的时间基准。

当多个硬件设备协同工作时,设备之间的数据通讯需要通过发送和接收数据包来完成。为了方便同步不同类型数据包和分辨同类型数据包的先后顺序,数据包发送设备通常会将数据包打上时间戳。

每个数据发送设备都要有自己单独的计数器,当多个设备协同工作时,通常每个设备即要发送数据包,又要接收数据包。

由于每个设备使用自己单独的计数器,使得每个设备发送数据包的时间戳和接收到的数据包时间戳没有关联性,同时每个设备收到不同发送端发送的数据包时间戳也没有关联性,很容易造成数据包发送和接收的混乱。

在实际应用中,通常通过时钟同步算法同步各协同工作设备的计数器,使得各设备计数时钟在同一时间相同,或者时钟计数误差在一个可以接受的范围内,所述的时钟同步算法实施时,时钟同步算法主要通过主设备统一发送时钟计数数据包给各个从设备,使各个从设备所收到的时钟计数达到一致,达到时钟同步目的。

以目前时钟同步算法为例,主设备每隔一段间隔时间发布数据包,所述的数据包包含有主设备计数器所产生的时钟计数数据,从设备获取数据包中时钟计数数据,判断是否达到时钟同步,然而,由于数据包包含整个时钟计数数据,主设备与从设备之间需耗费较多的数据发送量,而数据通讯功耗也会随之增加。

目前电子产品设计上都以节省功耗做为设计重点。有些做法是减少数据发送次数,但这将会延长从设备确认时钟同步的时机,可能造成主设备与从设备误差更严重,这并不是设计者所希望看到的状况,所以,如何以较小的数据发送量达成时钟同步,这是急需解决的问题。

发明内容

有鉴于上述的问题,本发明人依据多年来从事相关行业的经验,针对全局时钟同步传输方法进行研究及改进,本发明的主要目的在于提供一种主设备仅需发送部分时钟计数数据至从设备,就能达成全局时钟同步传输的方法。

为达到上述目的,本发明的全局时钟同步传输方法,其应用于一个数字硬件系统,所述的数字硬件系统包含有一个主设备及至少一个从设备,实施时,主设备将一个时钟计数数据包传送给各个从设备,所述的时钟计数数据包只带有一个高位计数数据,各个从设备可基于高位计数数据自行计算出一个低位计数数据,使各从设备储存全部 (高位和低位)计数数据后开始计数作业,当各从设备再次收到时钟计数数据包后,从设备即可比对全部(高位和低位)计数数据,判断从设备是否与主设备达到时钟同步,因此,主设备仅需传送高位计数数据给从设备,以大幅减少数据的发送量及减少数据通讯功耗。

为使贵审查委员得以清楚了解本发明的的目的、技术特征及其实施后的功效,兹以下列说明搭配图示进行说明,敬请参阅。

附图说明

图1为本发明的硬件系统架构图。

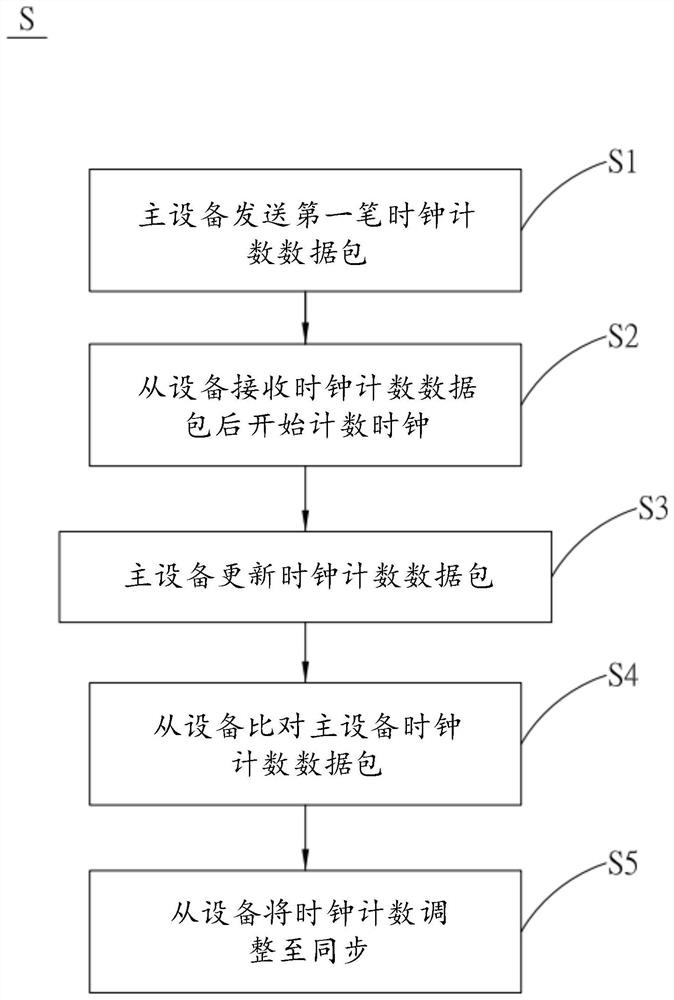

图2为本发明的实施流程图。

图3为本发明时钟计数数据包结构的实施例(一)。

图4为本发明时钟计数数据包结构的实施例(二)。

图5为本发明数据包间隔周期设定的实施例(一)。

图6为本发明数据包间隔周期设定的实施例(二)。

具体实施方式

请参阅「图1」,图中所示为本发明的硬件系统架构图,如图,本发明的数字硬件系统10,其主要具有一个主设备101及至少一个从设备(102、102’、102”),其中,主设备101及各从设备(102、102’、 102”)分别具有一个计数器,所述的计数器可供执行计数任务及比对计数数据,主设备和从设备可为同一电路板上的芯片,或以数据线连接安装有芯片的不同电路板。

主设备101和各从设备(102、102’、102”)的间通过数据线完成信息连接,所述的数据线可以差分线或单端线,主设备101通过数据线定时将主设备的一个时钟计数数据包发送给所有从设备(102、102’、 102”)。

各从设备(102、102’、102”)接收主设备101的时钟计数数据包后,各个从设备(102、102’、102”)可触发计数器进行计数、以及各从设备 (102、102’、102”)比对时钟计数数据包的数据调整从设备计数器的计数数据,使各从设备(102、102’、102”)的时钟计数数据与主设备101 的时钟计数数据误差在一个极小的误差范围内,即各从设备(102、102’、102”)的计数器锁定主设备101的时钟计数器,从设备(102、102’、102”) 可以将这个锁定信息,通过发送计数时钟的数据线传送,也可以建立专属的锁定数据线发送给主设备101,或者,从设备(102、102’、102”) 可以不发送锁定信息给主设备101以简化全局时钟同步程序。

在全局时钟同步传输过程中,主设备101需要定时将完整的时钟计数数据通过数据线以数据包的形式发送给从设备(102、102’、102”),数据线可以是专门用于全局时钟同步的专用数据线,也可以是设备间通讯的通用数据线,本发明的数据线使用专门用于全局时钟同步的专用数据线,使主设备101与从设备(102、102’、102”)间传输其它数据时,不会因为传输其它数据而影响到主设备101精准发送时钟计数数据的时间。

请参阅「图2」,图中所示为本发明的实施流程图。本发明的硬件全局时钟同步传输方法S如图,其包含:

(1)主设备发送第一笔时钟计数数据包S1:设备初始化后,主设备的计数器基于一个时钟计数周期进行计数,历经一个时钟计数周期后,主设备计数器将一个时钟计数数据包通过数据线发布到至少一个从设备;所述的时钟计数周期是介于2的16次方纳秒(ns)~2的32次方纳秒,最佳为2的24次方纳秒,时钟计数周期可以依据需求设定,选择以低位为零的数值作为时钟计数周期,例如65,536纳秒(即2的 16次方纳秒),时钟计数周期的设定以节省功耗作为考虑,时钟同步传输中,如果时钟计数周期很短,从设备可以经常接收到主设备的时钟计数数据包调整从设备的时钟计数数据,可以确保从设备的时钟计数数据与主设备的时钟计数数据同步或接近于同步,然而主设备通讯功耗也相对提高,如果时钟计数周期很长,主设备需等待很长一段时间才能发送一次时钟计数数据包给从设备,如此,主设备可以节省通讯功耗,但从设备接收数据包的间隔时间较长,可能会造成较大的同步误差;

(2)因此,本实施例中以16,777,216纳秒(约16ms)为最佳实施例,可满足多数应用在100纳秒左右的主设备与从设备计数误差要求,所述的时钟计数数据包包含有一个包头、一个高位计数数据和一个数据包包尾,其中,高位计数数据可以依据需求设定,可以选用8位(bit,亦可称比特)、24位或40位等,另外,主计数器进一步对低位计数数据补0,例如,当主设备计数到16,777,216纳秒时,主设备的计数十六进制表示为0x1000000,即高位为0x1、低位为0x0,如果主设备时钟计数器设定为32位时,主设备发给从设备的高位计数数据应为8 位(8’b00000001),低位部分全部为 0(24’b000000000000000000000000(24’h0))(主设备仅发送高位计数数据);

(3)从设备接收时钟计数数据包后开始时钟计数S2:在从设备初始化完成后,各个从设备收到主设备发来的时钟计数数据包后,各从设备可分别取出数据包中的高位计数数据,各个从设备计数器可进一步基于数据包中的高位计数数据,经补零计算出低位计数数据,储存全部数据(即高位计数数据和低位计数数据)并开始计数作业;

(4)主设备更新时钟计数数据包S3:主设备计数器再次计数至指定的时钟计数周期(例如16,777,216纳秒)时,主设备计数器更新时钟计数数据包中高位计数数据,并且将更新后的时钟计数数据包再次发布至各个从设备,例如,主设备计数器计数到33,554,432纳秒(即下一次16,777,216纳秒)时,主设备计数器以十六进制表示为”0x2000000”,即高位为”0x2”、低位为”0x0”,如果主设备为32位计数,主设备发给从设备的计数应为高位为8位,即为8’b00000010,低位全部为0,即为24’b000000000000000000000000(24’h0)(主设备仅发送高位计数数据);

(5)从设备比对主设备时钟计数数据包S4:从设备再次收到主设备的时钟计数数据包后,从设备以数据包中经过低位补零的计数数据,比对从设备计数器的时钟计数数据,若主设备的时钟计数数据和从设备的时钟计数数据之间误差在一误差允许范围内,从设备即可判断从设备的时钟计数数据与主设备的时钟计数数据达到同步,并等待主设备下一笔发送的时钟计数数据包进行下一次比对,若主设备的时钟计数数据与从设备的时钟计数数据未在误差允许范围内(即误差过大),则进行下一步骤,所述的误差允许范围可依据主设备与从设备的应用进行设定,例如,视频电子标准协会(VESA)制定的数字式视频接口标准(DisplayPort)中,全局时间码(Global Time Code,GTC)用于Video和 Audio之间的同步,标准要求,在GTC保持阶段(maintenance phase), GTC master和GTC slave的时钟计数数据误差在平均+-50纳秒,最大误差不能超过+-100纳秒;

(6)从设备将时钟计数调整至同步S5:若主设备的时钟计数数据与从设备的时钟计数数据之间差值未在误差允许范围内,则从设备调整从设备计数时钟的频率或调整从设备每个时钟周期的计数增加值,然后重复上述步骤「主设备更新时钟计数数据包S3」和「从设备比对主设备时钟计数数据包S4」,直到从设备的时钟计数数据值再次与主设备的时钟计数数据值同步,即主设备的时钟计数数据和从设备的时钟计数数据误差维持在误差允许范围内。

承上,主设备每个时钟周期计数器增加2的整数次幂,例如主设备时钟使用125MHz,每个时钟周期计数器计数增加为8,每个时钟周期为8纳秒,如果主设备时钟使用62.5MHz,则每个时钟周期计数器计数增加为16,代表每个时钟周期为16纳秒,为了尽量减少主设备发给从设备的计数数据量(bit,位/比特),同时维持主设备与从设备之间数据包发送时间在合适区间内,主设备优先选择以16,777,216纳秒作为数据包发送时间的间隔周期,但不以此为限,其中,16,777,216 为2的24次方,所以每次主设备为从设备发送时钟计数数据时,主设备只需发送时钟计数数据中高位计数数据(数据不为0的部分)至从设备,而不发送低位(24位)数据,从而减少主设备的数据发送量。

请参阅「图3」,图中所示为本发明时钟计数数据包结构的实施例(一),如图,实施例(一)中,主设备计数器以24位作为低位计数数据,当主设备时钟计数器采用32位计数规格时,每次只需发送高位计数数据给从设备102,即,主设备时钟计数数据获取高位计数数据的部分,即32位-24位=8位。

请参阅「图4」,图中所示为本发明时钟计数数据包结构的实施例(二),如图,主设备计数器以24位作为低位计数数据,当主设备时钟计数器采用64位计数规格时,每次只需发送高位计数数据给从设备102,即,主设备时钟计数数据获取高位计数数据的部分,即64位-24位=40位。

请参阅「图5」,图中所示为本发明数据包间隔周期设定的实施例(一),图中所示为主设备发送时钟计数数据包D及下一笔时钟计数数据包D’的间隔时间,当主设备计数器使用16,777,216纳秒作为时钟计数周期,且主设备时钟采用125MHz计数时,每个主时钟周期时钟计数增加8,则主设备时钟计数数据包(D、D’)发送的间隔周期为 16,777,216÷8=2,097,152个主设备时钟计数周期。

请参阅「图6」,图中所示为本发明数据包间隔周期设定的实施例(二),图中所示为主设备发送时钟计数数据包D及下一笔时钟计数数据包D’的间隔时间,当主设备计数器使用了16,777,216纳秒作为时钟计数周期,且主设备时钟采用62.5MHz计数时,每个主时钟周期时钟计数增加16,则主设备数据包发送的间隔周期为16777216÷ 16=1,048,576个主设备时钟计数周期。

综上可知,本发明的用于数字硬件系统的全局时钟同步传输方法,主要通过主设备向多个从设备发送时钟计数数据包,使从设备接收到数据包后可开始计数或确认是否达到时钟同步,其中,主设备所发送的时钟计数数据包中只保留高位计数数据,当从设备收到时钟计数数据包后,从设备可基于高位计数数据,经补零计算出低位计数数据,使从设备计数器可以比对全部计数数据(即高位计数数据和低位计数数据),进而确认从设备计数器是否与主设备计数器形成同步,并进行修正至同步。

本发明其据以实施后,确实可达到提供一种主设备仅需发送部分时钟计数数据至从设备,达到全局时钟同步传输的目的。

以上所述者,仅为本发明的较佳的实施例而已,并非用以限定本发明实施的范围;任何熟悉此技术者,在不脱离本发明的精神与范围下所作的均等变化与修饰,皆应涵盖于本发明的专利范围内。

【符号说明】

10数字硬件系统

101主设备 102从设备

102’从设备 102”从设备

D时钟计数数据包

D’时钟计数数据包

S硬件全局时钟同步传输方法

S1主设备发送第一笔时钟计数数据包

S2从设备接收时钟计数数据包后开始计数时钟

S3主设备更新时钟计数数据包

S4从设备比对主设备时钟计数数据包

S5从设备将时钟计数调整至同步。

- 全局时钟同步传输方法

- 用于基于全局时钟对计数器进行同步采样的技术