一种AOCC系统软件和鉴定级原理样机用调试平台及测试方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及航天系统测试技术领域,具体涉及一种AOCC系统软件和鉴定级原理样机用调试平台及测试方法。

背景技术

现阶段的航天系统测试领域,测试对象种类繁多,从单板测试到整星测试,从功能测试到性能测试,从开环测试到闭环测试。在所有测试阶段都需要有针对性的研制相应的测试设备,达到对航天产品全面和有效的测试。同时,随着航天产品的复杂度不断提高,对测试设备的要求也越来越高,测试设备正朝着高可靠、智能化、标准化、通用化、网络化的方向发展。随着型号产品的不断增加及研制周期的不断缩短,测试设备的研制进度和可靠性保证成为关键性的问题,如何实现测试设备硬件和软件的通用化平台,满足安全性、可靠性、小型化、可扩展的要求成为现阶段测试设备研制需要考虑的首要问题。

发明内容

针对现有技术存在的不足,本发明的目的在于提供一种AOCC系统软件和鉴定级原理样机用调试平台及测试方法,以提供AOCC系统与开发的硬件运行平台,整个平台应用范围广泛,测试功能多,集成度高,以满足安全性、可靠性、小型化、可扩展的要求。

为了实现上述目的,本发明提供如下技术方案:

一种AOCC系统软件和鉴定级原理样机用调试平台,包括包括主控板和测试板,所述主控板与所述测试板通过连接器进行信号传输,所述主控板的输入端电信号连接有上位机,所述主控板用于解析上位机测试流程控制指令,控制测试板进行相应测试,并将测试结果发回给上位机;

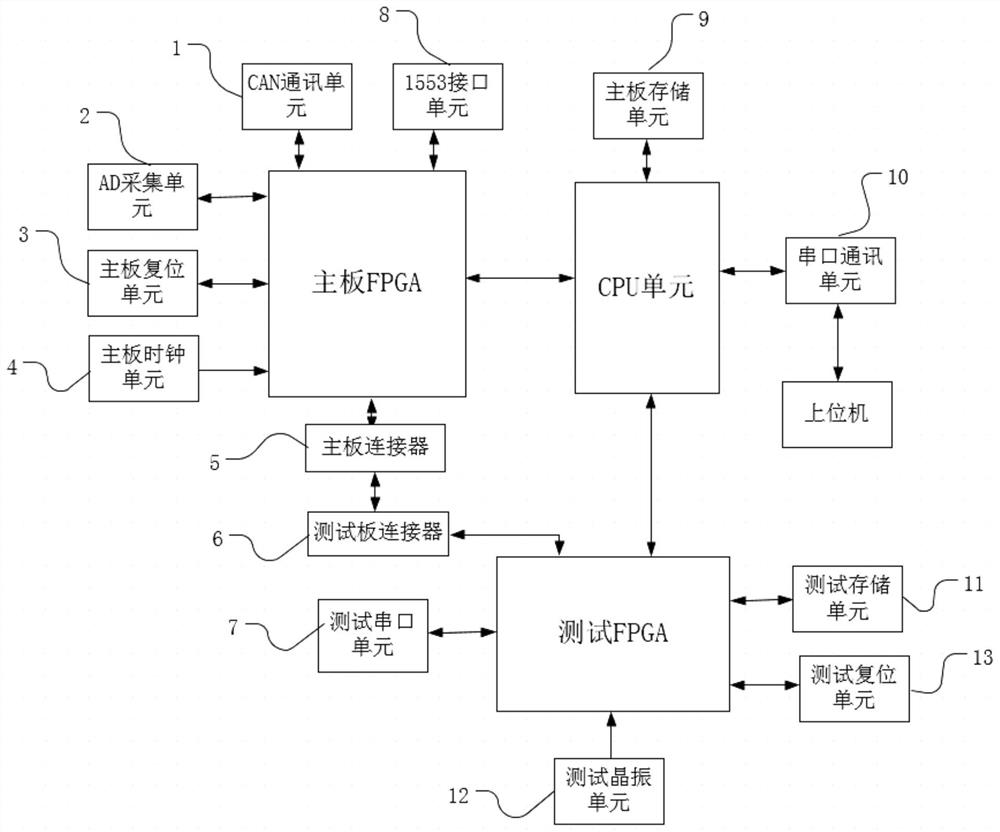

在本发明中,进一步的,所述主控板包括CPU单元、主板FPGA,所述CPU单元与主板FPGA电信号连接,所述CPU单元用于解析上位机测试流程指令并控制主板FPGA指令的收发,所述测试板包括测试FPGA,所述CPU单元、主板FPGA均与所述测试FPGA电信号连接,所述测试FPGA用于处理主板FPGA发出的指令以调用相应测试模块,实现待测产品的测试采集信号的处理、校验、上传。

在本发明中,进一步的,所述主控板还包括串口通讯单元和主板存储单元,所述串口通讯单元、主板存储单元均与所述CPU单元电信号连接,所述串口通讯单元用于与上位机进行数据传输,所述主板存储单元用于对主控板中的数据进行存储。

在本发明中,进一步的,所述主控板还包括CAN通讯单元、主板复位单元、1553接口单元、主板时钟单元,所述CAN通讯单元、主板复位单元、1553接口单元、主板时钟单元均与所述主板FPGA电信号连接,所述主板FPGA用于CAN通讯单元的调试控制,所述主板复位单元用于控制主板FPGA复位,所述主板FPGA用于1533接口单元的控制调试,所述主板时钟单元用于为所述主板FPGA提供脉冲时钟信号。

在本发明中,进一步的,所述主板FPGA电连接有AD采集单元,所述AD采集单元用于完成外部设备的电压信号采集。

在本发明中,进一步的,所述测试板连接有测试存储单元、测试串口单元、测试晶振单元、测试存储单元以及测试复位单元,所述测试存储单元、测试串口单元、测试晶振单元、测试存储单元以及测试复位单元均与所述测试FPGA连接,测试存储单元用于存储测试板中的数据,所述测试串口单元用于串口转换以用于通讯,所述测试晶振单元用于为测试板提供精确的脉冲信号,所述测试复位单元用于使测试板复位。

在本发明中,进一步的,所述主控板包括主板连接器,所述主控板连接器与所述主板FPGA连接,所述测试板包括测试板连接器,所述测试板连接器与所述测试板FPGA连接,所述主板连接器与所述测试板连接器电连接,用于满足主控板与测试板之间的信息传输。

在本发明中,进一步的,所述串口通讯单元包括UART串口电路和DSU串口电路,所述UART串口电路和DSU串口电路经过电平转换后连接有USB接口,所述USB接口用于与计算机进行通讯。

在本发明中,优选的,所述主板存储单元包括型号为AM29LV320DB的第一存储器、型号为K9WAG08U1B-PIB0的第二存储器、型号为IS61WV102416BLL的第三存储器,所述第一存储器、第二存储器、第三存储器用于不同的数据存储以满足主控板的配置需求。

一种AOCC系统软件和鉴定级原理样机用调试测试方法,基于上述平台,在进行测试时,上位机向CPU单元发送测试指令,CPU测试单元接收到测试指令,控制主板FPGA工作并向测试板FPGA发出指令以调用测试板中相应的测试模块进行测试。

在本发明中,优选的,所述测试模块包括激励产生模块、测试采集模块以及回环测试模块,所述激励产生模块激励产生模块根据测试需求产生主板FPGA所需的输入激励;所述测试采集模块会将主板FPGA输出的信号采集下来保存在寄存器中;所述回环测试模块将主板FPGA的输入、输出接口连接起来,由主板FPGA处理测试结果并保存在寄存器中。

与现有技术相比,本发明的有益效果是:

本发明的上位机测试软件主要功能是控制测试流程,向主控板中的CPU模块发送测试指令,实现相应测试功能。同时测试过程中,上位机会接收处理器返回的测试结果,并通过上位机界面显示。主控板集成了CPU单元、主板FPGA、串口通讯单元、主板存储单元、1553接口单元及其他IO ASIC测试相关电路,主板单元串口通讯单元连接测试产品和上位机,串口通讯单元采用USB的连接方式,与产品通讯方便。同时主控板可以满足多路通用输入输出测试、同步串口、异步串口以及各种通讯测试,调试功能全面,适用范围广,主控板可根据上位机指令完成相应测试功能,并将测试结果发回给上位机。测试板的主要器件为测试FPGA,测试板由主控板供电,在IO ASIC测试过程中,主控板会向测试板FPGA发出指令以调用相应测试模块完成对主板FPGA的测试。且主控板和测试板之间通过连接器进行信号传输,以实现系统的低功耗、稳定的数据传输。

因此,本平台测试功能齐全,集成度高,有效的减少了外设的占用空间,可以满足IO ASIC的不同功能的测试,可拓展性强,满足安全性、可靠性、小型化、可扩展的测试设备需求。

附图说明

附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。在附图中:

图1是本发明的系统整体结构框图;

图2是本发明的系统的信号传输关系框图;

图3是本发明的CPU单元的部分电路图I;

图4是本发明的CPU单元的部分电路图II;

图5是本发明的主板FPGA的部分电路图I;

图6是本发明的主板FPGA的部分电路图II;

图7是本发明的主板FPGA的部分电路图III;

图8是本发明的主板FPGA的部分电路图IV;

图9是本发明的1553接口单元的电路图;

图10是本发明的AD采集单元的电路图;

图11是本发明的CAN通讯单元的电路图;

图12是本发明的UART串口电路的电路图;

图13是本发明的DSU串口电路的电路图;

图14是本发明的第一存储器的电路图;

图15是本发明的第二存储器的电路图;

图16是本发明的第三存储器的电路图;

图17是本发明的主板复位单元和主板时钟单元的电路图;

图18是本发明的主板连接器的电路图;

图19是本发明的测试板连接器的电路图;

图20是本发明的测试FPGA的部分电路图;

图21是本发明的测试复位单元电路图;

图22是本发明的测试串口单元部分电路图;

1、CAN通讯单元;2、AD采集单元;3、主板复位单元;4、主板时钟单元;5、主板连接器;6、测试板连接器;7、测试串口单元;8、1553接口单元;9、主板存储单元;10、串口通讯单元;11、测试存储单元;12、测试晶振单元;13、测试复位单元。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

需要说明的是,当组件被称为“固定于”另一个组件,它可以直接在另一个组件上或者也可以存在居中的组件。当一个组件被认为是“连接”另一个组件,它可以是直接连接到另一个组件或者可能同时存在居中组件。当一个组件被认为是“设置于”另一个组件,它可以是直接设置在另一个组件上或者可能同时存在居中组件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

请同时参见图1、图2,本发明一较佳实施方式提供一种AOCC系统软件和鉴定级原理样机用调试平台,包括主控板和测试板,所述主控板与所述测试板通过连接器进行信号传输,所述主控板的输入端电信号连接有上位机,所述主控板用于解析上位机测试流程控制指令,控制测试板进行相应测试,并将测试结果发回给上位机;所述主控板包括CPU单元、主板FPGA,所述CPU单元与主板FPGA电信号连接,所述CPU单元用于解析上位机测试流程指令并控制主板FPGA指令的收发,所述测试板包括测试FPGA,所述CPU单元、主板FPGA均与所述测试FPGA电信号连接,所述测试FPGA用于处理主板FPGA发出的指令以调用相应测试模块,实现待测产品的测试采集信号的处理、校验、上传。

在本发明中,上位机上具有测试软件主要功能是控制测试流程,上位机向CPU单元发送测试实现相应测试功能。同时测试过程中,上位机会接收处理器返回的测试结果,并通过上位机界面显示,CPU测试单元接收到测试指令,控制主板FPGA工作并向测试板FPGA发出指令以调用测试板中相应的测试模块进行测试。

具体的,如图3、4所示,CPU单元采用型号为Soc2012的处理器U1A、U1B、U1C(附图中未全部给出),工作频率可达到80Mhz;并行总线可扩展充足存储器资源,具备多路GPIO资源;具备串口,可与上位机通信。如图5-8所示,主板FPGA嵌入IO ASIC iP核,具体选用型号为EP3C120F780的芯片U47A至U47J(附图中未全部给出),主板FPGA上设有多种功能串口,如通用输入输出接口,即80个GPIO,40个为通用输入接口,40个为通用输出接口;八通道频率采集模块设计,即频率采集IO接口;同步串口设计以及AC模块、异步串口等,以使资源满足系统的使用,可以满足与不同功能测试产品的信号收发以完成不同单元的功能测试,具有集成度较高,适用范围较广的特点。

在本发明中,进一步的,主控板还包括串口通讯单元10和主板存储单元9,串口通讯单元10、主板存储单元9均与所述CPU单元电信号连接,所述串口通讯单元10用于与上位机进行数据传输,所述主板存储单元9用于对主控板中的数据进行存储。

在本发明中,优选的,如图14、15、16所示,主板存储单元9包括型号为AM29LV320DB的第一存储器、型号为K9WAG08U1B-PIB0的第二存储器、型号为IS61WV102416BLL的第三存储器,所述第一存储器、第二存储器、第三存储器用于不同的数据存储以满足主控板的配置需求。

CPU单元外部挂载了5片第一存储器,均具有上电复位器件写保护功能。其中1片作为代码存储Flash,采用8位方式连接,1片作为外部存储,采用8位方式连接,另外3片组合为40位位宽模式与CPU单元连接,带EDAC功能,用于代替EEPROM,此型号比EEPROM容量更大,访问时间更短,可满足在地面测试系统当中的使用需求。

此外,CPU单元外部挂载了3片第三存储器,容量1MB,访问速度20nS,组合为40位位宽模式与CPU单元连接,带EDAC功能。1片第二存储器,存储NAND Flash。

具体的,如图12、13所示,串口通讯单元10包括UART串口电路和DSU串口电路,所述UART串口电路和DSU串口电路经过电平转换后连接有USB接口,所述USB接口用于与计算机进行通讯。UART串口电路包括转换芯片U49,转换芯片U49的4、5引脚连接USB接口J1,转换芯片U49的25、26引脚与处理器U1B的41、42脚对应连接,转换芯片U49用于将USB接口J1信号的电平转换为处理器所需要的电平。DSU串口电路包括转换芯片U51,转换芯片U51的4、5引脚连接USB接口J18,转换芯片U51的25、26引脚与处理器U1B的29、32脚对应连接,转换芯片U49以及转换芯片U51均为型号为CP2102的单片机。USB接口用于与计算机、测试产品进行通讯,例如在连接计算机时,本设备只需和电脑之间连接一根USB线缆,无需连接MOXA卡,因此连接方便快捷。

在本发明中,进一步的,主控板还包括CAN通讯单元1、主板复位单元3、1553接口单元8、主板时钟单元4,CAN通讯单元1、主板复位单元3、1553接口单元8、主板时钟单元4均与主板FPGA电信号连接,主板FPGA用于CAN通讯单元1的调试控制,主板复位单元3用于控制主板FPGA复位,主板FPGA用于1533接口单元的控制调试,主板时钟单元4用于为所述主板FPGA提供脉冲时钟信号。

具体的,如图11所示,CAN通讯单元1结构相同的两个,CAN通讯单元1包括电平转换芯片U52,电平转换芯片U52的1脚连接有发送开关P12,所述发送开关P12的输出端与芯片U47G的A25、A26端口连接,电平转换芯片U52的4脚连接有接收开关P13,用于实现数据的发送,所述接收开关P13的输出端与芯片U47G的B25、B26端口连接,用于实现数据的接收,电平转换芯片U52的6、7脚连接CAN接口,作为预留接口用于与待测产品的CAN接口进行通讯。本发明采用4路独立CAN收发链路,总线测试链路采用回环式设计,对待测产品测试时可以通过跳线进行测试通路选择。

具体的,如图17所示,主板复位单元3包括复位按键K5,所述复位按键K5的52脚与主板FPGA的芯片U47L的Y1端口连接,用于实现主板FPGA的复位。所述主板时钟单元4包括时钟控制芯片Y3,时钟控制芯片Y3经过电阻R134与芯片U47L的Y2端口连接,用于为主板FPGA提供准确的时钟信号,以使内部程序准确的运行。

如图9所示,1553接口单元8包括模拟收发器U48,模拟收发器U48连接有变压器T1、变压器T2,模拟收发器U48的收发接口连接至主板FPGA的芯片U47M的DATA端口,以实现数据传输,变压器T1、变压器T2均连接有连接器J16,通过连接器J16与飞机内部的控制器进行通讯。模拟收发器型号采用HI1573,变压器型号采用B3226,均符合标准1553B总线通信要求。本发明才用变压器耦合的1553B总线设计,其主要特点是分布处理、集中控制和实时响应。其可靠性机制包括防错功能、容错功能、错误的检测和定位、错误的隔离、错误的校正、系统监控及系统恢复功能。采用双冗余系统,有两个传输通道,保证了良好的容错性和故障隔离。

在本发明中,进一步的,所述主板FPGA电连接有AD采集单元2,所述AD采集单元2用于完成外部设备的电压信号采集。具体的,如图10所示,AD采集单元2包括AD控制芯片U2,采用型号为AD128S102的AD控制芯片U2作为主板FPGA的外部采集AD,AD控制芯片U2的1、14、15、16引脚与主板FPGA中的芯片U47C的AE9、AF7、AE8、AF8对应连接,以实现主板FPGA语AD采集单元2的通讯,完成不同通道的采集测试。为了减少测试电路复杂程度,因此在本发明中,在主控板上集成了一片AD128S102,测试时由外部设备检测各CS及CH引脚状态,同时由板上AD采集单元2完成电压信号采集,有效的减少了外设的占用空间,同时满足的待测产品的AD采集单元2的测试需求。

如图18、19、20所示,测试FPGA选用的型号为XC6SLX150FGG900单片机U1A至U1E,以满足主板FPGA资源的使用。其中,主板FPGA与测试FPGA通过连接器进行连接。具体的,主控板包括主板连接器5,所述主控板连接器与所述主板FPGA连接,所述测试板包括测试板连接器6,所述测试板连接器6与所述测试板FPGA连接,所述主板连接器5与所述测试板连接器6电连接,用于满足主控板与测试板之间的信息传输。主控板连接器和测试板连接器6选用的型号均为TFM-150-12-L-D-A,且均设有四个,每个主控板连接器和测试板连接器6接口对接,每个连接器有100Pin,可满足系统测试需求,连接器支持信号传输速率最大可达8Gbps。同时,通过主板FPGA与测试FPGA的连接器接口,主板FPGA可以为测试FPGA供电,主板FPGA可以与测试板FPGA进行通信。

在本发明中,进一步的,测试板连接有测试存储单元11、测试串口单元7、测试晶振单元12以及测试复位单元13,所述测试存储单元11、测试串口单元7、测试晶振单元12以及测试复位单元13均与所述测试FPGA连接,测试存储单元11用于存储测试板中的数据,所述测试串口单元7用于串口转换以用于通讯,所述测试晶振单元12用于为测试板提供精确的脉冲信号,所述测试复位单元13用于使测试板复位。

具体的,如图20所示,测试存储单元11包括存储器U10,存储器U10的型号W25Q64FVZPI,存储器U10的2脚与测试FPGA中的芯片U1B上的AH25端口连接,用于实现存储器与测试板FPGA中的数据传输。存储器U10主要用于对测试过程中的数据进行存储,以方便调用。如图22所示,测试串口单元7包括UART1接口,UART1接口连接有型号为MAX3223的串口芯片,串口芯片的13、15脚与测试FPGA连接,用于用于实现测试FPGA的串口通讯。测试晶振单元12包括测试晶振芯片U9,测试晶振芯片U9的3脚与测试FPGA的AH19端口连接,测试晶振芯片U9主要为测试FPGA提供一个基准的脉冲信号,以保证测试FPGA内部程序稳定的运行。如图21所示,测试复位单元13包括复位芯片U22,所述复位芯片U22的1、4脚与测试FPGA连接,用于对测试FPGA的复位功能进行测试。从此,通过在测试板上集成上述单元,不仅扩展了测试板的功能,同时使测试板能够稳定、精准的配合主板FPGA、CPU单元完成测试工作。

需要说明的是,本主控板通过程控电源进行供电,程控电源具备对整个测试系统供电的能力,供给+1.2V、+2.5V和+3.3V电源,其中+1.2V和+2.5V电源电流最大为4A,+3.3V电源最大电流为8A。

基于上述统平台,本发明提供一种AOCC系统软件和鉴定级原理样机用调试测试方法,在进行测试试验时,上位机向CPU单元发送测试指令,CPU测试单元接收到测试指令,控制主板FPGA工作并向测试板FPGA发出指令以调用测试板中相应的测试模块进行测试。

具体的,测试FPGA中的测试模块可分为三大类测试模块,包括激励产生模块、测试采集模块以及回环测试模块,所述激励产生模块激励产生模块根据测试需求产生主板FPGA所需的输入激励,如IO ASIC在测试频率采集模块、AC模块时会调用该类测试模块。

测试采集模块会将主板FPGA输出的信号采集下来保存在寄存器中,CPU单元可直接从测试FPGA的寄存器中读取测试结果。如AC模块输出、串口输出时会调用该类测试模块。

回环测试模块主要将主板FPGA的输入、输出接口连接起来,由主板FPGA处理测试结果并保存在寄存器中,CPU单元可从主板FPGA的寄存器中读取测试结果。如进行GPIO测试、同步串口测试时会调用这类测试模块。

在本实施方式中,工作原理:

将待测产品以及上位机通过串口通讯单元10与本系统进行通讯,并通过程控电源来为本系统供电,在对待测产品进行测试时,通过上位机上的测试软件向本系统CPU单元发送测试指令,CPU测试单元接收到测试指令并解析转换,控制主板FPGA工作并向测试板FPGA发出指令以调用测试板中相应的测试模块进行测试,例如,对待测产品的频率采集模块、AC模块等输入模块进行测试时,主板FPGA会向测试模块发出控制指令调用激励产生模块,激励产生模块产生与测试项目所需要的激励对完成该单元的测试,测试完成后,测试FPGA将测试结果发送到CPU单元,由CPU单元返回至上位机进行显示。

上述说明是针对本发明较佳可行实施例的详细说明,但实施例并非用以限定本发明的专利申请范围,凡本发明所提示的技术精神下所完成的同等变化或修饰变更,均应属于本发明所涵盖专利范围。

- 一种AOCC系统软件和鉴定级原理样机用调试平台及测试方法

- 一种调度自动化主站系统软件测试方法及其平台