半导体装置及其形成方法

文献发布时间:2023-06-19 11:54:11

技术领域

本公开涉及半导体装置,特别是涉及一种包含开孔(scallop)的半导体装置。

背景技术

半导体装置使用于各种电子应用,例如,举例而言,个人电脑、手机、数码相机、及其他电子设备。半导体装置的制造通常是通过依序沉积绝缘或介电层、导电层、及半导体层的材料于半导体基板上,且利用光刻图案化各种材料层以形成电路组件及元件于其上方。

半导体产业持续通过不断的缩小最小部件尺寸,允许更多的组件集成至给定的区域,借此改善各种电子组件(例如,晶体管、二极管、电阻器、电容器等)的集成密度。然而,随着最小部件尺寸缩小,发生了额外的需要解决的问题。

发明内容

一种半导体装置,包括:第一基板;以及贯孔(through via),延伸穿过第一基板,第一基板包括:多个第一开孔,在第一基板的第一区域中邻近贯孔,第一开孔的每个开孔具有第一深度;以及多个第二开孔,在第一基板的第二区域中邻近贯孔,第二开孔的每个开孔具有第二深度,其中第二深度大于第一深度

一种半导体装置的形成方法,包括:用第一图案化制程蚀刻基板以形成开口(opening)于基板中,开口从基板的第一表面延伸第一深度,其中第一图案化制程包括多个第一重复步骤(iteration),每个第一重复步骤包括第一沉积及第一蚀刻;以及用第二图案化制程蚀刻基板以将基板中的开口从第一深度延伸至第二深度,其中第二图案化制程包括多个第二重复步骤,每个第二重复步骤包括第二沉积、第二蚀刻、及第三蚀刻,第三蚀刻具有与第一蚀刻及第二蚀刻不同的制程参数。

一种半导体装置的形成方法,包括:蚀刻基板以形成第一开口,第一开口包括第一区域及第二区域,其中第一区域从基板的表面延伸至基板中的第一深度,其中第二区域从基板中的第一深度延伸至第二深度,其中蚀刻包括:进行第一图案化制程以形成第一开口于第一区域中,第一图案化制程包括多个第一图案化重复步骤;以及进行第二图案化制程以形成第一开口于第二区域中,第二图案化制程包括多个第二图案化重复步骤,其中每个第二图案化重复步骤的持续时间大于每个第一图案化重复步骤的持续时间;以及沿着第一开口的多个侧壁沉积金属层,其中金属层在第一区域中的导电率小于金属层在第二区域中的导电率。

附图说明

以下将配合附图详述本公开实施例。应注意的是,依据在业界的标准做法,各种特征并未按照比例绘制且仅用以说明例示。事实上,可任意地放大或缩小元件的尺寸,以清楚地表现出本公开实施例的特征。

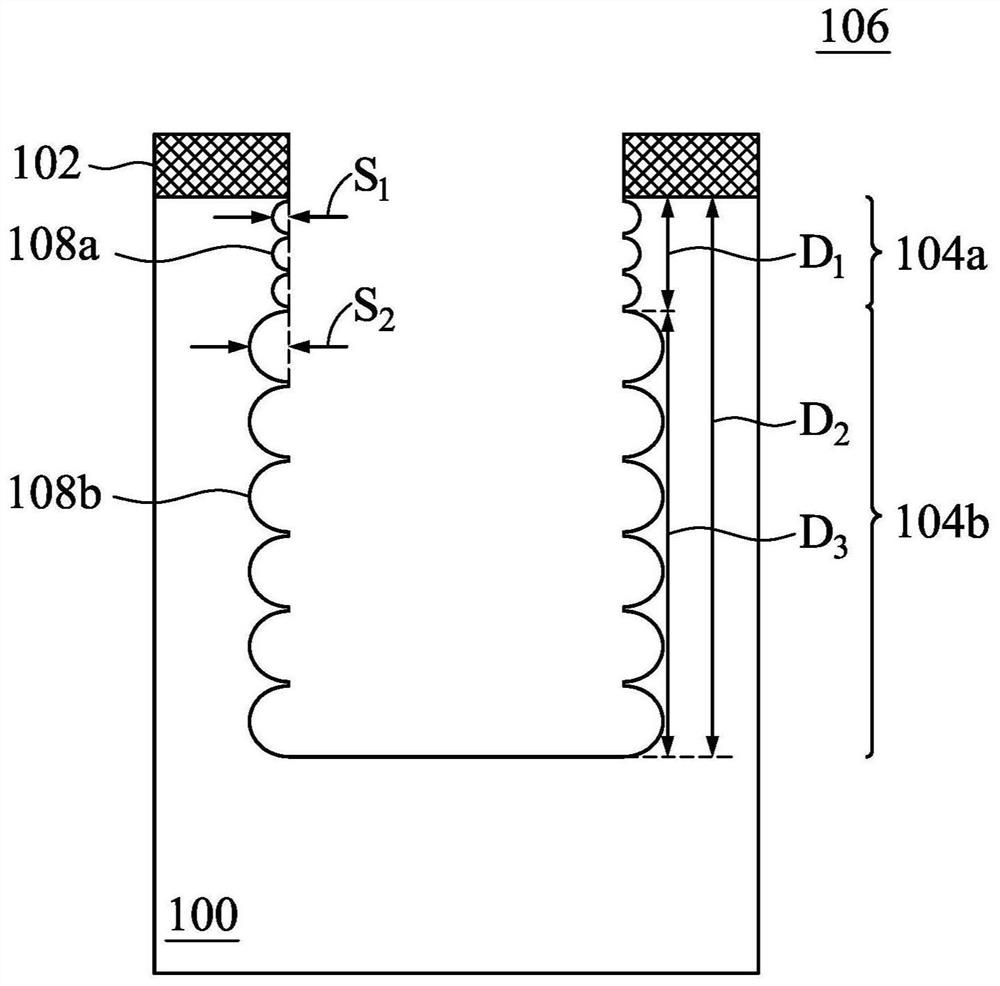

图1、图2A、图2B、图3A、图3B、图4、图5、图6、图7、图8A、图8B、及图9是根据一些实施例的半导体装置的制造中的中间阶段的剖面图。

其中,附图标记说明如下:

100:第一半导体基板

102:图案化光阻

104:第一开口

104a:第一区域

104b:第二区域

106,112,134:区域

108a:第一开孔

108b:第二开孔

110:第一金属层

114:牺牲材料

116:第一钝化膜

118:第二钝化膜

120:载体基板

122:第二半导体基板

124:第三钝化膜

126:第四钝化膜

128:空腔

130:第二开口

132:第二金属层

136:划线

150:半导体装置

D

S

T

W

W

具体实施方式

以下公开提供了许多的实施例或范例,用于实施所提供的标的物的不同元件。各元件和其配置的具体范例描述如下,以简化本公开实施例的说明。当然,这些仅仅是范例,并非用以限定本公开实施例。举例而言,叙述中若提及第一元件形成在第二元件之上,可能包含第一和第二元件直接接触的实施例,也可能包含额外的元件形成在第一和第二元件之间,使得它们不直接接触的实施例。此外,本公开实施例可能在各种范例中重复参考数值以及/或字母。如此重复是为了简明和清楚的目的,而非用以表示所讨论的不同实施例及/或配置之间的关系。

再者,其中可能用到与空间相对用词,例如“在……之下”、“下方”、“较低的”、“上方”、“较高的”等类似用词,是为了便于描述图式中一个(些)部件或特征与另一个(些)部件或特征之间的关系。空间相对用词用以包括使用中或操作中的装置的不同方位,以及附图中所描述的方位。当装置被转向不同方位时(旋转90度或其他方位),其中所使用的空间相对形容词也将依转向后的方位来解释。

各种实施例提供了用于半导体装置的改善的贯孔及其形成方法。贯孔可以用第一图案化制程且接着用具有与第一图案化制程不同的制程条件的第二图案化制程来形成。第一图案化制程蚀刻贯孔的第一区域且在贯孔的侧壁中形成第一开孔。第二图案化制程蚀刻贯孔的第二区域且在贯孔的侧壁中形成第二开孔,第二开孔具有与第一开孔的深度不同的深度。接着沉积金属层于贯孔中。通过利用不同的图案化制程,其中不同的图案化制程产生不同深度的开孔于贯孔的第一区域及第二区域中,可以在第一区域及第二区域中控制金属层的导电率而不需要额外的沉积及蚀刻步骤。金属层及贯孔可以用于在微机电系统(microelectromechanical system,MEMS)装置、发光二极管(light emitting diode,LED)装置、电子束装置(例如,电子束写入器(electron-beam writer)控制装置)等装置中提供屏蔽(shielding)。

图1根据一些实施例示出了第一半导体基板100,具有图案化光阻102形成于其顶表面。第一半导体基板100可以包含块体(bulk)半导体基板、绝缘体上半导体(semiconductor-on-insulator,SOI)基板、多层半导体基板等。第一半导体基板100的材料可以是:硅(silicon)、锗(germanium)、包含硅锗(silicon germanium)、碳化硅(siliconcarbide)、砷化镓(gallium arsenic)、磷化镓(gallium phosphide)、磷化铟(indiumphosphide)、砷化铟(indium arsenide)、及/或锑化铟(indium antimonide)的化合物半导体;包含SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP、及/或GaInAsP的合金半导体;或前述的组合。也可以使用其他基板,例如多层或渐变(gradient)基板。第一半导体基板100可以是掺杂的或未掺杂的。可以将例如晶体管、电容器、电阻器、二极管等的装置(未个别示出)形成于第一半导体基板100的主动面(例如,朝上的表面)中及/或主动面上。

图案化光阻102形成于第一半导体基板100的顶表面上。光阻材料的膜层可以利用旋转涂布(spin coating)等制程沉积于第一半导体基板100上。接着可以通过将光阻材料暴露于图案化的能量源(例如,图案化的光),且接下来将光阻材料暴露于显影剂以移除暴露或未暴露的部分的光阻材料,形成图案化光阻102。通过显影剂移除的部分的光阻材料可以对应至接下来形成于第一半导体基板100中的开口(例如,以下关于图2A及图2B所讨论的第一开口104)。

图2A及图2B根据一些实施例,示出了利用图案化光阻102作为遮罩在第一半导体基板100中形成第一开口104。图2B示出了图2A的区域106的详细视图。第一图案化制程可以用于蚀刻第一开口104的第一区域104a,上述第一区域104a在其侧壁中具有第一开孔108a。在第一图案化制程后的第二图案化制程可以用于蚀刻第一开口104的第二区域104b,上述第二区域104b在其侧壁中具有第二开孔108b。在各种实施例中,第一图案化制程及第二图案化制程可以是波希法(Bosch process)、其他深度反应离子蚀刻(deep reactive ionetching,DRIE)制程等。第一开孔108a及第二开孔108b可以用于控制第一金属层(例如,以下关于图3A及图3B所讨论的第一金属层110)的导电率,上述第一金属层沉积于第一半导体基板100上及第一开口104中。

用于形成第一开口104的第一区域104a的第一图案化制程包含第一沉积及第一蚀刻。每个第一沉积后接着一个第一蚀刻,且这个模式会重复多个重复步骤。第一沉积及第一蚀刻可以两者都是基于等离子体的制程,且在一些实施例中,可以两者都使用氟基(fluorine-based)等离子体。第一沉积是用于沉积钝化膜于图案化光阻102上以及由图案化光阻102露出的部分的第一半导体基板100上。接着第一蚀刻是用于蚀刻穿过在露出第一半导体基板100的图案化光阻中的开口的底部的部分的钝化膜,且用于蚀刻第一半导体基板100。

第一蚀刻可以大部分是等向性的,但可以包含一些在几乎垂直的方向上附着的离子。这会造成第一蚀刻穿透设置于开口的底部的部分的钝化膜而不会穿透钝化膜的侧壁,造成第一图案化制程将第一开口104的第一区域104a图案化为具有实质上垂直的侧壁。第一蚀刻的等向性质造成第一开孔108a形成于第一开口104在第一区域104a中的侧壁中。用于形成第一开口104的第一区域104a的第一图案化制程的重复步骤的数目可以是从50到150个重复步骤,例如84个重复步骤,然而,也可以使用蚀刻第一开口104的第一区域104a至理想的深度所需的任何其他数目的重复步骤。

第一图案化制程的每个重复步骤会将第一开口104延伸至第一半导体基板100中,且围绕第一开口104的圆周(circumference)以形成其中一个第一开孔108a。每个第一开孔108a可以具有从约40nm至约50nm的深度S

第一沉积可以在约5mTorr到约200mTorr的压力下进行,例如约40mTorr。第一沉积可以进行从约0.5秒到约5秒的时间,例如约0.9秒。可以将从约1000W到约3000W的范围内的等离子体功率用于第一沉积,例如约2500W。

第一沉积可以使用主要沉积气体及次要沉积气体,各自包括含氟(fluorine-containing)气体,例如二氟甲烷(difluoromethane,CH

第一蚀刻是在从约5mTorr到约200mTorr的压力下进行,例如约23mTorr,进行从约0.5秒到约5秒的时间,例如约1.5秒,主要等离子体功率在从约1000W到约3000W的范围内,例如约2500W,且次要等离子体功率在从约50W到约1000W的范围内,例如约400W。第一蚀刻可以利用基板偏压来进行,基板偏压从第一图案化制程的第一重复步骤时的第一基板偏压变化(ramp)到第一图案化制程的最后重复步骤时的第二基板偏压。第一基板偏压可以是从约5W到约1000W,例如约150W,且第二基板偏压可以是从约5W到约1000W,例如约270W。

第一蚀刻可以使用主要蚀刻气体及次要蚀刻气体,各自包括含氟气体,例如二氟甲烷(CH

用于形成第一开口104的第二区域104b的第二图案化制程包含第二沉积、第二蚀刻、及第三蚀刻。每个第二沉积后接着其中一个第二蚀刻,之后接着其中一个第三蚀刻,且这个模式会重复多个重复步骤。第二沉积、第二蚀刻、及第三蚀刻可以是基于等离子体的制程,且在一些实施例中,可以使用氟基等离子体。第二沉积是用于沉积钝化膜于图案化光阻102上以及在第一开口104中露出的部分的第一半导体基板100上。接着第二蚀刻及第三蚀刻是用于蚀刻穿过在第一开口104的底部的部分的钝化膜,且用于蚀刻第一半导体基板100。

第二蚀刻及第三蚀刻可以大部分是等向性的,但可以包含一些在几乎垂直的方向上附着的离子。这会造成第二蚀刻及第三蚀刻穿透设置于第一开口104的底部的部分的钝化膜而不会穿透钝化膜的侧壁,造成第二图案化制程将第一开口104的第二区域104b图案化为具有实质上垂直的侧壁。第二蚀刻及第三蚀刻的等向性质造成第二开孔108b形成于第一开口104在第二区域104b中的侧壁中。第二蚀刻及第三蚀刻可以各自具有相似的制程参数,且可以进行与第一蚀刻相似的时间,且因此第二蚀刻与第三蚀刻的组合可以在第二区域104b中产生比第一蚀刻在第一区域104a中产生的第一开孔108a更大的第二开孔108b。第二图案化制程的每个重复步骤也可以比第一图案化制程的每个重复步骤进行更长的时间。用于形成第一开口104的第二区域104b的第二图案化制程的重复步骤的数目可以是从50到500个重复步骤,例如105个重复步骤,然而,可以使用蚀刻第一开口104的第二区域104b至理想的深度所需的任何其他数目的重复步骤。

第二图案化制程的每个重复步骤会将第一开口104延伸至第一半导体基板100中,且围绕第一开口104的圆周以形成其中一个第二开孔108b。每个第二开孔108b可以具有从约150nm到约180nm的深度S

第二沉积可以是在从约5mTorr到约200mTorr的压力下进行,例如约40mTorr,而主要等离子体功率在从约1000W到约3000W的范围内,例如约2500W,且次要等离子体功率在从约50W到约1000W的范围内,例如约400W。第二沉积可以用一个时段来进行,上述时段从第二图案化制程的第一重复步骤时的第一时段变化到最后重复步骤时的第二时段。第一时段可以是从约0.5秒到约5秒,例如约1.0秒,且第二时段可以是从约0.5秒到约5秒,例如约2.0秒。

第二沉积可以使用主要沉积气体及次要沉积气体,其各自包括含氟气体,例如二氟甲烷(CH

第二蚀刻可以在从约5mTorr到约200mTorr的压力下进行,例如约30mTorr,主要等离子体功率在从约1000W到约3000W的范围内,例如约2500W,且次要等离子体功率在从约50W到约1000W的范围内,例如约400W。第二蚀刻可以使用从约5W到约1000W的基板偏压来进行,例如约80W。第二蚀刻可以进行一个时段,上述时段从第二图案化制程的第一重复步骤时的第一时段变化到最后重复步骤时的第二时段。第一时段可以是从约0.5秒到约5秒,例如约0.8秒,且第二时段可以是从约0.5秒到约5秒,例如约2.9秒。

第二蚀刻可以使用主要蚀刻气体及次要蚀刻气体,其各自包括含氟气体,例如二氟甲烷(CH

第三蚀刻可以在从约5mTorr到约200mTorr的压力下进行,例如约40mTorr,主要等离子体功率在从约1000W到约3000W的范围内,例如约2500W,且次要等离子体功率在从约50W到约1000W的范围内,例如约500W。第三蚀刻可以使用从约50W到约1000W的基板偏压来进行,例如约500W。第三蚀刻可以进行一个时段,上述时段从第二图案化制程的第一重复步骤时的第一时段变化到最后重复步骤时的第二时段。第一时段可以是从约0.5秒到约5秒,例如约0.8秒,且第二时段可以是从约0.5秒到约5秒,例如约3.6秒。

第二蚀刻可以使用主要蚀刻气体及次要蚀刻气体,其各自包括含氟气体,例如二氟甲烷(CH

图3A及图3B根据一些实施例示出了图案化光阻102的移除以及第一金属层110在第一半导体基板100上及第一开口104中的沉积。图3B示出了图3A的区域112的详细视图。在第一开口104形成于第一半导体基板100后,可以利用适合的光阻剥除(stripping)技术移除图案化光阻102,例如化学溶剂清洗(chemical solvent cleaning)、等离子体灰化(plasma ashing)、干剥除(dry stripping)及/或类似技术。

第一金属层110可以通过溅镀沉积、物理气相沉积(physical vapor deposition,PVD)、化学气相沉积(chemical vapor deposition,CVD)等来沉积。第一金属层110可以包含导电材料,例如金属。第一金属层110可以包含金属,例如铜(copper)、钛(titanium)、钨(tungsten)、铝(aluminum)、金(gold)、前述的组合等。在一个特定的实施例中,第一金属层110可以包括钛层以及沉积于钛层上的金层。钛层可以具有从约10nm到约500nm的厚度,例如约100nm,且金层可以具有从约10nm到约1000nm的厚度,例如约400nm。第一金属层110可以具有从约20nm到约1500nm的厚度,例如约500nm。

在一些实施例中,第一金属层110可以具有大于第一开孔108a的深度S

第一半导体基板100中所包含的装置可以被设置于一部分的第一半导体基板100直到深度D

在其他实施例中,第一金属层110可以具有大于第一开孔108a的深度S

图4根据一些实施例示出了牺牲材料114在第一开口104中的沉积以及载体基板120与第一半导体基板100的接合。牺牲材料114可以包括氧化硅(silicon oxide)、氮氧化硅(silicon oxynitride)、SiCON、SiC、SiOC、及/或氮化硅(silicon nitride),且可以利用CVD、原子层沉积(atomic layer deposition,ALD)、PVD、旋转涂布(spin-on coating)等、或前述的组合来沉积。可以将牺牲材料114沉积为使牺牲材料114填满第一开口104且延伸于第一半导体基板100上。牺牲材料114可以接着被平坦化,使得牺牲材料114的顶表面与第一金属层110的顶表面等高。可以利用例如化学机械抛光(chemical mechanicalpolishing,CMP)的制程来平坦化牺牲材料114。

接着将第一钝化膜116形成于第一金属层110及牺牲材料114上。第一钝化膜116可以由热氧化(thermal oxidation)、CVD、PVD等来形成。第一钝化膜116可以包括任何适合的介电材料,上述介电材料能够在后续的制程步骤中直接接合至另一个介电层。举例而言,第一钝化膜116可以包括氧化硅(例如,SiO

载体基板120可以包含块体半导体基板、绝缘体上半导体(SOI)基板、多层半导体基板等。载体基板120的半导体材料可以是硅、锗、包含硅锗、碳化硅、砷化镓、磷化镓、磷化铟、砷化铟、及/或锑化铟的化合物半导体;包含SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP、及/或GaInAsP的合金半导体;或前述的组合。也可以使用其他基板,例如多层或渐变基板。载体基板120可以是掺杂的或未掺杂的。

第二钝化膜118设置于载体基板120上。第二钝化膜118可以包括任何适合的介电材料,上述介电材料能够在后续的制程步骤中直接接合至另一个介电层。举例而言,第二钝化膜118可以包括氧化硅(例如,SiO

第一半导体基板100的第一钝化膜116可以实体接触且接合至载体基板120的第二钝化膜118。在接合之前,可以对第一钝化膜116或第二钝化膜118的至少一个进行表面处理。上述表面处理可以是等离子体处理。上述等离子体处理可以是在真空环境中进行。用于产生等离子体的制程气体可以是含氢(hydrogen-containing)气体,其包括含有氢(hydrogen,H

在清洗制程后,第一半导体基板100及载体基板120彼此对压。可以施加预接合(pre-bonding)按压力以将第一半导体基板100及载体基板120彼此对压。可以在一些例示性的实施例中将小于约5N的按压力各施加于第一半导体基板100及载体基板120,尽管也可以使用更大或更小的力。预接合可以是在室温下进行(例如,约21℃及约25℃之间),尽管可以使用更高的温度。举例而言,接合时间可以比约1分钟短。

在预接合后,第一钝化膜116及第二钝化膜118接合至彼此。然而,上述接合可以在后续的退火步骤中被强化。举例而言,可以在约170℃的温度下对第一半导体基板100及载体基板120进行约1小时的可选的退火。当温度上升,在第一钝化膜116及第二钝化膜118中的-OH键断裂以形成较强的Si-O-Si键,且第一半导体基板100及载体基板120因此透过融合键结接合至彼此。

图5根据一些实施例,示出了图4中所示出的结构的翻转(flipping)以及第一半导体基板100的薄化(thinning)。在第一半导体基板100与载体基板120接合后,可以对第一半导体基板100施加薄化制程。薄化制程可以包含在第一半导体基板100的表面上进行研磨或CMP制程、回蚀(etch back)制程、或其他可接受的制程。第一半导体基板100可以被薄化至露出牺牲材料114。在薄化制程后,第一半导体基板100可以具有从约10μm到约100μm的厚度T1,例如约50μm。

图6根据一些实施例,示出了第二半导体基板122接合至第一半导体基板100。第三钝化膜124形成于第一半导体基板100及牺牲材料114上。第三钝化膜124可以是通过热氧化、CVD、PVD、等所形成。第三钝化膜124可以包括任何适合的介电材料,上述介电材料能够在后续的制程步骤中直接接合至另一个介电层。举例而言,第三钝化膜124可以包括氧化硅(例如,SiO

第二半导体基板122可以包含块体半导体基板,、绝缘体上半导体(SOI)基板、多层半导体基板等。第二半导体基板122的半导体材料可以是硅、锗、包含硅锗、碳化硅、砷化镓、磷化镓、磷化铟、砷化铟、及/或锑化铟的化合物半导体;包含SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP、及/或GaInAsP的合金半导体;或前述的组合。也可以使用其他基板,例如多层或渐变基板。第二半导体基板122可以是掺杂的或未掺杂的。

第四钝化膜126设置于第二半导体基板122上。第四钝化膜126可以包括任何适合的介电材料,上述介电材料能够在后续的制程步骤中直接接合至另一个介电层。举例而言,第四钝化膜126可以包括氧化硅(例如,SiO

第一半导体基板100的第三钝化膜124可以与第二半导体基板122的第四钝化膜126实体接触且接合。可以利用与以上关于图4所述的接合制程相同的制程将第三钝化膜124接合至第四钝化膜126。举例而言,在接合之前,可以对至少第三钝化膜124或第四钝化膜126的其中一个进行表面处理,上述表面处理可以是等离子体处理。在表面处理之后,可以将清洗制程(例如,用去离子水淋洗)施加于第三钝化膜124及/或第四钝化膜126。在清洗制程后,将第一半导体基板100及第二半导体基板122彼此对压以造成第三钝化膜124与第四钝化膜126之间的预接合。最后,第三钝化膜124与第四钝化膜126之间的接合可以通过后续的退火步骤强化。

图7根据一些实施例,示出了空腔(cavity)128及第二开口130的形成。空腔128可以通过蚀刻第二半导体基板122来形成。第二半导体基板122可以是利用非等向性蚀刻制程来蚀刻,例如反应离子蚀刻(reactive ion etching,RIE)、中性束蚀刻(neutral beametching,NBE)等。在一些实施例中,第四钝化膜126可以作为用于在第二半导体基板122中蚀刻空腔128的蚀刻停止层(etch stop layer)。如图7所示出,空腔128可以完全地延伸穿过第二半导体基板122。如图7所进一步示出,空腔128可以从远离(distal)第一半导体基板100的第一宽度W

在将空腔128蚀刻穿过第二半导体基板122后,可以蚀刻第四钝化膜126及第三钝化膜124以延伸空腔128至第一半导体基板100,且可以蚀刻牺牲材料114、第二钝化膜118、及第一钝化膜116以形成第二开口130。在一些实施例中,第四钝化膜126、第三钝化膜124、牺牲材料114、第二钝化膜118、及第一钝化膜116可以由相同的材料形成。举例而言,第四钝化膜126、第三钝化膜124、牺牲材料114、第二钝化膜118、及第一钝化膜116可以由氧化硅形成。在进一步的实施例中,可以将不同的材料用于第四钝化膜126、第三钝化膜124、牺牲材料114、第二钝化膜118、及第一钝化膜116的任何一个。可以利用干蚀刻制程或湿蚀刻制程来蚀刻第四钝化膜126、第三钝化膜124、牺牲材料114、第二钝化膜118、及第一钝化膜116,且可以在一个单一的蚀刻制程或多个蚀刻制程中蚀刻。如图7所示出,在第二半导体基板122、第四钝化膜126、第三钝化膜124、牺牲材料114、第二钝化膜118、及第一钝化膜116的蚀刻后,第二半导体基板122、第四钝化膜126、及第三钝化膜124的侧表面以及第一半导体基板100的顶表面在空腔128中露出。此外,第一半导体基板100、第一金属层110、第二钝化膜118、及第一钝化膜116的侧表面以及第一金属层110及载体基板120的顶表面在第二开口130中露出。

图8A及图8B根据一些实施例,示出了第二金属层132在第二半导体基板122上、在空腔128中、以及在第二开口130中的形成。图8B示出了图8A的区域134的详细视图。第二金属层132可以通过溅镀沉积、PVD、CVD等来沉积。第二金属层132可以包含导电材料,例如金属。第二金属层132可以包含例如铜、钛、钨、铝、金、前述的组合等金属。在一个特定的实施例中,第二金属层132可以包括钛层以及设置于钛层上的金层。钛层可以具有从约10nm到约500nm的厚度,例如约100nm,且金层可以具有从约10nm到约1000nm的厚度,例如约200nm。第二金属层132可以具有从约20nm到约1500nm的厚度,例如约300nm。

在一些实施例中,第二金属层132及第一金属层110可以具有大于第一开孔108a的深度S

第二金属层132及第一金属层110可以耦合至第一半导体基板100及/或第二半导体基板122,且可以被包含以为第一半导体基板100及/或第二半导体基板122中所包含的装置提供遮蔽。在一些实施例中,第二金属层132及第一金属层110提供接地电路至第一半导体基板100及/或第二半导体基板122,且提供静电放电(electrostatic discharge,ESD)保护。

在其他实施例中,第二金属层132及第一金属层可以具有大于第一开孔108a的深度S

图9示出了在载体基板120、第一钝化摸116、及第二钝化膜118的移除以及部分的第二金属层132的平坦化后的半导体装置150的形成。制程,例如研磨或CMP制程、回蚀制程、或其他可接受的制程,可以用于移除载体基板120、第一钝化膜116、及第二钝化膜118,且用于平坦化第二金属层132。

可以通过沿着划线(scribe lines)136进行单粒化(singulation)制程以进一步将半导体装置150从其他半导体装置单粒化。单粒化可以通过沿着划线136锯切(sawing)、激光钻孔(laser drilling)等来进行。单粒化制程会使半导体装置150从邻近的半导体装置分离。

第一金属层110及/或第二金属层132可以用于在半导体装置150中提供遮蔽。利用第一图案化制程及第二图案化制程在第一开口104中分别形成在第一区域104a及第二区域104b有不同的深度的第一开孔108a及第二开孔108b。这会在第一区域104a及第二区域104b中提供第一金属层110及/或第二金属层132的导电率的控制,而不需要额外的沉积及蚀刻步骤,且减少形成半导体装置150的成本。

根据一个实施例,一种半导体装置包含:第一基板;以及贯孔,延伸穿过第一基板,第一基板包含多个第一开孔,在第一基板的第一区域中邻近贯孔,多个第一开孔的每个开孔具有第一深度;以及多个第二开孔,在第一基板的第二区域中邻近贯孔,多个第二开孔的每个开孔具有第二深度,第二深度大于第一深度。在一个实施例中,第一深度是从30nm到50nm,且第二深度是从150nm到250nm。在一个实施例中,第一深度对第二深度的比例是从0.2到0.6。在一个实施例中,贯孔包含邻近第一基板的金属层,金属层的厚度大于第一深度且小于第二深度。在一个实施例中,金属层在第一区域中是连续的且在第二区域中是不连续的。在一个实施例中,第一基板包含第一表面及与第一表面相对的第二表面,第一区域从第一表面延伸至第一表面与第二表面之间的点,且第二区域从点延伸至第二表面。在一个实施例中,半导体装置更包含接合至第一基板的第二基板,空腔延伸穿过第二基板,空腔具有锥形侧壁。在一个实施例中,半导体装置更包含介于第一基板与第二基板之间的第一钝化膜及第二钝化膜,第二基板是通过第一钝化膜与第二钝化膜之间的介电质对介电质(dielectric-to-dielectric)接合来接合至第一基板。

根据另一个实施例,一种半导体装置的形成方法,包含:用第一图案化制程蚀刻基板以形成开口于基板中,开口从基板的第一表面延伸第一深度,第一图案化制程包含多个第一重复步骤,每个第一重复步骤包含第一沉积及第一蚀刻;以及用第二图案化制程蚀刻基板以将基板中的开口从第一深度延伸至第二深度,第二图案化制程包含多个第二重复步骤,每个第二重复步骤包含第二沉积、第二蚀刻、及第三蚀刻,第三蚀刻具有与第一蚀刻及第二蚀刻不同的制程参数。在一个实施例中,第一图案化制程包含从50到150个第一重复步骤,且第二图案化制程包含从50到500个第二重复步骤。在一个实施例中,用第一图案化制程蚀刻基板的步骤形成多个第一开孔于开口的多个侧壁中,多个第一开孔具有从约40nm到约90nm的深度。在一个实施例中,用第二图案化制程蚀刻基板的步骤形成多个第二开孔于开口的多个侧壁中,多个第二开孔具有从约100nm到约300nm的深度。在一个实施例中,第一深度是从4μm到17μm,且第二深度是从10μm到100μm。在一个实施例中,用于第一沉积及第二沉积的处理气体包含八氟环丁烷(C

根据又另一个实施例,一种半导体装置的形成方法,包含:蚀刻基板以形成第一开口,第一开口包含第一区域及第二区域,第一区域从基板的表面延伸至基板中的第一深度,第二区域从基板中的第一深度延伸至第二深度,蚀刻包含:进行第一图案化制程以形成第一开口于第一区域中,第一图案化制程包含多个第一图案化重复步骤;以及进行第二图案化制程以形成第一开口于第二区域中,第二图案化制程包含多个第二图案化重复步骤,其中每个第二图案化重复步骤的持续时间大于每个第一图案化重复步骤的持续时间;以及沿着第一开口的多个侧壁沉积金属层,金属层在第一区域中的导电率小于金属层在第二区域中的导电率。在一个实施例中,第一开口在第一区域中的多个侧壁包含具有第一深度的多个开孔,第一开口在第二区域中的多个侧壁具有第二深度的多个开孔,且金属层是沉积至介于第一深度及第二深度之间的厚度。在一个实施例中,第二深度大于第一深度,且沉积金属层使得金属层在第一区域中是连续的且在第二区域中是不连续的。在一个实施例中,金属层是通过溅镀沉积来沉积。在一个实施例中,第一开口在第一区域中的多个侧壁包含具有第一深度的多个开孔,第一开口在第二区域中的多个侧壁具有第二深度的多个开孔,且金属层是沉积至大于第一深度及第二深度各自的厚度。在一个实施例中,第二深度大于第一深度,且金属层在第一区域及第二区域两者中是连续的。

以上概述数个实施例的部件,以便在本公开所属技术领域中具有通常知识者可更易理解本公开实施例的观点。在本公开所属技术领域中具有通常知识者应理解,他们能以本公开实施例为基础,设计或修改其他制程和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本公开所属技术领域中具有通常知识者也应理解到,此类等效的制程和结构并无悖离本公开的精神与范围,且他们能在不违背后附的权利要求的精神和范围的下,做各式各样的改变、取代和替换。

- 芯片封装及其形成方法、半导体器件及其形成方法、半导体装置及其形成方法、三相系统

- 半导体膜的形成方法、半导体器件的形成方法和半导体器件