半导体存储器件、包括其的存储器系统和控制其的方法

文献发布时间:2023-06-19 19:00:17

相关申请的交叉引用

本申请要求于2021年9月13日在韩国知识产权局提交的韩国专利申请No.10-2021-0121736的优先权,所述韩国专利申请的公开内容通过引用全部包含于此。

技术领域

示例实施例总体上涉及半导体集成电路,更具体地,涉及半导体存储器件、包括半导体存储器件的存储器系统以及控制半导体存储器件的方法。

背景技术

当半导体存储器件的工作温度过度升高时,可能发生物理损坏并且损坏的半导体存储器件变得无法使用。通常,温度调节(temperature throttling)可以作为系统级被执行以调整半导体存储器件的工作温度。然而,温度调节基于设置在半导体存储器件外部的温度传感器(例如,TSOD(DIMM(双列直插式存储器模块)上的温度传感器)),这不能反映半导体存储器件的准确温度。此外,如果将半导体存储器件的内部温度提供给存储器控制器以进行温度调节,那么存储器系统的配置会变得复杂并且性能会降低。

发明内容

一些示例实施例提供一种半导体存储器件、存储器系统以及相关联的方法,其能够有效地防止由于高温导致的半导体存储器件的物理损坏。

根据示例实施例的一方面,一种半导体存储器件包括:被配置为与存储器控制器通信的多个输入-输出引脚、命令控制逻辑、温度测量电路和操作限制控制器。所述命令控制逻辑基于通过所述多个输入-输出引脚之中的控制引脚从所述存储器控制器传送的命令信号和控制信号,来控制所述半导体存储器件的操作。所述温度测量电路测量所述半导体存储器件的工作温度,以生成与所述工作温度对应的温度码。当基于所述温度码确定所述工作温度超过风险温度时,所述操作限制控制器控制所述半导体存储器件的内部操作,而不管从所述存储器控制器传送的所述命令信号和所述控制信号如何,从而降低所述半导体存储器件的功耗。

根据示例实施例的一方面,一种存储器系统包括存储器控制器以及半导体存储器件。所述半导体存储器件包括:多个输入-输出引脚,所述多个输入-输出引脚被配置为与所述存储器控制器通信;命令控制逻辑,所述命令控制逻辑被配置为:基于通过所述多个输入-输出引脚之中的控制引脚从所述存储器控制器传送的命令信号和控制信号,来控制所述半导体存储器件的操作;温度测量电路,所述温度测量电路被配置为:测量所述半导体存储器件的工作温度,以生成与所述工作温度对应的温度码;以及操作限制控制器,所述操作限制控制器被配置为:当基于所述温度码确定所述工作温度超过风险温度时,控制所述半导体存储器件的内部操作,而不管从所述存储器控制器传送的所述命令信号和所述控制信号如何,从而降低所述半导体存储器件的功耗。

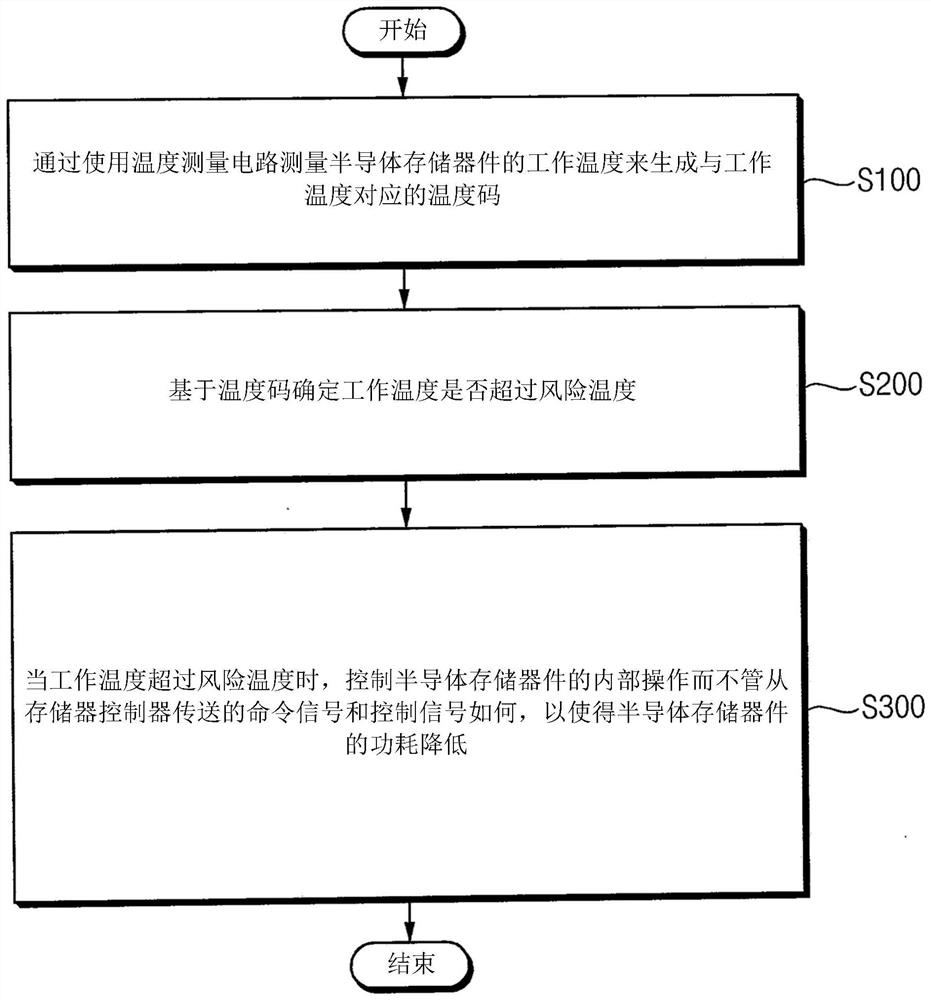

根据示例实施例的一方面,一种控制半导体存储器件的方法包括:通过使用温度测量电路测量半导体存储器件的工作温度来生成与所述工作温度对应的温度码;基于所述温度码确定所述工作温度是否超过风险温度;以及当所述工作温度超过所述风险温度时,控制所述半导体存储器件的内部操作,而不管从存储器控制器传送的命令信号和控制信号如何,从而降低所述半导体存储器件的功耗。

根据示例实施例的半导体存储器件、存储器系统和方法可以通过基于半导体存储器件的内部工作温度控制半导体存储器件的内部操作而不管存储器控制器的控制如何,来有效地防止半导体存储器件的物理损坏。

附图说明

根据以下结合附图的详细描述,将更清楚地理解本公开的以上以及其他方面,其中:

图1是示出根据示例实施例的控制半导体存储器件的方法的流程图;

图2是示出根据示例实施例的控制半导体存储器件的方法的概念图;

图3是示出根据示例实施例的存储器系统的框图;

图4是示出根据示例实施例的半导体存储器件的输入-输出引脚的示例实施例的图;

图5是示出根据示例实施例的半导体存储器件的框图;

图6是示出根据示例实施例的半导体存储器件中包括的操作限制控制器的示例实施例的框图;

图7和图8是示出在图6的操作限制控制器中生成的操作限制信号的示例实施例的图;

图9是示出根据示例实施例的半导体存储器件的状态的图;

图10是示出根据示例实施例的半导体存储器件的掉电命令的示例实施例的图;

图11是示出根据示例实施例的半导体存储器件的框图;

图12是示出图11的半导体存储器件中包括的操作限制控制器的操作的定时图;

图13和图14是示出在图11的半导体存储器件中包括的操作限制控制器中生成的虚拟掉电命令的示例实施例的图;

图15是示出根据示例实施例的半导体存储器件的掉电命令的示例实施例的图;

图16是示出根据示例实施例的半导体存储器件的框图;

图17和图18是示出在图16的半导体存储器件中包括的操作限制控制器中生成的虚拟掉电命令的示例实施例的图;

图19是示出根据示例实施例的半导体存储器件的掉电命令的示例实施例的图;

图20是示出根据示例实施例的半导体存储器件的框图;

图21是示出在图20的半导体存储器件中包括的操作限制控制器中生成的虚拟掉电命令的示例实施例的图;

图22是示出根据示例实施例的半导体存储器件的框图;

图23和图24是示出根据示例实施例的堆叠存储器件的图;

图25和图26是示出根据示例实施例的堆叠存储器件的封装结构的图;

图27是示出根据示例实施例的存储器系统的图;

图28是示出根据示例实施例的半导体存储器件中包括的温度测量电路的示例实施例的框图;

图29是示出图28的温度测量电路中包括的温度检测器的示例实施例的电路图;

图30是示出根据示例实施例的移动系统的框图。

具体实施方式

下文将参考示出了一些示例实施例的附图更全面地描述各种示例实施例。在附图中,相同的数字始终指相同的元件。可以省略重复的描述。

图1是示出根据示例实施例的控制半导体存储器件的方法的流程图,图2是示出根据示例实施例的控制半导体存储器件的方法的概念图。

参考图1,可以通过使用温度测量电路测量工作温度来生成与半导体存储器件的工作温度对应的温度码(S100)。下面将参考图28和图29来描述温度码的生成。

可以基于温度码确定工作温度是否超过风险温度(S200)。当工作温度超过风险温度时,可以控制半导体存储器件的内部操作而不管从存储器控制器传送的命令信号和控制信号如何,使得半导体存储器件的功耗降低(S300)。

在一些示例性实施例中,如将在下面参考图10至图19描述的,当工作温度超过风险温度时,可以控制半导体存储器件进入掉电模式,而不管从存储器控制器传送的掉电命令如何。

在一些示例性实施例中,如将在下面参考图20和图21描述的,当工作温度超过风险温度时,可以复位半导体存储器件,而不管从存储器控制器传送的复位信号如何。

在一些示例性实施例中,如将在下面参考图22描述的,当工作温度超过风险温度时,可以向存储器控制器传送包括错误的数据,而不管读取数据如何。

参考图2,存储器系统中的存储器控制器或主机设备可以基于诸如低温TL、中温TM、高温TH等若干参考温度来执行温度调节。第一温度调节水平THRT_1、第二温度调节水平THRT_2和第三温度调节水平THRT_3可以应用于参考温度TL、TM和TH之间的温度范围。当工作温度To超过参考温度TL、TM和TH时,可以控制半导体存储器件以降低功耗。可以通过降低半导体存储器件的工作频率和/或降低在半导体存储器件与存储器控制器之间传输数据的带宽,来实现功耗的降低。

在比较示例中,系统级的温度调节是基于从外部温度传感器(诸如TSOD)提供的、不能反映半导体存储器件的实际工作温度To的信息来执行的。

半导体存储器件可以基于来自内部传感器的信息,在工作温度To超过低温TL时执行双速(X2)刷新操作。这种刷新操作的控制不是为了防止半导体存储器件的物理损坏,而是为了防止数据丢失。

根据示例实施例,可以设置高于用于温度调节的参考温度的风险温度TR,以用于由半导体存储器件自身控制的内部温度调节。例如,风险温度TR可以被设置为大约100℃。当工作温度To超过风险温度TR时,可以控制半导体存储器件的内部操作以快速降低半导体存储器件的功耗,从而降低工作温度To。

因此,根据示例实施例的半导体存储器件、存储器系统和方法通过基于半导体存储器件的内部工作温度控制半导体存储器件的内部操作而不管存储器控制器的控制如何,来有效地防止半导体存储器件的物理损坏。

图3是示出根据示例实施例的存储器系统的框图。图4是示出根据示例实施例的半导体存储器件的输入-输出引脚的示例实施例的图。

参考图3,存储器系统10可以包括存储器控制器200和存储器件400。存储器控制器200和存储器件400可以包括用于相互通信的各个接口。接口可以通过用于传输命令CMD、地址ADDR、时钟信号CLK等的控制总线21以及用于传输数据的数据总线22连接。根据存储器件的一些标准,地址ADDR可以被包含在命令CMD中。存储器控制器200可以生成用于控制存储器件400的命令CMD,并且可以在存储器控制器200的控制下将数据写入存储器件400或从存储器件400读取数据。

存储器件400可以包括温度测量电路TMMS 100和操作限制控制器OLCON 300。半导体存储器件400可以包括多个输入-输出引脚、命令控制逻辑等。操作限制控制器OLCON 300可以向存储器控制器200传送操作限制信息OLINF。

多个输入-输出引脚可以用于与存储器控制器200通信。如图4所示,多个输入-输出引脚IOP可以包括电压引脚、控制引脚和数据引脚DQ,电压引脚被施加电源电压VDD、VPP和VDDQ以及接地电压VSS,控制引脚接收复位信号RESET_n、时钟信号CLK、芯片选择信号CS_n、命令地址信号CA、警报信号ALERT_n、时钟使能信号CKE、数据选通信号DQS、数据屏蔽信号DM_n等,数据引脚DQ接收或发送数据。图4示出了示例的引脚布局,并且输入-输出引脚的配置、数量和布局可以依据半导体存储器件400的种类而被不同地确定。

如下面将参考图5描述的,命令控制逻辑可以基于通过多个输入-输出引脚之中的控制引脚从存储器控制器200传送的命令信号和控制信号,来控制半导体存储器件400的操作。

如下面将参考图28和图29描述的,温度测量电路100可以测量半导体存储器件400的工作温度To,以生成与工作温度To对应的温度码TCODE。温度测量电路100可以包括设置在半导体存储器件400的半导体裸片中的片上温度传感器。可以使用片上温度传感器准确地反映半导体存储器件400的实际工作温度To。

当基于温度码TCODE确定工作温度To超过风险温度TR时,操作限制控制器300可以控制半导体存储器件400的内部操作,而不管从存储器控制器200传送的命令信号和控制信号如何,使得半导体存储器件400的功耗可以降低。下面将参考图6至图22进一步描述操作限制控制器300对内部操作的控制。

存储器控制器200可以包括ECC(错误校验码)引擎210。ECC引擎210可以对数据进行编码以向半导体存储器件400提供写入数据,以及对来自半导体存储器件400的数据进行解码以检查和纠正接收到的数据中的错误。当无法纠正数据中的错误时,存储器控制器200可以采取适当的措施,诸如,使半导体存储器件400复位。

图5是示出根据示例实施例的半导体存储器件的框图。

参考图5,存储器件400可以包括命令控制逻辑410、地址寄存器420、存储体控制逻辑430、行选择电路460(或行译码器)、列译码器470、存储单元阵列480、读出放大器单元485、输入/输出(I/O)门控电路490、数据输入/输出(I/O)缓冲器495、刷新控制器440、温度测量电路TMMS 100和操作限制控制器OLCON 300。

存储单元阵列480可以包括多个存储体阵列480a、...、480h。行选择电路460可以包括分别耦接到存储体阵列480a、...、480h的多个存储体行选择电路460a、...、460h。列译码器470可以包括分别耦接到存储体阵列480a、...、480h的多个存储体列译码器470a、...、470h。读出放大器单元485可以包括分别耦接到存储体阵列480a、...、480h的多个存储体读出放大器485a、...、485h。

地址寄存器420可以从存储器控制器200接收包括存储体地址BANK_ADDR、行地址ROW_ADDR和列地址COL_ADDR的地址ADDR。地址寄存器420可以向存储体控制逻辑430提供接收到的存储体地址BANK_ADDR,可以向行选择电路460提供接收到的行地址ROW_ADDR,并且可以向列译码器470提供接收到的列地址COL_ADDR。

存储体控制逻辑430可以响应于存储体地址BANK_ADDR生成存储体控制信号。存储体行选择电路460a、...、460h中的对应于存储体地址BANK_ADDR的存储体行选择电路可以响应于存储体控制信号被激活,并且存储体列译码器470a、...、470h中的对应于存储体地址BANK_ADDR的存储体列译码器可以响应于存储体控制信号被激活。

来自地址寄存器420的行地址ROW_ADDR可以应用于存储体行选择电路460a、...、460h。存储体行选择电路460a、...、460h中的被激活的存储体行选择电路可以对行地址ROW_ADDR进行译码,并且可以激活对应于行地址ROW_ADDR的字线。例如,被激活的存储体行选择电路460可以将字线驱动电压施加到对应于行地址ROW_ADDR的字线。

列译码器470可以包括列地址锁存器。列地址锁存器可以从地址寄存器420接收列地址COL_ADDR,并且可以临时存储接收到的列地址COL_ADDR。在一些示例实施例中,在突发模式下,列地址锁存器可以生成从接收到的列地址COL_ADDR递增的列地址。列地址锁存器可以将临时存储或生成的列地址应用到存储体列译码器470a、...、470h。

存储体列译码器470a、...、470h中的被激活的存储体列译码器可以对列地址COL_ADDR进行译码,并且可以控制I/O门控电路490以输出对应于列地址COL_ADDR的数据。

I/O门控电路490可以包括用于门控输入/输出数据的电路。I/O门控电路490还可以包括:用于存储从存储体阵列480a、...、480h输出的数据的读取数据锁存器,以及用于将数据写入存储体阵列480a、...、480h的写入驱动器。

要从存储体阵列480a、...、480h中的一个存储体阵列读取的数据可以由存储体读出放大器485a、...、485h中的与要从其读取数据的该存储体阵列耦接的存储体读出放大器感测,并且可以被存储在读取数据锁存器中。存储在读取数据锁存器中的数据可以经由数据I/O缓冲器495提供给存储器控制器200。要写入存储体阵列480a、...、480h中的一个存储体阵列中的数据DQ可以从存储器控制器200提供给数据I/O缓冲器495。写入驱动器可以将数据DQ写入存储体阵列480a、...、480h中的一个存储体阵列中。

命令控制逻辑410可以控制存储器件400的操作。例如,命令控制逻辑410可以生成用于存储器件400的控制信号,以便执行写入操作、读取操作或刷新操作。命令控制逻辑410可以基于从图3中的存储器控制器200传送的命令CMD生成诸如以下内部命令信号:激活信号IACT、预充电信号IPRE、刷新信号IREF、读取信号IRD、写入信号IWR等。命令控制逻辑410可以包括:对从存储器控制器200接收到的命令CMD进行译码的命令译码器411,以及设置存储器件400的操作模式的模式寄存器组412。

尽管图5将命令控制逻辑410和地址寄存器420示出为彼此不同,但是命令控制逻辑410和地址寄存器420可以实现为单个集成电路。此外,虽然图5示出了命令CMD和地址ADDR作为不同信号被提供,但是命令CMD和地址ADDR可以作为例如如由DDR5、HBM和LPDDR5标准所规定的组合信号被提供。

温度测量电路100可以测量半导体存储器件400的工作温度To,以生成对应于工作温度To的温度码TCODE。

当基于温度码TCODE确定工作温度To超过风险温度TR时,操作限制控制器300可以控制半导体存储器件400的内部操作,而不管从存储器控制器200传送的命令信号和控制信号如何,使得半导体存储器件400的功耗可以降低。下面将参考图6至图22进一步描述操作限制控制器300对内部操作的控制。

图6是示出根据示例实施例的半导体存储器件中包括的操作限制控制器的示例实施例的框图,图7和图8是示出在图6的操作限制控制器中生成的操作限制信号的示例实施例的图。

参考图6,操作限制控制器300可以包括比较电路CMP 310和控制信号生成器CSG320。

比较电路310可以基于温度码TCODE生成操作限制信号SOL。

在一些示例性实施例中,如图7所示,比较电路310可以响应于从逻辑低电平L到逻辑高电平H周期性激活的使能信号EN来确定是否激活操作限制信号SOL。在这种情况下,比较电路310可以在工作温度To超过风险温度TR的时间点激活操作限制信号SOL,并且在固定的操作限制时间tOLc之后去激活(deactivate)操作限制信号SOL,而不管工作温度To如何。图7示出了工作温度To在时间点T11和T13超过风险温度TR并且在时间点T12不超过风险温度TR的示例。

在一些示例实施例中,如图8中的第一情况CS1所示,比较电路310可以在工作温度To超过风险温度TR的时间点T21激活操作限制信号SOL,并在工作温度To降低到风险温度TR以下的时间点T22去激活操作限制信号SOL。在这种情况下,操作限制时间tOL1可以依据工作温度To的改变而改变。

在一些示例实施例中,如图8中的第二情况CS2所示,比较电路310可以在工作温度To超过风险温度TR的时间点T21激活操作限制信号SOL,并在工作温度To降低到低于风险温度TR的限制结束温度TR'以下的时间点T23去激活操作限制信号SOL。在图8中,TCDR指示与风险温度TR对应的温度码TCODE的值,TCDR'指示与限制结束温度TR'对应的温度码TCODE的值。使能信号EN可以维持逻辑高电平H。在这种情况下,操作限制时间tOL2可以依据工作温度To的改变而改变。比较电路310可以在工作温度To超过限制结束温度TR'的时间点T24不激活操作限制信号SOL。这样,可以应用滞后(hysteresis)方案,以使得用于去激活操作限制信号SOL的限制结束温度TR'被设置为低于用于激活操作限制信号SOL的风险温度TR。通过滞后方案,可以防止过度频繁地控制内部操作,以稳定半导体存储器件的操作并且有效地防止半导体存储器件的物理损坏。

操作限制控制器300可以响应于操作限制信号SOL的激活控制半导体存储器件进入掉电模式,以及响应于操作限制信号SOL的去激活控制半导体存储器件退出掉电模式。换言之,掉电模式的时间间隔可以根据图7和图8中的操作限制时间tOLc、tOL1和tOL2进行调整。

控制信号生成器320可以响应于操作限制信号SOL的激活而生成信号SCTR,以控制半导体存储器件的内部操作。

在一些示例性实施例中,如下面将参考图11、图12、图13和图14描述的,控制信号生成器320生成的信号SCTR可以包括虚拟时钟使能信号VCKE和虚拟芯片选择信号VCS_n。

在一些示例性实施例中,如下面将参考图15、图16、图17和图18描述的,信号SCTR可以包括虚拟行命令-地址信号VR0、VR1、VR2和VR3。

在一些示例性实施例中,如下面将参考图20和图21描述的,信号SCTR可以包括虚拟复位信号VRESET_n和虚拟芯片选择信号VCS_n。

图9是示出根据示例实施例的半导体存储器件的状态的图。

参考图9,当半导体存储器件被上电时,复位操作可以基于从存储器控制器传送的复位信号RESET_n来执行。半导体存储器件可以在完成复位操作之后进入空闲模式。半导体存储器件可以基于从存储器控制器传送的激活命令ACT从空闲模式退出并且进入正常操作模式。

此外,半导体存储器件可以基于从存储器控制器传送的掉电进入命令PDE进入掉电模式,并且基于从存储器控制器传送的掉电退出命令PDX退出掉电模式。

通常,空闲模式下的功耗低于正常操作模式下的功耗,掉电模式下的功耗低于空闲模式下的功耗。

根据示例实施例,当工作温度To超过风险温度TR时,可以在半导体存储器件内部生成虚拟命令或虚拟控制信号,以复位半导体存储器件或者使半导体存储器件(从空闲模式或正常操作模式,参见图9)进入掉电模式,从而降低功耗。通过强制功耗降低,可以降低工作温度To并且可以防止半导体存储器件的物理损坏。来自OLCON 300的命令VPDE和VPDX也被示出在图9中。

图10是示出根据示例实施例的半导体存储器件的掉电命令的示例实施例的图。图10示出了根据DDR4标准的掉电命令。

参考图10,掉电命令可以包括掉电进入命令PDE和掉电退出命令PDX。根据DDR4标准,可以基于时钟使能信号CKE的逻辑电平以及基于处于时钟使能信号CKE的第一边沿EG1和第二边沿EG2的芯片选择信号CS_n,来确定掉电进入命令PDE和掉电退出命令PDX。在图10中,H指示逻辑高电平,L指示逻辑低电平。

图11是示出根据示例实施例的半导体存储器件的框图。图11示出了用于描述示例实施例的组件,并且省略了参考图5描述的其他组件。

参考图11,半导体存储器件401可以包括控制引脚P11和P12、命令控制逻辑410、操作限制控制器OLCON 301和选择器501。

选择器501可以向命令控制逻辑410传送虚拟时钟使能信号VCKE和虚拟芯片选择信号VCS_n,来代替通过控制引脚P11和P12从存储器控制器传送的时钟使能信号CKE和芯片选择信号CS_n。

当工作温度To超过风险温度TR时,操作限制控制器301可以生成与掉电命令PDE和PDX对应的虚拟时钟使能信号VCKE和虚拟芯片选择信号VCS_n。

选择器501可以包括基于选择信号SEL进行操作的第一复用器MX1和第二复用器MX2。选择信号SEL可以由操作限制控制器301生成。

第一复用器MX1可以在选择信号SEL具有激活电平(例如,逻辑高电平H)时选择虚拟时钟使能信号VCKE,并且向命令控制逻辑410提供虚拟时钟使能信号VCKE。相反,第一复用器MX1可以在选择信号SEL具有去激活电平(例如,逻辑低电平L)时选择时钟使能信号CKE,并且向命令控制逻辑410提供时钟使能信号CKE。

第二复用器MX2可以在选择信号SEL具有激活电平时选择虚拟芯片选择信号VCS_n,并且向命令控制逻辑410提供虚拟芯片选择信号VCS_n。相反,第二复用器MX2可以在选择信号SEL具有去激活电平时选择芯片选择信号CS_n,并且向命令控制逻辑410提供芯片选择信号CS_n。

图12是示出图11的半导体存储器件中包括的操作限制控制器的操作的定时图。图13和图14是示出在图11的半导体存储器件中包括的操作限制控制器中生成的虚拟掉电命令的示例实施例的图。

参考图12,操作限制控制器301可以基于操作限制信号SOL的定时来生成虚拟命令VCMD。虚拟命令VCMD可以包括虚拟掉电进入命令VPDE和虚拟掉电退出命令VPDX。

操作限制控制器301可以例如在时间点T31,响应于操作限制信号SOL的激活,生成如图13所示的虚拟掉电进入命令VPDE。此外,操作限制控制器301可以例如在时间点T32,响应于操作限制信号SOL的去激活,生成如图14所示的虚拟掉电退出命令VPDX。另外,参见图9中所示的状态转换并且参考VPDE和VPDX。

图13和图14利用垂直虚线标出时钟信号CK_t和互补时钟信号CK_c的第一边沿EG1和第二边沿EG2来示出虚拟时钟使能信号VCKE的逻辑电平和虚拟芯片选择信号VCS_n的逻辑电平。图6中的控制信号生成器320可以生成具有与图10所示的掉电进入命令PDE和掉电退出命令PDX相同的电平的虚拟掉电进入命令VPDE和虚拟掉电退出命令VPDX。结果,命令控制逻辑410可以基于虚拟掉电进入命令VPDE和虚拟掉电退出命令VPDX,执行与基于掉电进入命令PDE和掉电退出命令PDX的序列完全相同的掉电进入和退出序列。在一些实施例中,例如存储器件400(或401或402等)内部的操作限制控制器OLCON 300模仿地生成(spoof)来自例如存储器控制器200的控制信号。模仿生成的控制信号的一些示例可以称为,例如,虚拟掉电进入命令VPDE、虚拟掉电退出命令VPDX、虚拟复位信号VRESET和虚拟芯片选择信号VCS。在温度已经恢复到正常状况之后(在非限制性示例中,诸如在图8中的时间T23之后),模仿生成被暂停并且存储器件再次处于存储器控制器200的控制之下。作为另一示例,向模仿生成的转变以及从模仿生成的转变参见图12的T31(“VPDE”)以及从T32到T33(“VPDX”)。

操作限制控制器301可以例如在时间点T31响应于操作限制信号SOL的激活来激活选择信号SEL,并且例如在时间点T33基于操作限制信号SOL的去激活来去激活选择信号SEL。

结果,操作限制控制器301可以控制半导体存储器件401,使得半导体存储器件401可以响应于虚拟掉电进入命令VPDE而进入掉电模式,以及响应于虚拟掉电退出命令VPDX而退出掉电模式。

图15是示出根据示例实施例的半导体存储器件的掉电命令的示例实施例的图。图15示出了根据HBM标准的掉电命令。

参考图15,掉电命令可以包括掉电进入命令PDE和掉电退出命令PDX。根据HBM标准,可以根据行命令-地址信号R0、...、R3中的一部分行命令-地址信号在时钟信号CK的上升沿EGr和下降沿Egf处的逻辑电平,来确定掉电进入命令PDE和掉电退出命令PDX。H指示逻辑高电平,L指示逻辑低电平。

图16是示出根据示例实施例的半导体存储器件的框图。图16示出了用于描述示例实施例的组件,并且省略了参考图5描述的其他组件。

参考图16,半导体存储器件402可以包括控制引脚P21、P22、P23、P24、命令控制逻辑410、操作限制控制器OLCON 302和选择器502。

选择器502可以向命令控制逻辑410传送第一至第四虚拟行命令-地址信号VR0、VR1、VR2、VR3,来代替通过控制引脚P21、...、P24从存储器控制器传送的第一至第四行命令-地址信号R0、...、R3。

当工作温度To超过风险温度TR时,操作限制控制器301可以生成与掉电命令PDE和PDX对应的虚拟行命令-地址信号VR0、...、VR3。

选择器501可以包括基于选择信号SEL进行操作的第一至第四复用器MX1、...、MX4。选择信号SEL可以由操作限制控制器302生成。

第一复用器MX1可以在选择信号SEL具有激活电平(例如,逻辑高电平H)时选择第一虚拟行命令-地址信号VR0,并且向命令控制逻辑410提供第一虚拟行命令-地址信号VR0。相反,第一复用器MX1可以在选择信号SEL具有去激活电平(例如,逻辑低电平L)时选择第一行命令-地址信号R0,并且向命令控制逻辑410提供第一行命令-地址信号R0。

第二复用器MX2可以在选择信号SEL具有激活电平时选择第二虚拟行命令-地址信号VR1,并且向命令控制逻辑410提供第二虚拟行命令-地址信号VR1。相反,第二复用器MX2可以在选择信号SEL具有去激活电平时选择第二行命令-地址信号R1,并且向命令控制逻辑410提供第二行命令-地址信号R1。

第三复用器MX3可以在选择信号SEL具有激活电平时选择第三虚拟行命令-地址信号VR2,并且向命令控制逻辑410提供第三虚拟行命令-地址信号VR2。相反,第三复用器MX3可以在选择信号SEL具有去激活电平时选择第三行命令-地址信号R2,并且向命令控制逻辑410提供第三行命令-地址信号R2。

第四复用器MX4可以在选择信号SEL具有激活电平时选择第四虚拟行命令-地址信号VR3,并且向命令控制逻辑410提供第四虚拟行命令-地址信号VR3。相反,第四复用器MX4可以在选择信号SEL具有去激活电平时选择第四行命令-地址信号R3,并且向命令控制逻辑410提供第四行命令-地址信号R3。

图17和图18是示出在图16的半导体存储器件中包括的操作限制控制器中生成的虚拟掉电命令的示例实施例的图。

如参考图12所描述的,操作限制控制器302可以基于操作限制信号SOL的定时来生成虚拟命令VCMD。虚拟命令VCMD可以包括虚拟掉电进入命令VPDE和虚拟掉电退出命令VPDX。

操作限制控制器302可以响应于操作限制信号SOL的激活生成如图17所示的虚拟掉电进入命令VPDE,以及响应于操作限制信号SOL的去激活生成如图18所示的虚拟掉电退出命令VPDX。

图17和图18示出了虚拟行命令-地址信号VR0、...、VR3在时钟信号CK_t的上升沿EGr和下降沿EGf的逻辑电平。图6中的控制信号生成器320可以生成具有与图15所示的掉电进入命令PDE和掉电退出命令PDX相同的电平的虚拟掉电进入命令VPDE和虚拟掉电退出命令VPDX。结果,命令控制逻辑410可以基于虚拟掉电进入命令VPDE和虚拟掉电退出命令VPDX,执行与基于掉电进入命令PDE和掉电退出命令PDX的序列完全相同的掉电进入和退出序列。

此外,如参考图12所描述的,操作限制控制器302可以例如在时间点T31响应于操作限制信号SOL的激活来激活选择信号SEL,并且例如在时间点T33基于操作限制信号SOL的去激活来去激活选择信号SEL。

结果,操作限制控制器302可以控制半导体存储器件402,使得半导体存储器件402可以响应于虚拟掉电进入命令VPDE而进入掉电模式,以及响应于虚拟掉电退出命令VPDX而退出掉电模式。

图19是示出根据示例实施例的半导体存储器件的掉电命令的示例实施例的图。图19示出了根据DDR5标准的掉电命令。

参考图19,掉电命令可以包括掉电进入命令PDE和掉电退出命令PDX。根据DDR5标准,可以根据芯片选择信号CS_n和命令-地址信号CA0、...、CA4中的一部分命令-地址信号在时钟信号的上升沿处的逻辑电平,来确定掉电进入命令PDE和掉电退出命令PDX。H指示逻辑高电平,L指示逻辑低电平。

半导体存储器件的配置和操作可以与参考图16至图18描述的基本相同,并且重复描述被省略。

如上所述,操作限制控制器可以基于操作限制信号SOL的定时来生成虚拟命令VCMD。虚拟命令VCMD可以包括虚拟掉电进入命令VPDE和虚拟掉电退出命令VPDX。操作限制控制器可以响应于操作限制信号SOL的激活生成虚拟掉电进入命令VPDE,以及响应于操作限制信号SOL的去激活生成虚拟掉电退出命令VPDX。

图20是示出根据示例实施例的半导体存储器件的框图,图21是示出在图20的半导体存储器件中包括的操作限制控制器中生成的虚拟掉电命令的示例实施例的图。图20示出了用于描述示例实施例的组件,并且省略了参考图5描述的其他组件。

参考图20,半导体存储器件403可以包括控制引脚P31和P32、命令控制逻辑410、操作限制控制器OLCON 303和选择器503。

选择器503可以向命令控制逻辑410传送虚拟复位信号VRESET_n和虚拟芯片选择信号VCS_n,来代替通过控制引脚P31和P32从存储器控制器传送的复位信号RESET_n和芯片选择信号CS_n。

当工作温度To超过风险温度TR时,操作限制控制器303可以如图21所示生成与掉电命令PDE和PDX对应的虚拟复位信号VRESET_n和虚拟芯片选择信号VCS_n。可以基于操作限制信号SOL的定时来确定选择信号SEL、虚拟复位信号VRESET_n和虚拟芯片选择信号VCS_n的定时。tPW_RESET、tINT2和tINT3与DDR5标准中规定的相同。

例如,半导体存储器件403的工作温度To可以在时间点T41超过风险温度TR。在时间点T41,图6中的比较电路310可以激活操作限制信号SOL,并且控制信号生成器320可以响应于操作限制信号SOL的激活来激活选择信号SEL。随后,tPW_RESET从时间点T42至时间点T43生效。控制信号生成器320可以使虚拟复位信号VRESET_n和虚拟芯片选择信号VCS_n转变为具有与DDR5标准中规定的定时相同的定时。在时间点T44之后,控制信号生成器320可以去激活选择信号SEL。

图22是示出根据示例实施例的半导体存储器件的框图。图22示出了用于描述示例实施例的组件,并且省略了参考图5描述的其他组件。

参考图22,半导体存储器件404可以包括数据引脚P41、...、P4k、数据输入-输出(I/O)缓冲器495、操作限制控制器OLCON 304和数据错误生成器504。

数据错误生成器504可以响应于操作限制信号SOL的激活,将数据引脚P41、P42、...、P4k中的至少一部分下拉至接地电压VSS。根据示例实施例,数据错误生成器504可以响应于操作限制信号SOL的激活,将数据引脚P41、...、P4k中的至少一部分上拉至电源电压。

在一些示例实施例中,如图22所示,数据错误生成器504可以包括用于基于操作限制信号SOL下拉数据引脚P41、...、P4k的晶体管NT1、...、NTk。

如参考图6至图8所描述的,当工作温度To超过风险温度TR时,操作限制控制器304可以激活操作限制信号SOL。结果,当工作温度超过风险温度时,数据错误生成器504可以向存储器控制器传送包括错误的数据,而不管从数据输入-输出缓冲器495提供的读取数据如何。

图3的存储器控制器200中包括的ECC引擎可以对从半导体存储器件400提供的读取数据进行解码。如果读取数据的错误不可纠正,则存储器控制器200可以采取适当的措施。例如,当读取数据的错误不可纠正时,存储器控制器200可以复位半导体存储器件400。如参考图22所描述的,可以通过故意产生提供给存储器控制器200的数据中的错误,在存储器控制器200的控制下降低工作温度To。通过将足够数量的引脚拉至VCC或接地,数据的任何特定部分的不可纠正错误的可能性几乎可以是特定的(概率几乎为1)。然后,例如,数据错误生成器504的错误可以使得存储器控制器200基于ECC引擎对不可纠正错误的检测而采取纠正动作,诸如,使半导体存储器件400复位。

图23和图24是示出根据示例实施例的堆叠存储器件的图。

参考图23,半导体存储器件900可以包括第一至第k半导体集成电路层LA1(910)至LAk(920),其中,最低的第一半导体集成电路层LA1被假设为接口或控制芯片,其他半导体集成电路层LA2至LAk被假设为包括核存储器芯片的从属层。从属芯片可以形成如上所述的多个存储体。

第一至第k半导体集成电路层LA1至LAk可以通过贯穿衬底通路TSV(例如,穿硅通路)在层之间发送和接收信号。作为接口或控制芯片的、最低的第一半导体集成电路层LA1可以通过形成在外表面上的导电结构与外部存储器控制器通信。

第一半导体集成电路层LA1 910至第k半导体集成电路层LAk 920均可以包括存储器区域921以及用于驱动存储器区域921的外围电路922。例如,外围电路922可以包括:用于驱动存储器的字线的行-驱动器、用于驱动存储器的位线的列-驱动器、用于控制数据的输入-输出的数据输入-输出电路、用于从外部源接收命令并缓冲命令的命令缓冲器、以及用于从外部源接收地址并缓冲地址的地址缓冲器。

第一半导体集成电路层LA1 910还可以包括控制电路。控制电路可以基于来自存储器控制器的命令和地址信号来控制对存储器区域921的访问,并且可以生成用于访问存储器区域921的控制信号。

对应于从属层的半导体集成电路层LA2至LAk均可以包括如上所述的刷新控制器。

图24示出了示例高带宽存储器(HBM)结构。参考图24,HBM 1100可以具有堆叠的多个DRAM半导体裸片1120、1130、1140和1150。堆叠结构的HBM可以通过多个独立接口(即,通道)来优化。根据HBM标准,每个DRAM堆叠最多可以支持8个通道。图24示出了包含4个DRAM半导体裸片1120、1130、1140和1150的示例堆叠,并且每个DRAM半导体裸片支持两个通道CHANNEL0和CHANNEL1。

每个通道提供对一组独立的DRAM存储体的访问。来自一个通道的请求可能无法访问附接到不同通道的数据。通道是独立时钟控制的,并且不需要同步。

HBM 1100还可以包括位于堆叠结构底部的接口裸片1110或逻辑裸片,以提供信号路由和其他功能。DRAM半导体裸片1120、1130、1140和1150的一些功能可以在接口裸片1110中实现。

DRAM半导体裸片1120、1130、1140和1150均可以包括如上所述的温度测量电路和操作限制控制器。在一些示例实施例中,接口裸片1110可以包括如上所述的温度测量电路和操作限制控制器。

图25和图26是示出根据示例实施例的堆叠存储器件的封装结构的图。

参考图25,存储器件1000a可以是存储器封装件,并且可以包括基底基板或中介层ITP以及堆叠在中介层ITP上的堆叠存储器件。堆叠存储器件可以包括逻辑半导体裸片LSD(或缓冲器半导体裸片)和多个存储器半导体裸片MSD1、...、MSD4。

参考图26,存储器件1000b可以是存储器封装件,并且可以包括基底基板BSUB和堆叠在基底基板BSUB上的堆叠存储器件。堆叠存储器件可以包括逻辑半导体裸片LSD和多个存储器半导体裸片MSD1、...、MSD4。

图25示出了除了逻辑半导体裸片LSD之外的存储器半导体裸片MSD1、...、MSD4被垂直堆叠并且逻辑半导体裸片LSD通过中介层ITP或基底基板电连接到存储器半导体裸片MSD1、...、MSD4的结构。相比之下,图26示出了逻辑半导体裸片LSD与存储器半导体裸片MSD1、...、MSD4垂直堆叠的结构。

如上所述的温度测量电路和操作限制控制器可以设置在逻辑半导体裸片LSD中。温度测量电路可以测量堆叠存储器件的工作温度,以生成对应于工作温度的温度码。当基于温度码确定工作温度超过风险温度时,操作限制控制器可以控制堆叠存储器件的内部操作,而不管从存储器控制器传送的命令信号和控制信号如何,使得堆叠存储器件的功耗降低。

基底基板BSUB可以与中介层ITP相同或包括中介层ITP。基底基板BSUB可以是印刷电路板(PCB)。诸如导电凸块BMP的外部连接元件可以形成在基底基板BSUB的下表面上,并且诸如导电凸块的内部连接元件可以形成在基底基板BSUB的上表面上。在一些示例实施例中,半导体裸片LSD和MSD1、...、MSD4可以通过穿硅通路电连接。在其他示例实施例中,半导体裸片LSD和MSD1、...、MSD4可以通过接合线(bonding wire)电连接。在另外的其他示例实施例中,半导体裸片LSD和MSD1、...、MSD4可以通过穿硅通路和接合线的组合电连接。在图25的示例实施例中,逻辑半导体裸片LSD可以通过形成在中介层ITP中的导线图案电连接到存储器半导体裸片MSD1、...、MSD4。可以使用诸如树脂RSN的密封剂来封装堆叠的半导体裸片LSD和MSD1、...、MSD4。

图27是示出根据示例实施例的存储器系统的图。

如图27所示,存储器系统70可以包括存储器模块1200和存储器控制器200。存储器模块1200可以包括模块基板以及安装在模块基板上的多个存储器芯片(MEM)401a、401b、401c、401d、401e、401f、401g、401h和温度传感器TSOD 1250。图27示出了八个存储器芯片401a、...、401h的非限制性示例,然而,可以不同地确定存储器模块1200中包括的存储器芯片的数量。

参考图27,存储器模块1200可以经由数据总线1210和控制总线1220连接到存储器控制器200。存储器模块1200可以插入到更大的存储器系统或计算系统的插座连接器(socket connector)中。存储器模块1200的电连接器(或引脚)可以连接到插座连接器的电接触。连接到电接触的电连接器和总线1210和1220允许直接访问存储器缓冲器或缓冲器芯片1270以及间接访问存储器模块1200的存储器芯片401a、...、401h。数据总线1210可以包括用于传输数据信号DQ和数据选通信号DQS的信号线(导电布线),并且控制总线1220包括命令(CMD)线和/或地址(ADD)线中的至少一者。

数据总线1210和控制总线1220通过相应的插座/引脚和总线信号线布置直接连接到缓冲器芯片1270。进而,缓冲器芯片1270至少通过从缓冲器芯片1270的指定端口到存储器芯片401a、...、401h的相应端口的、公共连接的第一总线1230和单独连接的第二总线1240a、1240b、1240c、1240d、1240e、1240f、1240g、1240h连接到相应的存储器芯片401a、...、401h。缓冲器芯片1270可以用于通过第一总线1230向相应的存储器芯片401a、...、401h传送通过控制总线1220从存储器控制器200接收到的命令和/或地址。

缓冲器芯片1270可以通过相应的第二总线1240a、...、1240h向存储器芯片401a、...、401h传送通过数据总线1210从存储器控制器200接收的写入数据DQ(即,要写入存储器芯片400a、...、400h中的一个或更多个存储器芯片的数据)以及数据选通信号DQS。或者,缓冲器芯片1270可以通过数据总线1210向存储器控制器200传送通过第二总线1240a、...、1240h从存储器芯片401a、...、401h中的一个或更多个存储器芯片获得的读取数据DQ(从存储器芯片401a、...、401h中的一个或更多个存储器芯片获取的数据)。

存储器芯片401a、...、401h均可以包括如上所述的温度测量电路TMMS100和操作限制控制器OLCON 300。温度测量电路100可以测量堆叠存储器件的工作温度,以生成对应于工作温度的温度码。当基于温度码确定工作温度超过风险温度时,操作限制控制器300可以控制堆叠存储器件的内部操作,而不管从存储器控制器传送的命令信号和控制信号如何,使得堆叠存储器件的功耗降低。在示例实施例中,对于存储器芯片401a、...、401h中的任一存储器芯片,存储器控制器200可以基于从温度传感器TSOD 1250提供的温度信息来控制温度调节操作,以调整该存储器芯片的工作温度,并且该存储器芯片中的操作限制控制器可以基于温度码控制该存储器芯片的内部操作,而不管温度调节操作如何。

图28是示出根据示例实施例的半导体存储器件中包括的温度测量电路的示例实施例的框图,图29是示出图28的温度测量电路中包括的温度检测器的示例实施例的电路图。

参考图28,温度测量电路100可以包括温度检测器(DET)110和模数转换器(CNV)120。温度检测器110可以输出与工作温度To成比例的电压信号VPTAT和电流信号IPTAT中的至少一者。模数转换器120可以将温度检测器110的输出转换为数字信号,以生成多位温度码TCODE。

在一些示例实施例中,温度检测器110可以利用耦接在电源电压VDD与接地电压VSS之间的第一PMOS晶体管M1(具有电流I1)、第二PMOS晶体管M2(具有电流I2)、反馈放大器AMP、电阻器R以及第一双极晶体管B1和第二双极晶体管B2来实现,如图29所示。电阻器R两端的电压dVBE可以由表达式1获得。

(表达式1)

dVBE=VBE1-VBE2

=VT*Ln(Ic1/Is1)-VT*Ln(n*Ic2/Is2)

=VT*Ln(n)

在表达式1中,Is1指示双极晶体管B1的反向饱和电流,Is2指示双极晶体管B2的反向饱和电流。此外,Ic1指示流过双极晶体管B1的电流,Ic2指示流过双极晶体管B2的电流;VBE1指示双极晶体管B1两端的电压,VBE2指示双极晶体管B2两端的电压。此外,n是双极晶体管B1、B2的增益比,VT指示与温度检测器110的绝对温度成比例的温度电压。Ln(n)是恒定值,因此电阻器R两端的电压dVBE和流过电阻器R的电流I2与温度变化成比例。可以基于与工作温度成比例的电压dVBE和电流I2生成电压信号VPTAT和电流信号IPTAT作为输出。

参考图28和图29描述的片上温度传感器可以集成在半导体存储器件的同一半导体裸片中,并且片上温度传感器不同于设置在存储器模块处的诸如TSOD的外部温度传感器。使用参考图28和图29描述的温度测量电路100,可以准确地测量半导体存储器件的工作温度To,并且可以防止半导体存储器件的物理损坏。

图30是示出根据示例实施例的移动系统的框图。

参考图30,移动系统2000可以包括应用处理器(AP)2100、连接单元2200、易失性存储器件(VM)2300、非易失性存储器件(NVM)2040、用户接口2500和电源2600。在一些实施例中,移动系统2000可以是,例如,移动电话、智能电话、个人数字助理(PDA)、便携式多媒体播放器(PMP)、数码相机、音乐播放器、便携式游戏机、导航系统或其他类型的电子设备。

应用处理器2100可以执行应用,例如,网络浏览器、游戏应用、视频播放器等。连接单元2200可以执行与外部设备的有线或无线通信。易失性存储器件2300可以存储由应用处理器2100处理的数据,或者可以用作工作存储器。非易失性存储器件2400可以存储用于启动移动系统2000的启动映像。用户接口2500可以包括:诸如键盘、触摸屏等的至少一个输入设备,以及诸如扬声器、显示设备等的至少一个输出设备。电源2600可以向移动系统1200提供电源电压。

如上所述,易失性存储器件2300可以包括温度测量电路TMMS 100和操作限制控制器OLCON 300。温度测量电路100可以测量堆叠存储器件的工作温度以生成对应于工作温度的温度码。当基于温度码确定工作温度超过风险温度时,操作限制控制器300可以控制堆叠存储器件的内部操作,而不管从存储器控制器传送的命令信号和控制信号如何,使得堆叠存储器件的功耗降低。

如上所述,根据示例实施例的半导体存储器件、存储器系统和方法可以通过基于半导体存储器件的内部工作温度控制半导体存储器件的内部操作而不管存储器控制器的控制如何,来有效地防止半导体存储器件的物理损坏。

本文描述的实施例可以应用于任何存储器件和包括存储器件的系统。例如,实施例可以应用于诸如以下系统:存储卡、固态硬盘(SSD)、嵌入式多媒体卡(eMMC)、移动电话、智能电话、个人数字助理(PDA)、便携式多媒体播放器(PMP)、数码相机、摄像机、个人计算机(PC)、服务器计算机、工作站、笔记本电脑、数字TV、机顶盒、便携式游戏机、导航系统、可穿戴设备、物联网(IoT)设备、万物互联(IoE)设备、电子书、虚拟现实(VR)设备、增强现实(AR)设备、服务器系统、汽车设备等。