晶片载置台及其制法

文献发布时间:2023-06-19 09:26:02

技术领域

本发明涉及晶片载置台及其制法。

背景技术

作为晶片载置台,公知例如专利文献1所记载的装置。专利文献1中,作为这样的晶片载置台,公开了具备陶瓷部件、网格电极、导电性的连接部件、以及外部通电部件的晶片载置台。陶瓷部件具备晶片载置面。网格电极埋设在陶瓷部件中。连接部件与网格电极接触,并从陶瓷部件中的与晶片载置面相反一侧的面露出到外部。外部通电部件经由接合层而与连接部件中的露出到外部的面接合。

现有技术文献

专利文献

专利文献1:国际公开第2015/198892号小册子

发明内容

发明所要解决的课题

然而,由于连接部件与网格电极线接触,所以接触部件与网格电极的实际接触面积较小。因此,在电流从外部通电部件经由连接部件流入到网格电极时的连接部件附近的发热量变多,有时晶片的均热性受损。

本发明是为了解决这样的课题而完成的,其主要目的在于,抑制对网格电极通电时的连接部件的发热。

用于解决课题的方案

本发明的晶片载置台具备:

陶瓷部件,其具备晶片载置面;

网格电极,其埋设在上述陶瓷部件中;

导电性的连接部件,其与上述网格电极接触,从上述陶瓷部件中的与上述晶片载置面相反一侧的面露出到外部;以及

外部通电部件,其接合于上述连接部件中的露出到外部的面,

上述晶片载置台的特征在于,

在位于上述网格电极中的与上述连接部件对置的区域的网格开口部填充有烧结导电体,该烧结导电体是包含导电性粉末和陶瓷原料的混合物的烧结体。

在该晶片载置台中,在网格电极中的位于与连接部件对置的区域的网格开口部填充有烧结导电体。烧结导电体是包含导电性粉末和陶瓷原料(颗粒或粉末)的混合物的烧结体。连接部件与构成网格电极的线接触之外,还经由烧结导电体而与网格电极接触。因此,连接部件与网格电极的实际接触面积与现有技术相比变大。由此,连接部件与网格电极之间的电阻值与现有技术相比变低,可抑制在使从外部通电部件经由连接部件流向网格电极时的连接部件的发热。

在本发明的晶片载置台中,上述网格电极还可以是被施加高频电压的RF电极。在对网格电极施加高频电压的情况下,连接部件自身因从外部通电部件经由连接部件流向网格电极的高频电流而容易发热,但由于如上所述地,连接部件与网格电极之间的电阻值与现有技术相比变低,所以可抑制连接部件自身的发热。

在本发明的晶片载置台中,也可以为,上述网格开口部是一边的长度为0.3mm以上且1mm以下的方形,上述导电性粉末的粒径为1μm以上且10μm以下。

在本发明的晶片载置台中,上述导电性粉末优选是与上述网格电极相同材料的粉末。这样,由于烧结导电体与网格电极的热膨胀系数为接近的值,所以能够防止陶瓷部件因热应力而产生裂缝。此外,导电性粉末与网格电极的热膨胀系数优选为接近陶瓷部件的热膨胀系数的值。

本发明的晶片载置台的制法的特征在于,包括以下各工序:

(a)在作为陶瓷成形体或陶瓷烧成体的基体上配置网格电极,并在位于上述网格电极中的预定区域的网格开口部放入导电性粉末;

(b)在上述网格电极的上述预定区域之上配置导电性的连接部件;

(c)在上述基体上以覆盖上述网格电极及上述连接部件的方式层叠陶瓷原料,从而成为层叠体;

(d)热压烧成上述层叠体将上述基体及上述陶瓷原料一体化,从而成为陶瓷部件;以及

(e)以从上述陶瓷部件中的与上述晶片载置面相反一侧的面到达上述连接部件的方式开孔,将外部通电部件插入上述孔中,并将上述外部通电部件接合于上述连接部件的露出面。

根据该晶片载置台的制法,能够比较容易地制作上述的本发明的晶片载置台。

附图说明

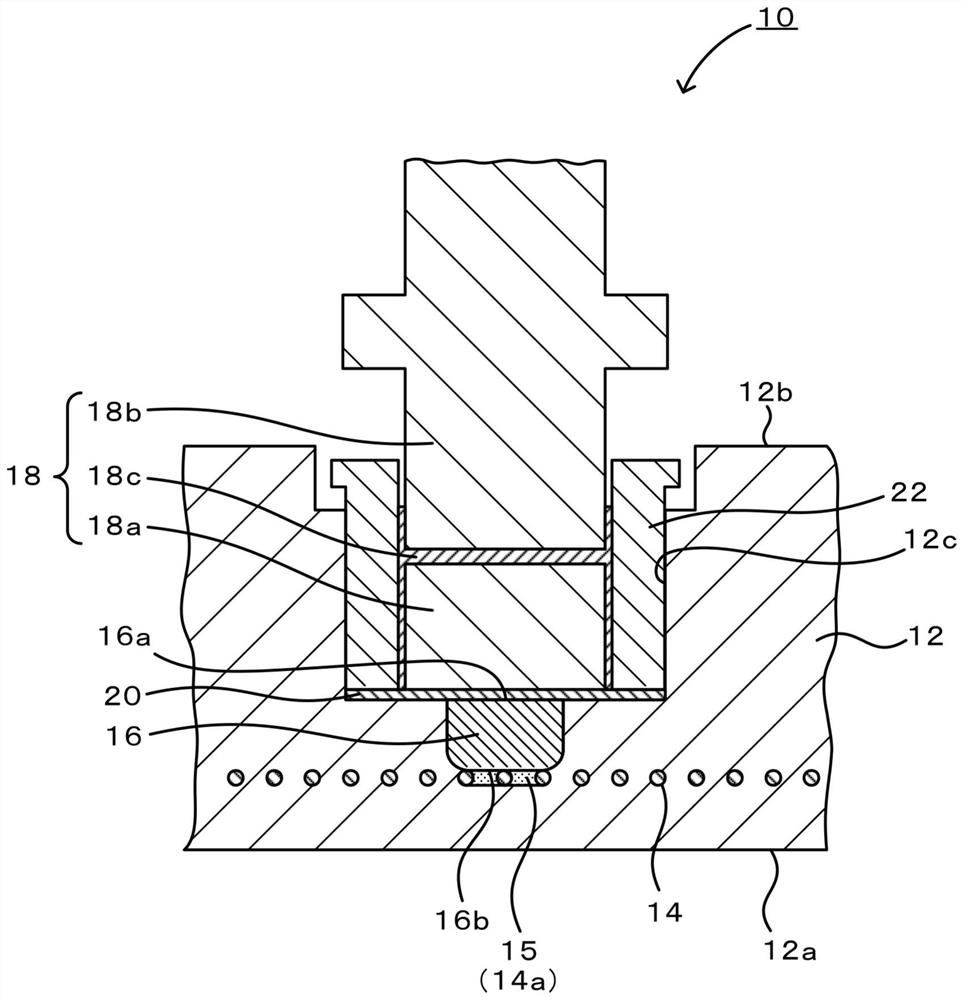

图1是晶片载置台10的主要部分的纵剖视图。

图2是网格电极14的局部俯视图。

图3是晶片载置台10的制造工序图。

图4是第一参考例的主要部分的纵剖视图。

图5是第二参考例的主要部分的纵剖视图。

图6是第三参考例的主要部分的纵剖视图。

具体实施方式

接下来,以下说明作为本发明优选的一个实施方式的晶片载置台10。图1是晶片载置台10的主要部分的纵剖视图,图2是网格电极14的局部俯视图。

晶片载置台10是为了载置实施蚀刻、CVD等处理的晶片而使用的装置,设置在未图示的真空腔内。该晶片载置台10具备陶瓷部件12、网格电极14、烧结导电体15、连接部件16、外部通电部件18、以及导向部件22。

陶瓷部件12形成为圆板状,一侧的面成为用于载置晶片的晶片载置面12a。此外,图1中,晶片载置面12a朝下,但实际上在使用晶片载置台10时,晶片载置面12a朝上。作为该陶瓷部件12的材质,例如优选氮化铝、氧化铝,碳化硅、氮化硅等。并且,在陶瓷部件12的与晶片载置面12a相反的一侧的面12b形成有有底筒状的孔12c。陶瓷部件12也可以是例如直径为150~500mm,厚度为0.5~30mm。孔12c也可以是例如直径为5~15mm,深度为5~25mm。

网格电极14是埋设在陶瓷部件12中的RF电极(被施加高频电压的电极),且是沿晶片载置面12a设置的圆形的金属网。作为该网格电极14的材质,例如优选钨、钼、铌、钽、铂以及它们的合金、它们的化合物等。图2所示的网格电极14的网孔(方形的网格开口部14a的一边的长度)A、网格(纵线及横线1英寸间的网眼个数)M、线径d、网格开口率ε没有特别限定,但网孔A优选为0.3mm以上且1mm以下,网格M优选为10以上且100以下,线径d优选为0.1mm以上且1mm以下,网格开口率ε优选为40%以上且60%以下。

烧结导电体15是包含导电性粉末P和陶瓷原料(颗粒或粉末)的混合物的烧结体,填充在位于网格电极14中的与连接部件16对置的区域的网格开口部14a。烧结导电体15与构成网格电极14的线的侧面接触,并且与连接部件16的水平面16b接触。烧结导电体15所含的导电性粉末P的材质优选热膨胀系数接近网格电极14,更优选材质与网格电极14的材质相同。并且,网格电极14及导电性粉末P的热膨胀系数优选接近陶瓷部件12的热膨胀系数。例如,在陶瓷部件12的材质为氮化铝的情况下,网格电极14及导电性粉末P的材质优选为钼、钨、碳化钼等钼化合物或者碳化钨等钨化合物。在陶瓷部件12的材质为氧化铝的情况下,网格电极14及导电性粉末P的材质优选为铌或碳化铌等铌化合物。

连接部件16是以从陶瓷部件12中的孔12c的底面到达网格电极14的方式埋设的圆柱状的金属部件。该连接部件16可以使用块状金属,也可以使用使金属粉末烧结而成的部件。连接部件16的材质优选接近陶瓷部件12的热膨胀系数的材质、或者接近网格电极14及导电性粉末P的热膨胀系数的材质。连接部件16的材质优选与网格电极14及导电性粉末P的材质相同。连接部件16中的露出到孔12c的底面的露出面16a与孔12c的底面为同一面。连接部件16的直径优选为2~5mm,高度优选为1~5mm。

外部通电部件18具备:第一部18a,其经由导电性的接合层20而与连接部件16接合;和第二部18b,其经由导电性的中间接合部18c而与该第一部18a中的与连接部件16的接合面相反一侧的面接合。考虑在等离子体气氛、腐蚀气体气氛下使用,第二部18b由耐氧化性较高的金属构成。但是,耐氧化性较高的金属一般热膨胀系数较大,因而若直接与连接部件16接合,则接合强度因两者的热膨胀差而降低。因此,第二部18b经由由热膨胀系数接近连接部件16的热膨胀系数的金属构成的第一部18a而与陶瓷部件12接合。这样的金属在大多情况下耐氧化性不充分。因此,第一部18a成为如下结构,即利用由耐氧化性较高的金属构成的导向部件22来包围周围,从而不会与等离子体气氛、腐蚀气体气氛直接接触。作为第二部18b的材质,优选纯镍、镍基耐热合金、金、铂、银以及它们的合金等。作为第一部18a的材质,优选钼、钨、钼-钨合金、钨-铜-镍合金、科瓦铁镍钴合金等。接合层20利用钎料来接合。作为钎料,优选金属钎料,例如优选Au-Ni钎料、Al钎料、Ag钎料等。接合层20将包含连接部件16的露出面16a的孔12c的底面与第一部18a的端面接合。外部通电部件18的中间接合部18c将第一部18a与第二部18b接合,并且填埋导向部件22的内周面与第一部18a的外周面整面或其一部分之间的间隙、导向部件22的内周面与第二部18b的外周面的一部分之间的间隙。因此,第一部18a由中间接合部18c遮断与周围气氛的接触。此外,中间接合部18c也能够使用与接合层20相同的材质。第一部18a也可以为直径3~6mm,高度2~5mm,第二部18b也可以为直径3~6mm,高度任意。

导向部件22是包围外部通电部件18中的至少第一部18a的周围的圆筒状的部件,由耐氧化性比第一部18a的耐氧化性高的材质形成。该导向部件22的内径比第一部18a及第二部18b的外径大,外径(除凸缘之外)比孔12c的直径小,高度比第一部18a的高度高。导向部件22中的面向孔12c的底面的端面经由接合层20而与连接部件16、外部通电部件18以及陶瓷部件12接合。导向部件22的材质能够使用作为外部通电部件18的第二部18b的材质而示例的材质。

接下来,说明晶片载置台10的使用例。在未图示的腔内,以晶片载置面12a朝上的方式配置晶片载置台10,并在晶片载置面12a载置晶片。经由外部通电部件18、接合层20以及连接部件16对网格电极14施加未图示的RF电源的交流高频电压,来使由设置于腔内的上方的未图示的对置水平电极和埋设在晶片载置台10中的网格电极14构成的平行平板电极间产生等离子体,并利用该等离子体来对晶片实施CVD成膜或者实施蚀刻。

接下来,以下基于图3的制造工序图来说明晶片载置台10的制造例。首先,在将陶瓷原料(颗粒或粉末)冲压成形为圆板而成的陶瓷成形体亦即基体112的上表面配置网格电极14,并在位于网格电极14中的预定区域14p的网格开口部14a内放入导电性粉末P(参照图3的(a))。预定区域14p是配置连接部件16的区域。此外,基体112的下表面在加工后成为晶片载置台10的顶面,最终成为晶片载置面12a侧。接下来,在网格电极14的预定区域14p之上配置圆柱状的连接部件16(参照图3的(b))。由此,连接部件16成为与网格电极14及导电性粉末P接触的状态。接下来,在基体112上以覆盖网格电极14及连接部件16的方式层叠陶瓷原料(颗粒或粉末)并进行冲压成形,从而成为层叠体114(参照图3的(c))。层叠体114包含基体112和层叠在其上的陶瓷成形体113。接下来,将层叠体114进行热压烧成将基体112及陶瓷成形体113一体化,从而成为陶瓷部件12(参照图3的(d))。由此,放入位于预定区域14p的网格开口部14a的导电性粉末P以与陶瓷原料混合的状态进行烧结,成为烧结导电体15。接下来,以从陶瓷部件12中的与晶片载置面12a相反的一侧的面12b到达连接部件16的方式开孔12c,将外部通电部件18的构成部件插入孔12c中,并将外部通电部件18接合于连接部件16的露出面16a,从而得到晶片载置台10(参照图3的(e))。在开孔12c时,以孔12c的底面与连接部件16的露出面16a为同一面的方式进行加工。在将外部通电部件18的构成部件接合于连接部件16的露出面16a时,在孔12c的底面敷设成为接合层20的钎料,并在其上依次堆积外部通电部件18的第一部18a、成为中间接合部18c的钎料以及外部通电部件18的第二部18b,并且在其周围配置导向部件22,之后在非氧化性条件下进行加热使钎料熔融,之后进行固化,由此得到图1所示的晶片载置台10。非氧化性条件是指真空下或者非氧化性气氛(例如氩气气氛、氮气气氛等惰性气氛)下。根据以上的制法,能够比较容易地制造晶片载置台10。

在以上说明的本实施方式的晶片载置台10中,在位于网格电极14中的与连接部件16对置的区域的网格开口部14a填充有烧结导电体15。连接部件16与构成网格电极14的线接触之外,还经由烧结导电体15而与网格电极14接触。因此,连接部件16与网格电极14的实际接触面积与没有烧结导电体15的情况变大。由此,连接部件16与网格电极14之间的电阻值与没有烧结导电体15的情况相比变低,可抑制在使电流从外部通电部件18经由连接部件16流向网格电极14时的连接部件16的发热。因此,连接部件16难以成为热点,改善晶片的均热性。

尤其,在对网格电极14施加高频电压的情况下,连接部件16自身因从外部通电部件18经由连接部件16流向网格电极14的高频电流而容易发热,但由于如上所述地连接部件16与网格电极14之间的电阻值变低,所以可抑制连接部件16自身的发热。

并且,优选为,网格开口部14a是一边的长度为0.3mm以上且1mm以下的方形,导电性粉末P的粒径为1μm以上且10μm以下。

另外,导电性粉末P优选为与网格电极14相同的材料的粉末。这样,烧结导电体15与网格电极14的热膨胀系数一致,因而能够防止陶瓷部件12因热应力而产生裂缝。

然后,发明人也研究了采用以下各构造来代替在预定区域14p的网格开口部14a填充导电性粉末P来成为烧结导电体15:在网格电极14的预定区域14p之上配置金属箔30并在该金属箔30载置连接部件16的构造(第一参考例,参照图4);在位于网格电极14的预定区域14p的网格开口部嵌入金属箔32的构造(第二参考例,参照图5);在位于网格电极14的预定区域14p的网格开口部插入从连接部件16的下表面突出的凸部16p的构造(第三参考例,参照图6)。但是,在图4的构造中,在用热压烧成来制成陶瓷部件12时,金属箔30的边缘为起点而产生了裂缝。在图5的构造中,埋设在陶瓷部件12中的金属箔32与连接部件16的接触不充分,无法抑制连接部件16的发热。在图6的构造中,在用热压烧成来制成陶瓷部件12时,插入网格开口部的凸部16p的前端为起点而产生了裂缝。上述的实施方式的烧结导电体15在热压烧成时是导电性粉末、陶瓷原料(颗粒或粉末)的混合物,具有流动性,这与金属箔32不同,因而认为抑制了裂缝的产生。

此外,本发明不限定于上述的任一实施方式,当然在属于本发明的技术范围的情况下能够以各种方式实施。

例如,在上述的实施方式中,在陶瓷部件12中埋设有作为RF电极的网格电极14,但代替地,可以埋设用于将晶片吸附于晶片载置面12a的静电电极,并且也可以埋设用于加热晶片的加热电极(电阻发热体)。

在上述的实施方式中,将网格电极14用作RF电极,但可以将网格电极14用作静电电极,也可以将其用作加热电极(电阻发热体)。

在上述的实施方式中,晶片载置面12a可以呈平面,但也可以呈通过压花加工等而形成有多个突起的面。

在上述的实施方式中,还可以在晶片载置台10的与晶片载置面12a相反一侧的面12b,使与陶瓷部件12相同材质的筒状的轴与陶瓷部件12一体化。在该情况下,在轴的中空内部配置外部通电部件18等。并且,在将轴与陶瓷部件12一体化后,安装外部通电部件18。在制造轴时,例如,使用金属模具并用CIP成形陶瓷原料(颗粒或粉末),在常压炉中以预定温度进行烧成,并在烧成后,加工成为预定尺寸即可。并且,当将轴与陶瓷部件12一体化时,例如,使轴的端面对接于陶瓷部件12的面12b,升温至预定温度来接合两者,进行一体化即可。

在上述的实施方式中,在晶片载置台10的制法中,使用陶瓷成形体作为基体112,但可以使用陶瓷烧结体作为基体112,也可以使用陶瓷烧锻体。

在上述的实施方式中,示出图3的制造工序的例子,但不特别限定于此。例如,也可以在陶瓷生片的上表面配置网格电极14,在网格开口部14a放入导电性粉末P,并在其上配置连接部件16,再载置其它陶瓷生片并压缩,来制成层叠体,对该层叠体进行常压烧成。在该情况,在压缩时,在网格开口部14a内,导电性粉末P成为与陶瓷生片中的陶瓷原料(颗粒或粉末)混合的状态,利用之后的常压烧成而成为烧结导电体。

本申请主张于2019年7月1日申请的日本专利申请第2019-122749号作为优先权主张的基础,并通过引用将其全部内容包括在本说明书中。

- 晶片载置台及其制法

- 晶片载置台及其制法