一种耐基板翘曲的倒装LED芯片及其制备方法

文献发布时间:2023-06-19 09:35:27

技术领域

本发明涉及光电子制造技术领域,尤其涉及一种耐基板翘曲的倒装LED芯片及其制备方法。

背景技术

倒装LED芯片是一种新型LED芯片,其散热性能和光效都比普通正装LED芯片优异,因此广泛应用于各类照明产品,低阶应用如球泡灯、吸顶灯,高阶应用如车灯、路灯等。。倒装LED芯片的封装于传统正装LED芯片相差较大,实现有效的实现封装是倒装LED芯片产业化的关键内容。

倒装LED芯片对于封装基板的平整度要求高,若基板不平,容易使得芯片受损(参图1,由于基板翘曲,应力大,导致钝化层开裂);同时,基板翘曲也会造成漏电,电压不良等缺陷,使得LED芯片出现异常不良,据统计,采用普通基板时,现有的异常不良率(VF<5.8V)时可达到15%以上,甚至可达到65%;此外,基板翘曲也容易造成焊接良率低,漏电、死灯的问题。因此,如何加大倒装LED芯片对于不良封装基板的制程窗口,是本领域亟待克服的问题。

发明内容

本发明所要解决的技术问题在于,提供一种耐基板翘曲的倒装LED芯片,其耐弯曲能力强,可有效降低封装异常不良率。

本发明还要解决的技术问题在于,提供一种耐基板翘曲的倒装LED芯片的制备方法。

为了解决上述技术问题,本发明提供了一种耐基板翘曲的倒装LED芯片,其包括应力缓冲层、衬底、发光结构、一次电极结构、钝化层和二次电极结构;

所述发光结构设于所述衬底的正面,所述一次电极结构设于所述发光结构上,所述钝化层设于所述一次电极结构上,所述二次电极结构设于所述钝化层上;所述二次电极结构贯穿所述钝化层与所述一次电极结构连接;

所述应力缓冲层设于所述衬底的背面。

作为上述技术方案的改进,所述应力缓冲层由AlN或BN制成,其厚度为0.3~6μm。

作为上述技术方案的改进,所述二次电极结构包括依次设于所述钝化层上的连接层、阻挡层、弹性层和粘附层。

作为上述技术方案的改进,所述连接层由Cr或Ti制成,其厚度为2~50nm。

作为上述技术方案的改进,所述阻挡层包括第一阻挡层、第二阻挡层和第三阻挡层,所述第二阻挡层由Ni制成,所述第一阻挡层和第三阻挡层由Au、Pt、Ti中的一种制成。

作为上述技术方案的改进,所述第一阻挡层和所述第三阻挡层的厚度为100~500nm,所述第二阻挡层的厚度为50~200nm。

作为上述技术方案的改进,所述阻挡层依次包括Au层、Ni层和Au层;或

所述阻挡层依次包括Ti层、Ni层和Ti层;或

所述阻挡层依次包括Au层、Ni层和Pt层。

作为上述技术方案的改进,所述弹性层为一层AuSn合金层;或

所述弹性层包括多层Au层、Sn层和AuSn合金层;

所述AuSn合金层中Sn含量≥80wt%,所述弹性层的厚度≥2.5μm;

所述粘附层由Au或Pt制成,其厚度为10~100nm。

作为上述技术方案的改进,所述衬底为蓝宝石,所述二次电极结构平行于所述衬底的易轴方向。

相应的,本发明还公开了一种上述的耐基板翘曲的倒装LED芯片的制备方法,其包括:

(1)提供衬底;

(2)在所述衬底的正面依次形成发光结构、一次电极结构、钝化层和二次电极结构,得到半成品;

(3)对所述衬底的背面进行研磨,抛光,并在研磨抛光后的衬底的背面形成应力缓冲层,即得到耐基板翘曲的倒装LED芯片成品。

实施本发明,具有如下有益效果:

本发明的倒装LED芯片,在衬底的背面设置了应力缓冲层,其可提供与封装应力方向相反的应力,有效降低封装翘曲,使得封装基板平整度高,焊接良率提升,从而提升了倒装LED芯片的整体良率。并且,本发明的二次电极包括连接层、阻挡层、弹性层和粘附层,这种结构的弹性更强,保护芯片主体不受基板应力拉扯,加大了倒装LED芯片对于不良封装基板的制程窗口。

附图说明

图1是现有倒装LED芯片封装缺陷图;

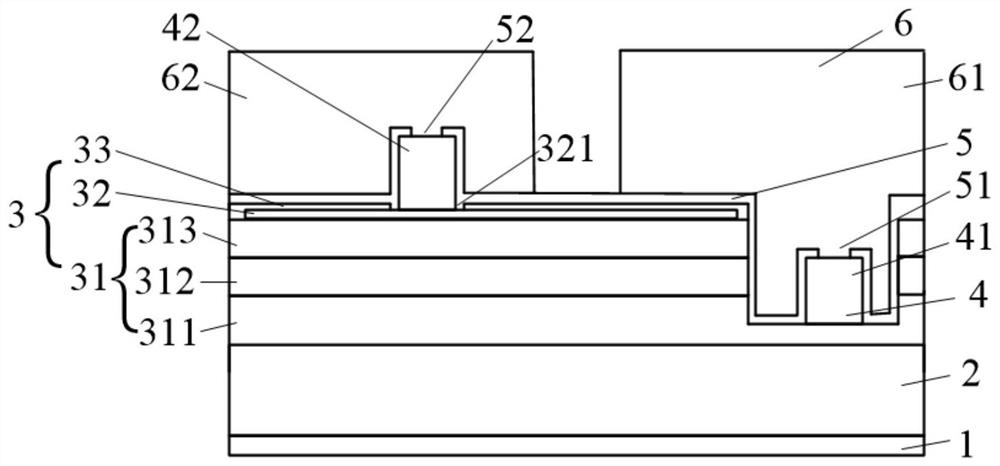

图2是本发明一种耐基板翘曲的倒装LED芯片结构示意图;

图3是蓝宝石衬底易轴方向示意图(衬底方向);

图4是蓝宝石衬底易轴方向示意图(晶体方向,蓝宝石晶体c轴俯视);

图5是本发明第一二次电极的结构示意图;

图6是本发明第二二次电极的结构示意图;

图7是本发明一种耐基板翘曲的倒装LED芯片的制备方法流程图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作进一步地详细描述。仅此声明,本发明在文中出现或即将出现的上、下、左、右、前、后、内、外等方位用词,仅以本发明的附图为基准,其并不是对本发明的具体限定。

参见图2,本发明提供一种耐基板翘曲的倒装LED芯片,其包括应力缓冲层1、衬底2、发光结构3、一次电极结构4、钝化层5和二次电极结构6;其中,应力缓冲层1设置在衬底2的背面,其可提供与封装应力方向相反的应力,从而起到缓解封装基板翘曲的作用。

具体的,应力缓冲层1可为AlN层、BN层,但不限于此。应力缓冲层1的厚度为0.3~6μm,当其厚度<0.3μm时,其提供的应力较小,对基板翘曲的矫正作用小;当其厚度>6μm时,则提供应力过大,容易造成反向翘曲。优选的,应力缓冲层的厚度为1~4μm,示例性地可为1μm、1.5μm、1.8μm、2.4μm、2.6μm、3μm、3.5μm,但不限于此。

需要说明的是,在倒装LED芯片焊接时,焊接温度可高达300℃,由于蓝宝石和GaN(发光结构)的热膨胀系数不同【蓝宝石的膨胀系数是(6~7)×10

还需要说明的是,现有技术中,往往将AlN沉积在衬底正面,以起到缓冲作用,其主要的作用机理是AlN可缓解衬底与GaN层之间的晶格失配,从而减少位错密度,减少晶内压力。这与本实施例中的作用机理是不同的。

衬底2可为蓝宝石、硅、金刚石,但不限于此;优选的,选用蓝宝石作为衬底2。

发光结构3包括外延层31、透明导电层32、反射层33和裸露区。外延层31包括依次设置在衬底2上的第一半导体层311、发光层312和第二半导体层312。透明导电层32设置在第二半导体层313上,反射层33设置在透明导电层32上,在反射层32上设置孔洞321,外延层2整体刻蚀形成裸露区。

一次电极结构4包括第一电极41和第二电极42,第一电极41设置在裸露区内,并与第一半导体层311电连接,第二电极42设置在反射层33上,并通过孔洞321与透明导电层32电连接,进而实现与第二半导体层313电连接。

钝化层5设置在反射层33、一次电极结构4和裸露区表面,并且在第一电极41处设有第一镂空孔51、在第二电极42处设置第二镂空孔52。

二次电极结构6包括第一二次电极61和第二二次电极62,其中,第一二次电极61通过第一镂空孔51与第一电极41电连接,第二二次电极62通过第二镂空孔52与第二电极42电连接。第一二次电极61与第二二次电极62高度相同,且面积相同。为了缓解晶片翘曲,二次电极结构6应分布在平行于蓝宝石衬底的易轴方向(参考图3、图4),避免受晶格方向的弯曲。二次电极6可通过Ebeam蒸镀或Thermo蒸镀方式形成,但不限于此。

进一步的,参考图5、图6,第一二次电极61和第二二次电极62均包括依次设置在钝化层5上的连接层611/621、阻挡层、弹性层612/622和粘附层613/623。

其中,连接层611/621用于连接一次电极结构4和二次电极结构5,其具体材料可选用Cr和/或Ti,但不限于此;其可为单层Cr层、单层Ti层,也可为多层Cr层和/或Ti层叠加。连接层611/612的厚度为2~50nm,当其厚度<2nm时,粘接作用太差,当其厚度>50nm时,容易造成金属断层。优选的,连接层611/612的厚度为10~30nm,示例性地可为10nm、13nm、15nm、19nm、20nm、22nm、27nm、29nm,但不限于此。

其中,阻挡层可有效防止锡金属扩散,使其与基版结合,形成共晶,增加黏附力。具体的,阻挡层为单层结构或多层叠层结构;当其为单层结构时,其材料为Ni;当其为叠层结构时,其中间层为Ni,两边叠层可为的材料为面心立方或六方最密堆积金属,如Au、Pt、Ti等,但不限于此。其中,Ni金属易与其他金属形成融合,阻挡金属扩散。面心立方或六方最密堆积金属的单界面堆积原子数最高,可有效地阻挡金属扩散。

具体的,阻挡层依次包括第一阻挡层614/624,第二阻挡层615/625和第三阻挡层616/626;其中,第一阻挡层614/624和第三阻挡层616/626的材料为Au和/或Pt和/或Ti,第二阻挡层615/625的材料为Ni。第一阻挡层614/624的厚度为100~500nm,第二阻挡层615/625的厚度为50~200nm,第三阻挡层616/626的厚度为100~500nm。若第一阻挡层和第三阻挡层的厚度>500nm,则容易造成电压过高,影响倒装LED芯片能效。

更具体的,在本实施例之中,阻挡层依次包括Au层、Ni层和Au层;在本发明的另一个实施例之中,阻挡层依次包括Ti层、Ni层和Ti层;在本发明的又一实施例之中,阻挡层依次包括Au层、Ni层和Pt层。

弹性层612/622的材料为AuSn合金、Au、Sn中的一种或多种;其中,AuSn合金中Sn含量≥80%。弹性层612/622为单层结构或叠层结构,例如为AuSn合金层单层结构,或多层Au、Sn、AuSn合金层堆叠的结构;弹性层的总厚度≥2.5μm。

粘附层613/623的材料为Au或Pt,但不限于此;其厚度为10~100nm,若其厚度<10nm,则其无法有效遮挡弹性层;若其厚度>100nm,则会影响后期封装焊接。优选的,粘附层613/623的厚度为30~80nm,示例性的可为32nm、44nm、49nm、53nm、66nm、72nm,但不限于此。

相应的,参见图7,本发明还提供了一种上述耐基板翘曲的倒装LED芯片的制备方法,其包括以下步骤:

S1:提供衬底;

S2:在衬底的正面依次形成发光结构、一次电极结构、钝化层和二次电极结构,得到半成品;

具体的,S2包括:

S21:在衬底正面形成外延层;

其中,外延层31包括第一半导体层311、发光层312和第二半导体层313;具体的,第一半导体层311为N型氮化镓层,第二半导体层313为P型半导体层;但不限于此。

S22:对外延层进行光刻刻蚀,形成裸露区;

具体的,通过光刻刻蚀工艺在外延层31上形成贯穿至第一半导体层311的裸露区域。在刻蚀时,选取衬底的易轴方向进行刻蚀。

S23:在外延层上形成透明导电层;

具体的,在第二半导体层313上形成透明导电层32。

S24:在透明导电层上形成反射层;

具体的,在形成反射层后,还需要对反射层进行光刻刻蚀,形成孔洞321。

S25:在所述反射层和裸露区域上形成一次电极结构;

具体的,采用电子束蒸镀、热蒸镀或磁控溅射工艺形成第一电极41和第二电极41。其中,第一电极41设置在裸露区内,并与第一半导体层311电连接,第二电极42设置在反射层33上,并通过孔洞321与透明导电层32电连接,进而实现与第二半导体层313电连接。

S25:形成钝化层,并对钝化层进行光刻刻蚀,暴露出第一电极和第二电极;

具体的,钝化层5设置在反射层33、一次电极结构4和裸露区表面;并通过光刻刻蚀工艺在第一电极41处形成第一镂空孔51、在第二电极42处形成第二镂空孔52。

S26:在钝化层上形成二次电极结构,得到半成品;

具体的,可通过Ebeam蒸镀或Thermo蒸镀方式形成二次电极结构。

S3:对衬底的背面进行研磨,抛光,并在研磨抛光后的衬底的背面形成应力缓冲层,即得到耐基板翘曲的倒装LED芯片成品。

具体的,S3包括:

S31:对半成品的衬底的背面进行研磨,抛光;

S32:在研磨抛光后的衬底的背面形成应力缓冲层,即得到耐基板翘曲的倒装LED芯片成品;

具体的,应力缓冲层1的形成温度为500~800℃。在此温度形成的应力缓冲层1即可在封装过程中提供较大的张应力,防止翘曲。

需要说明的是,传统的设置在衬底正面的AlN层,为了发挥其降低位错的作用,其形成温度往往在900℃以上。这是因为形成温度较低时,AlN的晶体成核性差,晶体趋向性差,无法有效降低位错密度。

将本发明之中的倒装LED芯片与常规的倒装LED芯片进行封装实验,其实验结果如下表所示:

由表中可以看出,当采用耐翘曲型基板(D6018KCDN)时,本实施例的倒装LED芯片与常规的倒装LED芯片差别不大。但采用普通基板(D6018HJN),本实施例的正品率为100%,而常规倒装LED芯片仅为82.99%,说明本实施例中的倒装LED芯片耐翘曲能力强。

以上所述是发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。

- 一种耐基板翘曲的倒装LED芯片及其制备方法

- 一种耐基板翘曲的倒装LED芯片