操作方法以及感测放大器

文献发布时间:2023-06-19 09:57:26

技术领域

本发明有关于一种非挥发性内存的感测放大器,特别有关于一种用以克服制程飘移的非理想效应且允许操作于更高速度的具有偏移消除的感测放大器。

背景技术

感测放大器在本领域是众所皆知的,并且通常用于许多类型的集成电路中,例如具有多个列以及多个栏之内存单元的随机存取半导体存储装置,用以侦测以及放大由内存单元所产生的信号。

为了存取特定内存单元组(即,位于内存数组中的字(word)),所欲耦接之该内存单元组的列地址以及栏地址必须先被译码。举例来说,在一静态随机存取内存数组中,数组中的每一内存单元耦接至两条位线,且该两条位线互为反相。这两条位线称之为“真位线”以及“补位线”,共同组成一栏,其地址必须先被译码后才能将状态读取或写入耦接至该栏之内存单元。

然而,锁存型感测放大器之输入级的不匹配将决定能够被侦测的敏感度以及最小的电压差。因此,有必要最小化锁存型感测放大器的不匹配以增进锁存型感测放大器的效能。

发明内容

本发明在此提出了一种用于非挥发性内存之感测放大器,感测放大器包括多个交叉耦合锁存,用以交替地且并列地操作于归零状态以及感测状态。因此,每一交叉耦合锁存在进入感测状态前就会提早先完成归零状态,使得侦测数据的速度得以更快。

根据本发明之一实施例,一种适用于一感测放大器所述的操作方法,其中上述感测放大器包括一第一交叉耦合锁存以及一第二交叉耦合锁存,其中上述第一交叉耦合锁存以及上述第二交叉耦合锁存之每一个包括一第一晶体管对以及耦接至上述第一晶体管对之个别的栅极端之一耦合电容对。上述操作方法包括在一第一阶段中,对上述第一交叉耦合锁存之上述耦合电容对充电而达成归零的目的,且提供一第一组输入电压至上述第二交叉耦合锁存;以及在紧接着上述第一阶段之一第二阶段中,对上述耦合电容对放电以消除(cancel)上述第一晶体管对之不匹配,且比较提供至上述第二交叉耦合锁存之上述第一组输入电压而产生一第一组输出电压。

根据本发明之一实施例,一种感测放大器包括一第一交叉耦合锁存、一第二交叉耦合锁存、一输入开关组以及一输出开关组。上述第一交叉耦合锁存操作于一充电状态以及一放电状态。上述第二交叉耦合锁存对应上述第一交叉耦合锁存操作于上述充电状态而操作于一取样状态,对应上述第一交叉耦合锁存操作于上述放电状态而操作于一比较状态。上述输入开关组对应上述第二交叉耦合锁存操作于上述取样状态以及上述比较状态,而将一输入电压组提供至上述第二交叉耦合锁存。上述输出开关组对应上述第二交叉耦合锁存操作于上述比较状态,而耦接至上述第二交叉耦合锁存。

附图说明

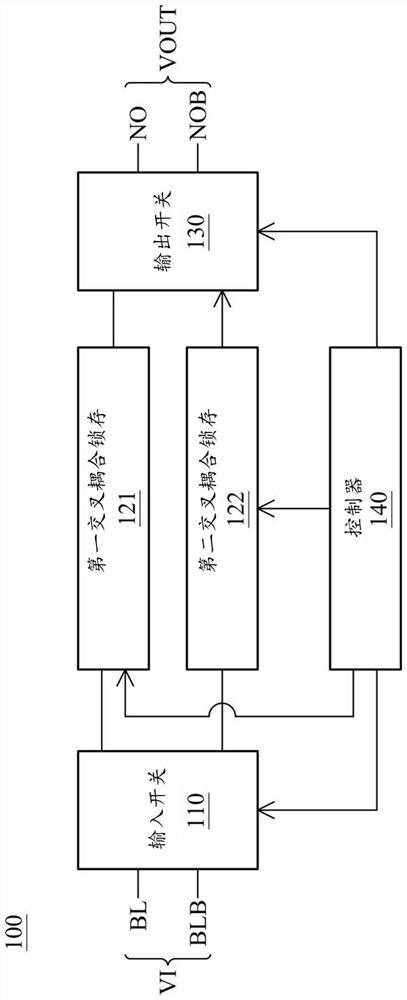

图1显示根据本发明之一实施例所述的感测放大器的方块图;

图2显示根据本发明之一实施例所述的感测放大器的电路图;

图3显示根据本发明之一实施例所述的感测放大器的时序图;

图4显示根据本发明之一实施例所述之交叉耦合锁存的电路图;

图5显示根据本发明之另一实施例所述之交叉耦合锁存的电路图;以及

图6显示根据本发明之一实施例所述之交叉耦合锁存之操作的流程图。

具体实施方式

以下说明为本发明的实施例。其目的是要举例说明本发明一般性的原则,不应视为本发明的限制,本发明之范围当以申请专利范围所界定者为准。

图1显示根据本发明之一实施例所述的感测放大器的方块图。如图1所示,感测放大器100包括一组输入开关110、第一交叉耦合锁存121、第二交叉耦合锁存122、一组输出开关130以及控制器140。根据本发明之一实施例,第一交叉耦合锁存121以及第二交叉耦合锁存122具有相同的电路结构。

输入开关110用以将来自位线BL以及反向位线BLB之一组输入电压VI提供至第一交叉耦合锁存121或第二交叉耦合锁存122。第一交叉耦合锁存121或第二交叉耦合锁存122感测提供之输入电压VI,而产生一组输出电压VOUT。输出开关130将来自第一交叉耦合锁存121或第二交叉耦合锁存122之输出电压VOUT,提供至输出节点NO以及反向输出节点NOB。

控制器140控制输入开关110而将输入电压VI提供至第一交叉耦合锁存121或第二交叉耦合锁存122,以及控制输出开关130输出由第一交叉耦合锁存121或第二交叉耦合锁存122所产生之输出电压VOUT。此外,控制器140更控制第一交叉耦合锁存121以及第二交叉耦合锁存122依序地且重复地操作于充电状态、放电状态、取样状态以及比较状态。当第一交叉耦合锁存121操作于充电状态以及放电状态时,第二交叉耦合锁存122分别操作于采样状态以及比较状态,反之亦然。

为了简化说明,以下将只针对输入开关110、第一交叉耦合锁存121、第二交叉耦合锁存122以及输出开关130之操作。根据本发明之其他实施例,感测放大器110可包括复数交叉耦合锁存,在此仅以两个交叉耦合锁存作为说明解释。

图2显示根据本发明之一实施例所述的感测放大器的电路图。如图2所示,感测放大器200包括第一输入开关SI1、第一反向输入开关SIB1、第二输入开关SI2、第二反向输入开关SIB2、第一交叉耦合锁存221、第二交叉耦合锁存222、第一输出开关SO1、第一反向输出开关SOB1、第二输出开关SO2以及第二反向输出开关SOB2。

将感测放大器200与图1之感测放大器100相比,输入开关SI1、第一反向输入开关SIB1、第二输入开关SI2以及第二反向输入开关SIB2对应至图1的输入开关110,第一输出开关SO1、第一反向输出开关SOB1、第二输出开关SO2以及第二反向输出开关SOB2对应至图1的输出开关130,第一交叉耦合锁存221对应至第一交叉耦合锁存121,第二交叉耦合锁存222对应至第二交叉耦合锁存122。

图3显示根据本发明之一实施例所述的感测放大器的时序图。如图3所示,第一阶段P1、第二阶段P2、第三阶段P3、第四阶段P4、第五阶段P5以及第六阶段P6一个接一个。第一交叉耦合锁存221以及第二交叉耦合锁存222依序地且重复地操作于充电状态SCH、放电状态SDCH、取样状态SSMP以及比较状态SCMP,其中第一交叉耦合锁存221以及第二交叉耦合锁存222系必列执行。

根据本发明之一实施例,如图3所示,当第一交叉耦合锁存221在第三阶段P3操作于取样状态SSMP时,第二交叉耦合锁存222操作于充电状态SCH。根据本发明之另一实施例,当第一交叉耦合锁存221在第四阶段P4操作于比较状态SCMP时,第二交叉耦合锁存222操作于放电状态SDCH。在第五阶段P5以及第六阶段P6时,第一交叉耦合锁存221操作于充电状态SCH以及放电状态SDCH,而第二交叉耦合锁存222操作于取样状态SSMP以及比较状态SCMP。

在充电状态SCH以及放电状态SDCH时,操作第一交叉耦合锁存221或第二交叉耦合锁存222而将第一交叉耦合锁存221或第二交叉耦合锁存222之不匹配归零。在取样状态SSMP以及比较状态SCMP时,操作第一交叉耦合锁存221或第二交叉耦合锁存222比较来自位线BL以及反向位线BLB之输入电压VI,而于输出节点NO以及反向输出节点NOB产生输出电压VOUT。

根据本发明之一实施例,充电状态SCH以及放电状态SDCH为归零状态。根据本发明之一实施例,取样状态SSMP以及比较状态SCMP为侦测状态。根据本发明之一实施例,当第一交叉耦合锁存221以及第二交叉耦合锁存222之一个操作于归零状态以归零不匹配时,另一个则操作于感测状态以感测来自位线BL以及反向位线BLB之输入电压VI。由于第一交叉耦合锁存221以及第二交叉耦合锁存222之一个操作于归零状态时另一个操作于感测状态,因此感测放大器200能够连续地侦测来自于位线BL以及反向位线BLB的输入电压VI,而无须花费一段时间用以归零不匹配。

根据本发明之一实施例,图2的感测放大器200用于非挥发性内存。当非挥发性内存进行初始化时,第一交叉耦合锁存221可操作于充电状态SCH(对应第一阶段P1)以及放电状态SDCH(对应第二阶段P2)。因此,一旦非挥发性内存完成初始化时,第一交叉耦合锁存221以准备好进行取样以及比较来自位线BL以及反向位线BLB之输入电压VI,使得感测放大器200的速度可以更快。

图4显示根据本发明之一实施例所述之交叉耦合锁存的电路图。如图4所示,交叉耦合锁存400系为图2的第一交叉耦合锁存221以及第二交叉耦合锁存222之一实施例。图4的输入开关SI以及反向输入开关SIB系分别对应至第一输入开关SI1以及第一反向输入开关SIB1,或分别对应至第二输入开关SI2以及第二反向输入开关SIB2。图4之输出开关SO以及反向输出开关SOB分别对应至第一输出开关SO1以及第一反向输出关SOB1,或分别对应至第二输出开关SO2以及第二反向输出关SOB2。

如图4所示,交叉耦合锁存400包括第一晶体管M1、第二晶体管M2、第一耦合电容CC1、第二耦合电容CC2、第三晶体管M3以及第四晶体管M4。第一晶体管M1、第二晶体管M2、第三晶体管M3以及第四晶体管M4形成交叉耦合锁存,第一耦合电容CC1与第二耦合电容CC2用以分别储存第一晶体管M1以及第二晶体管M2的临限电压。

第一晶体管M1包括栅极端、漏极端以及源极端,其中栅极端耦接至第一内部节点NI1、漏极端耦接至第三节点N3以及源极端耦接至第四节点N4。第二晶体管M2包括栅极端、漏极端以及源极端,其中栅极端耦接至第二内部节点NI2、漏极端耦接至第五节点N5以及源极端耦接至第四节点N4。

第一耦合电容CC1耦接于第一内部节点NI1以及第六节点N6,第二耦合电容CC2耦接于第二内部节点NI2以及第七节点N7。

第三晶体管M3包括栅极端、漏极端以及源极端,其中栅极端耦接至第六节点N6、漏极端耦接至第三节点N3以及源极端耦接至第八节点N8。第四晶体管M4包括栅极端、漏极端以及源极端,其中栅极端耦接至第七节点N7、漏极端耦接至第五节点N5以及源极端耦接至第八节点N8。

交叉耦合锁存400更包括供应电压开关SVDD、接地开关SGND、第一归零开关SZ1、第二归零开关SZ2、第一电容接地开关SCG1、第二电容接地开关SCG2、第一交叉耦合开关SCC1以及第二交叉耦合开关SCC2。

供应电压开关SVDD将供应电压VDD提供至第八节点N8,接地开关SGND耦接于第四节点N4以及接地端之间。第一归零开关SZ1耦接于第一内部节点NI1以及第三节点N3之间,第二归零开关SZ2耦接于第二内部节点NI2以及第五节点N5之间。

第一电容接地开关SCG1耦接于第六节点N6以及接地端之间,第二电容接地开关SCG2耦接于第七节点N7以及接地端之间。第一交叉耦合开关SCC1耦接于第三节点N3以及第七节点N7之间,第二交叉耦合开关SCC2耦接于第五节点N5以及第六节点N6之间。

当交叉耦合锁存400操作于图3的充电状态SCH时,第一归零开关SZ1、第二归零开关SZ2、第一电容接地开关SCG1、第二电容接地开关SCG2以及供应电压开关SVDD系为导通,而其他的开关皆为不导通。供应电压VDD透过第三晶体管M3、第一归零开关SZ1以及第一电容接地开关SCG1而对第一耦合电容CC1进行充电,且透过第四晶体管M4、第二归零开关SZ2以及第二电容接地开关SCG2而对第二耦合电容CC2进行充电。

当交叉耦合锁存400操作于图3的放电状态SDCH时,供应电压开关SVDD系为不导通,而接地开关SGND为导通,第一归零开关SZ1、第二归零开关SZ2、第一电容接地开关SCG1以及第二电容接地开关SCG2皆维持导通。第一耦合电容CC1经由第一归零开关SZ1以及第一晶体管M1而放电,第二耦合电容CC2经由第二归零开关SZ2以及第二晶体管M2而放电。根据本发明之一实施例,交叉耦合锁存400的不匹配包括第一晶体管M1以及第二晶体管M2之临限电压的不匹配。

换句话说,第一耦合电容CC1系放电至第一晶体管M1之临限电压,第二耦合电容CC2系放电至第二晶体管M2的临限电压。也就是,第一耦合电容CC1以及第二耦合电容CC2分别储存第一晶体管M1之临限电压以及第二晶体管M2之临限电压。也就是,在放电状态SDCH时,第一耦合电容CC1以及第二耦合电容CC2分别储存第一晶体管M1之临限电压以及第二晶体管M2的临限电压。

当交叉耦合锁存400操作于图3之取样状态SSMP时,第一归零开关SZ1、第二归零开关SZ2、第一电容接地开关SCG1、第二电容接地开关SCG2以及接地开关SGND系为不导通,输入开关SI、反向输入开关SIB、第一交叉耦合开关SCC1以及第二交叉耦合开关SCC2系为导通。因此,输入电压VI被提供至第六节点N6以及第七节点N7,以导通或不导通第三晶体管M3以及第四晶体管M4,并且第一晶体管M1、第二晶体管M2、第三晶体管M3以及第四晶体管M4因第一交叉耦合开关SCC1以及第二交叉耦合开关SCC2导通而形成交叉耦合锁存。

当交叉耦合锁存400操作于图3之比较状态SCMP时,输出开关SO、反向输出开关SOB、供应电压开关SVDD以及接地开关SGND系为导通。因此,交叉耦合锁存400比较来自位线BL以及反向位线BLB之输入电压VI,而产生输出节点NO以及反向输出节点NOB之输出电压VOUT。

举例来说,位线BL系为低逻辑电平,反向位原线BLB系为高逻辑电平。当来自位线BL以及反向位线BLB之输入电压VI于取样状态SSMP被提供至交叉耦合锁存400时,第三节点N3以及第七节点N7为低逻辑电平,第五节点N6以及第六节点N6系为高逻辑电平。因此,第一晶体管M1以及第四晶体管M4为导通。

当供应电压开关SVDD以及接地开关SGND于比较状态SCMP中为导通时,第一晶体管M1将第三节点N3的电压下拉至接地电平,第四晶体管M4将供应电压VDD提供至第五节点N5。接着,第三节点N3以及第五节点N5之电压分别输出至输出节点NO以及反向输出节点NOB,而为输出电压VOUT。因此,输入电压VI就被交叉耦合锁存400所侦测。

图5显示根据本发明之另一实施例所述之交叉耦合锁存的电路图。根据本发明之一实施例,第5图之交叉耦合锁存500对应至图2之第一交叉耦合锁存221以及第二交叉耦合锁存222。

将第5图之交叉耦合锁存500与图4的交叉耦合锁存400相比,交叉耦合锁存500更包括第五晶体管M5以及第六晶体管M6。

第五晶体管M5包括栅极端、漏极端以及源极端,其中栅极端耦接至第九节点N9、漏极端耦接至第一晶体管M1之源极端以及源极端耦接至第四节点N4。第六晶体管M6包括栅极端、漏极端以及源极端,其中栅极端耦接至第十节点N10、漏极端第二晶体管M2之源极端以及源极端耦接至第四节点N4。

交叉耦合锁存500更包括第一防浮接开关SAF1、第二防浮接开关SAF2、第一上拉开关SPU1以及第二上拉开关SPU2。第一防浮接开关SAF1耦接于第六节点N6以及第九节点N9之间。第二防浮接开关SAF2耦接于第七节点N7以及第十节点N10之间。第一上拉开关SPU1将供应电压VDD提供至第九节点N9。第二上拉开关SPU2将供应电压VDD提供至第十节点N10。

由于交叉耦合锁存500具有交叉耦合锁存400的相同组件,因此交叉耦合锁存500之该些相同组件操作于充电状态SCH、放电状态SDCH、取样状态SSMP以及比较状态SCMP的操作,在此不再重复赘述。

当交叉耦合锁存500操作于充电状态SCH、放电状态SDCH或取样状态SSMP时,第一上拉开关SPU1以及第二上拉开关SPU2分别将供应电压VDD提供至第五晶体管M5之栅极端以及第六晶体管M6之栅极端,使得第五晶体管M5以及第六晶体管M6完全导通。

当交叉耦合锁存500操作于比较状态SCMP时,第一防浮接开关SAF1将第九节点N9耦接至第六节点N6,第二防浮接开关SAF2将第十节点N10耦接至第七节点N7,进而避免瞬时漏电流由供应电压VDD流至接地端。

参考图4,举例来说,当交叉耦合锁存400操作于比较状态SCMP且位于低逻辑电平之反向位线BLB之电压提供至第六节点N6时,第一晶体管M1因临限电压储存于第一耦合电容CC1而操作于次临限区。此外,第三晶体管M3因第六节点N6位于低逻辑电平而导通。因此,导致了瞬间漏电流自供应电压VDD流至接地端,进而增加功率损耗。

参考第5图,当第九节点N9于比较状态SCMP中耦接至第六节点N6时,第五晶体管M5因第六节点N6位于低逻辑电平而不导通,进而排除瞬间漏电流且降低功率损耗以符合低功耗之应用。

图6显示根据本发明之一实施例所述之交叉耦合锁存之操作的流程图。如第6图所示,步骤611~641系由图2之交叉耦合锁存221所执行,步骤612~642系由图2之第二交叉耦合锁存222所执行。根据本发明之一实施例,第一交叉耦合锁存221以及第二交叉耦合锁存222可为图4之交叉耦合锁存400。根据本发明之另一实施例,第一交叉耦合锁存221以及第二交叉耦合锁存222可为第5图之交叉耦合锁存500。

在第一阶段中,第一交叉耦合锁存221之第一耦合电容CC1以及第二耦合电容CC2在步骤611进行充电,而达成归零的目的。在此同时,一组输入电压VI在步骤612提供至第二交叉耦合锁存222。

在紧接着第一阶段之第二阶段中,第一交叉耦合锁存221之第一耦合电容CC1以及第二耦合电容CC2在步骤621进行放电,以消除第一交叉耦合锁存221之第一晶体管M1以及第二晶体管M2之间的不匹配。在此同时,提供至第二交叉耦合锁存222之该组输入电压VI在步骤622被比较而产生第一组输出电压VOUT。

在紧接着第二阶段之第三阶段中,另一组输入电压VI在步骤631提供至第一交叉耦合锁存221之第三晶体管M3、第四晶体管M4、第一耦合电容CC1以及第二耦合电容CC2。在此同时,第二交叉耦合锁存222之第一耦合电容CC1以及第二耦合电容CC2在步骤632被充电而达成归零的目的。

在紧接着第三阶段之第四阶段中,提供至第一交叉耦合锁存221之该组输入电压VI在步骤641被比较,而产生另一组输出电压VOUT。在此同时,第二交叉耦合锁存222之第一耦合电容CC1以及第二耦合电容CC2在步骤642被放电,以消除第二交叉耦合锁存222之第一晶体管M1以及第二晶体管M2之间的不匹配。

本发明在此提出了非挥发性内存之感测放大器。感测放大器包括复数交叉耦合锁存,其中该些交叉耦合锁存交替地操作于归零状态以及感测状态,且并列执行。因此,交叉耦合锁存操作于归零状态所需的时间可是为零,使得侦测数据的速度得以更快。

虽然本公开的实施例及其优点已公开如上,但应该了解的是,任何所属技术领域中具有通常知识者,在不脱离本公开之精神和范围内,当可作更动、替代与润饰。此外,本公开之保护范围并未局限于说明书内所述特定实施例中的制程、机器、制造、物质组成、装置、方法及步骤,任何所属技术领域中具有通常知识者可从本公开一些实施例之揭示内容中理解现行或未来所发展出的制程、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本公开一些实施例使用。因此,本公开之保护范围包括上述制程、机器、制造、物质组成、装置、方法及步骤。另外,每一申请专利范围构成个别的实施例,且本公开之保护范围也包括各个申请专利范围及实施例的组合。

【符号说明】

100,200:感测放大器

110:输入开关

121:第一交叉耦合锁存

122:第二交叉耦合锁存

130:输出开关

140:控制器

221:第一交叉耦合锁存

222:第二交叉耦合锁存

400,500:交叉耦合锁存

BL:位线

BLB:反向位线

NO:输出节点

NOB:反向输出节点

VI:输入电压

VOUT:输出电压

SI:输入开关

SIB:反向输入开关

SI1:第一输入开关

SIB1:第一反向输入开关

SI2:第二输入开关

SIB2:第二反向输入开关

SO:输出开关

SOB:反向输出开关

SO1:第一输出开关

SOB1:第一反向输出开关

SO2:第二输出开关

SOB2:第二反向输出开关

SVDD:供应电压开关

SGND:接地开关

SZ1:第一归零开关

SZ2:第二归零开关

SCG1:第一电容接地开关

SCG2:第二电容接地开关

SCC1:第一交叉耦合开关

SCC2:第二交叉耦合开关

SAF1:第一防浮接开关

SAF2:第二防浮接开关

SPU1:第一上拉开关

SPU2:第二上拉开关

P1:第一阶段

P2:第二阶段

P3:第三阶段

P4:第四阶段

P5:第五阶段

P6:第六阶段

SCH:充电状态

SDCH:放电状态

SSMP:取样状态

SCMP:比较状态

M1:第一晶体管

M2:第二晶体管

M3:第三晶体管

M4:第四晶体管

M5:第五晶体管

M6:第六晶体管

CC1:第一耦合电容

CC2:第二耦合电容

NI1:第一内部节点

NI2:第二内部节点

N3:第三节点

N4:第四节点

N5:第五节点

N6:第六节点

N7:第七节点

N8:第八节点

N9第九节点

N10:第十节点

611~641、612~642:步骤流程

- 感测放大器和使用感测放大器的半导体存储装置

- 具有不同于感测放大器电路的页寄存器和存储器阵列下方的感测放大器接口的3D存储器装置