薄膜晶体管阵列基板和包括其的数字X射线检测器设备

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及一种用于数字X射线检测器设备的薄膜晶体管阵列基板和包括其的数字X射线检测器设备,该薄膜晶体管阵列基板能够将由于静电的流入而导致的缺陷减到最小。

背景技术

因为X射线具有短波长,所以X射线可以容易地穿过对象。X射线的透射率取决于对象的内部密度。因此,可以通过检测透射穿过对象的X射线的量来观察对象的内部结构。

在医学领域中使用的基于X射线的检查方法之一是胶片打印方案(film printingscheme)。然而,在胶片打印方案中,为了检查结果,拍摄图像,并且然后打印胶片。因此,为了检查结果需要花费很长时间。尤其是,在胶片打印方案中,在存储和保存打印胶片方面存在一些困难。

使用薄膜晶体管的数字X射线检测器(DXD)设备已经被开发并广泛用于医疗领域。

DXD设备对透射穿过对象的X射线的透射率进行检测,并且基于透射率在显示器上显示对象的内部状态。

因此,数字X射线检测器设备可以显示对象的内部结构,而无需使用额外的胶片和打印纸。此外,DXD设备可以在X射线拍摄之后立即实时检查结果。

发明内容

一种数字X射线检测器设备检测数字X射线检测面板内的电流以基于该电流实现图像,并且该数字X射线检测器设备包括响应于光的光电PIN(P型半导体-本征型半导体-N型半导体)二极管和诸如驱动光电PIN二极管的驱动薄膜晶体管之类的各种类型的元件。

由于元件易受电击(例如从外部引入的静电)的影响,因此当静电被引入到元件中时,可能出现元件缺陷。

例如,诸如液晶显示(LCD)设备或有机发光显示(OLED)设备等显示设备包括静电放电(ESD)防护电路以解决静电。

ESD防护电路可以进行操作,使得ESD发生并且过电压被施加到元件,过电压通过连接到接地端子的ESD防护电路被放电。

因此,该显示设备包括位于将数据焊盘连接到显示区域的数据线或连接线处的ESD防护电路,以解决通过数据线或连接线引入的静电。

在一些示例中,数字X射线检测器设备包括读出电路焊盘。读出电路焊盘可以通过读出线或连接线电连接到驱动区域。

与显示设备的数据焊盘相比,读出电路焊盘可以用于施加信号,并且还可以用于从驱动区域读取作为数据信号的读出信号。

在显示设备在读出电路焊盘与驱动区域之间的读出线或者连接线处包括ESD防护电路的一些情况下,由于信号干扰,在读出信号值中可能出现噪声。因此,优选地,数字X射线检测器设备可以不包括ESD防护电路。

在显示设备可能在读出电路焊盘区域中不包括ESD防护电路以避免信号干扰的一些情况下,可能不能解决由通过读出电路焊盘区域引入的静电所引起的元件缺陷。

因此,本发明的发明人发明了一种用于数字X射线检测器设备的薄膜晶体管阵列基板和包括其的数字X射线检测器设备,该薄膜晶体管阵列基板能够将由于静电的流入而引起的缺陷减到最小并且将信号干扰减到最小。

本发明提供了一种用于数字X射线检测器设备的薄膜晶体管阵列基板和数字X射线检测器设备,能够将由引入到读出电路焊盘或读出线和数字X射线检测器设备中的静电引起的缺陷减到最小。

本发明还提供了一种用于数字X射线检测器设备的薄膜晶体管阵列基板和数字X射线检测器设备,能够将由引入到读出电路焊盘或读出线中的静电引起的缺陷减到最小,并且将由于信号干扰而在读出电路信号中出现的噪声减到最小。

本发明还提供了一种用于数字X射线检测器设备的薄膜晶体管阵列基板和数字X射线检测器设备,能够将由在对母基板执行单元阵列工艺期间可能生成的静电引起的缺陷减到最小。

本发明的目的不限于上述目的,并且可以通过以下描述来理解本发明的尚未提及的其它目的和优点,并且通过本发明的实施例来更清楚地理解本发明的尚未提及的其它目的和优点。还容易理解,可以通过所附权利要求中描述的特征及其组合来实现本发明的目的和优点。

根据本发明的实施例,提供了一种用于数字X射线检测器设备的薄膜晶体管阵列基板和数字X射线检测器设备,能够将由静电的流入引起的缺陷减到最小,而无需在读出电路焊盘区域中设计ESD防护电路。

根据本发明的实施例,一种用于数字X射线检测器设备的薄膜晶体管阵列基板包括:具有驱动区域和非驱动区域的基础基板;至少一个读出电路焊盘,设置在非驱动区域内并电连接到驱动区域;以及至少一条读出电路焊盘连接线,被配置为将驱动区域电连接到至少一个读出电路焊盘,其中至少一条静电感应线进一步连接到读出电路焊盘连接线,并且具有比读出电路焊盘连接线的电阻大的电阻。

在这种情况下,静电感应线可以不与读出电路焊盘连接线重叠,并且可以设置在彼此相邻的读出电路焊盘连接线之间。

另外,静电感应线可以具有比读出电路焊盘连接线的宽度窄的宽度,并且至少一个电容器可以设置在静电感应线的下方。

另外,根据另一实施例,静电感应线与读出电路焊盘连接线重叠,并且可以设置在读出电路焊盘连接线的下方。

在这种情况下,静电感应线可以由包括氧化铟锡(ITO)的材料制成,并且静电感应线可以具有宽度重复增大或减小的图案。

另外,根据本发明的实施例,数字X射线检测器设备包括薄膜晶体管阵列基板;读出电路,连接到读出电路焊盘;至少一条读出电路连接线,设置在基础基板上方并被配置为将至少一个读出电路焊盘电连接到读出电路;以及闪烁体层,设置在薄膜晶体管阵列基板的上方,其中至少一条静电感应线可以进一步连接到读出电路连接线。

根据本发明,具有较大电阻的至少一条静电感应线连接到将驱动区域电连接到读出电路焊盘的读出电路焊盘连接线,以基于从外部引入的静电来使静电感应线破裂,从而在不设计额外的ESD防护电路的情况下将由通过读出电路焊盘或读出线引入的静电引起的缺陷减到最小。

此外,根据本发明,可以在不在读出电路焊盘区域中设计额外的ESD防护电路的情况下将由静电引起的缺陷减到最小,从而将由于信号干扰而在读出电路信号中产生的噪声以及由静电引起的缺陷减到最小。

另外,根据本发明,静电感应线可以连接到与用于大规模生产系统(MPS)测试的MPS线连接的读出电路连接线,以将由在对母基板执行单元阵列工艺期间可能从外部引入的静电引起的缺陷减到最小。

除了上述效果之外,将在描述实现本发明的具体内容的同时一起描述本发明的具体效果。

附图说明

图1是示出了示例性数字X射线检测器设备的示意性框图。

图2是示出了示例性数字X射线检测器设备的示意性平面图。

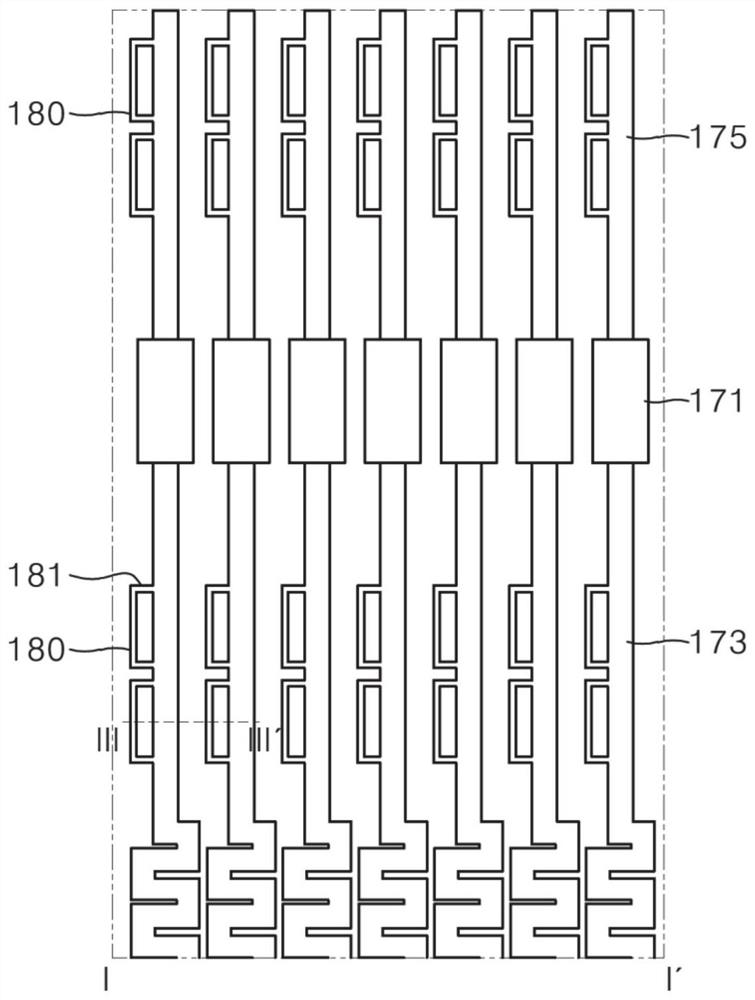

图3是示出了沿数字X射线检测器设备的线I-I'截取的示例性区域的平面放大图。

图4是示出了沿数字X射线检测器设备的线II-II'和线III-III'中的每条线截取的示例性区域的放大截面图。

图5A和图5B示出了平面放大图,其显示了沿数字X射线探测器设备的线I-I'截取的示例性区域。

图6是示出了沿数字X射线检测器设备的线II-II'、线IV-IV'和线V-V'截取的区域的放大截面图。

具体实施方式

参考附图详细描述本发明的一些实施例。因此,本发明所属领域的技术人员可以容易地实现本发明的技术构思。在本发明的描述中,如果确定与本发明相关的公知技术的详细描述会不必要地使本发明的要点难以理解,则可以省略该详细描述。参考附图详细描述本发明的一个或多个实施例。在附图中,相同的附图标记可以用于表示相同或相似的部件。

在本文中,术语“上部”、“下部”、“上”、“下”等被使用,使得在第一部件布置在第二部件的“上部”或“下部”处的情况下,第一部件可以布置为与第二部件的上表面(或下表面)接触,或者另一部件可以设置在第一部件和第二部件之间。类似地,在第一部件布置在第二部件上或下的情况下,第一部件可以直接布置在第二部件上或第二部件下(与第二部件接触),或者一个或多个其它部件可以设置在第一部件和第二部件之间。

此外,术语“连接”、“耦合”等被使用,使得在第一部件连接或耦合到第二部件的情况下,第一部件可以直接连接或能够连接到第二部件,或者一个或多个附加部件可以设置在第一部件和第二部件之间,或者第一部件和第二部件可以通过一个或多个附加部件连接或耦合。

在下文中,描述了根据本发明的一些实施例的用于数字X射线检测器设备的薄膜晶体管阵列基板和包括其的数字X射线检测器设备。

图1是示出了数字X射线检测器设备的示意性框图。数字X射线检测器设备可以包括薄膜晶体管阵列110、栅极驱动器120、偏置电源130、读出集成电路(IC)140和时序控制器150。

薄膜晶体管阵列110可以包括由沿第一方向布置的多条栅极线GL和沿与第一方向正交的第二方向布置的多条读出线RL限定的多个单元区域。

单元区域以矩阵结构进行布置。每个单元区域可以包括其中形成有光敏像素P的像素区域。薄膜晶体管阵列110可以检测从X射线源发射的X射线,可以将检测到的X射线转换为电信号,并且可以输出电信号。

每个光敏像素可以包括PIN二极管和薄膜晶体管TFT,PIN二极管将由闪烁体从X射线转换的可见光区域的光转换为电信号并输出该电信号,薄膜晶体管TFT将从PIN二极管输出的检测信号传送到读出电路140。PIN二极管的第一端可以连接到薄膜晶体管,而其第二端可以连接到偏置线BL。

薄膜晶体管的栅电极可以连接到承载扫描信号的栅极线GL。薄膜晶体管的源电极/漏电极可以分别连接到PIN二极管和读出线RL,所述读出线RL承载从PIN二极管输出的检测信号。每条偏置线BL可以以平行于每条读出线RL的方式延伸。

栅极驱动器120可以通过栅极线GL顺序地将栅极信号施加到光敏像素的薄膜晶体管。光敏像素的薄膜晶体管可以响应于具有栅极导通电压电平的栅极信号而导通。

偏置电源130可以通过偏置线BL将驱动电压施加到光敏像素。偏置电源130可以选择性地向PIN二极管施加反向偏置或正向偏置。

读出电路140可以读出从薄膜晶体管接收的检测信号,该薄膜晶体管响应于栅极驱动器的栅极信号而导通。例如,从PIN二极管输出的检测信号可以通过薄膜晶体管和读出线RL输入到读出电路140。

读出电路140可以具有用于读出偏移图像的偏移读出时间段和用于读出在X射线曝光之后的检测信号的X射线读出时间段,并且可以在X射线读出时间段期间读出从光敏像素输出的检测信号。

读出电路140可以包括信号检测器和多路复用器。信号检测器包括多个分别对应于读出线RL的放大电路。每个放大电路可以包括放大器、电容器和复位元件。

时序控制器150可以通过生成起始信号和时钟信号并将起始信号和时钟信号中的每一个提供给栅极驱动器120来控制栅极驱动器120的操作。此外,时序控制器150可以通过生成读出控制信号和读出时钟信号并将读出控制信号和读出时钟信号中的每一个提供给读出电路140来控制读出电路140的操作。

图2是示出了示例性数字X射线检测器200的示意性平面图。

用于数字X射线检测器设备的薄膜晶体管阵列基板100包括驱动区域AA和非驱动区域NAA。驱动区域AA包括一个或多个像素P,而非驱动区域NAA围绕驱动区域AA的周边。

栅极驱动器120可以包括一个或多个栅极驱动器集成电路(IC),并且可以在阵列基板100的一侧或两侧处设置在阵列基板100的非驱动区域NAA内。

栅极驱动器120的类型可以是面板内栅极(GIP)类型,并且栅极驱动器120可以通过一条或多条栅极线电连接到驱动区域AA中的像素。

一个或多个读出电路焊盘171设置在阵列基板100的非驱动区域NAA的未设置栅极驱动器120的一侧,并且读出电路连接线173可以设置在读出电路焊盘171和驱动区域AA之间。

读出电路焊盘171可以通过读出电路焊盘连接线173电连接到驱动区域AA的像素。

在这种情况下,读出电路焊盘连接线173可以通过附加的读出线RL连接到像素,但不限于此。读出电路焊盘连接线173和读出线RL可以彼此集成在一起。

读出电路焊盘连接线173可以连接到读出电路焊盘171的第一侧,并且读出电路连接线175可以设置在读出电路焊盘171的第二侧。

读出电路连接线175设置在读出电路140与读出电路焊盘171之间,并且将读出电路140电连接到读出电路焊盘171。

可以使用玻璃上芯片(COG)方法或膜上芯片(COF)方法来实现读出电路140。例如,读出电路140可以包括至少一个读出电路IC 143和柔性膜141,至少一个读出电路IC 143是至少一个读出IC。

在这种情况下,每个读出电路143安装在柔性膜141上,柔性膜141的第一端结合到控制印刷电路板(PCB)151,并且柔性膜141的第二端结合到阵列基板100,以电连接到读出电路连接线175。

在本发明中,读出电路区域指的是阵列基板100的非驱动区域NAA,以用于在阵列基板100的非驱动区域NAA中支撑读出电路焊盘171和读出电路140。

用驱动芯片实现的多个电路可以安装在控制PCB 151上,例如,时序控制器150可以设置在控制PCB 151上。

功率控制器可以进一步设置在控制PCB 151上,以向阵列基板100、栅极驱动器120和读出电路140中的每一个提供电压或电流,或者控制所提供的电压或电流。

在下文中,参考图3更详细地描述本发明的实施例,图3是示出了沿数字X射线检测器的线I-I'(图2中示出)截取的示例性区域的放大平面图。

电连接到驱动区域AA的至少一个读出电路焊盘171设置在非驱动区域NAA的读出电路区域内。

另外,至少一个读出电路焊盘连接线173设置在驱动区域AA和至少一个读出电路焊盘171之间,以电连接驱动区域AA和至少一个读出电路焊盘171,并且每条读出电路焊盘连接线173连接到一个读出电路焊盘171的第一端。

在这种情况下,至少一条静电感应线180进一步连接到读出电路焊盘连接线173,并且具有比读出电路焊盘连接线173的电阻高的电阻。

静电感应线180可以不与读出电路焊盘连接线173重叠,并且设置在两条相邻的读出电路焊盘连接线173之间,使得静电感应线180可以沿着读出电路焊盘连接线173布置为与读出电路焊盘连接线173平行。

至少一条静电感应线180与至少一条读出电路焊盘连接线173间隔开,并且可以通过至少一条静电感应桥接线181电连接到至少一条读出电路焊盘连接线173。

在这种情况下,静电感应桥接线181设置在静电感应线180的两端,以将静电感应线180电连接到读出电路焊盘连接线173。

静电感应线180和静电感应桥接线181可以均由与读出电路焊盘连接线173相同的材料制成,并且静电感应线180、静电感应桥接线181和读出电路焊盘连接线173可以彼此集成在一起。

在一些示例中,静电感应线180和静电感应桥接线181均具有比读出电路焊盘连接线173的宽度窄的宽度,并且均具有比读出电路焊盘连接线173的电阻大的电阻。

当静电通过读出电路焊盘连接线173被引入时,虽然读出电路焊盘连接线173可以不破裂,但是因为静电感应线180和静电感应桥接线181均具有比读出电路焊盘连接线173的电阻大的电阻,因此静电感应线180或静电感应桥接线181可以在具有更大电阻的区域处破裂。

在一些示例中,静电感应线180可以具有如图3所示的直线图案,但不限于此,并且可以具有电阻更大的图案,例如Z字形图案或静电感应线180的宽度重复增大或减小的图案。当静电感应线180具有电阻更大的图案时,静电感应线180可以容易地在具有该图案的区域处破裂。

当静电流入读出电路焊盘连接线173时,静电感应线180破裂以使静电消散,从而将由于静电引入驱动区域而对元件造成的损坏减到最小。

特别地,静电感应线180的破裂可以不影响读出电路焊盘连接线173,从而无异常地稳定检测读出电路信号。

另外,根据本发明,额外连接到读出电路焊盘连接线173的静电感应线180可以将从外部引入的静电的发生减到最小,而无需在读出电路焊盘连接线173中形成额外的静电放电(ESD)防护电路,以将由于信号干扰而在读出电路信号中产生的噪声和由静电引起的缺陷减到最小。

静电感应线180可以连接到读出电路焊盘连接线173。在一些示例中,多条静电感应线180连接到读出电路焊盘连接线173,以将由于静电的流入而对元件造成的损坏减到最小。

在多条静电感应线180连接到一条读出电路焊盘连接线173的一些情况下,第一静电感应线180基于静电的流入而破裂,并且随后,第二静电感应线180可以基于静电的进一步流入而进一步破裂。因此,即便静电被连续引入,也可以将静电引起的缺陷减到最小。

在一些示例中,如图4(下方将对其进行更详细的描述)所示,一个或多个电容器C1和C2均都设置在静电感应线180下方,并且引入到静电感应线180中的静电累积在电容器上以促进静电感应线180的破裂。

在电容器设置在静电感应线180下方的一些情况下,从外部引入的静电累积在电容器中,并且当静电累积在电容器中时,在超过电容器的可允许量的静电的情况下,电容器可能破裂以进一步将由于静电的流入而对元件造成的损坏减到最小。

在这种情况下,通过设置多个电容器,可以增大电容器中累积的静电量,从而即使当引入大量的静电时也能够有效地使静电消散。

在一些示例中,读出电路连接线175在与读出电路焊盘连接线173所连接的读出电路焊盘171的第一侧相对的第二侧处连接到读出电路焊盘171。

读出电路连接线175设置在读出电路焊盘171和读出电路部分140之间,以将读出电路焊盘171电连接到读出电路部分140。

静电感应线180可以另外连接到读出电路连接线175,以消散通过读出电路140或读出电路连接线175引入的静电。

另外,静电感应线180连接到读出电路连接线175,以将在单元阵列工艺之后从用于测试线路的大规模产品系统(MPS)线引入的静电的发生减到最小。

单元阵列工艺是指在母基板上限定多个阵列区域并在每个限定的阵列区域中形成包括栅极线、读出线、驱动薄膜晶体管和PIN二极管的薄膜晶体管阵列的工艺。

在执行单元阵列工艺之后,执行MPS测试以检查薄膜晶体管阵列的每条信号线的断开和短路缺陷,从而确定缺陷。如果基于MPS测试确定是有缺陷的,则另外执行修复工艺。

为了执行MPS测试,在单元阵列工艺期间形成至少一条由金属制成的MPS线,以用于执行随后的MPS测试。可以在将母基板切割成阵列区域的切割工艺期间,也就是在MPS测试之后去除MPS线。

读出电路连接线175在单元阵列工艺期间连接到MPS线,并且还连接到静电感应线180。如上所述,读出电路连接线175连接到静电感应线180以及MPS线,以将由在对母基板执行单元阵列工艺期间可能从外部引入的静电引起的缺陷减到最小。

例如,静电感应线180连接到读出电路连接线175,以有效地解决在MPS测试工艺期间生成的静电。

另外,当在单元阵列工艺和切割工艺之后将读出电路140连接到读出电路连接线175时,静电感应线180可以有效地将可能由于静电流入读出电路140而导致的元件损坏减到最小。

因此,静电感应线180另外连接到读出电路连接线175,以有效地解决在从单元阵列工艺到形成数字X射线检测器设备的最终工艺的所有情况下可能生成的静电。

图4是示出了沿数字X射线检测器设备的线II-II'(图2中所示)和线III-III'(图3中所示)截取的示例性区域的放大截面图。在下文中,参考图4描述本发明的实施例。

根据本发明的一个实施例的数字X射线检测器200包括基础基板210。

基础基板210可以具体化为由玻璃制成的玻璃基板,但不限于此。在基础基板210用于柔性数字X射线检测器设备的一些情况下,由聚酰亚胺材料制成并具有柔性特性的基板可以用作基础基板210的示例。

基础基板210的驱动区域AA包括多个像素区域。

每个像素包括薄膜晶体管220和PIN二极管230。多个薄膜晶体管220和多个PIN二极管230可以设置在具有多个像素区域的阵列基板上。以下描述像素的薄膜晶体管220和PIN二极管230,且除非另有指明,否则此结构也可被应用于相邻的像素。

包括第一电极225a、第二电极225b、栅电极221和有源层223的薄膜晶体管220设置在基础基板210上或上方。

缓冲层可以设置在基础基板210和薄膜晶体管220之间。在这种情况下,缓冲层可以由诸如氧化硅(SiOx)或氮化硅(SiNx)等无机材料制成,并且缓冲层可以作为由多个子层组成的多缓冲层来提供。

栅电极221可以设置在基础基板上。栅电极221可以由从由钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、铜(Cu)及其合金组成的组中选择的一种制成,并且可以包括单层或多层。

栅电极221可以从栅极线GL延伸。栅极线GL和栅电极221可以彼此集成在一起,使得栅电极221设置在栅极线GL中。因此,栅极线GL和栅电极221可以设置在同一层上。

栅极绝缘层222可以设置在栅电极221上,并且有源层223可以设置在栅极绝缘层222上。

有源层223可以由诸如氧化铟镓锌(IGZO)之类的氧化物半导体材料制成,但不限于此,并且可以由低温多晶硅(LTPS)或非晶硅(a-Si)制成。

第一电极225a可以设置在有源层223上,以连接到有源层223的第一端。第二电极225b可以设置在有源层223上,以连接到有源层223的第二端。

在这种情况下,第一电极225a可以从读出线RL分支出来,并且第一电极225a可以由将读出线RL连接到第一电极225a的附加连接电极电连接。

第一电极225a可以由从由钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、铜(Cu)及其合金组成的组中选择的一种制成,但不限于此。

第二电极225b可以是连接到PIN二极管230的源电极,而第一电极225a可以是漏电极,但不限于此,并且源区和漏区的位置可以互换。

作为绝缘层的第一钝化层226可以设置在有源层223上方以及第一电极225a和第二电极225b中的每一个上。第一钝化层226可以由诸如氧化硅(SiOx)或氮化硅(SiNx)之类的无机材料制成,但不限于此。

PIN二极管230设置在第一钝化层226上或上方,并连接到下方的薄膜晶体管220。PIN二极管230可以设置在像素区域中。

PIN二极管230可以包括连接到薄膜晶体管220的下电极231、在下电极231上的PIN层232和在PIN层232上的上电极233。

下电极231可以用作PIN二极管230中的像素电极。根据PIN二极管230的特性,下电极231可以由不透明金属(例如钼Mo)制成,或者由诸如氧化铟锡(ITO)、氧化铟锌(IZO)和氧化锌(ZnO)之类的透明氧化物中的至少一种制成。

下电极231可以经由第一钝化层226中的作为接触孔的第二接触孔226h连接到薄膜晶体管220的第二电极225b,使得薄膜晶体管220可以连接到PIN二极管230。

PIN层232可以设置在下电极231上,以将从X射线转换的可见光转换为电信号。在这一点上,闪烁体可以将X射线转换成可见光。

PIN层232可以通过在下电极231上顺序堆叠包含N型杂质的N(负)型半导体层、I(本征)型半导体层和包含P型杂质的P(正)型半导体层而形成。

I型半导体层可以比N型半导体层和P型半导体层中的每一个相对更厚。PIN层232可以由能够将从X射线源发射的X射线所转换成的可见光转换为电信号的材料制成,该材料例如是a-Se、HgI

上电极233可以设置在PIN层232上。上电极233可以由诸如氧化铟锡(ITO)、氧化铟锌(IZO)和氧化锌(ZnO)之类的透明氧化物中的至少一种制成,并且可以提高PIN二极管230的填充因子。

第二钝化层235可以设置在PIN二极管230上方。第二钝化层235可以由诸如氧化硅(SiOx)或氮化硅(SiNx)之类的无机材料制成,但是不限于此。第二钝化层235可以覆盖直到PIN二极管230的侧表面,以保护PIN二极管230的侧表面免受湿气或其它外来物质的影响。

偏置电极243可以设置在PIN二极管230上的第二钝化层235上。偏置电极243可以经由第二钝化层235中的作为接触孔的第三接触孔235a连接到PIN二极管230的上电极233,并且可以向PIN二极管230施加偏置电压。

偏置电极243可以从与读出线RL平行布置的偏置线BL分支出来。

平坦化层245可以设置在偏置电极243上,以覆盖包括PIN二极管230的基础基板210的整个表面。平坦化层245可以由诸如光丙烯酸(PAC)之类的有机材料制成,但不限于此。

闪烁体层260可以设置在平坦化层245上以覆盖PIN二极管230。

在一些示例中,闪烁体层260设置在薄膜晶体管220和PIN二极管230中的每一个上方,以覆盖薄膜晶体管220和PIN二极管230中的每一个。

由于闪烁体层260可以直接沉积在阵列基板上,所以可能需要对闪烁体层260的下表面平坦化。因此,平坦化层245被设置为对闪烁体层260的下表面平坦化,从而便于通过闪烁体的沉积来形成闪烁体层260。

闪烁体层260可以在垂直方向上生长以具有多个柱状晶相(crystal phase),使得多个闪烁体柱状晶体可以以并排方式布置,但是不限于此。闪烁体可以由诸如碘化铯(CsI)之类的材料制成,但不限于此。

在一些示例中,在读出电路区域的情况下,第二静电感应电容器电极184设置在基础基板210上,绝缘层可以设置在第二静电感应电容器电极184和第一静电感应电容器电极182之间,并且第一静电感应电容器电极182可以设置在第二静电感应电容器电极184上方。

在这种情况下,第二静电感应电容器电极184和第一静电感应电容器电极182之间的绝缘层可以是栅极绝缘层222。

在该示例中,第二静电感应电容器电极184可以由与栅电极221相同的材料制成,并可以与栅电极221形成在相同的层上,并且第一静电感应电容器电极182可以由与第一电极225a和第二电极225b中的每个电极相同的材料制成,并可以与第一电极225a和第二电极225b中的每个电极形成在相同的层上。

在这种情况下,第二电容器C

绝缘层可以设置在第一静电感应电容器电极182和静电感应线180之间,并且静电感应线180可以设置在第一静电感应电容器电极182上方。

在这种情况下,第一静电感应电容器电极182和静电感应线180之间的绝缘层可以是第一钝化层226和第二钝化层235。

因此,静电感应线180可以由与偏置电极243相同的材料制成,并且可以与偏置电极243形成在相同的层上。

在这种情况下,第一电容器C

读出电路焊盘连接线173可以与静电感应线180设置在相同的层上,并且可以与静电感应线180间隔开。读出电路焊盘连接线173可以由与偏置电极243相同的材料制成,并且可以与偏置电极243设置在相同的层上。

在这种情况下,静电感应线180具有比读出电路焊盘连接线173的宽度W

在下文中,参考图5A和图5B详细描述本发明的另一实施例,图5A和图5B是示出了沿数字X射线检测器设备的线I-I'(图2中所示)截取的示例性区域的放大平面图,并且省略与以上描述重复的内容。

一个或多个读出电路焊盘171设置在非驱动区域NAA的读出电路区域内,并且电连接到驱动区域AA。

另外,至少一条读出电路焊盘连接线173设置在驱动区域AA和至少一个读出电路焊盘171之间,以将驱动区域AA电连接到至少一个读出电路焊盘171,并且每条读出电路焊盘连接线173连接到一个读出电路焊盘171的第一端。

在这种情况下,具有比读出电路焊盘连接线173的电阻大的电阻的至少一条静电感应线280被附加地连接到读出电路焊盘连接线173。

静电感应线280与读出电路焊盘连接线173重叠,设置在读出电路焊盘连接线173下方,并且可以沿着读出电路焊盘连接线173布置为与读出电路焊盘连接线173平行。

静电感应线280与读出电路焊盘连接线173间隔开,并且可以通过绝缘层中的接触孔电连接到读出电路焊盘连接线173。

静电感应线280可以具有比读出电路焊盘连接线173的宽度窄的宽度,并且可以具有比读出电路焊盘连接线173的电阻大的电阻。

在这种情况下,静电感应线280可以由包括具有高电阻的ITO的材料制成。因此,静电感应线280可以具有比读出电路焊盘连接线173的电阻大的电阻。

在静电通过读出电路焊盘连接线173被引入的一些情况下,虽然读出电路焊盘连接线173可能不会破裂,但是由于静电感应线280的电阻大于读出电路焊盘连接线173的电阻,所以具有较大电阻的静电感应线280可以在具有较大电阻的区域处破裂。

在静电被引入到读出电路焊盘连接线173的一些情况下,静电感应线280破裂以使静电消散,从而将由于静电被引入到驱动区域中而对元件造成的损坏减到最小。

静电感应线280可以连接到一条读出电路焊盘连接线173。在一些示例中,多条静电感应线280连接到读出电路焊盘连接线173,以将由于静电的流入而对元件造成的损坏减到最小。

另外,在读出电路焊盘171下方另外连接一条或多条静电感应线280,以将通过读出电路焊盘171引入的静电的影响减到最小。

在这种情况下,静电感应线280另外连接到读出电路焊盘171下方,以将相邻的读出电路焊盘171和静电感应线280之间的短路减到最小,并将静电的影响减到最小。

在一些示例中,如作为本发明的另一实施例的图5B所示,静电感应线280可以具有宽度重复增大或减小的图案。

静电感应线280具有这样的图案,其中宽度重复增大或减小以促进静电感应线280基于静电而在出现瓶颈的位置处破裂。

读出电路连接线175可以在与读出电路焊盘连接线173所连接的读出电路焊盘171的第一侧相对的第二侧处连接到读出电路焊盘171。

读出电路连接线175设置在读出电路焊盘171和读出电路部分140之间,以将读出电路焊盘171电连接到读出电路140。

静电感应线280另外连接到读出电路连接线175,以有效地解决通过读出电路140或读出电路连接线175引入的静电。

图6是示出了沿数字X射线检测器设备的线II-II'(图2中所示)、线IV-IV'(图5A-5B中所示)和线V-V'(图5A-5B中所示)中的每条线截取的示例性区域的放大截面图。在下文中,将参考图6详细描述本发明的另一实施例。

然而,沿线II-II'截取的区域的描述与参考图4描述的内容重复,并且省略其细节。

在读出电路区域中,静电感应线280可以设置在基础基板210上方。

绝缘层可以设置在静电感应线280和读出电路焊盘连接线173之间,并且读出电路焊盘连接线173可以设置在静电感应线280上方。静电感应线280可以通过静电感应线280和读出电路焊盘连接线173之间的绝缘层中的接触孔电连接到读出电路焊盘连接线173。

例如,静电感应线280可以设置在第一钝化层226上,第二钝化层235可以设置在静电感应线280上,并且读出电路焊盘连接线173可以设置在第二钝化层235上。

另外,静电感应线280和读出电路焊盘连接线173可以通过第二钝化层235中的第三接触孔235b彼此电连接。

因此,静电感应线280由与PIN二极管230的上电极233相同的材料制成,并与PIN二极管230的上电极233设置在相同的层上,并且读出电路焊盘连接线173由与偏置电极243相同的材料制成,并可以与偏置电极243设置在相同的层上。

在这种情况下,静电感应线280具有比读出电路焊盘连接线173的宽度W

另外,静电感应线280可以沿着读出电路焊盘连接线173平行布置,如沿着线V-V'截取的截面图中所示。

另外,读出电路焊盘连接线173通过第二钝化层235中的两个第三接触孔235b电连接到静电感应线280,以允许静电流向静电感应线280。例如,读出电路焊盘连接线173的两端可以通过第二钝化层235中的两个第三接触孔235b电连接到静电感应线280。

根据本发明的数字X射线检测器设备200如下操作。

X射线照射到数字X射线检测器设备200。闪烁体层260将X射线转换成可见光。PIN二极管230的PIN层232将可见光区域中的光转换成电信号。

例如,当可见光区域中的光照射到PIN层232时,I型半导体层被N型半导体层和P型半导体层中的每一个耗尽,从而在其中产生电场。然后,由光产生的空穴和电子基于电场漂移,并分别被收集到P型半导体层和N型半导体层中。

PIN二极管230将可见光区域中的光转换为电信号,并将该电信号传送到薄膜晶体管220。这样传送的电信号经由连接到薄膜晶体管220的读出线RL显示为图像信号。

根据本发明,用于数字X射线检测器设备的薄膜晶体管阵列基板包括具有驱动区域和非驱动区域的基础基板;至少一个读出电路焊盘,设置在非驱动区域内并电连接到驱动区域;以及至少一条读出电路焊盘连接线,用于将驱动区域电连接到至少一个读出电路焊盘。

在这种情况下,具有比读出电路焊盘连接线的电阻大的电阻的一条或多条静电感应线进一步连接到读出电路焊盘连接线。

静电感应线可以不与读出电路焊盘连接线重叠,并且可以设置在彼此相邻的读出电路焊盘连接线之间,静电感应线具有比读出电路焊盘连接线的宽度窄的宽度,并且一个或多个电容器可以设置在静电感应线的下方。

静电感应线与读出电路焊盘连接线重叠,并且可以设置在读出电路焊盘连接线的下方,静电感应线可以由包括ITO的材料制成,并且静电感应线可以具有宽度重复增大或减小的图案。

驱动区域可以包括驱动薄膜晶体管、PIN二极管和偏置电极。驱动薄膜晶体管包括有源层、第一电极、第二电极和栅电极。PIN二极管电连接到驱动薄膜晶体管,且包括上电极、PIN层和下电极。偏置电极电连接到PIN二极管。

在这种情况下,静电感应线可以由与偏置电极相同的材料制成,并且可以与偏置电极设置在相同的层上,并且第一静电感应电容器电极和第二静电感应电容器电极设置在静电感应线的下方。

第一静电感应电容器电极可以由与第一电极和第二电极中的每一个相同的材料制成,并且可以与第一电极和第二电极中的每一个设置在相同的层上。第二静电感应电容器电极可以由与栅电极相同的材料制成,并且可以与栅电极设置在相同的层上。

另外,静电感应线可以由与上电极相同的材料制成,并且可以与上电极设置在相同的层上。

在读出电路焊盘下方可以另外连接一条或多条静电感应线。

另外,根据本发明,数字X射线检测器设备可以包括用于数字X射线检测器设备的薄膜晶体管阵列基板;读出电路,连接到读出电路焊盘;至少一条读出电路连接线,设置在基础基板上方并被配置为将读出电路焊盘电连接到读出电路;以及闪烁体,设置在薄膜晶体管阵列基板的上方,其中至少一条静电感应线可以另外连接到读出电路连接线。

尽管已经参考示例性附图描述了本发明,但是本发明不限于本文公开的实施例和附图,并且本领域技术人员可以在本发明的技术构思的范围内进行各种修改。此外,即使在本发明的实施例的描述中没有明确地描述基于本发明的结构而获得的工作效果,但是基于相应结构可预测的效果应当得到承认。

- 薄膜晶体管阵列基板和包括其的数字X射线检测器设备

- 薄膜晶体管阵列基板和包括其的数字X射线检测器装置