电致发光显示装置

文献发布时间:2023-06-19 13:49:36

本申请要求于2020年6月22日提交的韩国专利申请第10-2020-0075693号的权益,其通过引用并入本文,如同在本文中完整阐述一样。

技术领域

本公开涉及一种电致发光显示装置。

背景技术

基于发光层的材料,电致发光显示装置分类为无机发光显示装置和有机电致发光显示装置。电致发光显示装置的多个像素中的每个像素包括自发光的发光器件,并且通过使用基于图像数据的灰度级的数据电压来控制由发光器件发出的光量从而调节亮度。每个像素的像素电路可以包括驱动元件。

基于工艺偏差和/或驱动时间的流逝,每个像素中的驱动元件的阈值电压可能变化。而且,每个像素中的发光器件的阈值电压可能变化。当发生像素之间的驱动特性偏差时,尽管将相同的数据电压施加于每个像素,然而对在每个像素中发光有贡献的发光电流可能会不可避免地发生变化。发光电流的偏差导致亮度不均匀,从而降低图像质量。

在电致发光显示装置中,正在进行用于补偿像素之间的驱动特性偏差的各种研究,但是由于像素结构复杂并且补偿程度不足,因此在确保亮度均匀性方面存在限制。

发明内容

为了克服现有技术的上述问题,本公开可以提供一种电致发光显示装置,其中简化了像素结构,并且使由驱动元件和发光器件各自的特性偏差引起的发光电流的变化最小化。

此外,本公开可以提供一种基于简单的驱动方法来增强MPRT特性的电致发光显示装置。

为了实现这些目的和其他优点,并且根据本公开的目的,如在本文中实施和广泛描述的,一种电致发光显示装置包括:像素阵列,所述像素阵列包括多个像素、共同连接至在第一方向上相邻的像素的栅极线、共同连接至在与第一方向相交的第二方向上相邻的像素的数据线、以及共同连接至所有的多个像素的第一电源线、第二电源线和初始化电压供应线;以及面板驱动电路,所述面板驱动电路连接至像素阵列。

多个像素中的每个像素包括:驱动元件,所述驱动元件包括连接至第一节点的栅极、通过第一电源线连接至高电平驱动电源的源极、以及连接至第二节点的漏极;开关元件,所述开关元件包括连接至栅极线的栅极并包括源极和漏极,源极和漏极中的一个连接至第一节点,源极和漏极中的另一个电极连接至第二节点;第一电容器,所述第一电容器连接在数据线和第一节点之间;第二电容器,所述第二电容器连接在初始化电压供应线与第一节点之间;以及发光器件,所述发光器件包括连接至第二节点的阳极和通过第二电源线连接至低电平驱动电源的阴极。

本公开可以提供一种电致发光显示装置,其中简化了像素结构,并且使由驱动元件和发光器件各自的特性偏差引起的发光电流的变化最小化。此外,本公开可以提供一种基于简单的驱动方法来增强MPRT特性的电致发光显示装置。

附图说明

本公开包括附图以提供对本公开的进一步理解,并且附图被并入本申请的一部分并构成本申请的一部分,附图示出了本公开的一个或多个实施例,并且与说明书一起用于解释本公开的原理。在附图中:

图1是示出根据本公开的实施例的电致发光显示装置的框图;

图2是示出在图1的显示面板中设置的像素阵列的图;

图3和图4是示出根据本公开的实施例的暂时发光方法(temporary emissionmethod)的驱动时序的图;

图5是示出基于暂时发光方法驱动的像素的等效电路的图;

图6是示出与第一栅极线和第m数据线连接的像素的驱动时序的图。

图7A是示出在图6的第一初始化时段中像素的工作的图;

图7B是示出在图6的第二初始化时段中像素的工作的图;

图7C是示出在图6的编程时段(programming period)中像素的工作的图;

图7D是示出在图6的发光时段中像素的工作的图;以及

图8是示出关于发光电流的变化相对于发光器件的特性变化与现有技术进行比较而获得的结果的图。

具体实施方式

在下文中,将参照附图详细描述本公开的示例性实施例。在说明书中,在为每个附图中的元件添加附图标记时,应当注意,尽可能对元件使用已经用于表示其他附图中的相同元件的相同附图标记。在以下描述中,当相关的已知功能或结构的详细描述被确定为不必要地使本公开的要点模糊时,将省略该详细描述。

图1是示出根据本公开的实施例的电致发光显示装置的框图。图2是示出在图1的显示面板中设置的像素阵列的图。

参照图1和图2,根据本公开的实施例的电致发光显示装置可以包括显示面板10、时序控制器11、数据驱动器12、栅极驱动器13和电源电路20。在图1中,时序控制器11、数据驱动器12和电源电路20中的全部或一部分可以被集成到驱动集成电路(IC)中,并且可以设置为一个主体。在图1中,时序控制器11、数据驱动器12和电源电路20可以构成面板驱动电路。面板驱动电路可以通过多条信号线14、15、IL、EVL1和EVL2连接到显示面板10的像素阵列。

参照图1和图2,在显示面板10中显示输入图像的画面中,在列方向(或垂直方向)上延伸的多条数据线14和在行方向(或水平方向)上延伸的多条栅极线15)可以彼此相交,并且多个像素PIX可以被布置为矩阵类型以将像素阵列配置在多个相交区域中。各条数据线14可以共同连接至在行方向上彼此相邻的像素PIX,并且各条栅极线15可以共同连接至在列方向上彼此相邻的像素PIX。如图2所示,多条数据线141至14m可以彼此电断开,并且多条栅极线151至15n可以彼此电断开。像素阵列可以进一步包括共同连接到所有像素PIX的初始化电压供应线IL、第一电源线EVL1和第二电源线EVL2。

像素阵列中包括的像素PIX可以被分组为多个像素组,并且可以显示各种颜色。当将用于实现颜色的像素组被定义为单位像素时,一个单位像素可以包括红色(R)像素、绿色(G)像素和蓝色(B)像素,此外,可以包括红色(R)像素、绿色(G)像素、蓝色(B)像素和白色(W)像素。

每个像素PIX可以包括发光器件和驱动元件,该驱动元件基于栅极-源极电压产生发光电流以驱动发光器件。发光器件可以包括阳极、阴极以及在阳极和阴极之间形成的有机化合物层。有机化合物层可以包括空穴注入层(HIL)、空穴传输层(HTL)、发射层(EML)、电子传输层(ETL)和电子注入层(EIL),而不限于此。当像素电流在发光器件中流动时,穿过空穴传输层(HIL)的空穴和穿过电子传输层(ETL)的电子可能移动到发射层(EML)以产生激子,因此,发射层(EML)可以发射可见光。有机化合物层可以用无机化合物层替代。

可以由基于有机基板(或塑料基板)的低温多晶硅(LTPS)或氧化物薄膜晶体管(TFT)来实现驱动元件,而不限于此。可以由基于硅晶片的CMOS晶体管来实现驱动元件。在所有像素中,驱动元件的电特性(例如,阈值电压、电子迁移率等)应该是均匀的,但是由于工艺偏差和元件特性偏差可能具有像素PIX之间发生的差异。驱动元件的电特性可能随着显示驱动时间的流逝而改变,由此,在像素PIX之间劣化程度可能具有差异。为了补偿驱动元件的电特性偏差,可以将内部补偿方法应用于电致发光显示装置。内部补偿方法可以通过使用在每个像素的像素电路中包括的内部补偿器来补偿驱动元件的电特性偏差,使得驱动元件的电特性变化不会不利地影响发光电流。内部补偿器可以包括多个开关元件,每个开关元件包括TFT(或CMOS晶体管)和至少一个电容器。

通过使用氧化物晶体管来实现像素电路的一些元件(例如,其源极或漏极连接至驱动元件的栅极的开关元件)的研究正在增加。氧化物晶体管可以包括半导体材料,例如可以包括诸如铟镓锌氧化物(IGZO)的氧化物而不是多晶硅。氧化物晶体管的电子迁移率可以是非晶硅晶体管的电子迁移率的10倍以上,并且其制造成本可以比LTPS晶体管低得多。另外,由于氧化物晶体管的截止电流低,所以在晶体管的截止时段相对较长的低速驱动中氧化物晶体管的驱动稳定性和可靠性可以很高。因此,该氧化物晶体管可以应用于需要高分辨率和低功率驱动或者不能通过LTPS工艺实现合适的画面尺寸的有机发光二极管(OLED)电视(TV)。

在本公开的实施例中,为了提高驱动稳定性和补偿可靠性这两者,可以由P沟道(PMOS)晶体管实现每个像素PIX的像素电路中包括的驱动元件和开关元件。晶体管可以各自是包括栅极、源极和漏极的三电极元件。源极可以是向晶体管供应载流子的电极。在晶体管中,载流子可以从源极开始流动。漏极可以是使载流子能够从晶体管流出的电极。在晶体管中,载流子可以从源极流到漏极。在P沟道晶体管中,由于载流子是空穴,所以源极电压可以高于漏极电压,从而空穴从源极流向漏极。在P沟道晶体管中,因为空穴从源极流到漏极,所以电流可以从源极流到漏极。特别地,应当注意,晶体管的源极和漏极不是固定的。例如,基于施加到源极和漏极的电压,源极和漏极之间可以切换。因此,本公开不受晶体管的源极和漏极限制。

参考图1和图2,时序控制器11可以为数据驱动器12提供从主机系统(未示出)传输的数字图像数据D-DATA。时序控制器11可以从主机系统接收包括垂直同步信号Vsync、水平同步信号Hsync、数据使能信号DE和点时钟DCLK的时序信号,以生成用于面板驱动电路的工作时序的多个时序控制信号。时序控制信号可以包括:栅极时序控制信号GDC,所述栅极时序控制信号GDC用于控制栅极驱动器13的工作时序;数据时序控制信号DDC,所述数据时序控制信号DDC用于控制数据驱动器12的工作时序;以及电源时序控制信号PDC,所述电源时序控制信号PDC用于控制电源电路20的工作时序。

时序控制器11可以控制面板驱动电路的工作,从而实现暂时发光方法。为此,时序控制器11可以在时间上将一帧时段划分为初始化时段、在初始化时段之后的编程时段以及在编程时段之后的发光时段。时序控制器11可以控制面板驱动电路的工作,使得在初始化时段中同时初始化所有的像素PIX。时序控制器11可以控制面板驱动电路的工作,使得基于逐行线方案(row line progressive scheme)在编程时段中对像素PIX进行编程。时序控制器11可以控制面板驱动电路的工作,使得所有像素PIX在发光时段中同时发出多束光。

参考图1和图2,数据驱动器12可以通过数据线14连接至像素PIX。数据驱动器12可以产生像素PIX的驱动所需的模拟电压DATA1至DATAm,并且可以将模拟电压DATA1至DATAm供应给数据线141至14m。模拟电压DATA1至DATAm中的每一个可以包括数据电压和基准电压。

数据驱动器12可以基于时序控制信号DDC对从时序控制器11输入的数字图像数据D-DATA进行采样和锁存,以生成并行数据,并且数模转换器(DAC)可以基于伽马补偿电压将数字图像数据D-DATA转换为模拟数据电压,并且可以通过数据线14将数据电压供应给像素PIX。数据电压可以具有与基于在像素PIX中要实现的图像灰度级的不同的电压电平相对应的模拟电压值。数据驱动器12可以进一步基于数据控制信号DDC生成基准电压,并且可以通过数据线14将基准电压供应给像素PIX。基准电压可以具有预定的固定电压电平。

数据驱动器12可以基于数据时序控制信号DDC在编程时段中输出数据电压,并且可以在初始化时段和发光时段中输出基准电压。数据驱动器12可以配置有多个源极驱动IC。每个源极驱动IC可以包括移位寄存器、锁存器、电平移位器和输出缓冲器。

参照图1和图2,栅极驱动器13可以通过栅极线15连接至像素PIX,并且可以通过初始化电压供应线IL连接至像素PIX。

栅极驱动器13可以基于栅极时序控制信号GDC生成多个扫描信号SC1至SCn,并且可以将扫描信号SC1至SCn供应给栅极线151至15n。扫描信号SC1至SCn中的每一个可以生成为在栅极导通电压与栅极截止电压之间摆动的脉冲类型。栅极导通电压可以被设定为高于晶体管的阈值电压的电压。响应于栅极导通电压,可以使晶体管导通,并且响应于栅极截止电压,可以使晶体管断开。在P沟道晶体管中,栅极导通电压可以是栅极低电压VGL,并且栅极截止电压可以是栅极高电压VGH。在下文中,栅极低电压VGL可以被表示为导通电平,并且栅极高电压VGH可以被表示为截止电平。

栅极驱动器13可以基于栅极时序控制信号GDC生成在截止电平和导通电平之间摆动的脉冲型扫描信号SC1至SCn,并且可以使脉冲型扫描信号SC1至SCn的输出时序对应于数据电压的供应时序。换言之,在编程时段中,栅极驱动器13可以按顺序地将具有导通电平的扫描信号SC1至SCn供应给栅极线151至15n,并且在初始化时段中,栅极驱动器13可以按顺序地将具有截止电平的扫描信号SC1至SCn供应给栅极线151至15n。

栅极驱动器13可以基于栅极时序控制信号GDC在初始化时段中生成在低电压电平与高电压电平之间切换的第一初始化电压Vinit,并且可以将第一初始化电压Vinit供应给初始化电压供应线IL。此外,在编程时段和发光时段中,栅极驱动器13可以生成具有低电压电平的第二初始化电压Vinit,并且可以将具有低电压电平的第二初始化电压Vinit供应给初始化电压供应线IL。初始化电压供应线IL可以共同连接至所有像素PIX,因此,可以在初始化时段中通过具有高电压电平的第一初始化电压Vinit来同时导通像素PIX的驱动元件。

栅极驱动器13可以包括栅极移位寄存器、将栅极移位寄存器的输出信号移位到适合于像素的晶体管的驱动的开关宽度的电平移位器、以及多个栅极驱动IC,每个栅极驱动IC包括输出缓冲器。可替代地,可以基于面板中栅极驱动器(GIP)类型在显示面板10的基板上直接实现栅极驱动器13。在GIP类型中,可以将电平移位器安装在印刷电路板(PCB)上,并且可以将栅极移位寄存器设置在作为显示面板10的非显示区域的边框区域中。栅极移位寄存器可以包括以级联类型彼此连接的多个扫描输出级。扫描输出级可以独立地连接至栅极线151至15n,并且可以将扫描信号SC1至SCn输出至栅极线151至15n。栅极移位寄存器可以进一步包括一个初始化输出级。初始化输出级可以连接至初始化电压供应线IL,并且可以将第一或第二初始化电压Vinit输出到初始化电压供应线IL。

参考图1和图2,电源电路20可以通过第一电源线EVL1连接至像素PIX,并且可以通过第二电源线EVL2连接至像素PIX。

电源电路20可以基于电源时序控制信号PDC处理输入电压以生成具有固定的第一电压电平的高电平驱动电源EVDD,并且可以通过第一电源线EVL1将高电平驱动电源EVDD供应给像素PIX。另外,电源电路20可以基于电源时序控制信号PDC来处理输入电源,以生成在第二电压电平与第三电压电平之间摆动的低电平驱动电源EVSS,并且可以通过第二电源线EVL2将低电平驱动电源EVSS供应给像素PIX。在此,第二电压电平可以低于第一电压电平并且高于第三电压电平。

电源电路20可以基于电源时序控制信号PDC在初始化时段和编程时段中将低电平驱动电源EVSS转变为第二电压电平,从而可以防止在初始化时段和编程时段期间所有像素PIX的非期望的发光。

主机系统可以作为移动设备、可穿戴设备、虚拟/增强现实设备等中的应用处理器(AP)。此外,主机系统可以是用于电视系统、机顶盒、导航系统、个人计算机和家庭影院系统的主板。

图3和图4是示出根据本公开的实施例的暂时发光方法的驱动时序的图。

参考图3和图4,根据本公开的实施例的暂时发光方法可以是为了在作为保持型装置的电致发光显示装置中增加运动图像响应时间(MPRT)提出的方法。暂时发光方法可以通过使用比现有技术的黑数据插入(BDI)方法更简单的驱动方法来增强MPRT特性。在BDI方法中,由于在同一帧中为了在原始图像之后显示黑图像应该施加单独的黑电压,因此成本可能提高并且驱动方案可能复杂。另一方面,在暂时发光方法中,由于不需要施加单独的黑电压,因此可以解决由BDI方法引起的问题。此外,在暂时发光方法中,由于在一帧中发光时段可调节为相对较长,因此可以以低成本实现高亮度。

在暂时发光方法中,可以在初始化时段X中将所有的像素同时初始化为第一初始化电压Vinit,可以在编程时段Y中以低压线为单位将数据电压Vdata施加于像素,并且所有的像素可以在发光时段Z中同时发射多束光。为此,可以将高电平驱动电源EVDD设定为固定至第一电压电平LV1,并且可以将低电平驱动电源EVSS设定为在第二电压电平LV2与第三电压电平LV3之间摆动。低电平驱动电源EVSS可以在初始化时段X和编程时段Y中以第二电压电平LV2施加,并且可以在发光时段Z中以低于第二电压电平LV2的第三电压电平LV3施加。

初始化时段X可以包括:供应垂直同步信号Vsync的脉冲的第一初始化时段Xl;以及供应具有高电压电平HIGH的第一初始化电压Vinit的第二初始化时段X2。如图4所示,低电平驱动电源EVSS可以从第二初始化时段X2以第二电压电平LV2施加,而不限于此,并且可以从第一初始化时段X1以第二电压电平LV2施加。

在编程时段Y中,可以以低压线为单位将数据电压Vdata按顺序地供应到多条数据线。另外,为了通过低压线单元将数据电压Vdata施加于像素,可以将具有导通电平ON的多个扫描信号SC1至SCn与数据电压Vdata的施加时序同步施加于多条栅极线。

在初始化时段X和发光时段Z中,可以将不同于数据电压Vdata的基准电压Vref施加于数据线。数据电压Vdata和基准电压Vref可以各自是用于确定发光时段Z中的发光电流的因素。

在初始化时段X和编程时段Y中发光电流可以是“0”,因此,所有的像素的发光器件可以不发光。在初始化时段X和编程时段Y期间,在像素中实现的显示图像可以是黑图像BLK,并且可以通过黑图像BLK来改善MPRT。

另一方面,在发光时段Z中可以将发光电流设定为具有与数据电压Vdata与基准电压Vref之间的差的平方成正比的亮度,并且所有像素的发光器件可以以发光电流发射多束光。在发光时段Z中,在像素中实现的显示图像可以表示灰度级亮度EML1或EML2,并且灰度级亮度可以以像素为单位变化。这是因为,对于每个像素,数据电压Vdata被不同地编程。

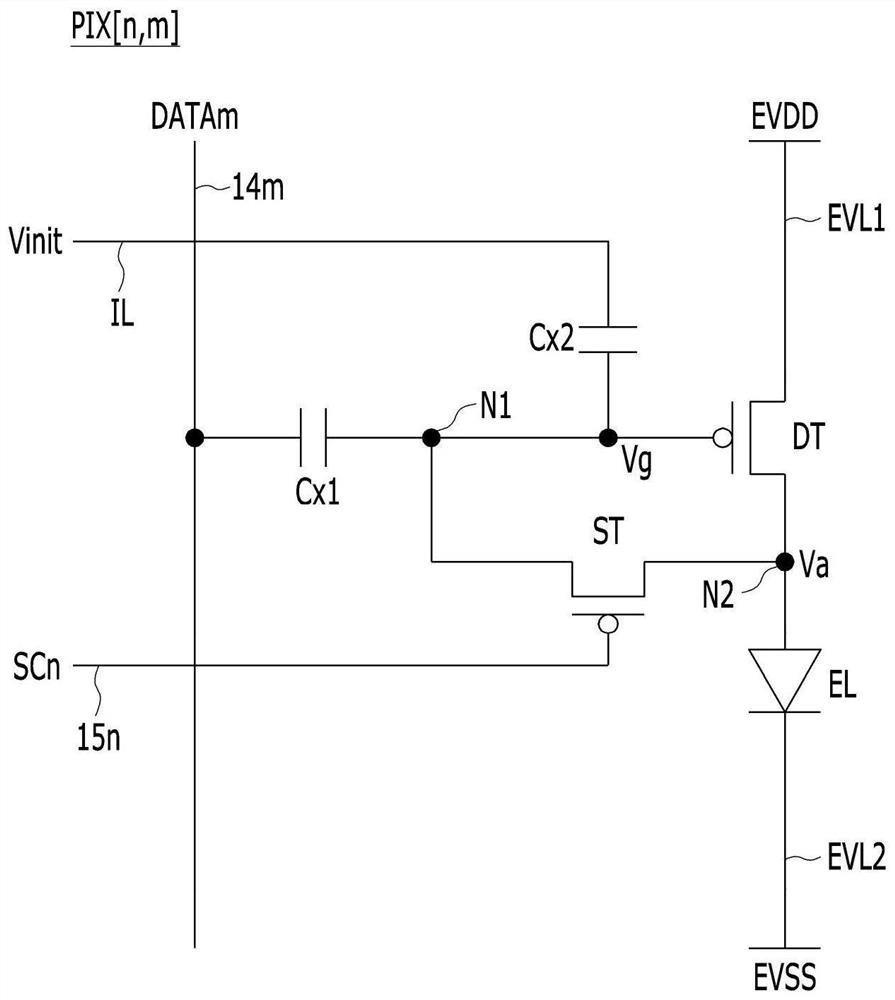

图5是示出基于暂时发光方法驱动的像素的等效电路的图。

参照图5,连接至第n栅极线15n和第m数据线14m的像素的像素电路可以包括驱动元件DT、发光器件EL和内部补偿器。

驱动元件DT可以生成用于驱动发光器件EL的电流。驱动元件DT的栅极可以连接至第一节点N1,其源极可以通过第一电源线EVL1连接至高电平驱动电源EVDD,并且其漏极可以连接至第二节点N2。为了使由发光器件EL的特性变化引起的发光电流的变化最小化,驱动元件DT可以由P沟道晶体管来实现。在驱动元件DT由P沟道晶体管实现的情况下,驱动元件DT的源极电压可以被固定为高电平驱动电源EVDD,而与发光器件EL的特性变化无关,因此,可以容易地确保亮度均匀性。

发光器件EL可以包括连接至第二节点N2的阳极、通过第二电源线EVL2连接至低电平驱动电源EVSS的阴极以及设置在阳极和阴极之间的发光层。发光器件EL可以由包括有机发光层的OLED来实现,或者可以由包括无机发光层的无机发光二极管来实现。

内部补偿器可以用于补偿驱动元件DT的阈值电压的变化,并且可以配置有一个开关元件ST和两个电容器(例如,第一电容器和第二电容器)Cx1和Cx2。内部补偿器可以对驱动元件DT的阈值电压采样,并且可以将采样的阈值电压反映在驱动元件DT的栅极电压Vg中。与驱动元件DT的阈值电压变化无关,内部补偿器可以执行补偿,从而不会因此不利地影响发光电流。因此,可以在像素中执行关于驱动元件DT的阈值电压的变化的补偿工作。这种内部补偿工作应该与校正数字图像数据的外部补偿工作进行区分,以补偿驱动元件DT的电特性变化。

开关元件ST可以被电连接(被进行二极管连接)至驱动元件DT的栅极和漏极,因此可以对驱动元件DT的阈值电压进行采样。开关元件ST的栅极可以连接至栅极线15n,其漏极和源极中的一个可以连接至第一节点N1,并且其漏极和源极的另一个电极可以连接至第二节点N2。可以基于通过栅极线15n供应的具有导通电平ON的扫描信号SCn来使开关元件ST导通。当开关元件ST导通时,驱动元件DT可以被二极管连接到开关元件ST。开关元件ST可以由P沟道晶体管来实现。当开关元件ST由P沟道晶体管实现时,与由N沟道晶体管实现开关元件ST的情况相比,截止电流(或漏电流)可以减小两倍以上。结果是,可以增加电压保持率(VHR),因此,可以提高驱动稳定性和可靠性。

第一电容器Cx1可以连接在数据线14m与第一节点N1之间,并且可以将通过数据线14m供应的模拟电压DATAm(数据电压或基准电压)通过耦接反映在第一节点N1中。为了将模拟电压14m反映在第一节点N1中,与使用单独的开关晶体管的概念相比,使用第一电容器Cx1的概念可以更多的减少栅极线的数量并简化栅极驱动器的结构。

第二电容器Cx2可以连接在初始化电压供应线IL与第一节点N1之间,并且可以将通过初始化电压供应线IL供应的第一和第二初始化电压Vinit通过耦接反映在第一节点N1中。为了将第一和第二初始化电压Vinit反映在第一节点N1中,与使用单独的开关晶体管的概念相比,使用第二电容器Cx2的概念可以更多的减少栅极线的数量并简化栅极驱动器的结构。

第二电容器Cx2的电容可被设计为大于第一电容器Cx1的电容。当第二电容器Cx2的电容被设计为大于第一电容器Cx1的电容时,用于实现图像的灰度级的数据电压的范围V0至V255可以扩大。因此,相邻灰度级电压之间的最小电压差(例如,V255至V254)可以增加,因此,可以实现对构成源极驱动IC的输出缓冲器的运算放大器OPAMP的偏移不敏感的电路。其结果是,当第二电容器Cx2的电容被设计为大于第一电容器Cx1的电容时,可以不发生偏移的不利影响,因此,可以准确地实现灰度级并且可以提高图像质量。

如上文所述,因为像素电路仅包括两个晶体管、两个电容器和一个发光器件,所以像素电路的结构可以非常简单。当简化像素电路的结构时,像素阵列中的每个像素所占的面积可以减小,因此,每英寸像素(PPI)可以增加。

图6是示出连接到第一栅极线和第m数据线的像素的驱动时序的图。图7A是示出在图6的第一初始化时段中像素的工作的图。图7B是示出在图6的第二初始化时段中像素的工作的图。图7C是示出在图6的编程时段中像素的工作的图。图7D是示出在图6的发光时段中像素的工作的图。

参照图6和图7A,具有低电压电平LOW的初始化电压Vinit、具有截止电平OFF的扫描信号SC1、基准电压Vref、具有第一电压电平LV1的高电平驱动电源EVDD以及从第三电压电平LV3转变到第二电压电平LV2的低电平驱动电源EVSS可以在第一初始化时段X1中施加到像素。开关元件ST可以被断开,此外,驱动元件DT可以被断开。而且,发光器件EL可以通过具有第二电压电平LV2的低电平驱动电源EVSS而断开。

参照图6和7B,在低电压电平LOW与高电压电平HIGH之间切换的初始化电压Vinit、具有截止电平OFF的扫描信号SC1、基准电压Vref、具有第一电压电平LV1的高电平驱动电源EVDD、以及具有第二电压电平LV2的低电平驱动电源EVSS可以在第二初始化时段X2中施加到像素。可以通过具有截止电平OFF的扫描信号SC1使开关元件ST断开。驱动元件DT的栅极电压Vg可以基于切换为低-高-低(LOW-HIGH-LOW)的初始化电压Vinit被设定为比“EVDD-Vth”低的“EVDD+Vth-γ△Vinit”。在此,“γ”可以表示C2/(C1+C2),“C1”可以表示第一电容器Cx1的电容,并且“C2”可以表示第二电容器Cx2的电容。另外,“△Vinit”可以表示初始化电压Vinit的高电压电平HIGH与低电压电平LOW之间的电压差。驱动元件DT可以被导通,因此,驱动元件DT的漏极电压Va可以是“EVDD”。发光器件EL可以基于具有第二电压电平LV2的低电平驱动电源EVSS来保持断开状态(即,黑色状态BLK)。

参照图6和图7C,具有低电压电平LOW的初始化电压Vinit、具有导通电平ON的扫描信号SC1、数据电压Vdata、具有第一电压电平LV1的高电平驱动电源EVDD以及具有第二电压电平LV2的低电平驱动电源EVSS可以在编程时段Y中施加到像素。开关元件ST可以通过具有导通电平ON的扫描信号SC1导通,并且可以将保持导通状态的驱动元件DT的栅极和漏极连接。驱动元件DT可以被二极管连接,因此,驱动元件DT的阈值电压Vth可以被采样并且可以被反映在驱动元件DT的栅极电压Vg和漏极电压Va中。换言之,驱动元件DT的栅极电压Vg和漏极电压Va可以是“EVDD-Vth”。发光器件EL可以基于具有第二电压电平LV2的低电平驱动电源EVSS来保持断开状态(即,黑色状态BLK)。数据电压Vdata可以被充入到第一电容器Cx1的一个电极中。

参考图6和图7D,具有低电压电平LOW的初始化电压Vinit、具有截止电平OFF的扫描信号SC1、基准电压Vref、具有第一电压电平LV1的高电平驱动电源EVDD以及具有第三电压电平LV3的低电平驱动电源EVSS可以在发光时段Y中施加到像素。开关元件ST可以通过具有截止电平OFF的扫描信号SC1被断开,并且可以解除驱动元件DT的栅极与漏极之间的连接。第一电容器Cx1的一个电极处的电压可以从数据电压Vdata改变为基准电压Vref。第一电容器Cx1的电压变化“Vref-Vdata”可以基于耦接作用被反映在第一节点N1中。结果是,驱动元件DT的栅极电压Vg可以是“(EVDD-Vth)-α(Vref-Vdata)”。在此,“α”可以是“C1/(C1+C2)”。可以基于在驱动元件DT中流动的电流将驱动元件DT的漏极电压Va设定为发光器件EL的阈值电压Voled。此时,可以通过具有第三电压电平LV3的低电平驱动电源EVSS将发光器件EL置于导通状态(即,发光状态EML)。在发光器件EL中流动的发光电流Ioled可以如下式1被确定,而与驱动元件DT的阈值电压Vth无关。

[式1]

Ioled=k[α(Vref-Vdata)]

在式1中,K可以表示基于驱动元件的电子迁移率、寄生电容和沟道电容确定的常数值,α可以表示C1/(C1+C2),C1可以表示第一电容器的电容,C2可以表示第二电容器的电容,Vref可以表示基准电压,Vdata可以表示数据电压。

图8是示出关于发光电流的变化相对于发光器件的特性变化与现有技术进行比较而获得的结果的图。

图8(a)示出了当驱动元件由NMOS晶体管实现时发光电流相对于发光器件的特性(例如,温度等)的变化(例如,劣化)的变化。另外,图8(b)示出了当驱动元件由PMOS晶体管实现时,发光电流相对于发光器件的特性(例如,温度等)的变化(例如,劣化)的变化。在图8(a)和(b)的曲线图中,纵轴表示发光电流Ioled,横轴表示高电平驱动电源EVDD。

参照图8,当基于全白亮度在发光器件中长时间流过发光电流时,发光器件劣化,因此,示出发光器件的工作的EL电流-电压曲线可以从实线变为虚线。

在这种情况下,如图8(a)所示,在驱动元件由NMOS晶体管实现的模型(比较技术)中,由于发光器件的劣化,驱动元件的源极电压改变,并且基于此,示出驱动元件的工作的DT电流-电压曲线可以从实线改变为虚线。因此,EL电流-电压曲线与DT电流-电压曲线相交的工作点从Ioled1改变为Ioled2或Ioled3。Ioled2或Ioled3与Ioled1之间的电流偏差很大。因此,可能会发生非期望的亮度失真。

另一方面,如图8(b)所示,在驱动元件由PMOS晶体管实现的模型(本公开的实施例)中,由于发光器件的劣化导致驱动元件的漏极电压而不是源极电压发生改变,并且源极电压是固定的,因此示出驱动元件的工作的DT电流-电压曲线可以保持实线。另外,即使当EL电流-电压曲线与DT电流-电压曲线相交的工作点从Ioled1变为Ioled2或Ioled3时,在Ioled2或Ioled3与Ioled1之间可能也几乎不会发生电流偏差,因此可以防止非期望的亮度失真的发生。

如上所述,根据本公开的实施例,可以获得以下效果。

根据本公开的实施例,可以通过使用包括PMOS晶体管的简单的像素结构来设定发光电流,而与驱动元件的阈值电压的变化无关,从而提高了产品的可靠性和驱动稳定性。

根据本公开的实施例,通过使用包括PMOS晶体管的简单的像素结构,可以使由发光器件的特性(例如,温度等)的变化(例如,劣化)引起的发光电流的失真最小化,从而提高了产品的可靠性和驱动稳定性。

根据本公开的实施例,可以通过使用包括PMOS晶体管的简单的像素结构来提高VHR特性,从而提高产品的可靠性和驱动稳定性。

根据本公开的实施例,可以通过使用包括PMOS晶体管的简单的像素结构来减小被像素阵列中的每个像素占据的面积,从而增加PPI。

根据本公开的实施例,通过使用暂时发光方法,可以基于比传统的BDI方法更简单的驱动方法来提高MPRT特性。

根据本公开的效果不限于以上示例,并且在说明书中可以包括其他各种效果。

尽管已经参考本公开的示例性实施例具体示出和描述了本公开,但是本领域普通技术人员将理解,在不脱离如所附权利要求书限定的本公开的精神和范围的情况下,可以在形式和细节上进行各种改变。