一种基于SV和UVM的可控时钟复位信号生成模块及生成方法

文献发布时间:2023-06-19 19:21:53

技术领域

本发明属于芯片测试技术领域,具体涉及一种基于SV和UVM的可控时钟复位信号生成模块、一种基于UVM的定时器验证平台,以及定时器验证平台中可编辑时钟复位信号的生成方法。

背景技术

目前,随着集成电路制造技术的发展,芯片的集成度在不断的提高,其内部集成的知识产权(Intellectual Property,IP)模块的数量也越来越多且功能复杂。同时,因为工艺制程的提升和市场对产品缺陷的容忍度越来越低,每次流片失败所带来的损失也越来越大,因此越来越多的公司重视流片前的验证工作。在如今大多数的集成电路设计公司中,芯片验证所需要的人力,时间在整个芯片研发过程中所占的比例高达70%。

传统的验证方法学是基于Verilog语言搭建验证平台,重用性比较差且不能够覆盖全部的待测功能点,这大大降低了验证效率,增加了芯片研发的时间和成本。在此基础上,技术人员基于System Verilog验证语言开发并推广应用了一套完整源码库的验证平台开发框架,即:通用验证方法学(UVM,Universal Verification Methodology)。验证工程师可以以UVM提供的源码库为基础构建满足待测设计的功能验证环境,根据UVM验证方法学搭建的验证平台可以实现随机测试激励产生、结果自动比对以及高收集功能覆盖率等功能,目前已成为芯片验证领域的主流方法。

在芯片验证过程,为了提高验证工作的方便性以及验证环境的可重用性,EDA厂商普遍推出了验证IP(Verification IP,VIP)系统。VIP是一种预定义的功能块,可以插入到验证环境中加快验证环境的开发,从而提高工作效率。

然而,在现有各类测试平台的验证方案中,时钟复位信号基本都是在测试的顶层文件中利用initial和always语句生成的。在仿真过程中通常无法临时更改时钟复位信号的值,随意更改不仅比较繁琐且容易导致测试方案出错。这导致在现有各类不同框架的验证系统中,一方面,验证芯片不同功能的时钟频率时往往需要去修改顶层测试文件代码,因而需要重新编译顶层文件,这会影响仿真速度。另一方面,传统Verilog生成的时钟和复位信息无法进行复用,在验证不同模块时,都需要人为的去修改测试顶层中的信号值,若时钟复位信号众多时编写繁琐。

发明内容

为了解决传统验证环境存在的时钟复位信号的值无法灵活编辑,验证方案的所有内容需要在仿真前确定,无法临时更改,测试效率低等问题,本发明提供一种基于SV和UVM的可控时钟复位信号生成模块、一种基于UVM的定时器验证平台,以及定时器验证平台中可编辑时钟复位信号的生成方法。

本发明采用以下技术方案实现:

一种基于SV和UVM的可控时钟复位信号生成模块,其采用SV语言编写并利用UVM提供的源码库为基础进行搭建。该可控时钟复位信号生成模块用于在测试平台中向待测模块提供所需的时钟复位信号作为激励信号。具体地,本发明提供的可控时钟复位(rcc,resetclock control)信号生成模块的模块架构中包括:rcc接口、rcc配置类、rcc环境顶层、序列库,以及rcc事务类。

其中,rcc接口内包含N个虚拟时钟组接口,每个虚拟时钟组接口用于与各个待测模块进行通信连接。虚拟时钟组接口中声明了N个时钟信号和一个复位信号。

rcc配置类内定义了一个时钟复位组代理个数变量和N个时钟组配置。每个时钟组配置用于定义复位信号、复位延时信号和时钟使能信号,并赋予其一个默认值。时钟组配置还用于声明虚拟接口的句柄并创建rcc事务类对象。

rcc环境顶层内声明了一个rcc虚拟接口句柄、一个rcc配置句柄,以及N组时钟复位组代理。rcc虚拟接口句柄中包含N个虚拟时钟组接口句柄;每个虚拟时钟组接口句柄和rcc接口中的一个虚拟时钟组接口对接,进而在时钟复位组代理和待测模块间构建通信链路。rcc配置句柄用于在rcc配置类和rcc环境顶层中的各个时钟复位组代理间建立通信链路,以实现根据rcc配置类中的配置信息调整各个各个时钟复位组代理的运行状态。每个时钟复位组代理中均声明了时钟组配置句柄、序列发送器和驱动器。

序列库用于根据具体的时钟复位信号配置需求以调用内部序列最终形成对应的测试用例。序列库中包含四个用于控制激励信号中的时钟信号和复位释放信号的功能序列,分别为时钟频率配置序列、自动复位释放序列、只复位序列和只释放序列。其中,时钟频率配置序列用于调制时钟频率。自动复位释放序列按照默认的复位保持时间实现自动复位。只复位序列和只释放序列用于实现对复位保持时间进行自主调节。

rcc事务类中创建了N个clk事务类且封装对应时钟复位的属性配置。rcc事务类中包括N个时钟使能信号、复位请求信号和复位释放信号,在clk事务类中对时钟延时、占空比和时钟频率等信息进行默认配置。

作为本发明进一步的改进,在rcc环境顶层建立的相位中,rcc配置句柄从rcc环境顶层外部得到配置信息以及rcc虚拟接口句柄;然后根据所获取的rcc配置类中的时钟复位组代理个数变量的值来例化时钟复位组代理数量。可控时钟复位信号生成模块根据项目的需求最多支持将N个rcc虚拟接口句柄传递给对应的时钟复位组代理。

作为本发明进一步的改进,时钟复位组代理在其建立相位中实例化了序列发送器和驱动器,并从N个时钟组配置中得到相应的信息并将其传到驱动器中。在时钟复位组代理链接相位中还通过TLM机制将序列发送器中的事务发送端口和驱动器的事务接收端口进行通信连接,并将驱动器的虚拟接口句柄与虚拟时钟组接口句柄进行通信连接。

作为本发明进一步的改进,驱动器中声明时钟组配置句柄、虚拟接口句柄和clk事务类句柄。驱动器在其建立的相位中得到配置信息,然后在其链接相位中声明rcc事务类句柄,将得到的时钟相关信息配置赋值给clk事务类,将复位信号的相关信息赋值给rcc事务类,最后驱动器将事务中的驱动信号依次通过rcc虚拟接口句柄和rcc接口传输给待测模块。

作为本发明进一步的改进,在rcc事务类中各个clk事务类的默认配置信息中,时钟延时默认为0、占空比为50%、时钟频率为6MHZ信息。同时,各个clk事务类包含了预设的时钟变量初始化函数和时钟周期产生函数,以实现在不同项目中根据需要对时钟变量和时钟周期进行调整。

作为本发明进一步的改进,rcc配置类中创建的各个时钟组配置分别用于对各个时钟复位组代理进行配置;同时,rcc配置类还在内部定义了一个时钟复位组代理个数变量用于配置开启时钟复位组代理的个数,时钟复位组代理个数变量的默认值为1。

在每个时钟组配置定义的复位信号、复位延时信号和时钟使能信号中,默认配置为低电平复位、复位延时为213.73μs、时钟使能信号全部关闭。同时,每个时钟组配置内部声明了对应的rcc虚拟接口句柄并创建rcc事务类对象,用于将顶层的时钟配置信息及时更新到事务中,并通过驱动器传递到待测模块上。

作为本发明进一步的改进,序列库为一个System Verilog格式的文件,序列库内部编写了时钟频率配置序列、自动复位释放序列、只复位序列和只释放序列。四种序列的功能的用法如下:

(1)时钟频率配置序列单独使用,进而实现根据待测模块在不同测试项目中对特定频率的要求灵活配置时钟信号,以保证模块的功能准确性。

(2)自动复位释放序列单独使用,进而实现复位信号拉低到默认低电平状态后213.73μs释放,即实现默认自动复位释放的复位功能。自动复位释放序列用于检验待测模块在复位后各寄存器的值是否正常,以满足功能模块在大部分自动复位测试任务中的验证需求。

(3)只复位序列和只释放序列配合使用:进而实现根据项目需要对复位保持时间进行灵活控制,在验证某些非默认复位保持时间下的项目,或者满足某些情景对复位保持时间的特定要求。

作为本发明进一步的改进,可控时钟复位信号生成模块根据项目某种场景需求生成一个虚拟序列并确定对应的测试用例。虚拟序列调用了序列库中的对应序列,并在时钟频率配置序列中调用了预先创建的rcc事务类。序列发送器将生成的虚拟序列发送给对应的时钟复位组代理中的驱动器执行。

本发明还包括一种基于UVM的定时器验证平台,其结合如前述的基于SV和UVM的可控时钟复位信号生成模块的架构设计,进而用于对定时器进行功能验证。定时器验证平台包括由硬件和接口部分组成的测试平台,以及由软件部分构成的测试层。

其中,测试平台内包括一个用于与待测模块连接的rcc接口;rcc接口中包含一个对应的虚拟时钟组接口0。虚拟时钟组接口0与测试层中的rcc虚拟接口句柄中的虚拟时钟组接口句柄0连接后,支持待测模块与测试层之间进行双向通信;实现通过UVM中的config_db机制将rcc接口信号最终传递到驱动器中,进而利用run_test()启动测试层。

测试层中例化了rcc配置类和rcc环境顶层;rcc配置类用于对定时器验证平台中的时钟复位组代理个数以及时钟复位信息进行配置,然后通过config_db传到rcc环境顶层中的rcc配置句柄。rcc环境顶层中得到rcc配置类中的配置信息,然后将配置信息传到驱动器中。测试层中例化了rcc配置类、rcc环境顶层,并生成一个与测试用例对应的虚拟序列。虚拟序列中应用了时钟频率配置序列和自动复位释放序列,时钟频率配置序列调用了预先创建的rcc事务类。序列发送器将生成的虚拟序列发送到所述驱动器中;驱动器得到配置信息以及虚拟序列后,将包含对应时钟频率的时钟信号以及相应复位保持时间的复位信号的驱动信号发送到待测模块,作为待测模块的激励信号。

本发明还包括一种定时器验证平台中可编辑时钟复位信号的生成方法,其用于在前述的基于UVM的定时器验证平台中,通过生成的时钟信号和复位信号实现对定时器的默认时钟进行调整,并实现自动复位释放。时钟复位信号的生成方法包括如下步骤:

S1:分析待测模块的工作时钟,确定其包括外部时钟extclk和APB时钟pclk以及一个APB复位prst_n;且在默认情况下pclk频率为6MHZ,extclk为32KHZ。

S2:在测试平台中例化待测模块和rcc接口,将rcc接口的虚拟时钟组接口0的gclk[0]、gclk[1]和reset信号分别与待测模块的pclk、extclk和prst_n连接;然后通过config_db机制传到rcc环境顶层中rcc虚拟接口句柄的虚拟时钟组接口句柄0中,虚拟时钟组接口句柄0在接收到虚拟时钟组接口0中的信息后最终传递给驱动器;

S3:根据待测模块的默认时钟信号频率在测试层中的rcc配置类中设置时钟复位组代理个数变量为1,从而打开时钟组配置0,在时钟组配置0中设置gclk[0]和gclk[1]的默认时钟信号频率分别为6MHZ和32KHZ。

S4:根据实际场景需求判断是否需要在仿真过程中改变待测模块的默认时钟复位配置以及复位信号是否自动释放:

(1)若需要改变默认配置,则执行步骤S5~S9。

(2)若不需更改默认配置,则跳转执行步骤S10~S12。

S5:根据待测模块在特殊的应用场景需求下得出:APB时钟pclk为3MHZ,外部时钟extclk为6KHZ,以及需要在仿真过程中进行复位自动释放。

S6:利用序列库在虚拟序列中创建时钟频率配置序列和自动复位释放序列。时钟频率配置序列中创建了rcc事务类,定义了复位请求、复位释放和时钟使能信号,然后将配置值赋值到clk事务类中;在配置信息中,pclk为3KHZ,extclk为6KHZ;自动复位释放序列继承于时钟频率配置序列,内部将复位请求和复位释放信号都置1。

S7:在测试层中编写对应的测试用例,最后采用default_sequence的方式将虚拟序列挂载到序列发送器上。

S8:在测试平台中通过run_test()启动后序列发送器接收到虚拟序列中rcc事务类的信息并传递给驱动器。

S9:驱动器在接收到rcc事务类信息并进行相应数据处理后,通过虚拟时钟组接口0将gclk[0]、gclk[1]和reset信号发送至待测模块,待测模块接收到信号后正常工作。

S10:在测试层中编写对应的测试用例,最后采用default_sequence的方式将虚拟序列挂载到序列发送器上。

S11:在测试平台中通过run_test()成功启动后将rcc配置类中设置好的信号传到rcc配置句柄中,rcc配置句柄在接收到设置好的信号后再传递到时钟组配置句柄0中,然后,由时钟组配置句柄0将得到的gclk[0]和gclk[1]信号和reset信号传入驱动器。

S12:驱动器在接收到时钟组配置句柄0中的信息并进行相应数据处理后,最终通过虚拟时钟组接口0将gclk[0]、gclk[1]和reset信号发送至待测模块,待测模块接收到信号后正常工作。

本发明提供的技术方案,具有如下有益效果:

1.本发明使用System Verilog语言编写,采用目前最主流的UVM验证方法学搭建VIP环境,与传统的采用verilog产生时钟复位信号方法相比,其具有很强的复用性,该VIP不仅仅局限于IP模块级验证平台,也可复用于系统级芯片验证平台,可以将该VIP集成于任何UVM环境中使用,能够任意配置多组时钟复位信号,使得在一些复杂的IP和系统级芯片中应用更加方便。

2.调用该VIP产生的时钟具有独立性且可同时配置多个时钟,在给待测模块输入不同的频率的时钟时只需要在rcc配置序列中去配置即可,不需要重新编译顶层模块,因此可以提高验证系统的灵活性,并答复提升验证系统的工作效率;同时,还可以有效抑制因时钟信号频率和复位保持时间调整对验证过程造成的错误。

3.本发明提供的可控时钟复位信号生成模块及其方法,在时钟复位信号通过调用时钟复位验证IP产生后,可以通过UVM中的sequence机制在仿真过程中随时改变时钟复位信号的值。相比于verilog写的顶层模块能够更灵活全面地模拟一些特殊的应用场景;进一步提升验证系统对不同任务和对象时的通用性。

附图说明

附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。在附图中:

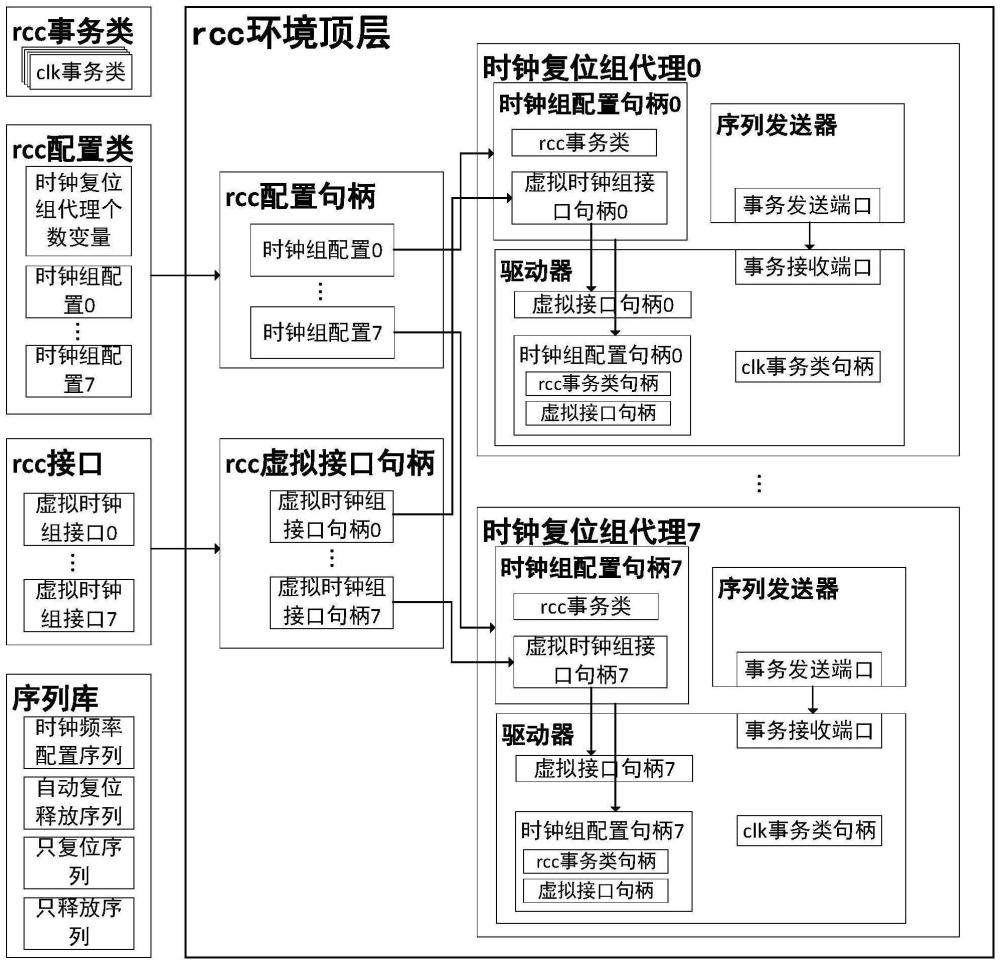

图1为本发明实施例1提供的一种基于SV和UVM的可控时钟复位信号生成模块的模块架构图。

图2为本发明实施例1中,可控时钟复位信号生成模块在三种典型场景下的运行流程图。

图3为本发明实施例1中的基于SV和UVM的可控时钟复位信号生成模块仿真过程中的波形图。

图4为本发明实施例2中提供的一种基于UVM的定时器验证平台的平台架构框图。

图5为本发明实施2中定时器验证平台生成不同类型的时钟复位信号的步骤流程图。

具体实施方式

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

实施例1

本实施例提供一种基于SV和UVM的可控时钟复位信号生成模块,其采用SV语言编写并利用UVM提供的源码库为基础进行搭建。该型可控时钟复位信号生成模块用于在测试平台中向待测模块提供所需的时钟复位信号作为激励信号。具体地,如图1所示,本实施例提供的可控时钟复位(rcc,reset clock control)信号生成模块的模块架构中包括:rcc接口、rcc配置类、rcc环境顶层、序列库,以及rcc事务类。具体地,本案图1中的可控时钟复位信号生成模块的架构包含8个独立的通道,各个通道可在不同的任务中独立完成各自的信号生成任务。其中,本实施例中的8个通道仅是本案设计的典型的通用架构,该架构基本可以满足常规验证平台的性能需求。当然,在硬件性能支持的条件下,也可以根据需求配置不同的通道数。

具体地,在本实施例的方案中,rcc接口内包含N个虚拟时钟组接口,每个虚拟时钟组接口用于与各个待测模块进行通信连接。rcc接口中声明了N个时钟信号和一个复位信号。

rcc配置类内定义了一个时钟复位组代理个数变量和N个时钟组配置。每个时钟组配置用于定义复位信号、复位延时信号和时钟使能信号,并赋予其一个默认值。时钟组配置还用于声明虚拟接口的句柄并创建rcc事务类对象。

rcc配置类中创建的各个时钟组配置分别用于对各个时钟复位组代理进行配置;同时,rcc配置类还在内部定义了一个时钟复位组代理个数变量用于配置开启时钟复位组代理的个数,时钟复位组代理个数变量的默认值为1。

在每个时钟组配置定义的复位信号、复位延时信号和时钟使能信号中,默认配置为低电平复位、复位延时为213.73μs、时钟使能信号全部关闭。同时,每个时钟组配置内部声明了对应的rcc虚拟接口句柄并创建rcc事务类对象,用于将顶层的时钟配置信息及时更新到事务中,并通过驱动器传递到待测模块上。

rcc环境顶层内声明了一个rcc虚拟接口句柄、一个rcc配置句柄,以及N组时钟复位组代理。rcc虚拟接口句柄中包含N个虚拟时钟组接口句柄;每个虚拟时钟组接口句柄和rcc接口中的一个虚拟时钟组接口对接,进而在时钟复位组代理和待测模块间构建通信链路。rcc配置句柄用于在rcc配置类和rcc环境顶层中的各个时钟复位组代理间建立通信链路,以实现根据rcc配置类中的配置信息调整各个各个时钟复位组代理的运行状态。每个时钟复位组代理中均声明了时钟组配置句柄、序列发送器和驱动器。

在rcc环境顶层建立的相位中,rcc配置句柄从rcc环境顶层外部得到配置信息以及rcc虚拟接口句柄;然后根据所获取的rcc配置类中的时钟复位组代理个数变量的值来例化时钟复位组代理数量。可控时钟复位信号生成模块根据项目的需求最多支持将N个rcc虚拟接口句柄传递给对应的时钟复位组代理。

时钟复位组代理在其建立相位中实例化了序列发送器和驱动器,并从N个时钟组配置中得到相应的信息并将其传到驱动器中。在时钟复位组代理的链接相位中还通过TLM机制将序列发送器中的事务发送端口和驱动器的事务接收端口进行通信连接,并将驱动器的虚拟接口句柄与虚拟时钟组接口句柄进行通信连接。

驱动器中声明时钟组配置句柄、虚拟接口句柄和clk事务类句柄。驱动器在其建立的相位中得到配置信息,然后在其链接相位中声明rcc事务类句柄,将得到的时钟相关信息配置赋值给clk事务类,将复位信号的相关信息赋值给rcc事务类,最后驱动器将事务中的驱动信号依次通过rcc虚拟接口句柄和rcc接口传输给待测模块。

序列库用于接收时钟复位组代理的调用以形成对应的测试用例。序列库中包含四个用于控制激励信号中的时钟信号和复位释放信号的功能序列,分别为时钟频率配置序列、自动复位释放序列、只复位序列和只释放序列。其中,时钟频率配置序列用于调制时钟频率。自动复位释放序列按照默认的复位保持时间实现自动复位。只复位序列和只释放序列用于实现对复位保持时间进行自主调节。

序列库为一个System Verilog格式的文件,序列库内部编写了时钟频率配置序列、自动复位释放序列、只复位序列和只释放序列。四种序列的功能的用法如下:

(1)时钟频率配置序列单独使用,进而实现根据待测模块在不同测试项目中对特定频率的要求灵活配置时钟信号,以保证模块的功能准确性。

(2)自动复位释放序列单独使用,进而实现复位信号拉低到默认低电平状态后213.73μs释放,即实现默认自动复位释放的复位功能。自动复位释放序列用于检验待测模块在复位后各寄存器的值是否正常,以满足功能模块在大部分自动复位测试任务中的验证需求。

(3)只复位序列和只释放序列配合使用:进而实现根据项目需要对复位保持时间进行灵活控制,在验证某些非默认复位保持时间下的项目,或者满足某些情景对复位保持时间的特定要求。

rcc事务类中创建了N个clk事务类且封装对应时钟复位的属性配置。rcc事务类中包括N个时钟使能信号、复位请求信号和复位释放信号,在clk事务类中对时钟延时、占空比和时钟频率等信息进行默认配置。

在rcc事务类中各个clk事务类的默认配置信息中,时钟延时默认为0、占空比为50%、时钟频率为6MHZ信息。同时,各个clk事务类包含了预设的时钟变量初始化函数和时钟周期产生函数,以实现在不同项目中根据需要对时钟变量和时钟周期进行调整。

可控时钟复位信号生成模块根据项目某种场景需求生成一个虚拟序列并确定对应的测试用例。虚拟序列调用了序列库中的对应序列,并在时钟频率配置序列中调用了预先创建的rcc事务类。序列发送器将生成的虚拟序列发送给对应的时钟复位组代理中的驱动器执行。

在本实施例提供的如图1的基于SV和UVM的可控时钟复位信号生成模块中。可实现典型场景大致包括三种类型:第一种是实现对具体的时钟参数的灵活配置。第二种是实现自动复位以及释放,复位保持时间为默认值。第三种是实现“手动”复位以及释放,复位保持时间可以根据需要进行任意配置。

本实施例实现的三种不同应用场景中验证平台的运行过程大致如图2所示,包括如下的过程:

首先,在测试平台中例化待测模块和rcc接口,将rcc接口的虚拟时钟组接口中的时钟复位信号分别与待测模块的时钟复位信号连接;然后通过config_db机制传到rcc环境顶层中rcc虚拟接口句柄的虚拟时钟组接口句柄中,虚拟时钟组接口句柄在接收到虚拟时钟组接口中的信息后最终传递给驱动器。

其次,根据不同场景需求在虚拟序列中例化并启动序列库中相应的序列。例如,当采用时钟频率配置序列和自动复位释放序列为例来验证是否成功实现在仿真过程中改变时钟频率等信息以及自动复位和释放的过程时。时钟频率配置序列中创建了rcc事务类,定义了复位请求、复位释放和时钟使能信号(用于打开时钟个数),然后将配置值赋值到clk事务类中,具体配置APB时钟pclk为3KHZ,外部时钟extclk为6KHZ。自动复位释放序列继承于时钟频率配置序列,内部只是将复位请求和复位释放信号都置1,最后通过序列发送器发送到驱动器中,后者内部接收到配置的事务类后将其传到定时器模块的接口上。

此时,虚拟序列中部分代码如下:

rcc_reset_auto_sequencerst_at_seq;

rcc_common_sequencercc_seq;

rcc_seq=new("rcc_seq");

rcc_seq.h_clock_req='h3;

rcc_seq.h_gclk[0].clk_unit=KHZ;

rcc_seq.h_gclk[0].clk_freq=3;

rcc_seq.h_gclk[1].clk_unit=KHZ;

rcc_seq.h_gclk[1].clk_freq=6;

#10

rst_at_seq=new("rst_at_seq");

rst_at_seq.start(p_sequencer.rcc_sqr);

rcc_seq.start(p_sequencer.rcc_sqr);

接着,编写对应的测试用例继承于测试层。由于某个待测模块在通常情况下外部工作时钟extclk为32KHZ,APB时钟为6MHZ,则在rcc配置类中只需要打开一个时钟复位组,开启两个时钟使能以及配置上述时钟频率作为默认值,最后采用default_sequence的方式将虚拟序列挂载到虚拟发送器上启动对应的序列。

其中,rcc配置类中部分代码如下:

group_num=1;

gp_cfg[0].clk_en='b11;

gp_cfg[0].gp_rcc_tr.gclk[0].clk_freq=6;

gp_cfg[0].gp_rcc_tr.gclk[0].clk_unit=MHZ;

gp_cfg[0].gp_rcc_tr.gclk[1].clk_unit=KHZ;

gp_cfg[0].gp_rcc_tr.gclk[1].clk_freq=32;

最后,测试平台中通过run_test()启动UVM验证平台,根据上一步骤的测试用例名字产生一个uvm_test_top实例,然后依次执行uvm_test的各个组件,按照phase机制执行,所有phase执行完毕后结束仿真。

图3为验证平台在图2的步骤执行后的仿真波形示意图,从波形图中可以看出,在仿真过程中调用时钟频率配置序列后,APB时钟pclk将会从6MHZ变为3KHZ,外部工作时钟extclk从32KHZ变为6KHZ,复位信号在调用了自动复位释放序列后,其将在拉低后213.73μs后释放,该时间为时钟复位验证IP中的默认配置。

实施例2

在实施例1方案的基础上,本实施例进一步提供一种基于UVM的定时器验证平台,其结合如实施例1的基于SV和UVM的可控时钟复位信号生成模块的架构设计,进而用于对定时器进行功能验证。如图4所示,定时器验证平台包括由硬件和接口部分组成的测试平台,以及由软件部分构成的测试层。

其中,测试平台内包括一个用于与待测模块连接的rcc接口;rcc接口中包含一个对应的虚拟时钟组接口0。虚拟时钟组接口0与测试层中rcc虚拟接口句柄中的虚拟时钟组接口句柄0连接后,支持待测模块与测试层之间进行双向通信;实现通过UVM中的config_db机制将rcc接口信号最终传递到驱动器中,进而利用run_test()启动测试层。

测试层中例化了rcc配置类和rcc环境顶层;rcc配置类用于对定时器验证平台中的时钟复位组代理个数以及时钟复位信息进行配置,然后通过config_db传到rcc环境顶层中的rcc配置句柄。rcc环境顶层中得到rcc配置类中的配置信息,然后将配置信息传到驱动器中。测试层中例化了rcc配置类、rcc环境顶层,并生成一个与测试用例对应的虚拟序列。虚拟序列中应用了时钟频率配置序列和自动复位释放序列,时钟频率配置序列调用了预先创建的rcc事务类。序列发送器将生成的虚拟序列发送到所述驱动器中;驱动器得到配置信息以及虚拟序列后,将包含对应时钟频率的时钟信号以及相应复位保持时间的复位信号的驱动信号发送到待测模块,作为待测模块的激励信号。

在本实施例提供的基于UVM的定时器验证平台中,通过生成的时钟信号和复位信号实现对定时器的默认时钟进行调整,并实现自动复位释放。如图5所示,时钟复位信号的生成方法包括如下步骤:

S1:分析定时器模块的工作时钟,确定其包括外部时钟extclk和APB时钟pclk以及一个APB复位prst_n;且在默认情况下pclk频率为6MHZ,extclk为32KHZ。

S2:在测试平台中例化定时器模块和rcc接口,将rcc接口的虚拟时钟组接口0的gclk[0]、gclk[1]和reset信号分别与定时器模块的pclk、extclk和prst_n连接;然后通过config_db机制传到rcc环境顶层中rcc虚拟接口句柄的虚拟时钟组接口句柄0中,虚拟时钟组接口句柄0在接收到虚拟时钟组接口0中的信息后最终传递给驱动器。

S3:根据定时器模块的默认时钟信号频率在测试层中的rcc配置类中设置时钟复位组代理个数变量为1,从而打开时钟组配置0,在时钟组配置0中设置gclk[0]和gclk[1]的默认时钟信号频率分别为6MHZ和32KHZ。

S4:根据实际场景需求判断是否需要在仿真过程中改变定时器模块的默认时钟复位配置以及复位信号是否自动释放:

(1)若需要改变默认配置,则执行步骤S5~S9。

(2)若不需更改默认配置,则跳转执行步骤S10~S12。

S5:根据定时器模块在特殊的应用场景需求下得出:APB时钟pclk为3MHZ,外部时钟extclk为6KHZ,以及需要在仿真过程中进行复位自动释放。

S6:利用序列库在虚拟序列中创建时钟频率配置序列和自动复位释放序列。时钟频率配置序列中创建了rcc事务类,定义了复位请求、复位释放和时钟使能信号,然后将配置值赋值到clk事务类中;在配置信息中,pclk为3KHZ,extclk为6KHZ;自动复位释放序列继承于时钟频率配置序列,内部将复位请求和复位释放信号都置1。

S7:在测试层中编写对应的测试用例,最后采用default_sequence的方式将虚拟序列挂载到序列发送器上。

S8:在测试平台中通过run_test()启动后序列发送器接收到虚拟序列中rcc事务类的信息并传递给驱动器。

S9:驱动器在接收到rcc事务类信息并进行相应数据处理后,通过虚拟时钟组接口0将gclk[0]、gclk[1]和reset信号发送至定时器模块,定时器模块接收到信号后正常工作。

S10:在测试层中编写对应的测试用例,最后采用default_sequence的方式将虚拟序列挂载到序列发送器上。

S11:在测试平台中通过run_test()成功启动后将rcc配置类中设置好的信号传到rcc配置句柄中,rcc配置句柄在接收到设置好的信号后再传递到时钟组配置句柄0中,然后,由时钟组配置句柄将得到的gclk[0]和gclk[1]信号和reset信号传入驱动器。

S12:驱动器在接收到时钟组配置句柄0中的信息并进行相应数据处理后,最终通过虚拟时钟组接口0将gclk[0]、gclk[1]和reset信号发送至定时器模块,定时器模块接收到信号后正常工作。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

- 一种时钟信号生成装置及时钟信号生成方法

- 一种时钟信号生成装置及时钟信号生成方法