发光显示装置

文献发布时间:2024-04-18 19:44:28

技术领域

本发明涉及一种显示装置,更具体而言,涉及一种包括发光二极管的发光显示装置。

背景技术

发光显示装置可以包括与像素相对应的发光二极管(light emitting diodes),并控制各个发光二极管的亮度来显示图像。与液晶显示装置之类受光型显示装置不同,发光显示装置不需要背光(backlight)之类光源,因此,可以减少厚度和重量。另外,发光显示装置具有高亮度、高对比度、高颜色再现性、高反应速度等特性,因此,可以显示高质量的图像。

由于这种优点,发光显示装置适用于智能电话、平板、笔记本计算机之类移动装置、监视器、电视机等各种电子装置,作为汽车用显示装置备受瞩目。

发明内容

实施例用于提供一种能够改善像素的特性差异导致的显示质量降低的发光显示装置。

根据一实施例的发光显示装置包括:第一像素,显示第一颜色并包括第一发光二极管以及与所述第一发光二极管连接的第一像素电路部;以及第二像素,显示第二颜色并包括第二发光二极管以及与所述第二发光二极管连接的第二像素电路部。所述第一像素电路部包括与所述第一发光二极管的第一电极连接而传输初始化电压的初始化晶体管,所述初始化晶体管包括接收栅极导通电压的第一栅极电极以及第二栅极电极。所述第二像素电路部包括与所述第二发光二极管的第一电极连接而传输初始化电压的初始化晶体管,所述初始化晶体管包括接收栅极导通电压的第一栅极电极。

可以是,所述第一像素电路部的所述第一栅极电极和所述第二栅极电极电连接。

可以是,所述第一像素电路部还包括向所述第一发光二极管传输驱动电流的发光控制晶体管。可以是,所述第一像素电路部的所述初始化晶体管以及所述发光控制晶体管接收相同的栅极信号。

可以是,所述第一像素电路部的所述初始化晶体管是n型晶体管,所述发光控制晶体管是p型晶体管。

可以是,所述第一像素电路部还包括调节输出给所述第一发光二极管的驱动电流的大小的驱动晶体管以及向所述驱动晶体管施加偏置电压的偏置晶体管。可以是,所述第一像素电路部的所述初始化晶体管以及所述偏置晶体管接收相同的栅极信号。

可以是,所述第一像素电路部的所述初始化晶体管以及所述偏置晶体管是p型晶体管。

可以是,所述第一像素电路部的所述第一栅极电极以及所述第二栅极电极分别位于所述初始化晶体管的半导体层的上方以及下方。

可以是,所述发光显示装置还包括:第一绝缘层,位于所述第一像素电路部的所述第一栅极电极和所述半导体层之间;以及第二绝缘层,位于所述第一像素电路部的所述第二栅极电极和所述半导体层之间且厚于所述第一绝缘层。

可以是,所述第二像素电路部的所述第一栅极电极位于所述初始化晶体管的半导体层的上方。

可以是,所述第二像素电路部的所述初始化晶体管还包括位于所述半导体层的下方且电浮置状态的第二栅极电极。

可以是,所述第一像素的发光区域大于所述第二像素的发光区域。

可以是,所述发光显示装置还包括:第三像素,显示第三颜色并包括第三发光二极管以及与所述第三发光二极管连接的第三像素电路部。可以是,所述第三像素电路部包括与所述第三发光二极管的第一电极连接而传输初始化电压的初始化晶体管,所述初始化晶体管包括接收栅极导通电压的第二栅极电极。

可以是,所述第三像素电路部的所述第二栅极电极位于所述初始化晶体管的半导体层的下方。

可以是,所述第三像素电路部的所述初始化晶体管还包括位于所述半导体层的上方且电浮置状态的第一栅极电极。

可以是,所述第三像素的发光区域小于所述第二像素的发光区域。

根据一实施例的发光显示装置包括:第一像素、第二像素以及第三像素,显示彼此不同的颜色。所述第一像素、所述第二像素以及所述第三像素分别包括发光二极管以及与所述发光二极管连接的像素电路部,所述像素电路部包括向所述发光二极管传输初始化电压的晶体管。所述第一像素的所述晶体管包括分别位于半导体层的上方以及下方并接收栅极信号的上栅极电极以及下栅极电极,所述第二像素的所述晶体管包括位于半导体层的上方并接收栅极信号的上栅极电极,所述第三像素的所述晶体管包括位于半导体层的下方并接收栅极信号的下栅极电极。

可以是,所述第一像素的所述发光二极管的电容大于所述第二像素的所述发光二极管的电容。可以是,所述第二像素的所述发光二极管的所述电容大于所述第三像素的所述发光二极管的电容。

可以是,所述发光显示装置还包括:上绝缘层,位于所述第一像素的所述晶体管的所述上栅极电极和所述半导体层之间;以及下绝缘层,位于所述第一像素的所述晶体管的所述下栅极电极和所述半导体层之间且厚于所述上绝缘层。

可以是,所述第二像素的所述晶体管还包括位于所述半导体层的下方且电浮置状态的下栅极电极。

可以是,所述第三像素的所述晶体管还包括位于所述半导体层的上方且电浮置状态的上栅极电极。

根据实施例,可以提供能够改善像素的特性差异导致的显示质量降低的发光显示装置。另外,根据实施例,具有可以跨整个说明书判断的有利效果。

附图说明

图1是概要示出根据一实施例的发光显示装置的立体图。

图2是根据一实施例的发光显示装置中配置在显示区域中的像素的概要平面图。

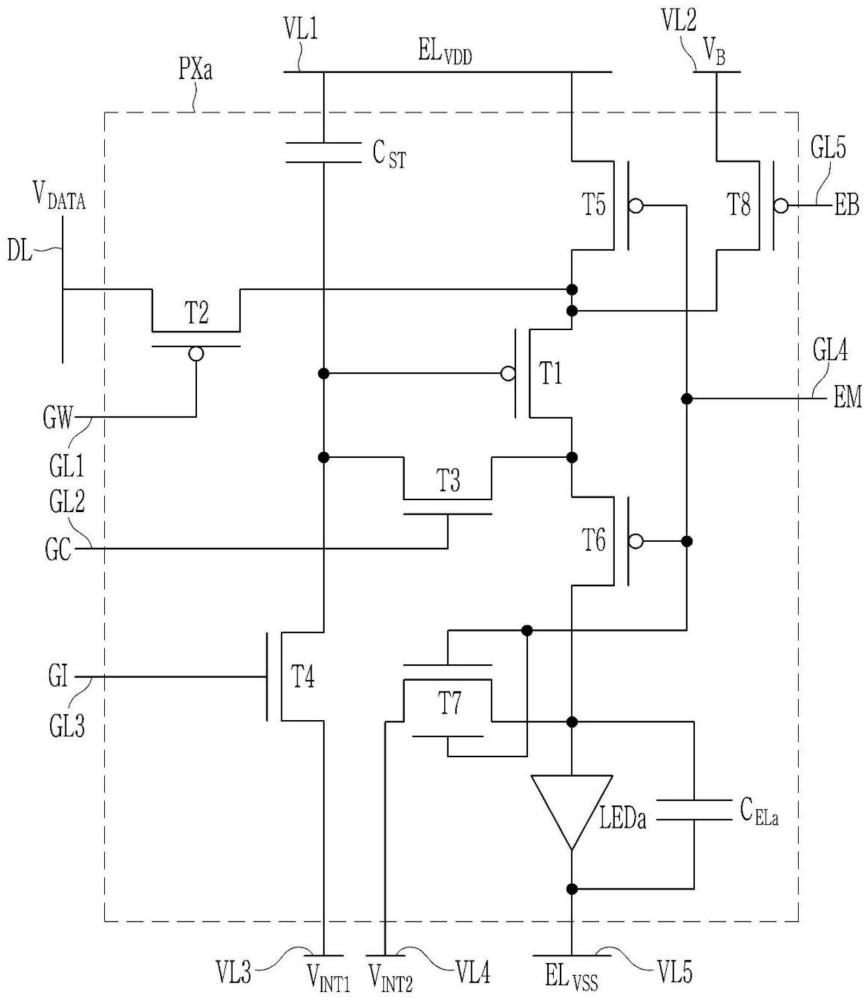

图3、图4以及图5分别是根据一实施例的发光显示装置的一像素的电路图。

图6是概要示出根据一实施例的发光显示装置中能够用于像素的第七晶体管的晶体管的截面结构的图。

图7是图6所示的晶体管的电路图。

图8、图9以及图10分别是示出图6所示的晶体管的工作的概念图。

图11是示出根据一实施例的发光显示装置中根据第七晶体管的模式的电压-电流特性的图表。

图12是根据一实施例的显示面板的概要截面图。

图13、图14以及图15分别是根据一实施例的发光显示装置的一像素的电路图。

图16是根据一实施例的显示面板的概要截面图。

(附图标记说明)

10:显示面板 110:基板

111:阻挡层 120:缓冲层

141、142、143:第一栅极绝缘层、第二栅极绝缘层、第三栅极绝缘层

161、162:第一层间绝缘层、第二层间绝缘层

181、182:第一平坦化层、第二平坦化层 190:像素界定层

A6、A7:半导体层 E1a、E1b、E1c:第一电极

ELa、ELb、ELc:发光层 FG:第一栅极电极

FIL:第一绝缘层 G6、G7:栅极电极

LB:光阻断层 LEDa:第一发光二极管

LEDb:第二发光二极管 LEDc:第三发光二极管

PXa:第一像素 PXb:第二像素

PXc:第三像素 SG:第二栅极电极

SIL:第二绝缘层 T1-T8:晶体管

具体实施方式

参考所附的附图详细说明实施例,以使在本发明所属技术领域中具有通常知识的人能够容易实施。

当表述为层、膜、区域、板等部分“在”另一部分“之上”或“上”时,其不仅包括“直接在”另一构成“之上”的情况,还包括其中间有又另一构成的情况。相反,当表述为某一部分“直接在”另一部分“之上”时,意指中间没有另一部分的情况。

在整个说明书中,只要没有表述为某一部分“包括”某一构成要件的相反的记载,意指还可以包括其它构成要件。

在整个说明书中,当表述为“连接”时,其不仅意指两个以上的构成要件直接连接的情况,而且还包括两个以上的构成要件通过其它构成要件间接连接的情况、物理连接和电连接的情况或者虽然根据位置或功能用不同的名称来指代但实质上为一体的各部分彼此连接的情况。

在附图中,表示方向时使用符号“x”、“y”以及“z”,在此,“x”是第一方向,“y”是与第一方向垂直的第二方向,“z”是与第一方向以及第二方向垂直的第三方向。

图1是概要示出根据一实施例的发光显示装置的立体图。

参考图1,发光显示装置(以下,也简称为“显示装置”)可以在移动电话、智能电话、平板、笔记本计算机、监视器、多媒体播放器、游戏机之类电子设备中用于显示图像。显示装置可以包括显示面板10、包括接合到显示面板10的柔性印刷电路膜20以及集成电路芯片30等的驱动装置。

显示面板10可以包括相当于显示图像的屏幕的显示区域(display area)DA以及配置用于生成和/或传输施加到显示区域DA的各种信号的电路和/或信号线的非显示区域(non-display area)NA。非显示区域NA可以包围显示区域DA。图1中虚线四边形内侧和外侧可以分别相当于显示区域DA和非显示区域NA。

在显示面板10的显示区域DA中像素PX可以以矩阵配置。另外,在显示区域DA中可以配置栅极线(gate line)(也称为扫描线(scan line))、数据线(data line)、驱动电压线(driving voltage line)之类信号线。栅极线可以在大致第一方向x上延伸,数据线以及驱动电压线可以在大致第二方向y上延伸。在各个像素PX中可以连接栅极线、数据线、驱动电压线等,而各个像素PX从这些信号线接收栅极信号(也称为扫描信号)、数据电压、驱动电压等。各个像素PX可以包括发光二极管以及与其连接的像素电路部。像素电路部可以基于通过栅极线、数据线等信号线施加的信号生成驱动电流来向发光二极管施加。

在显示区域DA中可以配置用于感测用户的接触和/或非接触触摸的触摸传感器。虽然示出了大致四边形的显示区域DA,但是,显示区域DA可以具有除了四边形之外的多边形、圆形、椭圆形等各种形状。

在显示面板10的非显示区域NA中可以配置排列有用于从显示面板10的外部接收信号的焊盘的焊盘部(pad portion)PP。焊盘部PP可以沿显示面板10的一边缘在第一方向x上长长地配置。在焊盘部PP中可以接合(bonding)柔性印刷电路膜20,柔性印刷电路膜20的焊盘可以电连接于焊盘部PP的焊盘。

在显示面板10的非显示区域NA中可以配置生成和/或处理用于驱动显示面板10的各种信号的驱动装置(driving unit)。驱动装置可以包括向数据线施加数据电压的数据驱动部(data driver)、向栅极线施加栅极信号的栅极驱动部(gate driver)以及控制数据驱动部及栅极驱动部的信号控制部(signal controller)。像素PX可以根据从栅极驱动部生成的栅极信号在预定时序内接收数据电压。栅极驱动部可以集成在显示面板10中,可以位于显示区域DA的至少一侧。数据驱动部以及信号控制部可以提供为集成电路芯片(也称为驱动IC芯片)30,集成电路芯片30可以装配在显示面板10的非显示区域NA中。集成电路芯片30也可以装配在柔性印刷电路膜20等而电连接于显示面板10。

图2是根据一实施例的发光显示装置中配置在显示区域中的像素的概要平面图。

参考图2,示出了配置在显示面板10(参照图1)的显示区域DA中的像素PXa、PXb、PXc。像素PXa、PXb、PXc可以包括第一像素PXa、第二像素PXb以及第三像素PXc。虽然示出了八个像素,但是,在显示区域DA中像素PXa、PXb、PXc可以在矩阵方向上有规则地配置。在所示的实施例中,在偶数行中第一像素PXa和第二像素PXb可以沿第一方向x交替配置,在奇数行中可以配置第三像素PXc。可以不同地改变像素PXa、PXb、PXc的配置。

第一像素PXa、第二像素PXb以及第三像素PXc可以显示彼此不同的颜色,各自可以显示基本色中的一个。例如,可以是,第一像素PXa、第二像素PXb以及第三像素PXc中的一个显示红色,另一个显示绿色,其余一个显示蓝色。作为一例,第一像素PXa可以显示蓝色,第二像素PXb可以显示红色,第三像素PXc可以显示绿色。第一像素PXa的区域可以宽于第二像素PXb的区域,第二像素PXb的区域可以宽于第三像素PXc的区域。

第一像素PXa、第二像素PXb以及第三像素PXc可以分别包括第一电极E1a、第二电极E1b以及第三电极E1c。各自的第一电极E1a、E1b、E1c可以包括与像素电路部(未示出)连接的延伸部。第一像素PXa、第二像素PXb以及第三像素PXc可以分别包括第一发光层ELa、第二发光层ELb以及第三发光层ELc。第一像素PXa、第二像素PXb以及第三像素PXc可以分别包括第一发光层ELa、第二发光层ELb以及第三发光层ELc。第一发光层ELa可以宽于第二发光层ELb,第二发光层ELb可以宽于第三发光层ELc。第一像素PXa、第二像素PXb以及第三像素PXc可以分别包括第二电极(未示出)。第二电极可以配置为跨显示区域DA整体。第一电极E1a、第一发光层ELa以及第二电极可以构成第一像素PXa的发光二极管,第二电极E1b、第二发光层ELb以及第二电极可以构成第二像素PXb的发光二极管,第三电极E1c、第三发光层ELc以及第二电极可以构成第三像素PXc的发光二极管。第一电极E1a、E1b、E1c可以是发光二极管的阳极(anode),第二电极可以是发光二极管的阴极(cathode)。第一电极E1a、E1b、E1c可以称为像素电极,第二电极可以称为公共电极。各像素PXa、PXb、PXc的发光区域可以与对应的发光层ELa、ELb、ELc的区域实质上相同或者小于其。

当驱动像素PXa、PXb、PXc时,每个帧被施加初始化电压而可以初始化第一电极E1a、E1b、E1c。由于第一发光层ELa、第二发光层ELb以及第三发光层ELc之间的面积差异,像素PXa、PXb、PXc的发光二极管之间可以产生电容差异。由此,当初始化第一电极E1a、E1b、E1c时,像素PXa、PXb、PXc之间可能产生初始亮度差异。为了防止像素PXa、PXb、PXc之间产生初始亮度差异,可以不同地设计像素PXa、PXb、PXc的像素电路部。针对其,参考图3至图5详细说明。

图3、图4以及图5分别是根据一实施例的发光显示装置的一像素的电路图。

图3、图4以及图5所示的像素PXa、PXb、PXc可以分别与图2中的第一像素PXa、第二像素PXb以及第三像素PXc相对应。首先说明图3所示的第一像素PXa,针对图4以及图5所示的第二像素PXb以及第三像素PXc主要说明与第一像素PXa的区别点。

参考图3,第一像素PXa可以包括第一发光二极管LEDa以及与其连接的第一像素电路部。第一像素电路部可以包括晶体管T1-T8以及储存电容器C

信号线GL1-GL5、DL、VL1-VL5可以包括栅极线GL1-GL5、数据线DL以及电压线VL1-VL5。栅极线GL1-GL5可以电连接于栅极驱动部,数据线DL可以电连接于数据驱动部。栅极线GL1-GL5可以包括第一扫描线GL1、第二扫描线GL2、初始化控制线GL3、发光控制线GL4以及偏置控制线GL5。电压线VL1-VL5可以包括驱动电压线VL1、偏置电压线VL2、第一初始化电压线VL3、第二初始化电压线VL4以及公共电压线VL5。驱动电压线VL1、偏置电压线VL2、第一初始化电压线VL3、第二初始化电压线VL4以及公共电压线VL5可以分别连接于电压生成部。

晶体管T1-T8可以包括第一晶体管T1、第二晶体管T2、第三晶体管T3、第四晶体管T4、第五晶体管T5、第六晶体管T6、第七晶体管T7以及第八晶体管T8。晶体管T1-T8可以实现为薄膜晶体管。晶体管T1-T8可以分别包括栅极电极、第一电极以及第二电极。根据晶体管T1-T8的种类和/或工作条件,第一电极以及第二电极中的一个可以是源极电极,另一个可以是漏极电极。第二至第八晶体管T2-T8可以通过栅极线GL1-GL5接收各自的栅极信号。

第一扫描线GL1可以将第一扫描信号GW向第二晶体管T2传输。第二扫描线GL2可以将第二扫描信号GC向第三晶体管T3传输。第一扫描信号GW和第二扫描信号GC的极性可以是相反的。例如,当高电压施加到第一扫描线GL1时,低电压可以施加到第二扫描线GL2。

初始化控制线GL3可以将初始化控制信号GI向第四晶体管T4传输。发光控制线GL4可以将发光控制信号EM向第五晶体管T5、第六晶体管T6以及第七晶体管T7传输。偏置控制线GL5可以将偏置控制信号EB向第八晶体管T8传输。数据线DL可以传输数据电压V

当说明晶体管T1-T8时,驱动晶体管即第一晶体管T1可以是p型晶体管,可以包括多晶半导体。可以是根据施加到第一晶体管T1的栅极电极的数据电压V

开关晶体管即第二晶体管T2可以是p型晶体管,可以包括多晶半导体。第二晶体管T2的栅极电极可以与第一扫描线GL1连接,第二晶体管T2的第一电极可以与数据线DL连接,第二晶体管T2的第二电极可以与第一晶体管T1的第一电极连接。若第二晶体管T2由通过第一扫描线GL1传输的第一扫描信号GW的栅极导通电压(低电压)导通,则通过数据线DL传输的数据电压V

第三晶体管T3可以是n型晶体管,可以包括氧化物半导体。第三晶体管T3可以电连接第一晶体管T1的第二电极和栅极电极。其结果,数据电压V

第四晶体管T4可以是n型晶体管,可以包括氧化物半导体。第四晶体管T4可以将第一晶体管T1的栅极电极以及储存电容器C

第五晶体管T5可以是p型晶体管,可以包括多晶半导体。第五晶体管T5可以将通过驱动电压线VL1施加的驱动电压EL

第六晶体管T6可以是p型晶体管,可以包括多晶半导体。第六晶体管T6可以将从第一晶体管T1输出的驱动电流向第一发光二极管LEDa传输。第六晶体管T6的栅极电极可以与发光控制线GL4连接,第六晶体管T6的第一电极可以与第一晶体管T1的第二电极连接,第六晶体管T6的第二电极可以与第一发光二极管LEDa的第一电极连接。若第五晶体管T5以及第六晶体管T6通过发光控制信号EM的栅极导通电压(低电压)导通,则驱动电流可以流向第一发光二极管LEDa。第五晶体管T5以及第六晶体管T6可以分别称为第一发光控制晶体管以及第二发光控制晶体管。

第七晶体管T7可以是n型晶体管,可以包括氧化物半导体。第七晶体管T7可以初始化第一发光二极管LEDa的第一电极。第七晶体管T7可以称为第二初始化晶体管。第七晶体管T7可以包括分别位于半导体层(也称为有源层(active layer))的上方以及下方的第一栅极电极以及第二栅极电极。第七晶体管T7的第一栅极电极以及第二栅极电极可以与发光控制线GL4连接,第七晶体管T7的第一电极可以与第一发光二极管LEDa的第一电极连接,第七晶体管T7的第二电极可以与第二初始化电压线VL4连接。第一栅极电极和第二栅极电极可以电连接。第七晶体管T7可以是栅极导通电压施加到第一栅极电极和第二栅极电极的双栅极(double gate)模式的晶体管。发光控制信号EM可以用作第七晶体管T7的栅极信号。若发光控制信号EM的栅极导通电压(高电压)施加到第一栅极电极以及第二栅极电极而第七晶体管T7导通,则第二初始化电压V

第八晶体管T8可以是p型晶体管,可以包括多晶半导体。第八晶体管T8的栅极电极可以与偏置控制线GL5连接,第八晶体管T8的第一电极可以与偏置电压线VL2连接,第八晶体管T8的第二电极可以与第一晶体管T1的第一电极连接。若第八晶体管T8通过偏置控制信号EB的栅极导通电压(低电压)导通,则偏置电压V

储存电容器C

参考图4,第二像素PXb可以包括第二发光二极管LEDb以及与其连接的第二像素电路部。第二像素PXb在构成第二像素电路部的第七晶体管T7方面上与图3所示的第一像素电路部存在区别。

能够初始化第二发光二极管LEDb的第一电极的第七晶体管T7可以是n型晶体管,可以包括氧化物半导体。第七晶体管T7可以包括分别位于半导体层的上方以及下方的第一栅极电极以及第二栅极电极。第七晶体管T7的第一栅极电极可以与发光控制线GL4连接,第七晶体管T7的第一电极可以与第二发光二极管LEDb的第一电极连接,第七晶体管T7的第二电极可以与第二初始化电压线VL4连接。第七晶体管T7的第二栅极电极可以是电浮置(floating)状态。第七晶体管T7也可以不包括第二栅极电极而仅包括第一栅极电极。第七晶体管T7可以是栅极导通电压施加到第一栅极电极的第一栅极模式的晶体管。若发光控制信号EM的栅极导通电压(高电压)施加到第一栅极电极而第七晶体管T7导通,则第二初始化电压V

参考图5,第三像素PXc可以包括第三发光二极管LEDc以及与其连接的第三像素电路部。第三像素PXc在构成第三像素电路部的第七晶体管T7方面上与图3所示的第一像素电路部存在区别。

能够初始化第三发光二极管LEDc的第一电极的第七晶体管T7可以是n型晶体管,可以包括氧化物半导体。第七晶体管T7可以包括分别位于半导体层的上方以及下方的第一栅极电极以及第二栅极电极。第七晶体管T7的第二栅极电极可以与发光控制线GL4连接,第七晶体管T7的第一电极可以与第三发光二极管LEDc的第一电极连接,第七晶体管T7的第二电极可以与第二初始化电压线VL4连接。第七晶体管T7的第一栅极电极可以是电浮置状态。第七晶体管T7也可以不包括第一栅极电极而仅包括第二栅极电极。第七晶体管T7可以是栅极导通电压施加到第二栅极电极的第二栅极模式的晶体管。若发光控制信号EM的栅极导通电压(高电压)施加到第二栅极电极而第七晶体管T7导通,则第二初始化电压V

第一发光二极管LEDa的电容C

由于初始化发光二极管LEDa、LEDb、LEDc的第一电极E1a、E1b、E1c时的像素PXa、PXb、PXc的响应差异,像素PXa、PXb、PXc之间可能产生初始亮度差异。其可能恶化低灰度级中的可变刷新率(variable refresh rate)特性或者恶化低灰度级中的色彩推移(colorshift)和/或黑色(black)视感。如实施例,可以通过使得像素PXa、PXb、PXc的像素电路部的第七晶体管T7以彼此不同的模式工作或设计来改善发光二极管LEDa、LEDb、LEDc的电容C

另一方面,与所示的实施例不同,第三晶体管T3以及第四晶体管T4可以包括多晶半导体,可以是p型晶体管。在所示的实施例中,虽然像素电路部包括八个晶体管T1-T8以及一个储存电容器C

图6是概要示出根据一实施例的发光显示装置中能够用于像素的第七晶体管的晶体管的截面结构的图,图7是图6所示的晶体管的电路图。

参考图6以及图7,像素PXa、PXb、PXc的第七晶体管T7可以具有双栅极结构。双栅极晶体管可以包括位于包括第一区域S、第二区域D以及它们之间的沟道区域C的半导体层之上以及之下的第一栅极电极FG以及第二栅极电极SG。在半导体层和第一栅极电极FG之间可以配置第一绝缘层FIL,在半导体层和第二栅极电极SG之间可以配置第二绝缘层SIL。第二绝缘层SIL可以厚于第一绝缘层FIL。

图8、图9以及图10分别是示出图6所示的晶体管的工作的概念图。

双栅极晶体管可以用作双栅极模式或者独立栅极模式。参考图8,在双栅极模式下相同的栅极信号可以施加到第一栅极电极FG和第二栅极电极SG。通过施加到第一栅极电极FG的栅极导通电压,在沟道区域上方可以形成第一沟道,通过施加到第二栅极电极SG的栅极导通电压,在沟道区域下方可以形成第二沟道。参考图9,若在第一栅极模式下向第一栅极电极FG施加栅极导通电压,则在沟道区域上方可以形成第一沟道。参考图10,若在第二栅极模式下向第二栅极电极SG施加栅极导通电压,则在沟道区域上方可以形成第二沟道。

参照图3至图10,第一绝缘层FIL的厚度T

图11是示出根据一实施例的发光显示装置中根据第七晶体管的模式的电压-电流特性的图表。

参照图3至图6以及图11中红色图表是双栅极模式的第一像素PXa的第七晶体管T7的特性,蓝色图表是第一栅极模式的第二像素PXb的第七晶体管T7的特性,绿色图表是第二栅极模式的第三像素PXc的第七晶体管T7的特性。模拟中所使用的第一绝缘层FIL的厚度是140nm,第二绝缘层SIL的厚度是260nm,半导体层包括IGZO。在相同的栅极-源极电压V

图12是根据一实施例的显示面板的概要截面图。

图12可以概要示出包括图3、图4以及图5所示的像素PXa、PXb、PXc的显示面板10的截面结构,可以示出与大致三个像素PXa、PXb、PXc相对应的像素区域。显示面板10可以包括显示部100、触摸部200以及防反射部300。

显示部100可以基本上包括基板110、形成在基板110之上的晶体管T6、T7、储存电容器C

基板110可以是包括聚酰亚胺(polyimide)、聚酰胺(polyamide)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate)等高分子的柔性基板。基板110也可以是玻璃基板。

在基板110之上可以配置防止水分、氧气等渗透的阻挡层111。阻挡层111可以包括硅氮化物(SiN

在阻挡层111之上可以配置缓冲层120。缓冲层120可以在形成半导体层A6时阻断来自基板110的杂质来提高半导体层A6的特性,可以平坦化基板110的表面来缓解半导体层A6的应力。缓冲层120可以包括硅氧化物、硅氮化物、硅氮氧化物等无机绝缘物质。缓冲层120也可以包括非晶硅。

在缓冲层120之上可以配置半导体层A6。半导体层A6可以包括第一区域、第二区域以及这些区域之间的沟道区域。半导体层A6可以包括多晶硅。

在半导体层A6之上可以配置第一栅极绝缘层141。第一栅极绝缘层141可以包括硅氮化物(SiN

在第一栅极绝缘层141之上可以配置可以包括栅极电极G6、储存电容器C

在第一栅极导电层之上可以配置第二栅极绝缘层142。第二栅极绝缘层142可以包括硅氮化物、硅氧化物、硅氮氧化物等无机绝缘物质,可以是单层或者多层。

在第二栅极绝缘层142之上可以配置可以包括光阻断层LB、储存电容器C

在第二栅极导电层之上可以配置第一层间绝缘层161。第一层间绝缘层161可以包括硅氮化物、硅氧化物、硅氮氧化物等无机绝缘物质,可以是单层或者多层。当第一层间绝缘层161是多层时,下层可以包括硅氮化物,上层可以包括硅氧化物。图6所示的第二绝缘层SIL可以与第一层间绝缘层161相对应。

在第一层间绝缘层161之上可以配置半导体层A7。半导体层A7可以与光阻断层LB重叠。半导体层A7可以包括第一区域、第二区域以及这些区域之间的沟道区域。半导体层A7可以包括氧化物半导体。半导体层A7可以包括锌(Zn)、铟(In)、镓(Ga)以及锡(Sn)中的至少一个。作为一例,半导体层A7可以包括IGZO(铟镓锌氧化物;indium-gallium-zinc oxide)。

在半导体层A7之上可以配置第三栅极绝缘层143。第三栅极绝缘层143可以包括硅氮化物、硅氧化物、硅氮氧化物等无机绝缘物质,可以是单层或者多层。图6所示的第一绝缘层FIL可以与第三栅极绝缘层143相对应。第三栅极绝缘层143可以具有薄于第一层间绝缘层161的厚度。

在第三栅极绝缘层143之上可以配置可以包括栅极电极G7等的第三栅极导电层。第一像素PXa中栅极电极G7可以与光阻断层LB电连接。第二像素PXb中栅极电极G7可以是电浮置状态。第三栅极导电层可以包括钼(Mo)、铝(Al)、铜(Cu)、钛(Ti)等,可以是单层或者多层。例如,第三栅极导电层可以包括包含钛的下层和包含钼的上层,下层可以防止在干蚀刻上层时蚀刻气体即氟(F)扩散。

在第三栅极导电层之上可以配置第二层间绝缘层162。第二层间绝缘层162可以包括硅氮化物、硅氧化物、硅氮氧化物等无机绝缘物质,可以是单层或者多层。第二层间绝缘层162例如可以包括包含硅氮化物的下层和包含硅氧化物的上层。

在第二层间绝缘层162之上可以配置可以包括第一电极S6、S7、第二电极D6、D7、栅极线等的第一数据导电层。第一电极S6以及第二电极D6可以通过形成在绝缘层141、142、161、143、162中的接触孔分别连接于半导体层A6的第一区域以及第二区域。第一电极S7以及第二电极D7可以通过形成在绝缘层143、162中的接触孔分别连接于半导体层A7的第一区域以及第二区域。栅极线可以是图3所示的第一扫描线GL1、第二扫描线GL2、初始化控制线GL3、发光控制线GL4和/或偏置控制线GL5。第一数据导电层可以包括铝(Al)、铂(Pt)、钯(Pd)、银(Ag)、镁(Mg)、金(Au)、镍(Ni)、钕(Nd)、铱(Ir)、铬(Cr)、钙(Ca)、钼(Mo)、钛(Ti)、钨(W)、铜(Cu)等,可以是单层或者多层。例如,第一数据导电层可以包括包含钼、铬、钽、钛等难熔金属(refractory metal)的下层、包含铝、铜、银等电阻率低的金属的中间层以及包含难熔金属的上层。作为一例,第一数据导电层可以具有钛(Ti)-铝(Al)-钛(Ti)之类三层结构。

半导体层A6、栅极电极G6、第一电极S6以及第二电极D6可以构成第六晶体管T6。半导体层A7、栅极电极G7、第一电极S7以及第二电极D7可以构成第七晶体管T7。第一像素PXa中光阻断层LB可以与栅极电极G7电连接而作为第七晶体管T7的下栅极电极发挥功能。第三像素PXc中光阻断层LB可以作为第七晶体管T7的栅极电极发挥功能以代替栅极电极G7。

在第一数据导电层之上可以配置第一平坦化层181。第一平坦化层181可以是有机绝缘层。例如,第一平坦化层181可以包括聚甲基丙烯酸甲酯(poly(methylmethacrylate))、聚苯乙烯(polystyrene)之类通用高分子、具有苯酚类基团的高分子衍生物、丙烯酸类高分子、酰亚胺类高分子(例如,聚酰亚胺)、硅氧烷类高分子等有机绝缘物质。

在第一平坦化层181之上可以配置可以包括数据线DLa、DLb、DLc、电压线VL、连接电极LE等的第二数据导电层。电压线VL可以是图3所示的驱动电压线VL1、偏置电压线VL2、第一初始化电压线VL3、第二初始化电压线VL4和/或公共电压线VL5。连接电极LE可以通过形成在第一平坦化层181中的接触孔连接于第六晶体管T6的第二电极D6。第二数据导电层可以包括铝(Al)、铂(Pt)、钯(Pd)、银(Ag)、镁(Mg)、金(Au)、镍(Ni)、钕(Nd)、铱(Ir)、铬(Cr)、钙(Ca)、钼(Mo)、钛(Ti)、钨(W)、铜(Cu)等,可以是单层或者多层。例如,第二数据导电层可以具有钛/铝/钛(Ti/Al/Ti)之类三层结构。

在第二数据导电层之上可以配置第二平坦化层182。第二平坦化层182可以是有机绝缘层。例如,第二平坦化层182可以包括聚甲基丙烯酸甲酯、聚苯乙烯之类通用高分子、具有苯酚类基团的高分子衍生物、丙烯酸类高分子、酰亚胺类高分子、硅氧烷类高分子等有机绝缘物质。

在第二平坦化层182之上可以配置包括第一电极E1a、E1b、E1c的像素导电层。第一电极E1a、E1b、E1c可以通过形成在第二平坦化层182中的接触孔与连接电极LE连接。第一电极E1a、E1b、E1c可以与第二电极D6电连接而接收控制发光二极管LEDa、LEDb、LEDc的亮度的驱动电流。像素导电层可以包括银(Ag)、锂(Li)、钙(Ca)、铝(Al)、镁(Mg)、金(Au)之类金属。像素导电层也可以包括铟锡氧化物(ITO)、铟锌氧化物(IZO)之类透明导电性氧化物(TCO)。像素导电层可以是多层,例如,可以具有ITO-银(Ag)-ITO的三层结构。

在像素导电层之上可以配置像素界定层190。像素界定层190可以具有与第一电极E1a、E1b、E1c重叠的开口195a、195b、195c。像素界定层190可以包括聚甲基丙烯酸甲酯、聚苯乙烯之类通用高分子、具有苯酚类基团的高分子衍生物、丙烯酸类高分子、酰亚胺类高分子(例如,聚酰亚胺)、硅氧烷类高分子等有机绝缘物质。像素界定层190可以是包括黑色染料或者颜料的黑色像素界定层190。黑色像素界定层190可以提高对比度,可以防止位于下方的金属层引起的反射。

在第一电极E1a、E1b、E1c之上可以配置发光层ELa、ELb、ELc。发光层ELa、ELb、ELc可以位于开口195a、195b、195c中,但是,也可以包括位于开口195a、195b、195c外部的部分。发光层ELa、ELb、ELc可以包括唯一发出红色、绿色、蓝色等基本色的光的物质层。除了发光层ELa、ELb、ELc之外,在第一电极E1a、E1b、E1c之上可以还配置空穴注入层、空穴输送层、电子输送层以及电子注入层中的至少一个。

在发光层ELa、ELb、ELc以及像素界定层190之上可以配置第二电极E2。第二电极E2可以共同提供给所有像素PXa、PXb、PXc。第二电极E2可以包括钙(Ca)、钡(Ba)、镁(Mg)、铝(Al)、银(Ag)、铂(Pt)、钯(Pd)、金(Au)、镍(Ni)、钕(Nd)、铱(Ir)、铬(Cr)、锂(Li)等金属。第二电极E2可以包括铟锡氧化物(ITO)、铟锌氧化物(IZO)之类透明导电性氧化物(TCO)。

第一电极E1a、第一发光层ELa以及第二电极E2可以构成第一发光二极管LEDa以及电容器C

在第二电极E2之上可以配置封装层EN。封装层EN可以通过封装发光二极管LEDa、LEDb、LEDc来防止水分和氧气从外部渗透。封装层EN可以是包括一个以上的无机层和一个以上的有机层的薄膜封装层。例如,封装层EN可以具有无机层-有机层-无机层的三层结构。

在封装层EN之上可以配置触摸部200。

触摸部200可以包括位于封装层EN之上的第一绝缘层210。第一绝缘层210可以覆盖封装层EN而保护封装层EN,并防止透湿。第一绝缘层210可以减少第二电极E2和触摸电极TE之间的寄生电容。

在第一绝缘层210之上可以配置可以包括桥接器BR等的第一触摸导电层,在第一触摸导电层之上可以配置第二绝缘层220。在第二绝缘层220之上可以配置可以包括触摸电极TE的第二触摸导电层,在第二触摸导电层之上可以配置钝化层230。

触摸电极TE可以包括形成互感电容器的第一触摸电极以及第二触摸电极。桥接器BR可以电连接第一触摸电极或者第二触摸电极。例如,相邻的同时彼此分离的第一触摸电极可以通过形成在第二绝缘层220中的接触孔连接于桥接器BR而通过桥接器BR电连接。

第一绝缘层210以及第二绝缘层220可以包括硅氮化物、硅氧化物、硅氮氧化物等无机绝缘物质,可以是单层或者多层。钝化层230可以包括硅氮化物、硅氧化物、硅氮氧化物等无机绝缘物质或者丙烯酸类高分子、酰亚胺类树脂等有机物。

第一触摸电极层以及第二触摸电极层可以是具有与像素PXa、PXb、PXc重叠的开口的网格(mesh)形状。第一触摸电极层以及第二触摸电极层可以分别包括铝(Al)、铜(Cu)、钛(Ti)、钼(Mo)、银(Ag)、铬(Cr)、镍(Ni)等金属。

在触摸部200之上可以配置防反射部300。

防反射部300可以包括遮光层320和滤色器330a、330b、330c。

遮光层320可以与显示部100的像素界定层190重叠,宽度可以窄于像素界定层190。遮光层320可以具有与像素界定层190的开口195a、195b、195c重叠的开口325a、325b、325c。

滤色器330a、330b、330c可以位于遮光层320之上。滤色器330a、330b、330c可以包括透射第一颜色的第一滤色器330a、透射第二颜色的第二滤色器330b、透射第三颜色的第三滤色器330c。在滤色器330a、330b、330c之上可以配置外涂层340。

防反射部300可以防止从外部入射的外部光被布线等反射而被识别。遮光层320和滤色器330a、330b、330c可以组合来作为防反射层发挥功能。在这种结构中可以不需要偏光层作为防反射层,因此,可以提高出光效率,可以减少显示面板10的厚度。

可以不同地改变显示面板10的层叠结构以及构成要件的配置。

图13、图14以及图15分别是根据一实施例的发光显示装置的一像素的电路图。

图13、图14以及图15所示的像素PXa、PXb、PXc可以分别与图2中的第一像素PXa、第二像素PXb以及第三像素PXc相对应。首先说明图13所示的第一像素PXa,针对图14以及图15所示的第二像素PXb以及第三像素PXc主要说明与第一像素PXa的区别点。

参考图13,与图3所示的第一像素PXa在整体上类似,但是,在第一像素电路部的第三晶体管T3、第四晶体管T4以及第七晶体管T7上存在区别。具体地,第三晶体管T3、第四晶体管T4以及第七晶体管T7可以是p型晶体管,可以包括多晶半导体。第三晶体管T3可以由通过第二扫描线GL2接收的第二扫描信号GC的栅极导通电压(低电压)导通而连接第一晶体管T1的栅极电极和第一晶体管T1的第二电极。第四晶体管T4可以由通过初始化控制线GL3接收的初始化控制信号GI的栅极导通电压(低电压)导通,从而第一初始化电压V

参考图14,第二像素PXb可以包括第二发光二极管LEDb以及与其连接的第二像素电路部。第二像素PXb在构成第二像素电路部的第七晶体管T7方面上与图13所示的第一像素电路部存在区别。

第七晶体管T7可以是p型晶体管,可以包括多晶半导体。第七晶体管T7可以是独立栅极模式。第七晶体管T7可以包括分别位于半导体层的上方以及下方的第一栅极电极以及第二栅极电极。第七晶体管T7的第一栅极电极可以与偏置控制线GL5连接。第七晶体管T7的第二栅极电极可以是电浮置状态。第七晶体管T7也可以不包括第二栅极电极而仅包括第一栅极电极。第七晶体管T7可以通过偏置控制信号EB的栅极导通电压(低电压)导通,从而第二初始化电压V

参考图15,第三像素PXc可以包括第三发光二极管LEDc以及与其连接的第三像素电路部。第三像素PXc在构成第三像素电路部的第七晶体管T7的方面上与图13所示的第一像素电路部存在区别。

第七晶体管T7可以是p型晶体管,可以包括多晶半导体。第七晶体管T7可以是独立栅极模式。第七晶体管T7可以包括分别位于半导体层的上方以及下方的第一栅极电极以及第二栅极电极。第七晶体管T7的第二栅极电极可以与偏置控制线GL5连接,第七晶体管T7的第一栅极电极可以是电浮置状态。第七晶体管T7也可以不包括第一栅极电极而仅包括第二栅极电极。第七晶体管T7可以通过偏置控制信号EB的栅极导通电压(低电压)导通,从而第二初始化电压V

如上所述,可以将像素PXa、PXb、PXc的像素电路部的晶体管全部构成为p型。即使在这种构成下,也可以通过使得像素PXa、PXb、PXc的像素电路部的第七晶体管T7以彼此不同的模式工作或设计而改善发光二极管LEDa、LEDb、LEDc的电容C

图16是根据一实施例的显示面板的概要截面图。

图16可以概要示出包括图13、图14以及图15所示的像素PXa、PXb、PXc的显示面板的截面结构,可以示出与大致三个像素PXa、PXb、PXc相对应的像素区域。

参考图16,显示面板10与图12所示的显示面板10在显示部100上存在区别,针对相同的构成简化或省略说明。

显示部100可以基本上包括基板110、形成在基板110之上的晶体管T6、T7、储存电容器C

在基板110之上可以配置阻挡层111。在阻挡层111之上可以配置第七晶体管T7的第二栅极电极SG。第一像素PXa以及第三像素PXc中第二栅极电极SG可以与偏置控制线GL5(参照图13)连接而被施加偏置控制信号EB(参照图13),第七晶体管T7可以通过偏置控制信号EB的栅极导通电压(低电压)导通。

在第二栅极电极SG之上可以配置缓冲层120。图6所示的第二绝缘层SIL可以与缓冲层120相对应。

在缓冲层120之上可以配置半导体层A6、A7。半导体层A6、A7可以包括多晶硅。在半导体层A6、A7之上可以配置第一栅极绝缘层141。图6所示的第一绝缘层FIL可以与第一栅极绝缘层141相对应。第一栅极绝缘层141可以具有薄于缓冲层120的厚度。

在第一栅极绝缘层141之上可以配置可以包括栅极电极G6、G7、储存电容器C

在第一栅极导电层之上可以配置第二栅极绝缘层142。在第二栅极绝缘层142之上可以配置可以包括储存电容器C

在第二栅极导电层之上可以配置层间绝缘层161。在层间绝缘层161之上可以配置可以包括第一电极S6、S7、第二电极D6、D7、栅极线等的第一数据导电层。第一电极S6以及第二电极D6可以通过形成在绝缘层141、142、161中的接触孔分别连接于半导体层A6的第一区域以及第二区域。第一电极S7以及第二电极D7可以通过形成在绝缘层141、142、161中的接触孔分别连接于半导体层A7的第一区域以及第二区域。

半导体层A6、栅极电极G6、第一电极S6以及第二电极D6可以构成第六晶体管T6。半导体层A7、栅极电极G7、第一电极S7以及第二电极D7可以构成第七晶体管T7。第一像素PXa中第二栅极电极SG可以与栅极电极G7电连接而作为第七晶体管T7的下栅极电极发挥功能。第三像素PXc中第二栅极电极SG可以作为第七晶体管T7的栅极电极发挥功能以代替栅极电极G7。

位于第一数据导电层之上的构成可以与图12所示的构成实质上相同,省略针对其的说明。

以上,针对本发明的实施例详细地进行了说明,但是本发明的权利范围不限于此,本领域技术人员利用权利要求书中所定义的本发明的基本概念进行的多种变形和改良形式也属于本发明的权利范围。