集成电路封装及其形成方法

文献发布时间:2023-06-19 10:40:10

技术领域

本发明实施例是涉及集成电路封装及其形成方法。

背景技术

随着半导体技术不断演进,集成电路晶粒变得愈来愈小。此外,更多的功能被整合至晶粒中。因此,晶粒所需要的输入/输出(input/output,I/O)垫的数目已增加,而可用于I/O垫的面积已减小。I/O垫的密度随着时间迅速上升,进而增大了晶粒封装的难度。一些应用要求集成电路晶粒具有更强大的并行处理能力。封装技术可用于多个晶粒的整合,从而使得达成更大程度的并行处理能力。

在一些封装技术中,集成电路晶粒在被封装之前自晶片单体化。此种封装技术的有利特征是可形成扇出型封装(fanout package),所述扇出型封装使得晶粒上的I/O垫能够被重布线至更大的面积。因此可增加晶粒表面上的I/O垫的数目。

发明内容

在一实施例中,一种集成电路封装包括:处理器晶粒,包括电路区块,所述电路区块包括具有第一技术节点(technology node)的有源装置;电源闸控晶粒(power gatingdie),包括具有第二技术节点的功率半导体装置,所述第二技术节点大于所述第一技术节点;以及第一重布线结构,包括第一金属化图案,所述第一金属化图案包括电力供应源线及电力供应接地线,其中所述电路区块的第一子集经由所述功率半导体装置电性耦合至所述电力供应源线及所述电力供应接地线,且所述电路区块的第二子集永久地电性耦合至所述电力供应源线及所述电力供应接地线。

在一实施例中,一种集成电路封装包括:处理器晶粒,包括电路区块,所述电路区块包括具有第一技术节点的有源装置;电源闸控晶粒,藉由介电质对介电质结合及藉由金属对金属结合直接结合至所述处理器晶粒,所述电源闸控晶粒包括具有第二技术节点的功率半导体装置,所述第二技术节点大于所述第一技术节点,所述功率半导体装置电性耦合至所述电路区块的第一子集;介电层,环绕所述电源闸控晶粒;第一导通孔,延伸穿过所述介电层,所述第一导通孔电性耦合至所述电路区块的第二子集;以及第一重布线结构,包括第一金属化图案,所述第一金属化图案包括连接至所述第一导通孔及所述电源闸控晶粒的电力供应源线;封装衬底;以及第一导电连接件,将所述封装衬底连接至所述第一重布线结构的所述第一金属化图案。

在一实施例中,一种集成电路封装的形成方法包括:将电源闸控晶粒结合至晶片(wafer),所述晶片包括处理器晶粒,所述电源闸控晶粒与所述处理器晶粒包括节距(pitch)不同的有源装置,所述电源闸控晶粒包括第一导通孔;在所述电源闸控晶粒周围且在所述晶片上形成介电层;在第一介电层中图案化出开口,所述开口暴露出所述处理器晶粒的晶粒连接件;将导电材料镀覆于所述开口中及所述晶粒连接件上;将所述导电材料平坦化以在所述开口中形成第二导通孔,所述平坦化暴露出所述电源闸控晶粒的所述第一导通孔;以及锯切所述介电层及所述晶片以将所述处理器晶粒单体化。

附图说明

结合附图阅读以下详细说明,会最佳地理解本揭露的各个态样。注意,根据行业中的标准惯例,各种特征并非按比例绘制。事实上,为使论述清晰起见,可任意增大或减小各种特征的尺寸。

图1、图2及图3是根据一些实施例的用于形成集成电路封装的工艺期间的中间步骤的各种视图。

图4、图5及图6是根据一些实施例的用于形成实施集成电路封装的系统的工艺期间的中间步骤的剖视图。

图7是根据一些其他实施例的集成电路封装及实施所述集成电路封装的系统的剖视图。

图8、图9、图10、图11、图12、图13、图14、图15及图16是根据一些实施例的用于形成实施集成电路封装的系统的工艺期间的中间步骤的剖视图。

图17是根据一些其他实施例的集成电路封装及实施所述集成电路封装的系统的剖视图。

图18是根据一些其他实施例的集成电路封装及实施所述集成电路封装的系统的剖视图。

图19是根据一些其他实施例的集成电路封装及实施所述集成电路封装的系统的剖视图。

图20、图21、图22、图23及图24是根据一些实施例的用于形成集成电路封装的工艺期间的中间步骤的剖视图。

图25、图26、图27及图28是根据一些实施例的用于形成实施集成电路封装的系统的工艺期间的中间步骤的剖视图。

图29、图30、图31、图32、图33及图34是根据一些其他实施例的用于形成实施集成电路封装的系统的工艺期间的中间步骤的剖视图。

图35、图36、图37、图38、图39及图40是根据一些其他实施例的用于形成集成电路封装的工艺期间的中间步骤的剖视图。

图41是根据一些其他实施例的集成电路封装的剖视图。

具体实施方式

以下揭露内容提供诸多不同的实施例或实例以用于实施本发明的不同特征。下文阐述组件及排列的具体实例以简化本揭露。当然,这些仅为实例且不旨在进行限制。举例而言,在以下说明中第一特征形成于第二特征“之上”或形成于第二特征“上”可包括其中第一特征与第二特征被形成为直接接触的实施例,且亦可包括其中第一特征与第二特征之间可形成有额外特征使得所述第一特征与所述第二特征可不直接接触的实施例。另外,本揭露可在各种实例中重复使用参考编号及/或字母。此种重复是出于简洁及清晰的目的,而非自身指示所论述的各种实施例及/或配置之间的关系。

此外,为易于说明起见,本文中可使用例如“位于…之下(beneath)”、“位于…下方(below)”、“下部的(lower)”、“位于…上方(above)”、“上部的(upper)”等空间相对性用语来阐述图中所示的一个组件或特征与另一(其他)组件或特征的关系。除图中所绘示的定向之外,所述空间相对性用语亦旨在囊括装置在使用或操作中的不同定向。设备可具有其他定向(旋转90度或处于其他定向),且同样地可对本文中所使用的空间相对性描述语加以相应地解释。

根据一些实施例,形成具有处理器装置及电源闸控装置的集成电路封装,处理器装置与电源闸控装置是分离的半导体装置。电源闸控装置形成有较处理器装置大的有源装置,且包括为处理器装置提供电源闸控的功率半导体装置。因此,具有大的技术节点的开关晶体管可用于电力输送,从而允许减小所得的集成电路封装的功耗。

图1、图2及图3是根据一些实施例的用于形成集成电路封装100的工艺期间的中间步骤的剖视图。藉由将半导体设备堆叠于晶片102上形成集成电路封装100。说明将设备堆叠于晶片102的一个装置区102A中,但应了解,晶片102可具有任何数目的装置区,且可将半导体设备堆叠于每一装置区中以形成集成电路封装。半导体装置可以是裸集成电路晶粒或经封装晶粒。在所说明的实施例中,每一半导体装置是裸集成电路晶粒。在其他实施例中,所说明的半导体装置中的一或多者可以是被包封的经封装晶粒。

在图1中,获得晶片102。晶片102包括位于装置区102A中的处理器装置10。将在后续处理中将处理器装置10单体化以包括于集成电路封装100中。处理器装置10可以是任何可接受的处理器或逻辑设备,例如中央处理单元(central processing unit,CPU)、图形处理单元(graphics processing unit,GPU)、算术逻辑单元(arithmetic logic unit,ALU)、系统芯片(system-on-a-chip,SoC)、应用处理器(application processor,AP)、影像讯号处理器(image signal processor,ISP)、数字信号处理器(digital signal processor,DSP)、现场可编程栅极阵列(field programmable gate array,FPGA)、微控制器、人工智能(artificial intelligence,AI)加速度计等。如下文进一步论述,处理器装置10被形成为不包括电源闸控特征。

可根据可适用的制造工艺对处理器装置10进行处理以形成集成电路。举例而言,处理器装置10包括经掺杂或未经掺杂的半导体衬底12(例如硅)或绝缘体上半导体(semiconductor-on-insulator,SOI)衬底的有源层。半导体衬底12可包含其他半导体材料,例如:锗;化合物半导体,包括碳化硅、镓砷、磷化镓、磷化铟、砷化铟及/或锑化铟;合金半导体,包括SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP及/或GaInAsP;或其组合。亦可使用其他衬底,例如多层衬底或梯度衬底。半导体衬底12具有有源表面12A及非有源表面12N。

可在半导体衬底12的有源表面12A处形成装置。所述装置可以是有源装置(例如晶体管、二极管等)、电容器、电阻器等。非有源表面12N可不具有装置。层间介电质(inter-layer dielectric,ILD)位于半导体衬底12的有源表面12A之上。ILD环绕且可覆盖装置。ILD可包括由以下材料形成的一或多个介电层,例如磷硅酸盐玻璃(Phospho-SilicateGlass,PSG)、硼硅酸盐玻璃(Boro-Silicate Glass,BSG)、掺杂硼的磷硅酸盐玻璃(Boron-Doped Phospho-Silicate Glass,BPSG)、未经掺杂的硅酸盐玻璃(undoped SilicateGlass,USG)等。

内连结构14位于半导体衬底12的有源表面12A之上。内连结构14对半导体衬底12的有源表面12A处的装置进行内连以形成集成电路。可藉由例如介电层中的金属化图案形成内连结构14。金属化图案包括形成于一或多个介电层中的金属线及通孔。内连结构14的金属化图案电性耦合至半导体衬底12的有源表面12A处的装置。

晶粒连接件16位于处理器装置10的前侧10F处。晶粒连接件16可以是进行外部连接的导电柱、垫等。晶粒连接件16位于内连结构14中及/或上。晶粒连接件16可由金属(例如铜、铝等)形成,且可藉由例如镀覆等形成。

介电层18位于处理器装置10的前侧10F处。介电层18位于内连结构14中及/或上。介电层18在侧向上包封晶粒连接件16,且介电层18与处理器装置10的侧壁在侧向上毗连(coterminous)。首先,介电层18可隐埋晶粒连接件16,以使得介电层18的最顶表面位于晶粒连接件16的最顶表面上方。介电层18可以是:聚合物,例如聚苯并恶唑(polybenzoxazole,PBO)、聚酰亚胺、苯并环丁烯(benzocyclobuten,BCB)系聚合物等;氮化物,例如氮化硅等;氧化物,例如氧化硅,PSG,BSG,BPSG等;类似物或其组合。可例如藉由旋转涂布、层压、化学气相沉积(chemical vapor deposition,CVD)等形成介电层18。在形成之后,可使用例如化学机械抛光(chemical-mechanical polish,CMP)工艺、回蚀工艺等或其组合将晶粒连接件16及介电层18平坦化。在平坦化之后,晶粒连接件16的表面及介电层18的表面是平坦的且在处理器装置10的前侧10F处暴露出。

处理器装置10包括多个电路区块。电路区块是处理器装置10的电路的逻辑区块或逻辑单元。换言之,电路区块包括处理器装置10的电路的子集,其中电路区块中的电路全部与同一域相关。电路区块的实例包括算术电路区块、存储器电路区块、DSP电路区块等。

亦获得电源闸控装置20。电源闸控装置20是处理器装置10的电力输送网络的一部分。具体而言,电源闸控装置20为处理器装置10的电路区块中的一些或所有电路区块提供电源闸控。电源闸控装置20可在运行时间操作以接收控制讯号并因应于所述控制讯号而将处理器装置10的电路区块接通或关断。举例而言,处理器装置10的电路区块可在需要时接通且可不在处于使用中时关断,因此减少未使用电路区块泄漏的电力。因此,可减小处理器装置10的功耗。此外,形成不包括电源闸控特征的处理器装置10使得能够减小处理器装置10的面积。举例而言,将电源闸控特征移动到专用电源闸控装置20使得能够将处理器装置10的面积减小达20%。

可根据可适用的制造工艺对电源闸控装置20进行处理以形成集成电路。举例而言,电源闸控装置20包括半导体衬底22、内连结构24、晶粒连接件26及介电层28,所述半导体衬底22、内连结构24、晶粒连接件26及介电层28可分别类似于半导体衬底12、内连结构14、晶粒连接件16及介电层18。电源闸控装置20的前侧20F处暴露出晶粒连接件26及介电层28。电源闸控装置20还包括导通孔30,导通孔30被形成为延伸至半导体衬底22中。导通孔30电性耦合至内连结构24的金属化图案。

以形成导通孔30作为实例,可藉由例如蚀刻、铣削、激光技术、其组合等在内连结构24及/或半导体衬底22中形成凹陷部。可例如藉由使用氧化技术在所述凹陷部中形成薄的介电材料。可例如藉由CVD、原子层沉积(atomic layer deposition,ALD)、物理气相沉积(physical vapor deposition,PVD)、热氧化、其组合等在开口中共形地沉积薄的障壁层。障壁层可由氧化物、氮化物或氮氧化物(例如氮化钛、氮氧化钛、氮化钽、氮氧化钽、氮化钨、其组合等)形成。可在障壁层之上及在开口中沉积导电材料。可藉由电化学镀覆工艺、CVD、ALD、PVD、其组合等形成导电材料。导电材料的实例是铜、钨、铝、银、金、其组合等。藉由例如CMP自内连结构24的表面及/或半导体衬底22的表面移除多余导电材料及障壁层。障壁层的剩余部分及导电材料的剩余部分形成导通孔30。

在所说明的实施例中,电源闸控装置20的后侧20B处尚未暴露出导通孔30。而是,导通孔30隐埋于半导体衬底22中。如下文进一步论述,将在后续处理中经由平坦化工艺在电源闸控装置20的后侧20B处暴露出导通孔30。在暴露之后,导通孔30可被称为衬底穿孔或硅穿孔(through-substrate via或through-silicon via,TSV)。

电源闸控装置20包括用以为处理器装置10提供电源闸控的功率半导体装置(例如,用于功率电子器件的半导体装置)。具体而言,电源闸控装置20可包括开关晶体管、电源闸控控制器及电源闸控网络结构。电源闸控装置20的功率半导体装置可以是双极装置,例如绝缘闸双极晶体管(insulated-gate bipolar transistor,IGBT)装置等;或可以是功率金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field EffectTransistor,MOSFET)装置,例如互补金属氧化物半导体(complementary metal-oxide-semiconductor,CMOS)装置、双扩散金属氧化物半导体(diffused metal-oxide-semiconductor,DMOS)装置等。在一些实施例中,处理器装置10与电源闸控装置20是藉由不同的半导体工艺技术形成,且具有节距不同的装置(例如,有源装置)。举例而言,处理器装置10可包括CMOS装置,且电源闸控装置20可包括IGBT装置或DMOS装置。半导体衬底22的有源表面包括开关装置区22S,开关装置区22S包括开关晶体管。开关装置区22S的开关晶体管连接至电力供应源(V

内连结构24的金属化图案可形成电源闸控网络结构中的一些电源闸控网络结构、所有电源闸控网络结构,或者不形成电源闸控网络结构。在一些实施例中,电源闸控装置20的内连结构24包括所有的电源闸控网络结构。在一些实施例中,电源闸控装置20的内连结构24包括电源闸控网络结构中的一些电源闸控网络结构,且处理器装置10的内连结构14包括电源闸控网络结构中的一些电源闸控网络结构。在一些实施例中,电源闸控装置20的内连结构24不包括电源闸控网络结构,且处理器装置10的内连结构14包括所有的电源闸控网络结构。

开关晶体管的电力输送效能可显著地影响电源闸控装置20的总体电力输送效能。具体而言,具有大的技术节点的开关晶体管可适应较大的冲击电流,且在处理器装置10的电路区块接通时具有较小的电压降(例如,电压电位降(IR drop))。类似地,具有大的技术节点的开关晶体管可具有较大的临限值电压,此使得开关晶体管能够减少的电力泄漏。根据一些实施例,处理器装置10具有技术节点较小(例如,装置节距或间隔较小)的有源装置,所述技术节点较小的有源装置不适合于开关晶体管但适合于逻辑设备,且电源闸控装置20具有技术节点较大(例如,装置节距或间隔较大)的有源装置,所述技术节点较大的有源装置不适合于逻辑设备但适合于开关晶体管。举例而言,处理器装置10可具有技术节点处于约2纳米至约28纳米范围中的有源装置(例如,形成电路区块),且电源闸控装置20可具有技术节点处于约3纳米至约90纳米范围中的有源装置(例如,功率半导体装置)。形成有源装置较处理器装置10大的电源闸控装置20使得处理器装置10能够被缩小至提供改良的逻辑设备效能的较小技术节点,同时仍使得电源闸控装置20能够提供足够的电力输送效能。此外,形成具有较大的有源装置的电源闸控装置20使得能够降低电源闸控装置20的制造成本。

在图2中,将电源闸控装置20结合至处理器装置10(例如,晶片102)。藉由混合结合而以面对面方式直接结合处理器装置10与电源闸控装置20,以使得处理器装置10的前侧10F结合至电源闸控装置20的前侧20F。具体而言,经由介电质对介电质结合将处理器装置10的介电层18结合至电源闸控装置20的介电层28,而不使用任何黏合材料(例如,晶粒贴合膜),且经由金属对金属结合将处理器装置10的晶粒连接件16A的子集结合至电源闸控装置20的晶粒连接件26,而不使用任何共晶材料(例如,焊料)。所述结合可包括预结合及回火。在预结合期间,施加小的按压力以将电源闸控装置20按压成抵靠处理器装置10(例如,晶片102)。在低温下实行预结合,且在预结合之后,介电层18与介电层28结合至彼此。然后,在后续回火步骤中提高结合强度,其中在高温下对介电层18及28进行回火。在回火之后,形成结合(例如熔合结合),从而将介电层18与介电层28结合。举例而言,所述结合可以是介电层18的材料与介电层28的材料之间的共价键。晶粒连接件16A与晶粒连接件26一一对应地连接至彼此。晶粒连接件16A与晶粒连接件26可在预结合之后实体接触,或可在回火期间发生膨胀而达到实体接触。此外,在回火期间,晶粒连接件16A的材料与晶粒连接件26的材料(例如,铜)混杂,以使得亦形成金属对金属结合。因此,处理器装置10与电源闸控装置20之间所得的结合是包括介电质对介电质结合及金属对金属结合两者的混合结合。

在混合结合之后,藉由直接结合将处理器装置10电性耦合至电源闸控装置20,经由所述直接结合实行控制传讯及电源/接地传讯。具体而言,处理器装置10可经由所述直接结合将控制讯号发送至电源闸控装置20,且可经由所述直接结合自电源闸控装置20接收电源/接地讯号。可藉由使用直接结合来改良处理器装置10与电源闸控装置20之间的传讯延时及内连带宽。此外,亦可减小内连的阻抗且因此减小内连的功耗。如上文所述,内连结构24的金属化图案可形成电源闸控网络结构中的一些或所有电源闸控网络结构。在这些实施例中,电源闸控网络结构因此藉由直接结合连接至处理器装置10,此可使得布线能够较其他类型的内连更简单。在所示的实施例中,一个电源闸控装置20结合至处理器装置10。在另一实施例中,多个电源闸控装置20结合至处理器装置10。

在图3中,形成环绕电源闸控装置20的介电层104。可在放置电源闸控装置20之后但在回火之前形成介电层104以完成混合结合,或可在回火之后形成介电层104。介电层104填充电源闸控装置20与晶片102的邻近装置区(未示出)中的其他装置之间的间隙,因此保护半导体装置。介电层104可以是:氧化物,例如氧化硅、PSG、BSG、BPSG等;氮化物,例如氮化硅等;聚合物,例如PBO、聚酰亚胺、BCB系聚合物等;包封体,例如模制化合物、环氧树脂等;类似物或其组合。在一些实施例中,介电层104是氧化物,例如氧化硅。在一些实施例中,介电层104是使用CVD工艺等沉积而成。

然后,形成延伸穿过介电层104的导通孔106。以形成导通孔106作为实例,在介电层104中图案化出开口。可藉由可接受的工艺进行图案化,例如当介电层104是感旋光性材料时藉由将介电层104暴露于光,或藉由使用例如非等向性蚀刻来蚀刻介电层104。开口会暴露出处理器装置10的晶粒连接件16B的子集。在介电层104上及在晶粒连接件16B的由开口暴露出的部分上形成晶种层。在一些实施例中,所述晶种层是金属层,所述金属层可以是单层或包括由不同的材料形成的多个子层的复合层。在特定实施例中,所述晶种层包括钛层及位于所述钛层之上的铜层。可使用例如PVD等来形成晶种层。在晶种层上形成导电材料。可藉由镀覆(例如,电镀覆或无电镀覆)等形成导电材料。导电材料可包括金属,例如铜、钛、钨、铝等。然后,移除晶种层的多余部分及导电材料的多余部分,其中所述多余部分是上覆于介电层104上的部分。可藉由平坦化工艺进行移除。对晶种层、导电材料、介电层104及电源闸控装置20实行平坦化工艺。所述移除会同时移除晶种层的多余部分及导电材料的多余部分且暴露出导通孔30。平坦化工艺可以是例如CMP工艺、研磨工艺、回蚀工艺、类似工艺或其组合。晶种层及导电材料在开口中的剩余部分形成导通孔106。在平坦化工艺之后,介电层104的顶表面、导通孔106的顶表面、半导体衬底22的顶表面及导通孔30的顶表面是平坦的。

图4、图5及图6是根据一些实施例的用于形成实施集成电路封装100的系统的工艺期间的中间步骤的剖视图。在此实施例中,集成电路封装100被进一步处理成包括重布线结构且被直接安装至封装衬底。

在图4中,在介电层104、导通孔106及电源闸控装置20上形成重布线结构108。重布线结构108包括介电层110及位于介电层110之中的金属化图案112(有时被称为重布线层或重布线线路)。举例而言,重布线结构108可包括藉由相应的介电层110彼此隔开的多个金属化图案112。重布线结构108的金属化图案112连接至导通孔106及电源闸控装置20(例如,连接至导通孔30)。

在一些实施例中,介电层110由聚合物形成,所述聚合物可以是可使用光刻掩模来加以图案化的感旋光性材料,例如PBO、聚酰亚胺、BCB系聚合物等。在其他实施例中,介电层110由以下材料形成:氮化物,例如氮化硅;氧化物,例如氧化硅、PSG、BSG、BPSG等。可藉由旋转涂布、层压、CVD等或其组合形成介电层110。在形成每一介电层110之后,然后将介电层110图案化以暴露出下伏的导电特征,例如下伏金属化图案112的一些部分。图案化可藉由可接受的工艺进行,例如藉由在介电层110是感旋光性材料时将介电层暴露于光,或藉由使用例如非等向性蚀刻来进行蚀刻。若介电层110是感旋光性材料,则可在曝光之后对介电层110进行显影。

金属化图案112各自包括导通孔及/或导电线。导通孔延伸穿过介电层110,且导电线沿着介电层110延伸。以形成金属化图案作为实例,在相应的下伏特征之上形成晶种层(未示出)。举例而言,当形成重布线结构108的最底层时,晶种层可形成于介电层104、导通孔106、半导体衬底22及导通孔30上,或者当形成重布线结构108的中间层/最顶层时,晶种层可形成于相应的介电层110上及穿过相应的介电层110的开口中。在一些实施例中,所述晶种层是金属层,所述金属层可以是单层或包括由不同的材料形成的多个子层的复合层。在一些实施例中,所述晶种层包括钛层及位于所述钛层之上的铜层。可使用例如PVD等沉积工艺形成所述晶种层。然后,在晶种层上形成光刻胶并将所述光刻胶图案化。可藉由旋转涂布等形成光刻胶且可将光刻胶暴露于光以进行图案化。光刻胶的图案对应于金属化图案。图案化会形成穿过光刻胶以暴露出晶种层的开口。在光刻胶的开口中及在晶种层的暴露部分上形成导电材料。可藉由镀覆(例如,电镀覆或无电镀覆等)形成导电材料。所述导电材料可包括金属或金属合金,例如铜、钛、钨、铝、等或其组合。然后,移除光刻胶及晶种层的上面未形成导电材料的部分。可藉由可接受的灰化或剥除工艺(例如使用氧等离子体等)移除光刻胶。一旦光刻胶被移除,则例如藉由使用可接受的蚀刻工艺(例如,藉由湿式蚀刻或干式蚀刻)移除晶种层的暴露部分。晶种层的剩余部分及导电材料形成重布线结构108中的一层的金属化图案。

说明重布线结构108作为实例。可藉由重复或省略上文所述的步骤来在重布线结构108中形成较所说明的更多或更少的介电层110及金属化图案112。

重布线结构108的金属化图案112包括电力供应源(V

重布线结构108的金属化图案112亦包括数据讯号线,所述数据讯号线藉由导通孔106电性耦合至处理器装置10。举例而言,导通孔106中的一些导通孔将处理器装置10的输入/输出(I/O)连接耦合至重布线结构108。因此,处理器装置10可耦合至外部装置。

在图5中,形成连接至重布线结构108的金属化图案112的导电连接件114。可将重布线结构108的顶部介电层110图案化以暴露出下伏金属化图案112的一些部分。在一些实施例中,可在开口中形成凸块下金属(under bump metallurgies,UBM)。在UBM上形成导电连接件114。导电连接件114可以是球栅数组(ball grid array,BGA)连接件、焊料柱、金属柱、受控塌陷芯片连接(controlled collapse chip connection,C4)凸块、微凸块、无电镀镍钯浸金技术(electroless nickel-electroless palladium-immersion gold,ENEPIG)形成的凸块等。导电连接件114可由金属或金属合金形成,例如焊料、铜、铝、金、镍、银、钯、锡等或其组合。在一些实施例中,首先经由一些常用方法(例如蒸镀、电镀覆、印刷、焊料转移、植球等)形成焊料层来形成导电连接件114。一旦已在结构上形成焊料层,则可实行回焊以将材料塑形成所期望的凸块形状。在另一实施例中,导电连接件114是藉由溅镀、印刷、电镀覆、无电镀覆、CVD等形成的金属柱(例如,铜柱)。金属柱可不具有焊料且具有实质上垂直的侧壁。

在图6中,藉由沿着切割道区(例如,在装置区102A周围)进行锯切来实行单体化工艺。单体化工艺包括锯切重布线结构108、介电层104及晶片102。单体化工艺将装置区102A(包括处理器装置10)与晶片102的邻近装置区(未示出)分离以形成包括处理器装置10的集成电路封装100。如上文所述,电源闸控装置20以面对面方式直接结合至处理器装置10,而不使用焊料。因此,所得的集成电路封装100不具有焊料。在单体化之后,重布线结构108(例如,介电层110)、介电层104及处理器装置10在侧向上毗连。

然后将集成电路封装100倒置并使用导电连接件114贴合至封装衬底200。封装衬底200可由半导体材料(例如硅、锗、金刚石等)制成。作为另外一种选择,亦可使用化合物材料,例如硅锗、碳化硅、镓砷、砷化铟、磷化铟、碳化硅锗、磷化镓砷、磷化镓铟、这些材料的组合等。另外,封装衬底200可以是SOI衬底。通常,SOI衬底包含一层半导体材料,例如外延硅、锗、硅锗、SOI、SGOI或其组合。在一个替代实施例中,封装衬底200基于绝缘芯,例如玻璃纤维加强型树脂芯。一种示例性芯材料是玻璃纤维树脂,例如FR4。芯材料的替代物包括双马来酰亚胺三嗪(bismaleimide-triazine,BT)树脂,或作为另外一种选择包括其他印刷电路板(printed circuit board,PCB)材料或膜。构成膜(例如,味之素构成膜(Ajinomotobuild-up film,ABF))或其他层压体可用于封装衬底200。

封装衬底200可包括有源装置及无源装置(未示出)。例如晶体管、电容器、电阻器、这些的组合等装置可用于产生系统的设计的结构要求及功能要求。可使用任何适合的方法形成所述装置。

封装衬底200亦可包括金属化层及通孔(未示出)以及位于所述金属化层及通孔之上的结合垫202。金属化层可形成于有源装置及无源装置之上,且被设计成对各种装置进行连接以形成功能电路系统。金属化层可由介电质(例如,低介电常数(low-k)介电材料)与导电材料(例如,铜)的交替层形成且可经由任何适合的工艺(例如沉积、镶嵌、双镶嵌等)形成,其中通孔对导电材料层进行内连。在一些实施例中,封装衬底200实质上不具有有源装置及无源装置。

对导电连接件114进行回焊以将重布线结构108的UBM贴合至结合垫202。导电连接件114将封装衬底200(包括封装衬底200中的金属化层)连接至集成电路封装100(包括重布线结构108的金属化图案112)。在一些实施例中,无源装置(例如,表面安装式装置(surfacemount device,SMD),未示出)可在被安装于封装衬底200上之前贴合至集成电路封装100(例如,结合至结合垫202)。在这些实施例中,无源装置可与导电连接件114结合至集成电路封装100的同一表面。在一些实施例中,无源装置(例如SMD,未示出)可贴合至封装衬底200,例如贴合至结合垫202。

导电连接件114在被回焊之前上面可形成有环氧助焊剂(未示出),其中在将集成电路封装100贴合至封装衬底200之后环氧助焊剂的环氧部分的至少一些保留下来。此剩余的环氧部分可用作底部填充胶以减小应力且保护对导电连接件114进行回焊所得的接头。在一些实施例中,底部填充胶(未示出)可形成于集成电路封装100与封装衬底200之间,从而环绕导电连接件114。可在贴合集成电路封装100之后藉由毛细流动过程形成底部填充胶,或可在贴合集成电路封装100之前藉由适合的沉积方法形成底部填充胶。

图7是根据一些其他实施例的集成电路封装100及实施集成电路封装100的系统的剖视图。此实施例类似于关于图6所述的实施例,但处理器装置10与电源闸控装置20以面对背方式直接结合。因此,重布线结构108的金属化图案112(例如,VDD线及VSS线)连接至晶粒连接件26,且藉由导通孔30电性耦合至处理器装置10。

处理器装置10与电源闸控装置20藉由混合结合而以面对背方式直接结合,以使得处理器装置10的前侧10F结合至电源闸控装置20的后侧20B。具体而言,处理器装置10的介电层18经由介电质对介电质结合而结合至电源闸控装置20的半导体衬底22,而不使用任何黏合材料(例如,晶粒贴合膜),且处理器装置10的晶粒连接件16A的子集经由金属对金属结合而结合至电源闸控装置20的导通孔30,而不使用任何共晶材料(例如,焊料)。结合可包括预结合及回火。在预结合期间,施加小的按压力以将电源闸控装置20按压成抵靠处理器装置10。在低温下实行预结合,且在预结合之后,介电层18与半导体衬底22结合至彼此。在一些实施例中,在电源闸控装置20的后侧20B处(例如在半导体衬底22上)形成氧化物(例如天然氧化物、热氧化物等),且所述氧化物用于结合。然后在后续回火步骤中提高结合强度,其中在高温下对介电层18及半导体衬底22进行回火。在回火之后,形成结合(例如熔合结合),从而结合介电层18与半导体衬底22。举例而言,所述结合可以是介电层18的材料与半导体衬底22的材料之间的共价键。晶粒连接件16A与导通孔30一一对应地连接至彼此。晶粒连接件16A与导通孔30可在预结合之后实体接触,或可在回火期间发生膨胀以达到实体接触。此外,在回火期间,晶粒连接件16A的材料与导通孔30的材料(例如,铜)混杂,以使得亦形成金属对金属结合。因此,处理器装置10与电源闸控装置20之间所得的结合是包括介电质对介电质结合及金属对金属结合两者的混合结合。

图8、图9、图10、图11、图12、图13、图14、图15及图16是根据一些其他实施例的用于形成实施集成电路封装100的系统的工艺期间的中间步骤的剖视图。在此实施例中,将集成电路封装100单体化并包括于封装组件中。说明将装置封装于一个封装区302A中,但应了解,可同时形成任何数目的封装区。将在后续处理中将封装区302A单体化。经单体化的封装组件可以是扇出型封装,例如集成扇出型(integrated fan-out,InFO)封装。然后,将扇出型封装安装至封装衬底。

在图8中,提供载体衬底302,且在载体衬底302上形成释放层304。载体衬底302可以是玻璃载体衬底、陶瓷载体衬底等。载体衬底302可以是晶片,以使得多个封装可同时形成于载体衬底302上。释放层304可由聚合物系材料形成,可将释放层304与载体衬底302一起自将在后续步骤中形成的上覆结构移除。在一些实施例中,释放层304是在受热时失去其黏合性质的环氧树脂系热释放材料,例如光热转换(light-to-heat-conversion,LTHC)释放涂层。在其他实施例中,释放层304可以是在暴露于紫外线(ultra-violet,UV)光时失去其黏合性质的UV胶。可以液体的形式施配释放层304并将释放层304固化,释放层304可以是层压至载体衬底302上的层压膜,或可以是类似的材料。释放层304的顶表面可齐平且可具有高程度的平坦度。

在图9中,可在释放层304上形成重布线结构306。重布线结构306可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成。重布线结构306包括介电层308及金属化图案310(有时被称为重布线层或重布线线路)。可在重布线结构306中形成较所说明的更多或更少的介电层308及金属化图案310。重布线结构306是可选的。在一些实施例中,在释放层304上形成不具有金属化图案的介电层来代替重布线结构306。

在图10中,形成延伸穿过重布线结构306的最顶部介电层308的导通孔312。因此,导通孔312连接至重布线结构306的金属化图案310。导通孔312是可选的且可省略。举例而言,在省略重布线结构306的实施例中可(或可不)省略导通孔312。

以形成导通孔312作为实例,可在重布线结构306的最顶部介电层308中形成开口。然后,在重布线结构306之上(例如,在最顶部介电层308上及在金属化图案310的由最顶部介电层308中的开口暴露出的部分上)形成晶种层。在一些实施例中,所述晶种层是金属层,所述金属层可以是单层或包括由不同的材料形成的多个子层的复合层。在特定实施例中,所述晶种层包括钛层及位于所述钛层之上的铜层。可使用例如PVD等来形成晶种层。在晶种层上形成光刻胶并将所述光刻胶图案化。可藉由旋转涂布等形成光刻胶且将光刻胶暴露于光以进行图案化。光刻胶的图案对应于导通孔。图案化会形成穿过光刻胶以暴露出晶种层的开口。在光刻胶的开口中及在晶种层的暴露部分上形成导电材料。导电材料可藉由镀覆(例如,电镀覆或无电镀覆等)形成。导电材料可包括金属,如铜、钛、钨、铝等。移除光刻胶、及晶种层的上面未形成导电材料的部分。可藉由可接受的灰化或剥除工艺(例如使用氧等离子体等)移除光刻胶。一旦光刻胶被移除,则例如藉由使用可接受的蚀刻工艺(例如,藉由湿式蚀刻或干式蚀刻)移除晶种层的暴露部分。晶种层的剩余部分及导电材料形成导通孔312。

在图11中,将经单体化的集成电路封装100放置在重布线结构306(例如,最顶部介电层308)上。为形成经单体化的集成电路封装100,获得与关于图3所述的中间结构类似的中间结构。藉由沿着切割道区(例如,在装置区102A(参见图3)周围)进行锯切来实行单体化工艺。单体化工艺包括锯切介电层104及晶片102。单体化工艺将装置区102A(包括处理器装置10)与晶片102的邻近装置区(未示出)分离以形成包括处理器装置10的集成电路封装100。如上文所述,电源闸控装置20以面对面方式直接结合至处理器装置10,而不使用焊料。因此,所得的集成电路封装100不具有焊料。在单体化之后,介电层104与处理器装置10在侧向上毗连。

在图12中,在导通孔312及集成电路封装100上及周围形成包封体314。在形成之后,包封体314包封导通孔312及集成电路封装100。包封体314可以是模制化合物、环氧树脂等。可藉由压缩模制、转移模制等施加包封体314,且包封体314可形成于载体衬底302之上以使得隐埋或覆盖集成电路封装100及/或导通孔312。可以液体或半液体形式施加包封体314且然后随后将包封体314固化。在一些实施例中,包封体314不同于介电层104且包含与介电层104不同的材料。然后,可对包封体314实行平坦化工艺以暴露出导通孔312及集成电路封装100。平坦化工艺可移除导通孔312的材料、包封体314的材料、介电层104的材料、导通孔106的材料、半导体衬底22的材料及/或导通孔30的材料,直至暴露出导通孔30、106、312。在平坦化工艺之后,平坦化组件的顶表面是共面的。平坦化工艺可以是例如化学机械抛光(CMP)、研磨工艺、回蚀等。在一些实施例中,举例而言若导通孔30、106、312已暴露出,则可省略平坦化。

在图13中,在包封体314、导通孔312及集成电路封装100上形成重布线结构316。可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成重布线结构316。重布线结构316包括介电层318及金属化图案320(有时被称为重布线层或重布线线路)。可在重布线结构316中形成较所说明的更多或更少的介电层318及金属化图案320。重布线结构316的金属化图案320连接至导通孔30、106、312。重布线结构316的金属化图案320包括电力供应源(V

在图14中,形成连接至重布线结构316的金属化图案320的导电连接件322。可以与关于图5所述的导电连接件114类似的方式且由类似的材料形成导电连接件322。举例而言,可在重布线结构316的UBM上形成导电连接件322。

在图15中,实行载体衬底剥离以将载体衬底302自重布线结构306(例如,最底部介电层308)剥除(剥离)。根据一些实施例,剥离包括将光(例如,激光或UV光)投射于释放层304上,以使得释放层304在光的热量下分解且可移除载体衬底302。然后,可将结构倒置并放置于例如条带上。

此外,穿过重布线结构306的最底部介电层308形成导电连接件324。可穿过重布线结构306的最底部介电层308形成开口,从而暴露出金属化图案310的部分。可例如使用激光钻孔、蚀刻等形成开口。导电连接件324形成于开口中,且连接至金属化图案310的暴露部分。可以与关于图5所述的导电连接件114类似的方式且由类似的材料形成导电连接件324。

在图16中,藉由沿着切割道区(例如,在封装区302A周围)进行锯切来实行单体化工艺。单体化工艺包括锯切重布线结构306、316及包封体314。单体化工艺将封装区302A与邻近封装区(未示出)分离以形成集成电路封装300。在单体化之后,重布线结构306、316(例如,介电层308、318)与包封体314在侧向上毗连。

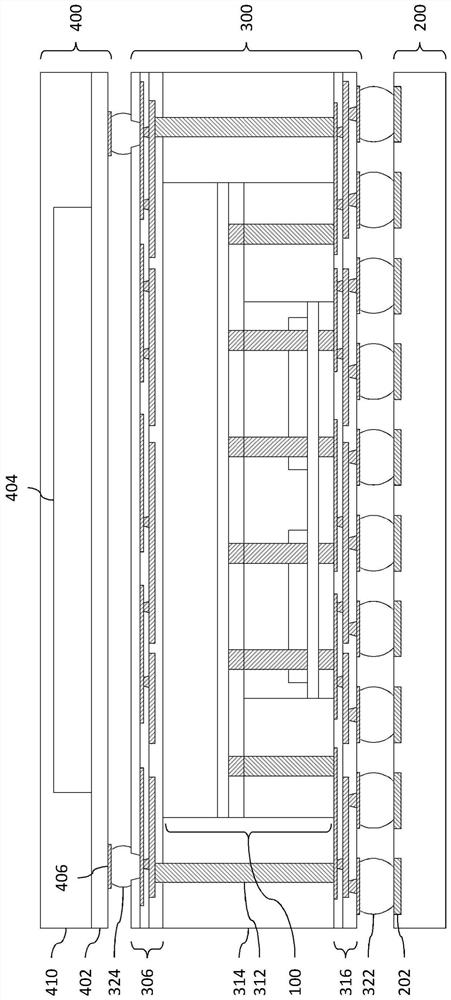

可将另一集成电路封装400贴合至集成电路封装300以形成迭层封装结构(package-on-package structure)。集成电路封装400可以是存储器封装。可在将集成电路封装300单体化之前或之后将集成电路封装400贴合至集成电路封装300。集成电路封装400包括衬底402以及连接至衬底402的一或多个晶粒404。在一些实施例中(未示出),晶粒404的一或多个堆叠连接至衬底402。衬底402可由半导体材料(例如硅、锗、金刚石等)制成。在一些实施例中,亦可使用化合物材料,例如硅锗、碳化硅、镓砷、砷化铟、磷化铟、碳化硅锗、磷化镓砷、磷化镓铟、这些材料的组合等。另外,衬底402可以是绝缘体上硅(silicon-on-insulator,SOI)衬底。通常,SOI衬底包含一层半导体材料,例如外延硅、锗、硅锗、SOI、绝缘体上硅锗(silicon germanium on insulator,SGOI)或其组合。在一个替代实施例中,衬底402基于绝缘芯,例如玻璃纤维加强型树脂芯。一种示例性芯材料是玻璃纤维树脂,例如FR4。芯材料的替代物包括双马来酰亚胺三嗪(BT)树脂,或作为另外一种选择,包括其他印刷电路板(PCB)材料或膜。构成膜(例如,味之素构成膜(ABF))或其他层压体可用于衬底402。

衬底402可包括有源装置及无源装置(未示出)。熟习此项技术者将认识到,各种各样的装置(例如,晶体管、电容器、电阻器、这些的组合等)可用于产生集成电路封装400的设计的结构要求及功能要求。可使用任何适合的方法形成装置。衬底402亦可包括金属化层(未示出)及穿孔。金属化层可形成于有源装置及无源装置之上且被设计成对各种装置进行连接以形成功能电路系统。金属化层可由介电质(例如,低介电常数介电材料)及导电材料(例如,铜)的交替层形成且可经由任何适合的工艺(例如沉积、镶嵌、双镶嵌等)形成,其中通孔对导电材料层进行内连。在一些实施例中,衬底402实质上不具有有源装置及无源装置。

衬底402可在衬底402的一侧上具有结合垫406,以连接至导电连接件324。在一些实施例中,藉由在衬底402的所述侧上的介电层(未示出)中形成凹陷部(未示出)来形成结合垫406。凹陷部可被形成为使得结合垫406能够嵌置至介电层中。在其他实施例中,当结合垫406可形成于介电层上时,省略凹陷部。在一些实施例中,结合垫406包括由铜、钛、镍、金、钯等或其组合制成的薄晶种层(未示出)。可在薄晶种层之上沉积结合垫406的导电材料。可藉由电化学镀覆工艺、无电镀覆工艺、CVD、ALD、PVD等或其组合形成导电材料。在一实施例中,结合垫406的导电材料是铜、钨、铝、银、金等或其组合。

在一实施例中,结合垫406是包括三个导电材料层(例如钛层、铜层及镍层)的UBM。举例而言,结合垫406可由铜形成,可形成于钛层(未示出)上且具有镍饰面,所述镍饰面可延长集成电路封装400的储放寿命,此在集成电路封装400是存储器装置(例如,动态随机存取存储器(Dynamic Random Access Memory,DRAM)模块)时可特别有利。然而,熟习此项技术者应认识到,存在适合于形成结合垫406的诸多适合的材料及层的排列,例如铬/铬-铜合金/铜/金的排列、钛/钛钨/铜的排列、或铜/镍/金的排列。可用于结合垫406的任何适合的材料或材料层完全旨在包括于本申请案的范围内。

在所说明的实施例中,晶粒404藉由导电凸块连接至衬底402,但可使用其他连接,例如打线结合。在一实施例中,晶粒404是堆叠式存储器晶粒。举例而言,晶粒404可以是存储器晶粒,例如低功率(low-power,LP)双倍数据速率(double data rate,DDR)存储器模块,例如LPDDR1、LPDDR2、LPDDR3、LPDDR4等。

可藉由模制材料410包封晶粒404及打线结合(当存在时)。可例如使用压缩模制将模制材料410模制于晶粒404及打线结合上。在一些实施例中,模制材料410是模制化合物、聚合物、环氧树脂、氧化硅填料材料等或其组合。可实行固化工艺以将模制材料410固化;固化工艺可以是热固化、UV固化等或其组合。在一些实施例中,晶粒404隐埋于模制材料410中,且在将模制材料410固化之后,实行平坦化步骤(例如,研磨)以移除模制材料410的多余部分且为集成电路封装400提供实质上平坦的表面。

在形成集成电路封装400之后,藉由导电连接件324将集成电路封装400贴合至集成电路封装300。可藉由对导电连接件324进行回焊来将导电连接件324连接至结合垫406。因此,晶粒404可经由导电连接件324、导通孔312及重布线结构306、316电性耦合至集成电路封装100。

在一些实施例中,在衬底402的与晶粒404相对的一侧上形成阻焊剂(未示出)。可将导电连接件324设置于阻焊剂中的开口中以连接至衬底402中的导电特征(例如,结合垫406)。阻焊剂可用于保护衬底402的一些区域不受外部损坏。

在一些实施例中,导电连接件324在被回焊之前上面形成有环氧助焊剂(未示出),其中在将集成电路封装400贴合至重布线结构306之后环氧助焊剂的环氧部分的至少一些保留下来。

在一些实施例中,底部填充胶(未示出)形成于重布线结构306与衬底402之间,从而环绕导电连接件324。底部填充胶可减小应力且保护对导电连接件324进行回焊所得的接头。可在贴合集成电路封装400之后藉由毛细流动过程形成底部填充胶,或可在贴合集成电路封装400之前藉由适合的沉积方法形成底部填充胶。在形成有环氧助焊剂的实施例中,环氧助焊剂可用作底部填充胶。

然后,将迭层封装结构倒置并使用导电连接件322贴合至封装衬底200。封装衬底200可类似于关于图6所述的封装衬底200。举例而言,封装衬底200可包括连接至导电连接件322的结合垫202。

图17是根据一些其他实施例的集成电路封装100及实施集成电路封装100的系统的剖视图。此实施例类似于关于图16所述的实施例,但处理器装置10与电源闸控装置20以面对背方式直接结合,这类似于关于图7所述的混合结合。因此,重布线结构316的金属化图案320(例如,V

图18是根据一些其他实施例的集成电路封装100及实施集成电路封装100的系统的剖视图。此实施例类似于关于图16所述的实施例,但省略了重布线结构306、导通孔312及集成电路封装400。

图19是根据一些其他实施例的集成电路封装100及实施集成电路封装100的系统的剖视图。此实施例类似于关于图17所述的实施例,但省略了重布线结构306、导通孔312及集成电路封装400。

图20、图21、图22、图23及图24是根据一些实施例的用于形成集成电路封装500的工艺期间的中间步骤的剖视图。藉由堆叠各自包封于包封材料中的多个半导体装置层来形成集成电路封装500。说明将装置封装于一个封装区502A中,但应了解,可同时形成任何数目的封装区。将在后续处理中将封装区502A单体化。经单体化的封装组件可以是多重堆叠(multi-stacked,MUST)封装。然后,将MUST封装安装至封装衬底。

在图20中,提供载体衬底502,且在载体衬底502上形成释放层504。可以与关于图8所述的载体衬底302类似的方式且由类似的材料形成载体衬底502。可以与关于图8所述的释放层304类似的方式且由类似的材料形成释放层504。然后,将与关于图1所述的处理器装置类似的处理器装置10(例如,包括半导体衬底12、内连结构14、晶粒连接件16及介电层18)放置于释放层504上。

在图21中,在处理器装置10上及周围形成包封体506。可以与关于图12所述的包封体314类似的方式且由类似的材料形成包封体506。若需要,可对包封体506实行平坦化工艺以暴露出晶粒连接件16。

在图22中,在包封体506及处理器装置10上形成重布线结构510。可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成重布线结构510。重布线结构510包括介电层512及金属化图案514(有时被称为重布线层或重布线线路)。可在重布线结构510中形成较所说明的更多或更少的介电层512及金属化图案514。重布线结构510的金属化图案514连接至处理器装置10的晶粒连接件16。

在图23中,形成延伸穿过重布线结构510的最顶部介电层512的导通孔516。可以与关于图10所述的导通孔312类似的方式且由类似的材料形成导通孔516。

将一或多个电源闸控装置20放置于重布线结构510(例如,最顶部介电层512)上。每一电源闸控装置20可类似于关于图1所述的电源闸控装置(例如,包括半导体衬底22、内连结构24、晶粒连接件26及介电层28)。电源闸控装置20将经由MUST封装的重布线结构电性耦合至处理器装置10,且因此不必形成导通孔30(参见图1)。因此,可降低电源闸控装置20的制造成本。

在图24中,在电源闸控装置20及导通孔516上及周围形成包封体518。包封体518可以与关于图12所述的包封体314类似的方式且由类似的材料形成。若需要,可对包封体518实行平坦化工艺以暴露出导通孔516及晶粒连接件26。

图25、图26、图27及图28是根据一些实施例的用于形成实施集成电路封装500的系统的工艺期间的中间步骤的剖视图。在此实施例中,集成电路封装500被进一步处理成包括重布线结构,且直接安装至封装衬底。

在图25中,在包封体518及电源闸控装置20上形成重布线结构520。可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成重布线结构520。重布线结构520包括介电层522及金属化图案524(有时被称为重布线层或重布线线路)。可在重布线结构520中形成较所说明的更多或更少的介电层522及金属化图案524。重布线结构520的金属化图案524连接至导通孔516及电源闸控装置20的晶粒连接件26。因此,处理器装置10经由导通孔514及重布线结构510的金属化图案524电性耦合至重布线结构520的金属化图案524。

重布线结构520的金属化图案524包括电性耦合至电源闸控装置20的输入端子的电力供应源(V

在图26中,形成连接至重布线结构520的金属化图案524的导电连接件526。可以与关于图5所述的导电连接件114类似的方式且由类似的材料形成导电连接件526。

在图27中,实行载体衬底剥离以将载体衬底502自重布线结构510(例如,最底部介电层512)剥除(剥离)。根据一些实施例,剥离包括将光(例如,激光或UV光)投射于释放层504上,以使得释放层504在光的热量下分解且可移除载体衬底502。然后,可将结构倒置并放置于例如条带上。

在图28中,藉由沿着切割道区(例如,在封装区502A周围)进行锯切来实行单体化工艺。单体化工艺包括锯切重布线结构510、520及包封体506、518。单体化工艺将封装区502A与邻近封装区(未示出)分离以形成集成电路封装500。在单体化之后,重布线结构510、520(例如,介电层512、522)与包封体506、518在侧向上毗连。

然后,使用导电连接件526将集成电路封装500贴合至封装衬底200。封装衬底200可类似于关于图6所述的封装衬底200。举例而言,封装衬底200可包括连接至导电连接件526的结合垫202。

图29、图30、图31、图32、图33及图34是根据一些实施例的用于形成实施集成电路封装500的系统的工艺期间的中间步骤的剖视图。在此实施例中,将集成电路封装500单体化并包括于封装组件中。说明将装置封装于一个封装区602A中,但应了解,可同时形成任何数目的封装区。将在后续处理中将封装区602A单体化。经单体化的封装组件可以是扇出型封装,例如集成扇出型(InFO)封装。然后,将扇出型封装安装至封装衬底。

在图29中,提供载体衬底602,且在载体衬底602上形成释放层604。可以与关于图8所述的载体衬底302类似的方式且由类似的材料形成载体衬底602。可以与关于图8所述的释放层304类似的方式且由类似的材料形成释放层604。

可在释放层604上形成重布线结构606。可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成重布线结构606。重布线结构606包括介电层608及金属化图案610(有时被称为重布线层或重布线线路)。可在重布线结构606中形成较所说明的更多或更少的介电层608及金属化图案610。重布线结构606是可选的。在一些实施例中,在释放层604上形成不包括金属化图案的介电层来代替重布线结构606。

在图30中,形成延伸穿过重布线结构606的最顶部介电层608的导通孔612。因此,导通孔612连接至重布线结构606的金属化图案610。可以与关于图10所述的导通孔312类似的方式且由类似的材料形成导通孔612。导通孔612是可选的,且可被省略。举例而言,在省略重布线结构606的实施例中可(或可不)省略导通孔612。

将经单体化的集成电路封装500邻近于导通孔612放置于重布线结构606(例如,最顶部介电层608)上。为形成经单体化的集成电路封装500,获得与关于图24所述的中间结构类似的中间结构。实行载体衬底剥离以将中间结构自载体衬底502(参见图24)剥除(剥离)。然后,藉由沿着切割道区(例如,在封装区502A(参见图24)周围)进行锯切来实行单体化工艺。单体化工艺包括锯切重布线结构510及包封体506、518。单体化工艺将封装区502A与邻近封装区(未示出)分离以形成集成电路封装500。在单体化之后,重布线结构510(例如,介电层512)与包封体506、518在侧向上毗连。

在图31中,在导通孔612及集成电路封装500上及周围形成包封体614。可以与关于图12所述的包封体314类似的方式且由类似的材料形成包封体614。在一些实施例中,包封体614不同于包封体506、518且包含与包封体506、518不同的材料。若需要,可对包封体614实行平坦化工艺以暴露出晶粒连接件26及导通孔516、612。

在图32中,在包封体614、导通孔612及集成电路封装500上形成重布线结构616。可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成重布线结构616。重布线结构616包括介电层618及金属化图案620(有时被称为重布线层或重布线线路)。可在重布线结构616中形成较所说明的更多或更少的介电层618及金属化图案620。重布线结构616的金属化图案620连接至晶粒连接件26及导通孔516、612。重布线结构616的金属化图案620包括电力供应源(V

形成连接至重布线结构616的金属化图案620的导电连接件622。可以与关于图5所述的导电连接件114类似的方式且由类似的材料形成导电连接件622。举例而言,可在重布线结构616的UBM上形成导电连接件622。

在图33中,实行载体衬底剥离以将载体衬底602自重布线结构606(例如,最底部介电层608)剥除(剥离)。根据一些实施例,剥离包括将光(例如,激光或UV光)投射于释放层604上,以使得释放层604在光的热量下分解且可移除载体衬底602。然后,可将结构倒置并放置于例如条带上。

此外,形成重布线结构606的最底部介电层608的导电连接件624。可穿过重布线结构606的最底部介电层608形成开口,从而暴露出金属化图案610的部分。可例如使用激光钻孔、蚀刻等形成开口。在开口中形成导电连接件624,且导电连接件624连接至金属化图案610的暴露部分。可以与关于图5所述的导电连接件114类似的方式且由类似的材料形成导电连接件624。

在图34中,藉由沿着切割道区(例如,在封装区602A周围)进行锯切来实行单体化工艺。单体化工艺包括锯切重布线结构606、616及包封体614。单体化工艺将封装区602A与邻近封装区(未示出)分离以形成集成电路封装600。在单体化之后,重布线结构606、616(例如,介电层608、618)与包封体614在侧向上毗连。

可将另一集成电路封装400贴合至集成电路封装600以形成迭层封装结构。集成电路封装400可在集成电路封装600被单体化之前或之后贴合至集成电路封装600。集成电路封装400可类似于关于图16所述的集成电路封装400。举例而言,集成电路封装400可包括连接至导电连接件624的结合垫406。

然后,将迭层封装结构倒置并使用导电连接件622贴合至封装衬底200。封装衬底200可类似于关于图6所述的封装衬底200。举例而言,封装衬底200可包括连接至导电连接件622的结合垫202。

图35、图36、图37、图38、图39及图40是根据一些其他实施例的用于形成集成电路封装700的工艺期间的中间步骤的剖视图。藉由将处理器装置10及电源闸控装置20单体化并将处理器装置10及电源闸控装置20包括于封装组件中来形成集成电路封装700。说明将装置封装于一个封装区702A中,但应了解,可同时形成任何数目的封装区。将在后续处理中将封装区702A单体化。经单体化的封装组件可以是扇出型封装,例如集成扇出型(InFO)封装。然后,将扇出型封装安装至封装衬底。

在图35中,提供载体衬底702,且在载体衬底702上形成释放层704。可以与关于图8所述的载体衬底302类似的方式且由类似的材料形成载体衬底702。可以与关于图8所述的释放层304类似的方式且由类似的材料形成释放层704。然后,在释放层704上形成导通孔706,且导通孔706远离释放层704延伸。可以与关于图10所述的导通孔312类似的方式且由类似的材料形成导通孔706。

然后,将与关于图1所述的处理器装置类似的处理器装置10(例如,包括半导体衬底12、内连结构14、晶粒连接件16及介电层18)邻近于导通孔706而放置于释放层704上。在此实施例中,处理器装置10还包括被形成为延伸穿过半导体衬底12的导通孔708。导通孔708电性耦合至内连结构14的金属化图案。

在图36中,在导通孔706及处理器装置10上及周围形成包封体710。可以与关于图12所述的包封体314类似的方式且由类似的材料形成包封体710。若需要,可对包封体710实行平坦化工艺以暴露出晶粒连接件16及导通孔706。

在图37中,在包封体710、导通孔706及处理器装置10上形成重布线结构712。可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成重布线结构712。重布线结构712包括介电层714及金属化图案716(有时被称为重布线层或重布线线路)。可在重布线结构712中形成较所说明的更多或更少的介电层714及金属化图案716。重布线结构712的金属化图案716连接至晶粒连接件16及导通孔706。

形成连接至重布线结构712的金属化图案716的导电连接件718。可以与关于图5所述的导电连接件114类似的方式且由类似的材料形成导电连接件718。举例而言,可在重布线结构712的UBM上形成导电连接件718。

在图38中,实行载体衬底剥离以将载体衬底702自处理器装置10剥除(剥离)。根据一些实施例,剥离包括将光(例如,激光或UV光)投射于释放层704上,以使得释放层704在光的热量下分解且可移除载体衬底702。然后,可将结构倒置并放置于例如条带上。

在包封体710、导通孔706及处理器装置10上形成重布线结构720。可以与关于图4所述的重布线结构108类似的方式且由类似的材料形成重布线结构720。重布线结构720包括介电层722及金属化图案724(有时被称为重布线层或重布线线路)。可在重布线结构720中形成较所说明的更多或更少的介电层722及金属化图案724。重布线结构720的金属化图案724连接至导通孔706、708。

在图39中,利用导电连接件726将与关于图1所述的电源闸控装置类似的电源闸控装置20(例如,包括半导体衬底22、内连结构24及晶粒连接件26)贴合至重布线结构720。电源闸控装置20将经由重布线结构712、720(例如,金属化图案716、724)电性耦合至处理器装置10,且因此不必形成导通孔30(参见图1)。此外,电源闸控装置20中亦可省略介电层28(参见图1)。因此,可降低电源闸控装置20的制造成本。

在一些实施例中,电源闸控装置20贴合至导电凸块,例如微凸块。举例而言,晶粒连接件728可被形成为延伸穿过重布线结构720的最底部介电层722。以形成晶粒连接件728作为实例,可穿过重布线结构720的最底部介电层722形成开口,从而暴露出金属化图案724的部分。可例如使用激光钻孔、蚀刻等形成开口。可在开口中镀覆或沉积晶粒连接件728,且晶粒连接件728连接至金属化图案724的暴露部分。形成导电连接件726,从而连接相应的成对晶粒连接件26、728。可以与关于图5所述的导电连接件114类似的方式且由类似的材料形成导电连接件726。在此实施例中,处理器装置10的后侧面向电源闸控装置20的前侧。

重布线结构712的金属化图案716包括电力供应源(V

然后,在电源闸控装置20与重布线结构720之间形成底部填充胶730,从而环绕导电连接件726。可在贴合电源闸控装置20之后藉由毛细流动过程形成底部填充胶730,或可在贴合电源闸控装置20之前藉由适合的沉积方法形成底部填充胶730。

在电源闸控装置20及底部填充胶730上及周围形成包封体732。可以与关于图12所述的包封体314类似的方式且由类似的材料形成包封体732。若需要,可对包封体710实行平坦化工艺以暴露出电源闸控装置20。

在图40中,藉由沿着切割道区(例如,在封装区702A周围)进行锯切来实行单体化工艺。单体化工艺包括锯切重布线结构712、720及包封体710、732。单体化工艺将封装区702A与邻近封装区(未示出)分离以形成集成电路封装700。在单体化之后,重布线结构712、720(例如,介电层714、722)与包封体710、732在侧向上毗连。

然后,使用导电连接件718将集成电路封装700贴合至封装衬底200。封装衬底200可类似于关于图6所述的封装衬底200。举例而言,封装衬底200可包括连接至导电连接件718的结合垫202。

图41是根据一些其他实施例的集成电路封装700的剖视图。此实施例类似于关于图40所述的实施例,但处理器装置10的前侧面向电源闸控装置20的前侧。因此,重布线结构720的金属化图案724(例如,V

实施例可达成许多优点。形成电源闸控装置20与处理器装置10分离的集成电路封装使得电源闸控装置20能够形成有较处理器装置10大的有源装置。因此,可使用技术节点大的开关晶体管来进行电力输送。技术节点大的开关晶体管可适应较大的冲击电流且在处理器装置10的电路区块接通时具有较小的电压降(例如,IR降),且亦具有较小的电力泄漏。因此,可减小所得的集成电路封装的功耗。

亦可包括其他特征及工艺。举例而言,可包括测试结构以辅助对三维(three-dimensional,3D)封装或三维集成电路(three-dimensional integrated circuit,3DIC)装置进行验证测试。所述测试结构可包括例如形成于重布线层中或衬底上的测试垫(testpad),以使得能对3D封装或3DIC装置进行测试、使用探针及/或探针卡(probe card)等。可对中间结构以及最终结构实行验证测试。另外,本文中所揭露的结构及方法可与包含对已知良好晶粒(known good die)进行中间验证的测试方法结合使用以提高良率并降低成本。

在一实施例中,一种装置包括:处理器晶粒,包括电路区块,所述电路区块包括具有第一技术节点的有源装置;电源闸控晶粒,包括具有第二技术节点的功率半导体装置,所述第二技术节点大于所述第一技术节点;以及第一重布线结构,包括第一金属化图案,所述第一金属化图案包括电力供应源线及电力供应接地线,其中所述电路区块的第一子集经由所述功率半导体装置电性耦合至所述电力供应源线及所述电力供应接地线,且所述电路区块的第二子集永久地电性耦合至所述电力供应源线及所述电力供应接地线。

在一些实施例中,所述装置还包括:封装衬底;以及导电连接件,连接至所述封装衬底及所述第一重布线结构的所述第一金属化图案。在所述装置的一些实施例中,所述处理器晶粒与所述电源闸控晶粒藉由介电质对介电质结合及藉由金属对金属结合直接结合,且所述装置还包括:导通孔,连接至所述处理器晶粒及所述第一重布线结构的所述第一金属化图案;以及介电层,环绕所述导通孔及所述电源闸控晶粒,所述介电层及所述电源闸控晶粒各自设置于所述第一重布线结构与所述处理器晶粒之间,所述第一重布线结构、所述介电层及所述处理器晶粒在侧向上毗连。在所述装置的一些实施例中,所述处理器晶粒与所述电源闸控晶粒藉由介电质对介电质结合及藉由金属对金属结合直接结合,且所述装置还包括:导通孔,连接至所述处理器晶粒及所述第一重布线结构的所述第一金属化图案;介电层,环绕所述导通孔及所述电源闸控晶粒,所述介电层及所述电源闸控晶粒各自设置于所述第一重布线结构与所述处理器晶粒之间,所述介电层与所述处理器晶粒在侧向上毗连;以及包封体,环绕所述处理器晶粒及所述介电层,所述包封体与所述第一重布线结构在侧向上毗连。在所述装置的一些实施例中,所述第一重布线结构的所述第一金属化图案连接至所述电源闸控晶粒,且所述装置还包括:第二重布线结构,设置于所述处理器晶粒与所述电源闸控晶粒之间,所述第二重布线结构包括第二金属化图案,所述处理器晶粒连接至所述第二金属化图案;第一包封体,环绕所述电源闸控晶粒;导通孔,延伸穿过所述第一包封体,所述导通孔连接至所述第一重布线结构的所述第一金属化图案及所述第二重布线结构的所述第二金属化图案;以及第二包封体,环绕所述处理器晶粒,所述第二包封体、所述第二重布线结构、所述第一包封体及所述第一重布线结构在侧向上毗连。在所述装置的一些实施例中,所述第一重布线结构的所述第一金属化图案连接至所述电源闸控晶粒,且所述装置还包括:第二重布线结构,设置于所述处理器晶粒与所述电源闸控晶粒之间,所述第二重布线结构包括第二金属化图案,所述处理器晶粒连接至所述第二金属化图案;第一包封体,环绕所述电源闸控晶粒;导通孔,延伸穿过所述第一包封体,所述导通孔连接至所述第一重布线结构的所述第一金属化图案及所述第二重布线结构的所述第二金属化图案;第二包封体,环绕所述处理器晶粒,所述第二包封体、所述第二重布线结构及所述第一包封体在侧向上毗连;以及第三包封体,环绕所述第二包封体、所述第二重布线结构及所述第一包封体,所述第三包封体与所述第一重布线结构在侧向上毗连。在所述装置的一些实施例中,所述第一重布线结构的所述第一金属化图案连接至所述处理器晶粒,且所述装置还包括:第二重布线结构,设置于所述处理器晶粒与所述电源闸控晶粒之间,所述第二重布线结构包括第二金属化图案,所述第二金属化图案连接至所述处理器晶粒及所述电源闸控晶粒;第一包封体,环绕所述处理器晶粒;导通孔,延伸穿过所述第一包封体,所述导通孔连接至所述第一重布线结构的所述第一金属化图案及所述第二重布线结构的所述第二金属化图案;以及第二包封体,环绕所述电源闸控晶粒,所述第二包封体、所述第一包封体、所述第二重布线结构及所述第一重布线结构在侧向上毗连。在所述装置的一些实施例中,所述电源闸控晶粒能够在运行时间操作以自所述处理器晶粒接收控制讯号,且因应于所述控制讯号而将所述处理器晶粒的所述电路区块的所述第一子集接通或关断。在所述装置的一些实施例中,所述处理器晶粒的所述有源装置是互补金属氧化物半导体装置,且所述电源闸控晶粒的所述功率半导体装置是绝缘闸双极晶体管装置或双扩散金属氧化物半导体装置。

在一实施例中,一种装置包括:处理器晶粒,包括电路区块,所述电路区块包括具有第一技术节点的有源装置;电源闸控晶粒,藉由介电质对介电质结合及藉由金属对金属结合直接结合至所述处理器晶粒,所述电源闸控晶粒包括具有第二技术节点的功率半导体装置,所述第二技术节点大于所述第一技术节点,所述功率半导体装置电性耦合至所述电路区块的第一子集;介电层,环绕所述电源闸控晶粒;第一导通孔,延伸穿过所述介电层,所述第一导通孔电性耦合至所述电路区块的第二子集;以及第一重布线结构,包括第一金属化图案,所述第一金属化图案包括连接至所述第一导通孔及所述电源闸控晶粒的电力供应源线;封装衬底;以及第一导电连接件,将所述封装衬底连接至所述第一重布线结构的所述第一金属化图案。

在所述装置的一些实施例中,所述处理器晶粒、所述介电层及所述第一重布线结构在侧向上毗连。在所述装置的一些实施例中,所述处理器晶粒与所述介电层在侧向上毗连,且所述装置还包括:包封体,环绕所述处理器晶粒及所述介电层,所述包封体与所述第一重布线结构在侧向上毗连。在一些实施例中,所述装置还包括:第二重布线结构,包括第二金属化图案,所述包封体设置于所述第一重布线结构与所述第二重布线结构之间;第二导通孔,延伸穿过所述包封体,所述第二导通孔连接至所述第二重布线结构的所述第二金属化图案及所述第一重布线结构的所述第一金属化图案;存储器封装;以及第二导电连接件,将所述存储器封装连接至所述第二重布线结构的所述第二金属化图案。在所述装置的一些实施例中,所述处理器晶粒的所述有源装置是互补金属氧化物半导体装置,且所述电源闸控晶粒的所述功率半导体装置是绝缘闸双极晶体管装置或双扩散金属氧化物半导体装置。在所述装置的一些实施例中,所述处理器晶粒与所述电源闸控晶粒以面对面方式直接结合。在所述装置的一些实施例中,所述处理器晶粒与所述电源闸控晶粒以面对背方式直接结合。

在一实施例中,一种方法包括:将电源闸控晶粒结合至晶片,所述晶片包括处理器晶粒,所述电源闸控晶粒与所述处理器晶粒包括节距不同的有源装置,所述电源闸控晶粒包括第一导通孔;在所述电源闸控晶粒周围且在所述晶片上形成介电层;在第一介电层中图案化出开口,所述开口暴露出所述处理器晶粒的晶粒连接件;将导电材料镀覆于所述开口中及所述晶粒连接件上;将所述导电材料平坦化以在所述开口中形成第二导通孔,所述平坦化暴露出所述电源闸控晶粒的所述第一导通孔;以及锯切所述介电层及所述晶片以将所述处理器晶粒单体化。

在一些实施例中,在所述锯切之前,所述方法还包括:在所述电源闸控晶粒、所述介电层及所述第二导通孔上形成重布线结构,所述锯切包括锯切所述重布线结构。在一些实施例中,在所述锯切之后,所述方法还包括:利用包封体包封所述电源闸控晶粒及所述介电层;以及在所述包封体、所述电源闸控晶粒、所述介电层及所述第二导通孔上形成重布线结构。在所述方法的一些实施例中,所述电源闸控晶粒包括技术节点较所述处理器晶粒大的有源装置。

前述内容概述了数个实施例的特征,以使熟习此项技术者可更佳地理解本揭露的各个态样。熟习此项技术者应了解,他们可容易地使用本揭露作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的及/或达成与本文中所介绍的实施例相同的优点。熟习此项技术者亦应意识到,这些等效构造并不背离本揭露的精神及范畴,而且他们可在不背离本揭露的精神及范畴的情况下对其作出各种改变、代替及变更。

- 集成电路封装及其形成方法、晶圆级集成电路封装结构

- 集成电路封装件及其形成方法