一种输入信号的自检方法和自检电路

文献发布时间:2023-06-19 11:27:38

技术领域

本发明涉及液晶模组的显示和测试技术领域。更具体地,涉及一种输入信号的自检方法和自检电路。

背景技术

随着消费电子业的发展,DP(DisplayPort)接口越来越多应用在4K、高刷新率等高端显示器。随着智能手机的发展,下一代显示模组也将放弃数据带宽较低的MIPI接口(移动产业处理器接口)而采用嵌入式DP接口。

对带有DP接口的显示模组的检测环节中,上位机将模组参数和图片传递至控制器,控制器将从上位机接收到的模组参数和图片传递至FPGA(Field Programmable GateArray,现场可编程门阵列),FPGA将模组参数和图片分别存储于内部寄存器和存储器中,需要发送图片时,FPGA将存储器中图片的像素数据读出并传递给DP内核,DP内核根据模组参数把图片的像素数据按DP协议装帧成并行数据,进行并串转换后,通过DP电缆发送给显示模组。其中,DP内核是设置于FPGA中的用于把其接收到的像素数据装帧成DP协议格式,通过DP电缆输出的驱动电路。

由于DP协议本身的复杂性和显示模组的多样性,检测时的显示模组时常出现黑屏、画面异常等情况。本领域技术人员在进行错误排查时,先通过软件来寻找缺陷,排查无误后,再通过借助示波器测量DP内核的输入信号的正确性,步骤复杂且浪费时间。此外,受场地和工作环境限制,示波器的使用具有很大的局限性,有时还受检测设备的结构限制不能安装探头,导致示波器不能使用。

发明内容

有鉴于此,本发明第一个实施例提供一种输入信号的自检方法,用以判断FPGA中DP内核输入信号的准确性,包括:

接收并检测所述输入信号,得到检测结果;

存储所述检测结果;

根据接收到的读取命令,读取所述检测结果并根据所述检测结果判断输入信号有无异常。

在一个具体实施例中,所述输入信号包括输入时钟信号,计算获得所述输入时钟信号的真实频率。

在一个具体实施例中,所述计算获得所述输入时钟信号的真实频率包括:

提供基准方波信号,确定基准方波信号的计数周期和/或频率;

将所述基准方波信号与所述输入时钟信号同步;

在所述基准方波信号的计数周期内,计量所述输入时钟信号的脉冲数;

根据计量得到的脉冲数和基准方波的计数周期和/或频率计算得到所述输入时钟信号的真实频率。

在一个具体实施例中,所述基准方波信号的获取方式为:提供任意已知频率的基准时钟信号,对所述基准时钟信号进行计数分频得到所述基准方波信号,同时设定所述基准方波信号的计数周期和/或频率。

在一个具体实施例中,所述输入信号包括多个行场同步信号,对多个所述行场同步信号进行计算获得信号参数。

在一个具体实施例中,所述对所述行场同步信号进行计算获得信号参数包括:

根据多个所述行场同步信号的波形关系,计算获取所述行场同步信号的水平参数信息和垂直参数信息,对所述水平参数信息和垂直参数信息进行字节合并得到信号参数。

在一个具体实施例中,所述检测结果直接或者拆分存放于DP内核的寄存器列表中。

本发明另一方面提供一种输入信号的自检电路,设置于FPGA的DP内核,其特征在于,包括:

检测单元,用于接收并检测DP内核的输入信号;

存储单元,连接至所述检测单元,以存储输入信号的检测结果。

在一个具体实施例中,所述输入信号包括:输入时钟信号和多个行同步信号,所述检测单元包括:用于检测所述输入时钟单元频率的时钟检测单元和用于检测所述行同步信号的信号参数的时序检测模块,其中,所述时序检测模块包括:用于检测所述行场同步信号的水平参数信息的水平参数计数电路和用于检测所述行场同步信号的垂直参数信息的垂直参数行计数电路。

在一个具体实施例中,所述存储单元采用DP内核的寄存器列表,所述寄存器列表连接至控制器,以便于供所述控制器读取检测结果。

本发明的有益效果如下:

本发明实施例提供的一种输入信号的自检方法,第一时间先确保输入DP内核的重要信号正确无误,从而达到DP模组调试过程少走弯路、更快响应的目的,时钟频率计算电路采用了特殊的计算方式,巧妙地消去了除法、乘法计算,从而节省了硬件资源。由于只需计算出频率判断时钟的工作状态,不需很高的精度,所以,对所选取的基准时钟和被测时钟的频率高低、相位关系没有什么要求,适用性比较强,基本上适应DP、非DP的各种液晶模组的检查机的设计。

附图说明

下面结合附图对本发明的具体实施方式作进一步详细的说明。

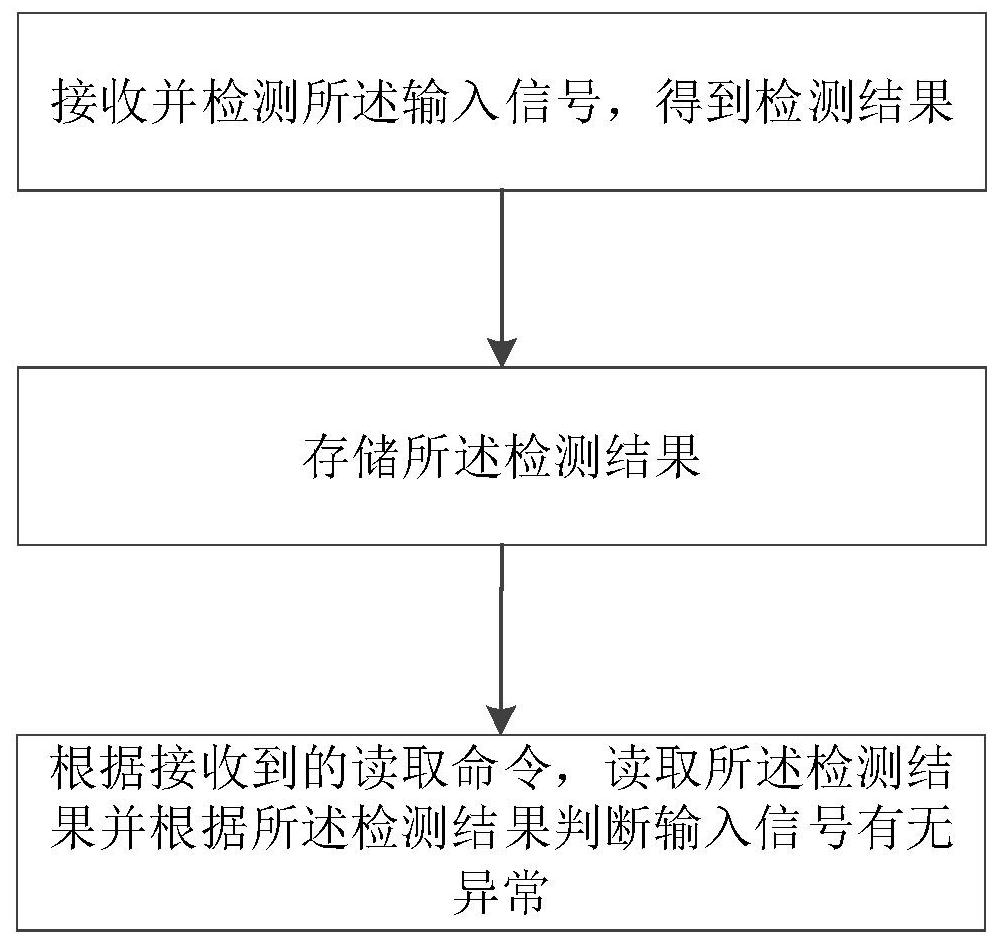

图1示出本发明实施例的一种DP内核输入信号检测方法的流程图;

图2a示出本发明实施例的输入信号为像素时钟信号和输入信号为DP内核链路层驱动时钟信号时的检测流程图;

图2b示出本发明实施例的输入信号为像素时钟信号和输入信号为DP内核链路层驱动时钟信号时的波形示意图;

图3示出根据本发明实施例的一种DP内核输入信号的自检电路示意图;

图4a和4b示出根据本发明实施例的记步电路计数单元原理图和信号波形示意图;

图5a和5b示出根据本发明实施例的垂直参数行计数单元原理图和信号波形示意图;

图6示出根据本发明实施例的VTC时序信号检测结果合并示意图。

具体实施方式

为了更清楚地说明本发明,下面结合优选实施例和附图对本发明做进一步的说明。附图中相似的部件以相同的附图标记进行表示。本领域技术人员应当理解,下面所具体描述的内容是说明性的而非限制性的,不应以此限制本发明的保护范围。

由于FPGA芯片的特性,高速串口的参考输入时钟clk_ref不能直接被布局布线到数字网络,因此,通过测试DP内核中锁相环的输出时钟lnk_clk对参考输入时钟进行间接测量。如果锁相环的输出时钟lnk_clk的频率正常,则可以判断参考输入时钟clk_ref和DP内核的锁相环都工作正常,该输出时钟lnk_clk为DP内核链路层的驱动时钟信号。

如图1所示,一种输入信号的自检方法,用以判断FPGA中DP内核输入信号的准确性,包括:

S1、接收并检测所述输入信号,得到检测结果。

在一个具体示例中,所述输入信号包括输入时钟信号,故步骤S1具体为:接收输入时钟信号,计算获得所述输入时钟信号的真实频率。

具体地,所述输入时钟信号包括像素时钟信号和DP内核链路层的驱动时钟信号,像素时钟信号和驱动时钟信号的检测方法相同,检测流程和波形示意如图2a和2b所示。

所述计算获得所述输入时钟信号的真实频率,包括:

S11、提供基准方波信号,确定基准方波信号的计数周期和/或频率。

在一个具体示例中,所述基准方波信号的获取方式为:提供任意已知频率的基准时钟信号,对所述基准时钟信号进行计数分频得到所述基准方波信号,同时设定所述基准方波信号的计数周期和/或频率。

如图2a所示,基准时钟可以选用任意已知频率的时钟,本实施例优选采用FPGA中AXI总线的时钟clk_base作为基准时钟。将基准时钟信号clk_base通过计数分频成方波信号div_sig,其中,计数周期为num=(f0/x)*500,num取整,每num个基准时钟周期,所述方波信号div_sig翻转1次,其中f0为所述基准时钟clk_base的频率,单位为Mhz。x为方波信号div_sig的频率,单位为kHz,图2b的示例中,方波信号div_sig(即图2b中的x kHz)占空比为50%。

在一个具体示例中,计数周期num=(f0/x)*500的推导过程为:

方波信号div_sig的周期T可表示为:

方波信号div_sig的周期T还可表示为:

因此:

即

所以num=(f0/x)*500,num取整。

S12、将所述基准方波信号与所述输入时钟信号同步。

具体地,将所述方波信号div_sig(x kHz)同步到所述驱动时钟信号或者像素时钟信号的时钟域,本实施例以输入时钟信号clk_test的时钟域为例进行说明,得到同步方波信号xkHz_synced。

S13、在所述基准方波信号的计数周期内,计量所述输入时钟信号的脉冲数。

具体地,获取同步方波信号xkHz_synced的上升沿脉冲pos_xkhz;即在所述输入时钟信号clk_test的时钟域中,设置计数器,遇到方波信号的上升沿脉冲pos_xkhz时,计数器置1即cnt=1,否则对输入时钟信号clk_test进行持续计数,并在再次遇到方波信号的上升沿脉冲时,输出计数器的累积计数结果result=cnt,然后计数器置1即cnt=1。

S14、根据计量得到的脉冲数和基准方波的计数周期和/或频率计算得到所述输入时钟信号的真实频率。

设被测时钟的频率为f,单位为0.01Mhz。

计算原理如下:

根据时间相等原理,列方程:

则

f=0.1﹡cnt﹡x

为了进一步消去乘法计算,优选地,采用x=10,则进一步简化为

f=cnt。

因此,本实施例可以巧妙地消去除法和乘法计算,节省了硬件资源。由于本实施例只需根据计算出的真实频率判断输入时钟信号的工作状态,不需要很高的精度,所以对所选取的基准时钟信号的频率高低、相位关系没有什么要求,适用性比较强。

在另一个实施例中,所述输入信号还包括多个行场同步信号,对多个所述行场同步信号进行计算获得信号参数。

具体地,输入信号为视频定时控制器时序信号(包括第一行场同步信号hsync信号、第二行场同步信号vsync信号、第三行场同步信号de信号以及clk_pix像素时钟信号)时,对多个所述行场同步信号进行计算获得信号参数的具体步骤包括:

根据多个所述行场同步信号的波形关系,计算获取所述行场同步信号的水平参数信息和垂直参数信息,对所述水平参数信息和垂直参数信息进行字节合并得到信号参数。

具体地,步骤包括:

S16、根据输入的第一行场同步信号hsync、第三行场同步信号de以及像素时钟信号clk_pix三个信号的电路波形关系,通过计数电路计数,获取水平前肩hfp参数(hsync的上升沿与de的下降沿的时延)、水平同步脉宽hs参数、水平后肩hbp参数(de的上升沿与hsync的下降沿的时延)、行像素数量hp的时钟周期参数;

S17、根据输入的第一行场同步信号hsync、第二行场同步信号vsync、第三行场同步信号de三个信号的电路波形关系,通过计数电路计数,获取垂直前肩vfp参数、垂直同步脉宽vs参数、垂直后肩vbp参数、帧数据有效行数vp参数,其中这些参数的计数单位为行数,2个hsync信号之间的间距为1行;

S18、将获取的所有参数,通过bit合并为1个wire型结果,作为所述检测结果。即将多个数据拼接输出,例如8位vs参数为01010101,16位vbp为1010101010101010,合并为wire型结果为24位010101011010101010101010。

S2、存储所述检测结果。

在一个具体示例中,所述检测结果直接或者拆分存放于DP内核的寄存器列表中。

例如,所述wire型结果被拆分存储在所述内核寄存器列表的多个地址中。

其中,所述寄存器列表挂载在检测设备的控制器上。

S3、根据接收到的读取命令,读取所述检测结果并根据所述检测结果判断输入信号有无异常。

具体地,响应于人工输入读取命令,通过控制器的串口,读取所述检测结果。例如输入信号为像素时钟信号检测时,读到的值为0x24EA=9450,则被测时钟频率为94.50Mhz。

本发明实施例提供的一种FPGA中DP内核的输入信号的自检方法,第一时间先确保输入DP内核的重要信号正确无误,从而达到检测设备调试过程少走弯路、更快响应的目的,时钟频率计算电路采用了特殊的计算方式,巧妙地消去了除法、乘法计算,从而节省了硬件资源。由于只需计算出频率判断时钟的工作状态,不需很高的精度,所以,对所选取的基准时钟和被测时钟的频率高低、相位关系没有什么要求,适用性比较强,基本上适应DP、非DP的各种液晶模组的检查机的设计。

如图3所示,输入信号的自检电路,设置于FPGA的DP内核,包括:

检测单元,用于接收并检测DP内核的输入信号;

存储单元,连接至所述检测单元,以存储输入信号的检测结果。

在一个具体示例中,所述输入信号包括:输入时钟信号和多个行同步信号,所述检测单元包括:用于检测所述输入时钟单元频率的时钟检测单元和用于检测所述行同步信号的信号参数的时序检测模块,其中,所述时序检测模块包括:用于检测所述行场同步信号的水平参数信息的水平参数计数电路和用于检测所述行场同步信号的垂直参数信息的垂直参数行计数电路。

在一个具体示例中,所述存储单元采用DP内核的寄存器列表,所述寄存器列表连接至控制器,以便于供所述控制器读取检测结果。

可选地,自检电路还包括检测结果输出单元,响应于人工输入读取命令,通过控制器的串口,读取所述检测结果。

在本实施例中,通过检测单元自带的多种输入信号检测功能,并通过寄存器列表存储和读取检测结果,从而确定当前自检电路的工作状态,其效率快,适用性强。

在一个可选的实施例中,所述输入时钟信号包括:像素时钟信号和驱动时钟信号,所述时钟检测单元包括两组时钟检测模块,两组时钟检测模块各自检测所述像素时钟信号和驱动时钟信号的真实频率,并将检测结果传递至所述存储单元。

具体地,该时钟检测模块被配置为:

S11、提供基准方波信号,确定基准方波信号的计数周期和/或频率。

在一个具体示例中,所述基准方波信号的获取方式为:提供任意已知频率的基准时钟信号,对所述基准时钟信号进行计数分频得到所述基准方波信号,同时设定所述基准方波信号的计数周期和/或频率。

如图2a所示,将基准时钟信号clk_base通过计数分频成方波信号div_sig,其中计数周期为num=(f0/x)*500,num取整,每num个基准时钟周期,所述方波信号div_sig翻转1次,其中f0为所述基准时钟clk_base的频率,单位为Mhz,该基准时钟可以选用任意已知频率的时钟,图2b中选用了AXI总线的时钟clk_axi作为基准时钟。x为方波信号频率,单位为kHz,图2b的示例中,方波信号div_sig(即图2b中的x kHz)占空比为50%。

在一个具体示例中,计数周期num=(f0/x)*500的推导过程为:

方波信号的周期T可表示为:

方波信号的周期T还可表示为:

因此:

即

所以num=(f0/x)*500。

S12、将所述基准方波信号与所述输入时钟信号同步。

具体地,将所述方波信号div_sig(频率为x kHz)同步到所述像素时钟信号clk_test的时钟域,得到同步方波信号xkHz_synced。

S13、在所述基准方波信号的计数周期内,计量所述输入时钟信号的脉冲数。

具体地,获取同步方波信号xkHz_synced的上升沿脉冲pos_xkhz;

在所述时钟域,设置计数器,遇到上升沿脉冲pos,计数器置1,否则不停计数,输出计数器的累积计数结果result=cnt。

S14、根据计量得到的脉冲数和基准方波的计数周期和/或频率计算得到所述输入时钟信号的真实频率。

设被测时钟的频率为f,单位为0.01Mhz。

计算原理如下:

根据时间相等原理,列方程:

则

f=0.1﹡cnt﹡x

为了进一步消去乘法计算,优选地,采用x=10,则进一步简化为

f=cnt。

在本实施例中,检测单元自带有用于检测像素时钟信号的功能,通过像素时钟信号的频率判断当前像素时钟信号的工作状态,该过程消去了除法、乘法计算,极大地节省了硬件资源。

本实施例通过检测检测单元的检测像素时钟信号的功能、DP内核链路层驱动时钟信号以及检测视频定时控制器时序VTC信号,快速判断当前各输入信号的工作状态,达到DP模组调试过程少走弯路、更快响应的目的。

如图4a和图4b所示,在一个可选的实施例中,水平参数计数电路被配置为:

根据输入的第一行场同步信号hsync、第三行场同步信号de、clk_pix像素时钟信号三个信号的电路波形关系,通过计数电路计数,获取水平前肩hfp参数(hsync的上升沿与de的下降沿的时延)、水平同步脉宽hs参数、水平后肩hbp参数(de的上升沿与hsync的下降沿的时延)、行像素数量hp的时钟周期参数;

垂直参数行计数电路被配置为:

如图5a和5b所示,根据输入的第一行场同步信号hsync信号、第二行场同步信号vsync信号、第三行场同步信号de信号三个信号的电路波形关系,通过计数电路计数,获取垂直前肩vfp参数、垂直同步脉宽vs参数、垂直后肩vbp参数、帧数据有效行数vp参数,其中这些参数的计数单位为行数,2个hsync信号之间的间距为1行。

如图6所示,将获取的所有参数,通过bit合并为1个wire型结果,作为所述检测结果。即将多个数据拼接输出,例如8位vs参数为01010101,16位vbp为1010101010101010,合并为wire型结果为24位010101011010101010101010。

本发明实施例提供的一种FPGA中DP内核的输入信号的自检电路第一时间先确保输入DP内核的重要信号正确无误,从而达到DP模组调试过程少走弯路、更快响应的目的,时钟频率计算电路采用了特殊的计算方式,巧妙地消去了除法、乘法计算,从而节省了硬件资源。由于只需计算出频率判断时钟的工作状态,不需很高的精度,所以,对所选取的基准时钟和被测时钟的频率高低、相位关系没有什么要求,适用性比较强,基本上适应DP、非DP的各种液晶模组的检查机的设计。

显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动,这里无法对所有的实施方式予以穷举,凡是属于本发明的技术方案所引伸出的显而易见的变化或变动仍处于本发明的保护范围之列。

- 一种输入信号的自检方法和自检电路

- 光敏器件自检电路、自检方法、自检系统和空调器