一种多复用性高速接口设备及控制方法

文献发布时间:2023-06-19 11:29:13

技术领域

本发明涉及数据通信技术,特别是一种多复用性高速接口设备及控制方法。

背景技术

市场上PCIE,SATA,USB等高速信号在接出到某一外接接口时,由于接口接入不易切换的限制,外界接口只能用一种单一功能,无法做到自动切换,扩展性和兼容性比较差,如果提供多个接口给客户选择使用,又会占用不少主板空间,增加PCB成本。

发明内容

本发明的发明目的在于:针对现有技术存在的接口功能不易切换的问题,提供一种多复用性高速接口设备及控制方法。

为了实现上述目的,本发明采用的技术方案为:

一种多复用性高速接口设备,包括上位机通讯模块一、上位机通讯模块二、CPU;

上位机通讯模块一、上位机通讯模块二分别连接到CPU;上位机通讯模块一用于输入输出SATA信号或PCIE信号,上位机通讯模块二用于输入输出PCIE信号或USB信号;

其中,上位机通讯模块一的SEL端连接CPU的PEDET端,并接第一上拉电阻,所述PEDET为所述CPU的PEDET接口;

上位机通讯模块二的SEL端连接CPU的DET端,并接第二上拉电阻;其中DET端是接地端。

一种如权利要求1所述的多复用性高速接口设备的控制方法,其特征在于,包括以下步骤:

步骤S100.插入外接高速接口,根据CPU的PEDET端电平是否拉低,进行判断:

若PEDET端电平拉低,则识别输入的信号为SATA信号;

若PEDET端电平拉高,则识别输入的信号为PCIE信号;

步骤S200.判断输入信号为SATA信号还是PCIE信号:

当输入的信号为SATA信号时,利用PEDET端拉低上位机通讯模块一的SEL端电平,切换由SATA输出信号至高速接口,同时通过软件GPIO切换CPU的SATA配置模式,将信号PIN配置为SATA信号,传输数据;

当输入的信号为PCIE信号时,利用PEDET端拉高上位机通讯模块一的SEL端电平,切换由PCIE输出信号至高速接口,同时通过软件GPIO切换CPU的PCIE配置模式,将信号PIN配置为PCIE信号,传输数据;

步骤S300.侦测CPU的DET端接入情况,根据DET端电平是否拉低,进行判断:

若DET端电平拉低,则切换至输入为SATA或PCIE且输出为USB的模式;

若DET端电平保持为高,则切换至输入为SATA或PCIE且输出为PCIE的模式。

综上所述,由于采用了上述技术方案,本发明的有益效果是:

一种多复用性高速接口设备及控制方法,利用不同外接设备接入时,接口电平的差异,使用软件GPIO对于高速型号的收发切换,及硬件线路对高速信号收发切换,两种方式实现高速信号的切换,在低成本,简单易用的情况下实现接口复用功能,增加产品兼容性,提高客户体验满意度。

附图说明

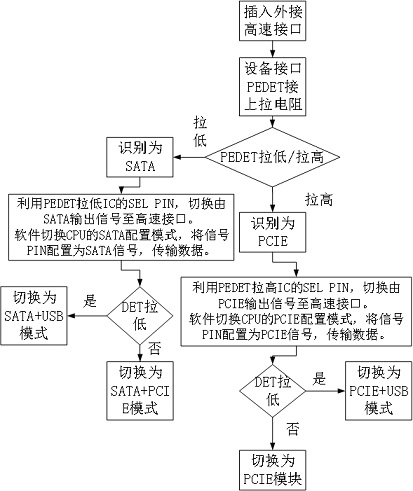

图1是本发明的流程示意图。

图2为多复用性高速接口设备的结构图。

具体实施方式

下面结合附图,对本发明作详细的说明。

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

如图2所示的一种多复用性高速接口设备,包括上位机通讯模块一、上位机通讯模块二、CPU;

上位机通讯模块一、上位机通讯模块二分别连接到CPU;上位机通讯模块一用于输入输出SATA信号或PCIE信号,上位机通讯模块二用于输入输出PCIE信号或USB信号;

其中,上位机通讯模块一的SEL端连接CPU的PEDET端,并接第一上拉电阻;

上位机通讯模块二的SEL端连接CPU的DET端,并接第二上拉电阻;其中DET端是接地端。

如图1所示,一种多复用性高速接口设备的控制方法,包括如下步骤:

S100插入外接高速接口,根据CPU的PEDET端电平是否拉低,进行判断:

若PEDET端电平拉低,则识别输入的信号为SATA信号;

S200当输入的信号为SATA信号时,利用PEDET端拉低上位机通讯模块一的SEL端电平,切换由SATA输出信号至高速接口,同时通过软件GPIO切换CPU的SATA配置模式,将信号PIN配置为SATA信号,传输数据;

使用硬件切换时,当设备插入,系统会通过插入外接设备引起的电平转换通知系统由设备接入,系统通过预设电压值判定接入设备的类型,确定设备类型后,转换IC进行传输线路的切换,使外设和系统进行正常传输。使用软件切换时,当设备插入,侦测信号会直接发送给系统,系统会根据预设值,通过软件切换接入系统的高速信号。

S300侦测CPU的DET端接入情况,根据DET端电平是否拉低,进行判断:

若DET端电平拉低,则切换至输入为SATA且输出为USB的模式;

若DET端电平保持为高,则切换至输入为SATA且输出为PCIE的模式。

优选的,所述步骤S100还包括:

插入外接高速接口,根据CPU的PEDET端电平是否拉低,进行判断:

若PEDET端电平拉高,则识别输入的信号为PCIE信号。

优选的,所述步骤S200还包括:

当输入的信号为PCIE信号时,利用PEDET端拉高上位机通讯模块一的SEL端电平,切换由PCIE输出信号至高速接口,同时通过软件GPIO切换CPU的PCIE配置模式,将信号PIN配置为PCIE信号,传输数据。

优选的,所述步骤S300还包括:

当输入的信号为PCIE信号时,侦测CPU的DET端接入情况,根据DET端电平是否拉低,进行判断:

若DET端电平拉低,则切换至输入为PCIE且输出为USB的模式;

若DET端电平保持为高,则切换至输入输出为PCIE的模式。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

- 一种多复用性高速接口设备及控制方法

- 一种基于不同波特率从设备的RS485总线复用控制方法