一种分时复用忆阻存储电路结构及工作方法

文献发布时间:2024-01-17 01:20:32

技术领域

本发明属于忆阻器存储技术领域,特别涉及一种分时复用忆阻存储电路结构及工作方法。

背景技术

目前,相较于普通存储器仅仅能够存储若干个状态,忆阻器能够凭借丰富状态调整,在消耗资源极少的情况下,存储大量的浮点信息。忆阻具有多种状态,要实现对应的存储和读取电路,不同于普通MOS和电容类存储器的结构,往往意味着更为复杂的线路布局和电路结构;并且目前的忆阻器存在有状态迁移引发的阻抗变化特点,导致实际的忆阻存储电路会有稳定性不高的特点,虽然部分先进的实验室能够制作出性能优异的器件,但如何能够以合理的方式来构建存储电路,仍在探索之中。因此需要研究一种可以通过稳定或者较为稳定的忆阻存储单元结构来构建新的存储器,同时兼顾资源节省和合理布线,使得忆阻存储电路的存储容量以及信号处理方面更具优势。

发明内容

发明目的:针对上述背景技术中存在的问题,本发明提供了一种分时复用忆阻存储电路结构及工作方法,不仅能够较为稳定地存储信息,而且在目前有限资源条件的情况下,同时兼顾合理布线和资源节省,并能够通过指定的方式输出稳定信号。

技术方案:本发明提供了一种分时复用忆阻存储电路结构,包括若干阵列组成的忆阻器存储单元;所述忆阻器存储单元包括忆阻器m1和m2、用于忆阻器编码的2T结构、二极管VD、和MOS管T2;所述忆阻器m1输入端连接2T结构,忆阻器m2输出端连接至忆阻器m1;所述二极管VD输入端连接至忆阻器m1和m2之间;所述MOS管T2一端连接至m2输出端,T2栅极连接至外部信号Va,另一端连接至外部信号Vd;所述2T结构上下两端分别连接于不同的使能端,输入端连接于通道选择器。

进一步地,所述忆阻存储电路阵列中,每一行忆阻器存储单元中二极管VD的输出共同连接至MOS管T1一端;MOS管T1栅极连接至外部信号Vc,另一端接地;同一行忆阻器存储单元中2T结构上下两端分别连接同一使能端wl和wl-;同一列忆阻器存储单元中2T结构输入端共同连接至通道选择器,每一行忆阻存储电路中MOS管T1栅极共用外部信号Vc。

进一步地,每一行二极管VD输出连接至数据缓冲模块;所述数据缓冲模块中包括若干独立的输出模块单元,使能端EN同时连接至各输出模块单元,控制输出模块单元的输出。

进一步地,所述通道选择器包括编码、读取和格式化3种工作状态;其中编码状态和读取状态下,对选中的通道提供高电平,未选中的通道为低电平;在格式化状态下,所有通道均为低电平。

一种采用上述分时复用忆阻存储电路结构工作方法,所述忆阻存储电路包括编码、读取、格式化三种状态;在忆阻存储电路编码阶段,通道选择器处于编码状态;此时各行使能端{wl}处于打开状态,Vc端输入信号,控制每行MOS管T1打开,外部信号Vd端为低电平,忆阻器m2不工作;通过通道选择器选择需要编码的忆阻器存储单元,并由对应使能端wl控制2T结构对忆阻器m1进行编码;编码完成后,使能端{wl}关闭,对应2T结构停止工作,此时外部信号Vd输入高电平,对各忆阻器m2进行定值编码;编码完成后,Vd端调整为低电平。

进一步地,在忆阻存储电路读取阶段,通道选择器处于读取状态;此时各行使能端{wl}处于打开状态,Vd端处于低电平状态,忆阻器m2不工作;Vc端处于低电平状态,MOS管T1停止工作;此时通道选择器选择的每一行忆阻器存储单元中,忆阻器m1存储信息通过二极管VD输出至数据缓冲器,最终实现数据读取。

进一步地,在忆阻存储电路格式化阶段,通道选择器处于格式化状态,全部通道均为低电平;此时MOS管T1停止工作,各行使能端{wl-}打开;Vd端输入高电平,经由忆阻器m2逆向输入至忆阻器m1,对忆阻器m1进行格式化;经过最长的编码周期T

有益效果:

本发明采用双忆阻器反向连接的结构构成基本存储单元,并基于线路分时复用技术将编码、读取和格式化的设计阵列式结构,既保证了资源的合理使用,又兼顾了忆阻器作为存储核心单元的稳定性,保证了存储阵列在存储数据时的优势,从而使忆阻器在存储器中的应用具有更好的适用性。

附图说明

图1是本发明提供的单个忆阻器存储单元结构示意图;

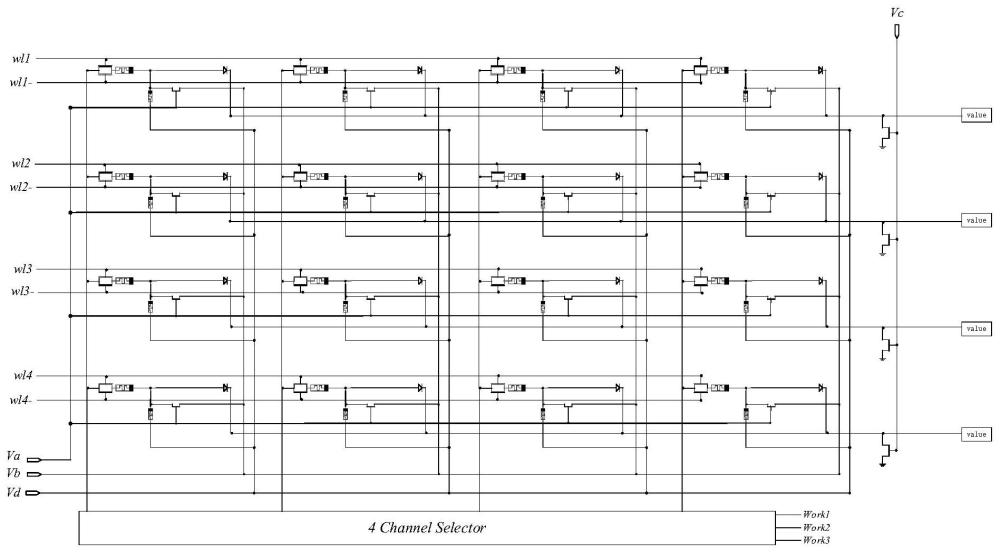

图2是本发明提供的存储单元阵列结构示意图;

图3a是忆阻器m1的编码流程示意图;

图3b是忆阻器m2的状态调整(编码)示意图;

图4是忆阻器存储信息读取方法示意图(work2);

图5a是忆阻器m1的格式化方法示意图(work3);

图5b是忆阻器m2的格式化方法示意图(work3);

图6a是本发明提供的输出模块单元结构示意图;

图6b是本发明提供的数据缓冲模块工作示意图。

具体实施方式

下面结合附图对本发明做更进一步的解释。

本发明公开了一种分时复用忆阻存储电路结构及工作方法,每个忆阻器存储单元包括相反相连的忆阻器m1和忆阻器m2;通过对通道选择器设置不同的工作电平,选择不同的状态,结合外存储单元阵列外部的MOS管{T1},在不同的通道选择Channel Selector工作电平下,实现存储、读取、格式化的对应功能;本发明采用分时复用技术设计了存储、读取、格式化电路,同时公开了相应的工作方法。

本发明提供的分时复用忆阻存储电路结构包括若干阵列组成的忆阻器存储单元,具体如图1所示,包括忆阻器m1和m2、用于忆阻器编码的2T结构、二极管VD、和MOS管T2。其中忆阻器m1输入端连接2T结构,忆阻器m2输出端连接至忆阻器m1;所述二极管VD输入端连接至忆阻器m1和m2之间;所述MOS管T2一端连接至m2输出端,T2栅极连接至外部信号Va,另一端连接至外部信号Vd;所述2T结构上下两端分别连接于不同的使能端,输入端连接于通道选择器。

单个忆阻器存储单元结构设计完毕后,接着基于分时复用原理,设计了一种对应存储、读取、格式化功能的忆阻器存储电路,编码和读取电路结构含有共用部分。具体如图2所示:

忆阻存储电路阵列中,每一行忆阻器存储单元中二极管VD的输出共同连接至MOS管T1一端;MOS管T1栅极连接至外部信号Vc,另一端接地;同一行忆阻器存储单元中2T结构上下两端分别连接同一使能端wl和wl-;同一列忆阻器存储单元中2T结构输入端共同连接至通道选择器,每一行忆阻存储电路中MOS管T1栅极共用外部信号Vc。所有忆阻器存储单元均共用外部信号端Va、Vb和Vd。

每一行二极管VD输出共同连接至数据缓冲模块;数据缓冲模块包括若干独立的输出模块单元,使能端EN同时连接至各输出模块单元,控制输出模块单元的输出。本实施例中采用的输出模块单元为电压跟随器,数据缓冲模块的目的在于,不同列的输出信号输出时间上存在先后差异,需要采用数据缓冲器对其到达时间进行统一,通过使能端EN控制同时输出读取结果,保证输出的时间一致。此外采用电压跟随器结构可以有效输出稳定的忆阻器存储值,并且可以处理电路中不稳定的信号毛刺。

下面介绍该电路结构分别对应的编码(存储)、读取、格式化的方法:

(1)编码状态:

如图3a-图3b所示,通道选择器Channel Selector工作在work1电平,所选通的通道为高电平,未选通的为低电平;在该阶段,信号{wl}打开,Vc信号输入MOS管{T1}组栅极,忆阻器{m2}连接的信号端Vd处于断开(高阻)状态;

选通信号通过2T中的Ta结构,依次经过忆阻器m1,二极管Vd,MOS管T1,构成回路,根据需要编码的时间(对应{wl}电平的打开时间)完成对选通信号线(所在列的)忆阻器{m1}的编码;

编码完成后,停止信号{wl},2T结构停止工作,此时通过Vd端口输入高电平,对存储阵列中所有忆阻器{m2}进行定向定值编码,编码完成之后,使得Vd端属于高阻状态。编码完成。

(2)读取阶段

如图4所示,此阶段中,通道选择器Channel Selector工作在work2电平,所选通的通道为较高电平,未选通的为低电平;信号{wl}打开,信号端Vd处于接地状态,信号Vc停止工作,MOS管T1停止工作;存储信号经由二极管Vd输出到数据缓冲器之中,最终实现读取功能。

(3)格式化状态;

如图5a-图5b所示,通道选择器Channel Selector工作在work3电平,全部通道为低电平,此时MOS管T1停止工作,各行使能端{wl-}打开;Vd端输入高电平,经由忆阻器m2逆向输入至忆阻器m1,对忆阻器m1进行格式化;经过最长的编码周期T

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 一种堆叠式双忆阻器存储结构、存储电路及工作方法

- 基于忆阻器的平衡三值多路复用器电路