一种片式三端子电容式滤波器及其制备方法

文献发布时间:2024-04-18 19:44:28

技术领域

本申请涉及电子陶瓷元件技术领域,具体涉及一种片式三端子电容式滤波器及其制备方法。

背景技术

为了满足电子整机不断向小型化、大容量化、高可靠性和低成本的方向发展,片式多层陶瓷滤波器(Multi-layer Ceramic Chip Filters,MLCF)应运而生,由于其优越的高频特性及较低的等效串联电感(ESL),被广泛应用于各个领域。

与常规的片式多层陶瓷电容器(Multi-layer Ceramic Chip Capacitor,英文缩写MLCC)相比,在宽度方向有一对接地电极,通过设置接地电极,使得电流可以从滤波器的两端流入,并从中间接地电极流出,从而可以缩短一半的电流路径,同时因电流可以从四个电极方向流出以及自感的存在,可以大大降低芯片的等效串联电感(ESL)。但是,因接地电极的存在,导致在制备的过程中,接地电极的内部有空洞,使得外部的杂质从空洞进入陶瓷本体中,从而导致的性能降低。

发明内容

鉴于此,本申请提供一种片式三端子电容式滤波器,以提高滤波器的性能。

本申请提供一种片式三端子电容式滤波器,包括:

陶瓷本体,包括层叠设置的第一内电极、第二内电极以及设置于所述第一内电极与所述第二内电极之间的介质层;

第一接地电极以及第二接地电极,间隔设置于所述陶瓷本体的相对两侧,所述第一接地电极以及所述第二接地电极均包括层叠设置的第一铜层、第二铜层、镍层以及锡层,所述第一铜层位于所述第二铜层靠近所述陶瓷本体的一侧,所述锡层设置于所述第二铜层背离所述陶瓷本体的一侧,所述第二铜层的致密性大于所述第一铜层的致密性;

第一端电极以及第二端电极,间隔设置于所述陶瓷本体的相对两端,所述第一接地电极以及所述第二接地电极设置于所述第一端电极以及所述第二端电极之间。

在一些实施例中,所述第一端电极以及所述第二端电极包括层叠设置的所述第一铜层、所述第二铜层、所述镍层以及所述锡层,所述第一铜层位于所述第二铜层靠近所述陶瓷本体的一侧,所述锡层设置于所述第二铜层背离所述陶瓷本体的一侧。

在一些实施例中,所述第一铜层为烧附铜层,所述第一铜层的厚度至少大于10μm,所述镍层为电镀镍层,所述锡层为电镀锡层。

在一些实施例中,所述第二铜层为烧附铜层,所述第二铜层的厚度为15-20μm,所述第一铜层的厚度为15-30μm。

在一些实施例中,所述第一铜层的厚度为15-30μm,所述第二铜层为电镀铜层,所述第二铜层的厚度小于10μm。

在一些实施例中,所述第一接地电极以及所述第一、第二接地电极还包括保护层,所述保护层设置于所述第一铜层与所述第二铜层之间。

在一些实施例中,所述保护层的材料包括聚乙烯、聚氯乙烯、聚苯乙烯、聚丙烯、硅氧烷、有机硅氧烷和聚硅氧烷中的至少一种。

在一些实施例中,所述第一接地电极以及所述第二接地电极还包括第三铜层,所述第三铜层为烧附铜层,所述第三铜层设置于所述第一铜层与所述第二铜层之间。

本申请还提供一种片式三端子电容式滤波器的制备方法,包括:

提供一陶瓷本体,包括层叠设置的第一内电极、第二内电极以及设置于所述第一内电极与所述第二内电极之间的介质层;

在所述陶瓷本体的外部设置第一接地电极、第二接地电极、第一端电极以及第二端电极,所述第一接地电极以及所述第二接地电极间隔设置于所述陶瓷本体的相对两侧,所述第一端电极以及所述第二端电极间隔设置于所述陶瓷本体的相对两端,所述第一接地电极以及所述第二接地电极设置于所述第一端电极以及所述第二端电极之间;

其中,所述第一接地电极以及所述第二接地电极均包括层叠设置的第一铜层、第二铜层、镍层以及锡层,所述第一铜层位于所述第二铜层靠近所述陶瓷本体的一侧,所述锡层设置于所述第二铜层背离所述陶瓷本体的一侧,所述第二铜层的致密性大于所述第一铜层的致密性。

在一些实施例中,所述在所述陶瓷本体的外部设置第一接地电极、第二接地电极、第一端电极以及第二端电极中,包括:

将电极材料设置于在所述陶瓷本体的相对两侧,并进行烧附处理,形成第一铜层;

采用电镀方式在所述第一铜层远离所述陶瓷本体的一侧形成第二铜层;

采用电镀方式在所述第二铜层远离所述陶瓷本体的一侧形成镍层;

采用电镀方式在所述镍层远离所述陶瓷本体的一侧形成锡层。

本申请提供一种片式三端子电容式滤波器及其制备方法,包括陶瓷本体、第一接地电极、第二接地电极、第一端电极以及第二端电极,包括层叠设置的第一内电极、第二内电极以及设置于第一内电极与第二内电极之间的介质层;第一接地电极以及第二接地电极,间隔设置于陶瓷本体的相对两侧,第一接地电极以及第二接地电极均包括层叠设置的第一铜层、第二铜层、镍层以及锡层,第一铜层位于第二铜层靠近陶瓷本体的一侧,锡层设置于第二铜层背离陶瓷本体的一侧,第二铜层的致密性大于第一铜层的致密性;第一端电极以及第二端电极间隔设置于陶瓷本体的相对两端,第一接地电极以及第二接地电极设置于第一端电极以及第二端电极之间,以提高滤波器的性能。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

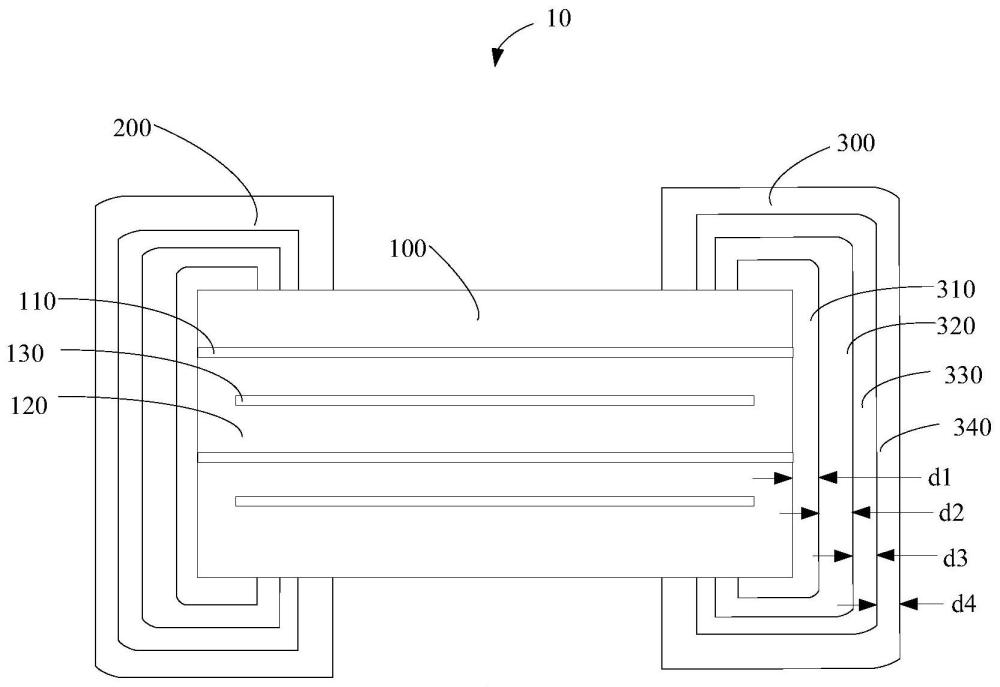

图1是本申请提供的片式三端子电容式滤波器的立体结构示意图;

图2是图1中的片式三端子电容式滤波器沿AB线的截面结构示意图;

图3是图1中的片式三端子电容式滤波器沿CD线的第一种截面结构示意图;

图4是图3中的片式三端子陶瓷电容器的DPA示意图;

图5是图1中的片式三端子电容式滤波器沿CD线的第二种截面结构示意图;

图6是图5中的片式三端子陶瓷电容器片式三端子电容式滤波器的DPA示意图;

图7是图1中的片式三端子电容式滤波器沿CD线的第三种截面结构示意图;

图8是本申请提供的片式三端子电容式滤波器的制备方法的流程示意图。

附图标记:

10、滤波器;100、陶瓷本体;110、第一内电极;120、介质层;130、第二内电极;200、第一接地电极;300、第二接地电极;310、第一铜层;320、第二铜层;330、镍层;340、锡层;350、保护层;360、第三铜层;400、第一端电极;500、第二端电极。

具体实施方式

下面结合附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本申请一部分实施例,而非全部实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。在不冲突的情况下,下述各个实施例及其技术特征可以相互组合。

本申请提供一种片式三端子电容式滤波器,包括陶瓷本体、第一接地电极、第二接地电极、第一端电极以及第二端电极,包括层叠设置的第一内电极、第二内电极以及设置于第一内电极与第二内电极之间的介质层;第一接地电极以及第二接地电极,间隔设置于陶瓷本体的相对两侧,第一接地电极以及第二接地电极均包括层叠设置的第一铜层、第二铜层、镍层以及锡层,第一铜层位于第二铜层靠近陶瓷本体的一侧,锡层设置于第二铜层背离陶瓷本体的一侧,第二铜层的致密性大于第一铜层的致密性;第一端电极以及第二端电极间隔设置于陶瓷本体的相对两端,第一接地电极以及第二接地电极设置于第一端电极以及第二端电极之间。

在本申请中,第一接地电极以及第二接地电极通过由第一铜层、第二铜层、镍层以及锡层依次层叠构成,且将第二铜层的致密性设置为大于第一铜层的致密性,以提高整体铜层的致密程度,从而降低第一接地电极以及第二接地电极内部的空洞数量,从而降低外部杂质或有害离子从空洞进入陶瓷本体内部的风险,从而提高滤波器的性能。

请参考图1-图4,图1是本申请提供的片式三端子电容式滤波器的立体结构示意图;图2是图1中的片式三端子电容式滤波器沿AB线的截面结构示意图;图3是图1中的片式三端子电容式滤波器沿CD线的第一种截面结构示意图;图4是图3中的片式三端子陶瓷电容器的DPA示意图。本申请提供一种片式三端子电容式滤波器10,包括陶瓷本体100、第一接地电极200、第二接地电极300、第一端电极400以及第二端电极500。具体描述如下。

陶瓷本体100包括层叠设置的第一内电极110、第二内电极120以及设置于第一内电极110与第二内电极130之间的介质层120,第一内电极110以及第二内电极130依次交替排列在介质层120内,第一内电极110和第二内电极130的材料包括镍、铜、银和钯中的至少一种,介质层120的材料包括钛酸钡、钛酸镁、钛酸钙、锆酸钙和钛酸锶中的至少一种。

第一接地电极200以及第二接地电极300间隔设置于陶瓷本体100的相对两侧,第一端电极400以及第二端电极500间隔设置于陶瓷本体100的相对两端,第一接地电极200以及第二接地电极300设置于第一端电极400以及第二端电极500之间,第一接地电极200、第二接地电极300、第一端电极400以及第二端电极500均包括层叠设置的第一铜层310、第二铜层320、镍层330以及锡层340,第一铜层310位于第二铜层320靠近陶瓷本体100的一侧,锡层340设置于第二铜层320背离陶瓷本体100的一侧,第二铜层320的致密性大于第一铜层310的致密性。进一步的,第二铜层320的致密性大于第一铜层310的致密性的20%。具体的,第二铜层320的致密性可以为第一铜层310的致密性的20%、22%、25%、30%、43%、56%或60%等,第一铜层310是采用低温烧制形成的烧附铜层,第一铜层310的厚度d1至少大于10μm,具体的,第一铜层310的厚度d1可以为10μm、13μm、16μm、19μm、23μm、26μm、30μm、或32μm等。优先的,第一铜层310的厚度d1为10-30μm,镍层330为电镀镍层330,锡层340为电镀锡层340,镍层330以及锡层340均是采用电镀的方式形成。

在一实施例中,第二铜层320为烧附铜层,第二铜层320的厚度d2为15-20μm,第一铜层310的厚度d1为15-30μm。具体的,第二铜层320的厚度d2可以为15μm、16μm、18μm、19μm或20μm等,第一铜层310的厚度d1可以为15μm、18μm、20μm、22μm、25μm、28μm或30μm等。

在一实施例中,镍层330的厚度d3为3-8μm,锡层340的厚度d4为4-10μm。具体的,镍层330的厚度d3可以为3μm、4μm、5μm、6μm、7μm或8μm等,锡层340的厚度d4可以为4μm、6μm、7μm、8μm或10μm等。

在另一实施例中,第一铜层310的厚度d1为15-30μm,第二铜层320为电镀铜层,第二铜层320的厚度d2小于10μm。具体的,第一铜层310的厚度d1可以为15μm、18μm、20μm、23μm、26μm、28μm或30μm,第二铜层320的厚度d2可以为3μm、4μm、6μm、7μm或10μm等。可选的,第二铜层320的厚度d2可以为3-10μm。

请参阅图4,图4是电容器10的物理破坏性分析(DPA)图,图4中第一铜层310中的小黑点为空洞,由图4中可知,第一接地电极200、第二接地电极300、第一端电极400以及第二端电极500通过由第一铜层310、第二铜层320、镍层330以及锡层340依次层叠构成,且将第二铜层320的致密性设置为大于第一铜层310的致密性,以使第二铜层320可以填充在第一铜层310中的空洞,从而降低电极中的空洞数量,从而可以提高整体铜层的致密程度,从而降低杂质或有害离子从空洞进入陶瓷本体100内部的风险。

在本申请中,第一接地电极200、第二接地电极300、第一端电极400以及第二端电极500通过由第一铜层310、第二铜层320、镍层330以及锡层340依次层叠构成,且将第二铜层320的致密性大于第一铜层310的致密性,以降低第一接地电极200、第二接地电极300、第一端电极400以及第二端电极500内部的空洞数量,从而提高整体铜层的致密程度,从而降低外部杂质或有害离子从空洞进入陶瓷本体100内部的风险,如降低镍镀液从而空洞进入陶瓷本体100的风险,从而保证了芯片的绝缘性能,进而提高滤波器10的可靠性。

在本申请中,通过将一接地电极、第二接地电极300、第一端电极400以及第二端电极500设置为由第一铜层310、第二铜层320、镍层330以及锡层340依次层叠构成,且将第二铜层320的致密性大于第一铜层310的致密性,以增大整体铜层的厚度,从而达到阻挡镍电镀液的渗入,从而提高滤波器10的可靠性。

在本申请中,将第二铜层320的厚度d2设置为15-20μm,第一铜层310的厚度d1设置为15-30μm,镍层330的厚度d3设置为3-8μm,锡层340的厚度d4设置为4-10μm,以使得整体铜层的厚度可以达到阻挡镍电镀液进入陶瓷本体100的内部的同时,降低滤波器10的整体厚度,以便于实现小型化设计。

请参阅图5和图6,图5是图1中的片式三端子电容式滤波器10沿CD线的第二种截面结构示意图;图6是图5中的片式三端子陶瓷电容器10的DPA示意图。需要说明的是第二种结构与第一种结构的不同之处在于:

第一接地电极200以及第二接地电极300还包括保护层350,保护层350设置于第一铜层310与第二铜层320之间,第一铜层310的厚度d1为15-30μm,第二铜层320为电镀铜层,第二铜层320的厚度d2为1-4μm。具体的,第二铜层320的厚度d2可以为2μm、2.5μm、3.0μm或4μm等。

在一实施例中,第一端电极400以及第二端电极500还包括设置于第一铜层310与第二铜层320之间的保护层350。保护层350的材料为高分子树脂材料。

在本申请中,通过在第一铜层310与第二铜层320之间的设置由高分子树脂形成的保护层350,以使得高分子树脂可以填充第一铜层310中的空洞,从而进一步提高滤波器10的可靠性。

在一实施例,保护层350的材料包括聚乙烯、聚氯乙烯、聚苯乙烯、聚丙烯、硅氧烷、有机硅氧烷和聚硅氧烷中的至少一种。

在一实施例中,保护层350的厚度d5小于0.5μm。具体的,保护层350的厚度d5可以为0.1μm、0.2μm、0.3μm、0.4μm或0.5μm等,以进一步提高滤波器10的可靠性。

请参阅图7,图7是图1中的片式三端子电容式滤波器10沿CD线的第三种截面结构示意图。需要说明的是,第三种结构与第一种结构的不同之处在于:

第一接地电极200以及第二接地电极300还包括第三铜层360,第三铜层360为烧附铜层,第三铜层360设置于第一铜层310与第二铜层320之间,第一铜层310的厚度d1为10-20μm,第二铜层320为电镀铜层,第二铜层320的厚度d2可以为3-10μm,第三铜层360的厚度d6为10-20μm。具体的,第一铜层310的厚度d1可以为10μm、12μm、15μm、18μm或20μm等,第三铜层360的厚度d6可以为10μm、13μm、15μm、16μm、18μm或20μm等。

在本申请中,通过将第一铜层310的厚度d1设置为10-20μm,第二铜层320为电镀铜层,第二铜层320的厚度d2设置为3-10μm,第三铜层360的厚度d6设置为10-20μm,以进一步提高滤波器10的可靠性。

请参阅图8,图8是本申请提供的片式三端子电容式滤波器10的制备方法的流程示意图。本申请还提供一种片式三端子电容式滤波器10的制备方法,用于制备本申请所提供的滤波器10,所述方法包括:

S11、提供一陶瓷本体,包括层叠设置的第一内电极、第二内电极以及设置于第一内电极与第二内电极之间的介质层。

S12、在陶瓷本体的外部设置有第一接地电极、第二接地电极、第一端电极以及第二端电极,第一接地电极以及第二接地电极间隔设置于陶瓷本体的相对两侧,第一端电极以及第二端电极间隔设置于陶瓷本体的相对两端,第一接地电极以及第二接地电极设置于第一端电极以及第二端电极之间;

其中,第一接地电极、第二接地电极、第一端电极以及第二端电极均包括层叠设置的第一铜层、第二铜层、镍层以及锡层,第一铜层位于第二铜层靠近陶瓷本体的一侧,锡层设置于第二铜层背离陶瓷本体的一侧,第二铜层的致密性大于第一铜层的致密性。

请继续参阅图2,将接地电极材料以及接地电极材料设置于在陶瓷本体100的相对两侧,将其置于650-850℃下,烧附10-15min,形成第一铜层310。具体的,烧附温度可以为650℃、680℃、720℃、750℃、780℃、810℃或850℃等,烧附时间可以为11min、12min、13min、13.6min、14.2min、14.9min或15min等。

然后,采用电镀方式在第一铜层310远离陶瓷本体100的一侧形成第二铜层320。

然后,采用电镀方式在第二铜层320远离陶瓷本体100的一侧形成镍层330。

然后,采用电镀方式在镍层330远离陶瓷本体100的一侧形成锡层340。

在本申请中,将第一铜层310的烧附时间以及烧附温度设置此范围,以降低端电极以及接地电极出现角裂的风险,同时保证了端电极以及接地电极的致密性,从而进一步提高了滤波器10的性能。

本申请提供一种片式三端子电容式滤波器10及其制备方法,在本申请中,通过将第一接地电极200、第二接地电极300、第一端电极400以及第二端电极500设置为由第一铜层310、第二铜层320、镍层330以及锡层340依次层叠构成,且将第二铜层320的致密性大于第一铜层310的致密性,以增大整体铜层的厚度和致密程度,从而达到阻挡外部杂质或有害离子的渗入,从而保改善滤波器10的可靠性。

以上所述仅为本申请的实施例,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换,例如各实施例之间技术特征的相互结合,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。