测试装置与异质整合结构

文献发布时间:2023-06-19 10:30:40

技术领域

本发明涉及一种测试装置与异质整合结构。

背景技术

在一般的半导体生产过程中,晶片允收测试(wafer acceptance test,WAT)是相当重要的线上(in-line)检测,作为判断制作工艺好坏及好或坏的管芯的依据,也是作为监控制作工艺飘动的直接证据。

另一方面,光子集成电路的硅光波导在制造上会遇到几个与传统半导体生产不同的问题,包括:1.布局(layout)较为困难,且设计规则检查(design rule checking)较复杂;2.制作工艺所得的结构粗糙度与蚀刻深度较为敏感;3.不易快速判断结果,因光输入与光输出的测量方法较电测复杂。

对于光子集成电路而言,晶片级测试(wafer level test)一般是适于采用表面耦合器(surface coupler)(例如光栅(grating))来进行,而边缘耦合器(edge coupler)则通常是适用于芯片级测试(chip level test)。

表面耦合器相较于边缘耦合器具有光损失较大、所能容纳的频宽较窄及受极化方向限制等缺点,但因为可以利用晶片级测试来进行而具有优势,所以常为硅光子制作工艺所采用。

然而,若光子集成电路因采用边缘耦合器而仅能采用芯片级测试与封装时,容易导致制作工艺复杂、制造成本与时间增加,并导致产量下降。

发明内容

本发明提供一种测试装置,其可达到简化的测量过程与良好的测量品质。

本发明提供一种异质整合结构,其利用简单的架构来达到与外界的光耦合。

本发明的一实施例提出一种测试装置,用以测试一光子集成电路。光子集成电路包括至少一波导边缘耦合器,而测试装置包括一光学耦合器。光学耦合器用以配置于光子集成电路上且光学对位于光子集成电路,且包括至少一聚焦透镜及一第一反射器。此至少一聚焦透镜对准于此至少一波导边缘耦合器。来自波导边缘耦合器的光依序被聚焦透镜聚焦、被第一反射器反射及传递至一光纤连接器,或者来自光纤连接器的光依序被第一反射器反射及被聚焦透镜聚焦至波导边缘耦合器。

本发明的一实施例提出一种异质整合结构,包括一光子集成电路及一光学耦合器。光子集成电路包括至少一波导边缘耦合器,而光学耦合器异质整合至光子集成电路上。光学耦合器包括至少一聚焦透镜及一第一反射器。此至少一聚焦透镜对准于此至少一波导边缘耦合器。来自波导边缘耦合器的光依序被聚焦透镜聚焦、被第一反射器反射及传递至一光纤连接器,或者来自光纤连接器的光依序被第一反射器反射及被聚焦透镜聚焦至波导边缘耦合器。

在本发明的实施例的测试装置与异质整合结构中,由于采用了可与光子集成电路光学对位或异质整合的光耦合器,因此可达到简化的测量过程与良好的测量品质,或利用简单的架构来达到与外界的良好光耦合。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

附图说明

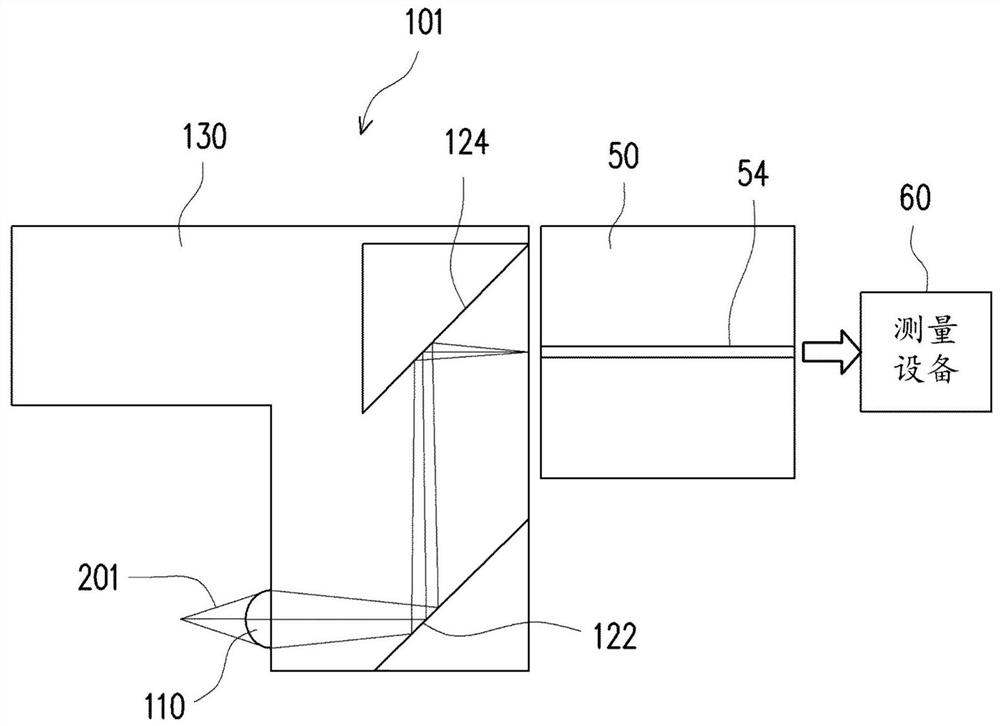

图1A是本发明的一实施例的测试装置的立体示意图;

图1B是图1A的测试装置沿着I-I线的剖面示意图;

图1C是从图1A的左方看过去的聚焦透镜的正视示意图;

图2A为利用多个图1A的测试装置分别测量的晶片上的多个光子集成电路的立体示意图;

图2B为图2A中的其中一个测试装置测量晶片上的其中一个光子集成电路的放大立体示意图;

图2C为图2B中的测试装置与光子集成电路沿着II-II线上的剖面示意图;

图3为图1A的测试装置与光纤连接器连接的立体示意图;

图4A是本发明的另一实施例的测试装置的立体示意图;

图4B是图4A的测试装置沿着III-III线的剖面示意图;

图4C为图4A的测试装置与光纤连接器连接的立体示意图;

图5A是本发明的又一实施例的测试装置的立体示意图;

图5B是图5A的测试装置沿着IV-IV线的剖面示意图。

符号说明

50:光纤连接器

51:贯孔

53:导引柱

54:光纤

60:测量设备

100、100a、100b:测试装置

101、101b:光学耦合器

110:聚焦透镜

122:第一反射器

124:第二反射器

130:光传输介质

132、134:凹洞

140:承靠件

200:光子集成电路

201:光

210:激光光源

220:调变器

230、250:硅波导

240:光检测器

260、270:波导边缘耦合器

300:晶片

310:沟槽

400:异质整合结构

具体实施方式

图1A是本发明的一实施例的测试装置的立体示意图,图1B是图1A的测试装置沿着I-I线的剖面示意图,而图1C是从图1A的左方看过去的聚焦透镜的正视示意图。图2A绘示利用多个图1A的测试装置分别测量的晶片上的多个光子集成电路的立体示意图,图2B为图2A中的其中一个测试装置测量晶片上的其中一个光子集成电路的放大立体示意图,而图2C为图2B中的测试装置与光子集成电路沿着II-II线上的剖面示意图。请参照图1A至图2C,本实施例的测试装置100用以测试一光子集成电路200。光子集成电路200上可具有激光光源210、硅波导230、250,调变器(modulator)220、波导边缘耦合器260、270及光检测器(photodetector)240。调变器220例如是马赫-任德干涉仪(Mach-Zehnder modulator)。

光子集成电路200包括至少一波导边缘耦合器270(在图2A至图2C中是以多个波导边缘耦合器270为例),而测试装置100包括一光学耦合器101。光学耦合器101用以配置于光子集成电路200上且光学对位于(optically aligned with)光子集成电路200,或者光学耦合器101用以异质整合(heterogeneously integrated)至光子集成电路200上。异质整合(heterogeneous integration,HI)是指将多个分开制造的元件组装及封装至单一芯片上,以提升功能与操作特性。

光学耦合器101包括至少一聚焦透镜110(在图1A及图2B中是以多个聚焦透镜110为例)及一第一反射器122。这些聚焦透镜110分别对准于这些波导边缘耦合器270,而来自波导边缘耦合器270的光201依序被聚焦透镜110聚焦、被第一反射器122反射及传递至一光纤连接器50(如图1B所绘示)。或者,这些聚焦透镜110也可分别对准于这些波导边缘耦合器260,而来自光纤连接器50的光依序被第一反射器122反射及被聚焦透镜110聚焦至波导边缘耦合器260。

在本实施例中,光学耦合器101还包括一第二反射器124。当这些聚焦透镜110分别对准于这些波导边缘耦合器270时,激光光源210所发出的光201依序通过调变器220、硅波导230及波导边缘耦合器270而后被聚焦透镜110聚焦。然后,来自聚焦透镜110的光201被第一反射器122反射至第二反射器124,而第二反射器124将被第一反射器122反射的光201反射至光纤连接器50,而光纤连接器50所固定的光纤54将第二反射器124所反射的光201传递至测量设备60。如此一来,通过测试装置100承靠于光子集成电路200上,测量设备60便能够测量光子集成电路200的光学特性,例如可判断光子集成电路200是良好的芯片或不好的芯片。在本实施例中,测量设备60例如为光功率计,然而,在其他实施例中,测量设备60也可以是其他适当的光学测量设备。

当这些聚焦透镜110分别对准于这些波导边缘耦合器260时,外部光源所发出的光可经由光纤连接器50所固定的光纤54传递至第二反射器124,第二反射器124将来自光纤连接器50的光反射至第一反射器122,第一反射器122将第二反射器124所反射的光反射至聚焦透镜110,然后聚焦透镜110将光聚焦于波导边缘耦合器260,接着光依序通过波导边缘耦合器260及硅波导250而传递至光检测器240。透过光检测器240将光转换而成的电信号,便能够判断光子集成电路200的光学特性,例如可判断光子集成电路200是良好的芯片或不好的芯片。在本实施例中,光检测器240例如是光电二极体(photodiode)或其他适当的光检测元件。

在本实施例中,光学耦合器101还包括一光传输介质130,包覆第一反射器122,且光传输介质130的至少一弯曲表面(在图1A中是以多个弯曲表面为例)形成上述至少一透镜110(在图1A中是以多个透镜110为例)。光传输介质130的材质包括聚合物,例如为环氧树脂(epoxy),而在光传输介质130中传递的光(例如光201)例如为红外光。

在本实施例中,测试装置100还包括至少一承靠件140(在图1A与图2C中是以两个承靠件140为例),连接至光传输介质130,其中测试装置100通过承靠件140承靠在光子集成电路200的表面,来固定波导边缘耦合器270或260与聚焦透镜110的相对位置,例如是使波导边缘耦合器270或260与聚焦透镜110在高度上互相对准。

在本实施例中,当这些聚焦透镜110分别对准于这些波导边缘耦合器270时,入射第一反射器122的光201的入射方向与从第二反射器124出射的光201的出射方向为同向。而当这些聚焦透镜110分别对准于这些波导边缘耦合器260时,来自光纤连接器50且入射第二反射器124的光的入射方向与来自第二反射器124且从第一反射器122出射的光的出射方向为同向。上述「同向」是指两方向的夹角落在±1.5度以内。在本实施例中,第一反射器122倾斜于从波导边缘耦合器270出射的光201的行进方向,或倾斜于入射波导边缘耦合器260的光的行进方向。在本实施例中,第一反射器122与第二反射器124为反射镀膜,例如为金属膜,且第一反射器122例如是平行于第二反射器124。

在本实施例的测试装置100中,由于采用了可光学对位于光子集成电路200的光耦合器101,因此可达到简化的测量过程与良好的测量品质,或利用简单的架构来达到与外界的光耦合。此外,与光子集成电路200异质整合的测试装置100也可以作为光子集成电路200的对外的光耦合器,而保留在光子集成电路200的成品上,且与光子集成电路200一起形成一个异质整合结构400,此异质整合结构400采用了简单的架构来达到与外界的良好光耦合。也就是说,当测试装置100在测试光子集成电路200时,光学耦合器101是用以配置于光子集成电路200上且光学对位于光子集成电路200,在测试完毕后,测试装置100可与光子集成电路200分离。而当测试装置100与光子集成电路200异质整合时,测试装置100与光子集成电路200之间的相对位置与上述测试时的相对位置相同,但测试装置100与光子集成电路200被封装在一起而不会分离,以形成异质整合结构400。

在本发明的一实施例的测试方法中,可利用测试装置100的承靠件140如上述承靠于光子集成电路200上,以使这些聚焦透镜110分别对准这些波导边缘耦合器270或260,以达到上述的光学测量。此外,本实施例的测试装置100与测试方法可达到晶片级测试。也就是说,在一晶片300上形成多个管芯(即光子集成电路200)后,可在相邻两管芯之间形成沟槽310(例如是蚀刻出沟槽310),以暴露出光子集成电路200的侧面,这样便能够在侧面暴露出波导边缘耦合器270与260。另一方面,一治具上可固定有排成阵列的多个测试装置100,然后这些测试装置100分别被承靠于这些管芯上,以分别测量这些管芯的光学特性,如图2A所绘示,进而判断哪些管芯是良好的管芯,而哪些又是不好的管芯。如此一来,在之后的过程中,便可以只对良好的管芯作封装,而舍弃不好的管芯不作封装。由于对于光子集成电路制作工艺而言,封装所占的成本比重高于晶片制作工艺所占的成本比重许多,因此本实施例采用晶片级测试舍弃不好的管芯不作封装便能够有效地降低整体制作成本。

此外,本实施例采用波导边缘耦合器270、260来作光耦合,因此不会有表面耦合器的诸多缺点。换言之,本实施例能利用波导边缘耦合器作到晶片级测试,而能够突破了现有测试方法的限制。

上述的实施例是以这些聚焦透镜110分别对准这些波导边缘耦合器270或260为例,但在另一实施例中,也可以扩增这些聚焦透镜110的数量,并使这些聚焦透镜110同时分别对准这些波导边缘耦合器270与260,而同时进行光输出与光进入的测试。

图3绘示了图1A的测试装置与光纤连接器连接的立体示意图。请参照图1A与图3,当测试装置100与光纤连接器50进行连接时,可利用多个导引柱(guiding pin)53来固定测试装置100与光纤连接器50的相对位置,导引柱53的一端可插入测试装置100上的凹洞132(例如是光传输介质130上的凹洞132),且导引柱53的另一端可插入光纤连接器50上的贯孔51。此外,光纤连接器50所固定的光纤54的一端可插入测试装置100上的凹洞134(例如是光传输介质130上的凹洞134),以对准光路径。

图4A是本发明的另一实施例的测试装置的立体示意图,图4B是图4A的测试装置沿着III-III线的剖面示意图,而图4C绘示了图4A的测试装置与光纤连接器连接的立体示意图。请参照图2B、图4A至图4C,本实施例的测试装置100a与图1A至图3的测试装置100类似,而两者的主要差异如下所述。在本实施例的测试装置100a中,当这些聚焦透镜110分别对准于这些波导边缘耦合器270时,入射第一反射器122的光201的入射方向与从第二反射器124出射的光201的出射方向为反向。而当这些聚焦透镜110分别对准于这些波导边缘耦合器260时,来自光纤连接器50且入射第二反射器124的光的入射方向与来自第二反射器124且从第一反射器122出射的光的出射方向为反向。上述「反向」是指两方向的夹角落在180±1.5度的范围内。

图5A是本发明的又一实施例的测试装置的立体示意图,而图5B是图5A的测试装置沿着IV-IV线的剖面示意图。请参照图5A与图5B,本实施例的测试装置100b与图1A至图3的测试装置100类似,而两者的主要差异如下所述。在本实施例的测试装置100b中,光学耦合器101b包括第一反射器122,但不包括如图1A的第二反射器124,而被第一反射器122反射的光201往上传递至位于光学耦合器101b上方的光纤连接器50,或者来自光纤连接器50的光往下传递至第一反射器122,并被第一反射器122反射至聚焦透镜110。

综上所述,在本发明的实施例的测试装置与异质整合结构中,由于采用了可与光子集成电路光学对位或异质整合的光耦合器,因此可达到简化的测量过程与良好的测量品质,或利用简单的架构来达到与外界的良好光耦合。

虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

- 测试装置与异质整合结构

- 异质整合组装结构及其制造方法