学习识别装置、学习识别方法以及学习识别程序

文献发布时间:2023-06-19 11:55:48

技术领域

本发明涉及学习识别装置、学习识别方法以及学习识别程序。特别涉及针对深度学习的定时攻击对策。

背景技术

将欺骗已学习的神经网络的样本称为Adversarial Examples(对抗样本)。Adversarial Examples可人工地生成。

以往的Adversarial Examples根据深度学习的内部参数或者输出的概率信息生成。

根据非专利文献1,在基于Adversarial Examples的攻击的对策中,有探测功能的嵌入或者异常数据的学习取入等,而成为攻击的线索的内部参数或者输出的概率信息的隐藏被认为是有效的对策之一。另一方面,在非专利文献1中,未考虑从深度学习的处理时间的信息泄漏。

在以往的定时攻击对策中着眼于基于密码装置的处理时间的秘密密钥的泄漏对策。

在专利文献1中,作为泄漏对策实施:在加密或者解密的执行中执行虚拟处理、使加密或者解密的执行开始时间延迟、使数据的变化量均匀化、或者变更处理顺序。

现有技术文献

专利文献

专利文献1:日本特开2014-192793号公报

非专利文献

非专利文献1:Xiaoyong Yuana等著、“Adversarial Examples:Attacks andDefenses for Deep Learning”arXiv:1712.07107v3[cs.LG]7 Jul 2018

发明内容

针对深度学习的攻击者有可能根据输入数据和处理时间的关系性来生成Adversarial Examples。攻击者着眼于输入数据和处理时间的关系,所以存在无法通过作为以往的对策的内部参数或者概率信息的隐藏防止攻击这样的课题。

另外,以往的定时攻击对策还有由于特别针对密码装置而无法原样地应用于深度学习这样的课题。

本发明的目的在于针对深度学习的定时攻击对策。

本发明的一个方案的学习识别装置具备:

学习识别部,对输入数据进行学习识别处理而输出输出数据;以及

时间控制部,使针对输入数据的学习识别处理的处理时间不依赖于输入数据。

在本发明中,时间控制部使针对输入数据的处理时间不依赖于输入数据,所以能够防御对学习识别装置的攻击。

附图说明

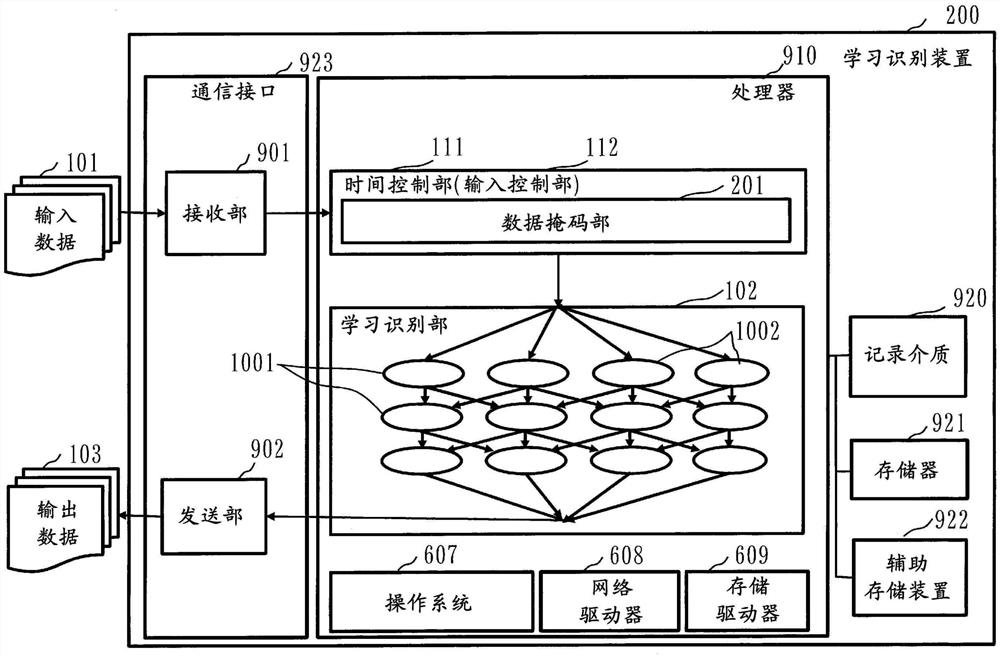

图1是实施方式1所涉及的学习识别装置的整体结构图。

图2是实施方式1所涉及的学习识别装置的动作图。

图3是实施方式2所涉及的学习识别装置的整体结构图。

图4是实施方式2所涉及的学习识别装置的动作图。

图5是实施方式3所涉及的学习识别装置的整体结构图。

图6是实施方式3所涉及的学习识别装置的动作图。

图7是实施方式4所涉及的学习识别装置的整体结构图。

图8是实施方式4所涉及的学习识别装置的动作图。

图9是实施方式5所涉及的学习识别装置的整体结构图。

图10是实施方式5所涉及的学习识别装置的动作图。

图11是实施方式5所涉及的学习识别装置的整体结构图。

图12是实施方式6所涉及的学习识别装置的整体结构图。

(附图标记说明)

101:输入数据;102:学习识别部;103:输出数据;109:中间数据;111:时间控制部;112:输入控制部;113:输出控制部;114:处理控制部;200:学习识别装置;201:数据掩码部;401:输入时刻扩散部;601:输出时刻扩散部;607:操作系统;608:网络驱动器;609:存储驱动器(storage driver);801:时间戳生成部;802:时间戳(time stamp);803:输出时刻调整部;901:接收部;902:发送部;909:电子电路;910:处理器;920:记录介质;921:存储器;922:辅助存储装置;923:通信接口;1001:神经网络层;1002:感知机处理;1003:输出时刻调整部。

具体实施方式

以下,使用附图说明本发明的实施方式。此外,在各图中,对同一或者相当的部分,附加同一符号。在实施方式的说明中,关于同一或者相当的部分,适宜地省略或者简化其说明。

在以下叙述的实施方式中说明的定时攻击对策中,使针对输入数据的处理时间不依赖于输入数据。换言之,在各实施方式中说明的定时攻击对策中,使从输入数据的输入时刻至输出数据的输出时刻的时间不依赖于输入数据而输出输出数据。

在各实施方式中,说明如下的针对深度学习的定时攻击对策。

1.在向深度学习的输入中采取对策

实施方式1:输入数据的掩码对策

实施方式2:输入定时的随机化对策

2.在从深度学习的输出中采取对策

实施方式3:输出定时的随机化对策

实施方式4:处理时间的恒定化对策

3.在深度学习的内部采取对策

实施方式5:内部处理时间的随机化或者恒定化对策

实施方式1.

说明本实施方式所涉及的装置的结构、本实施方式所涉及的装置的动作、本实施方式的效果。

***结构的说明***

图1是学习识别装置200的结构图。

学习识别装置200是一边学习输入数据一边对输入数据进行识别作业的装置。

学习识别装置200具有学习识别部102。

学习识别部102对输入数据101进行学习识别处理而输出输出数据103。

学习识别部102实施深度学习。

学习识别部102具有多个神经网络层1001。

神经网络层1001执行多个感知机处理1002。

在学习识别部102中,作为各神经网络层1001的运算,并行地执行感知机处理1002。

学习识别部102输出最终的神经网络层1001的感知机处理1002的运算结果。

学习识别装置200具有时间控制部111。

时间控制部111使针对输入数据101的学习识别部102的处理时间不依赖于输入数据101。

时间控制部111具有输入控制部112。

输入控制部112对输入数据101施加处理,变更学习识别部102的处理时间。

输入控制部112具有数据掩码部201。

数据掩码部201对输入数据101施加随机的噪声。

学习识别装置200通过在学习识别部102之前追加对输入数据101施加随机的噪声的数据掩码部201,使输入数据101和学习识别装置200的处理时间互不依赖。

在实施方式的说明中使用的用语的含义如下所述。

“学习识别处理”:学习识别装置200执行的处理。

“学习识别装置200的处理”:与“学习识别处理”相同。

“学习识别处理的处理时间”:从对学习识别装置200输入输入数据101的时刻至从学习识别装置200输出输出数据103的时刻的时间。

“学习识别装置200的处理时间”:与“学习识别处理的处理时间”相同。

“学习识别部102的处理”:学习识别部102执行的处理。

“学习识别部102的处理时间”:从对学习识别部102输入输入数据101的时刻至从学习识别部102输出输出数据103的时刻的时间。

如果“学习识别部102的处理时间”变化,则“学习识别装置200的处理时间”或者“学习识别处理的处理时间”也变化。

设为在以下的实施方式的说明中可忽略接收部901和发送部902的数据输入输出时间来进行说明。

***硬件结构的说明***

学习识别装置200具备处理器910。

学习识别装置200具备存储器921、辅助存储装置922、通信接口923、以及记录介质920这样的其他硬件。

处理器910经由信号线与其他硬件连接,控制这些其他硬件。

在学习识别装置200中,作为功能要素,具备时间控制部111和学习识别部102。

时间控制部111和学习识别部102的功能通过软件实现。

处理器910是执行学习识别程序的装置。

学习识别程序是实现时间控制部111和学习识别部102的功能的程序。

处理器910是进行运算处理的IC(Integrated Circuit,集成电路)。处理器910的具体例是CPU(Central Processing Unit,中央处理单元)、DSP(Digital SignalProcessor,数字信号处理器)、或者GPU(Graphics Processing Unit,图形处理单元)。

存储器921是暂时地存储数据的存储装置。

存储器921的具体例是SRAM(Static Random Access Memory,静态随机存取存储器)、或者DRAM(Dynamic Random Access Memory,动态随机存取存储器)。

记录介质920和辅助存储装置922是保管数据的存储装置。

记录介质920和辅助存储装置922的具体例是HDD(Hard Disk Drive,硬盘驱动器)。

另外,记录介质920和辅助存储装置922也可以是NAND闪存、软盘、光盘、紧凑盘、DVD(Digital Versatile Disk)这样的移动存储介质。

通信接口923具有接收数据的接收部901以及发送数据的发送部902。

通信接口923具有通信芯片或者NIC(Network Interface Card,网络接口卡)等。

将学习识别程序从存储器921读入到处理器910,通过处理器910执行。

在存储器921中,不仅是学习识别程序,而且还存储有操作系统607、网络驱动器608以及存储驱动器609。

处理器910一边执行操作系统607、网络驱动器608以及存储驱动器609,一边执行学习识别程序。

学习识别程序以及操作系统607、网络驱动器608以及存储驱动器609也可以存储于辅助存储装置922。

将存储于辅助存储装置922的学习识别程序以及操作系统607、网络驱动器608以及存储驱动器609载入到存储器921,通过处理器910执行。

此外,也可以将学习识别程序的一部分或者全部嵌入到操作系统607。

学习识别装置200也可以具备代替处理器910的多个处理器。这些多个处理器分担学习识别程序的执行。各个处理器与处理器910同样地是执行学习识别程序的装置。

由学习识别程序来利用、处理或者输出的数据、信息、信号值以及变量值被存储到存储器921、辅助存储装置922或者处理器910内的寄存器或者高速缓存存储器。

也可以将时间控制部111和学习识别部102的各部的“部”改称为“处理”、“过程”或者“工序”。另外,也可以将时间控制部111和学习识别部102的各处理的“处理”改称为“程序”、“程序产品”或者“记录有程序的计算机可读取的存储介质”。

学习识别程序使计算机执行将所述的各部的“部”改称为“处理”、“过程”或者“工序”的各处理、各过程或者各工序。另外,学习识别方法是通过学习识别装置200执行程序而进行的方法。

程序也可以储存到计算机可读取的记录介质而提供。另外,程序也可以作为程序产品提供。

另外,学习识别装置200也可以通过逻辑IC(Integrated Circuit,集成电路)、GA(Gate Array,门阵列)、ASIC(Application Specific Integrated Circuit,专用集成电路)、FPGA(Field-Programmable Gate Array,现场可编程门阵列)这样的处理电路实现。

另外,将处理器、存储器、处理器和存储器的组合、以及处理电路的上位概念称为处理线路(processing circuitry)。即,处理器、存储器、处理器和存储器的组合、以及处理电路分别是处理线路的具体例。

***动作的说明***

接下来说明动作。

图2是示出该实施方式的学习识别装置200的学习识别方法的动作的流程图300。以下的处理通过处理器910执行学习识别程序而实现。

首先,在步骤S301中,输入控制部112将输入到学习识别装置200的接收部901的输入数据101输入到数据掩码部201。

接下来,在步骤S302中,数据掩码部201对输入数据101施加随机的噪声。在此,关于数据掩码部201施加的噪声的强度,将不影响学习识别部102的处理的程度作为上限,设定与攻击者施加的噪声相同的程度或者其以上的程度。

接下来,在步骤S303中,数据掩码部201将施加随机噪声后的输入数据输入到学习识别部102。

学习识别部102在多个神经网络层1001中,执行感知机处理1002。

在感知机处理1002中,未施加随机噪声的输入数据的处理时间和施加随机噪声后的输入数据的处理时间不同。

神经网络层1001输出感知机处理1002的运算结果。

最终层的神经网络层1001成为学习识别结果。

学习识别部102从输入数据101得到学习识别结果,输出学习识别结果。

最后,在步骤S304中,学习识别部102将学习识别结果作为学习识别装置200的输出数据103,输出给发送部902。

发送部902将输出数据103输出到外部。

如以上所述,在本实施方式的学习识别方法中,时间控制部111使针对输入数据101的学习识别部102的处理时间不依赖于输入数据101。

然后,学习识别部102对输入数据101进行学习识别处理而输出输出数据。

另外,本实施方式的学习识别程序使执行学习识别处理的计算机针对输入数据101进行学习识别处理,从向学习识别部102的输入数据101的输入时刻至从学习识别部102的输出数据103的输出时刻的时间不依赖于输入数据,输出输出数据103。

***实施方式的特征***

本实施方式的学习识别装置200的特征在于,通过在学习识别部102之前追加处理输入数据101的单元,使输入数据101和学习识别部102的处理时间互不依赖。

本实施方式的学习识别装置200的特征在于,用对学习识别装置200的输入数据101施加随机的噪声的单元,实现处理输入数据101的单元。

本实施方式的学习识别装置200通过在学习识别部102之前追加对输入数据101施加随机的噪声的数据掩码部201,使输入数据101和学习识别部102的处理时间互不依赖。

本实施方式的学习识别装置200利用对输入数据101施加随机的噪声的数据掩码部201使学习识别部102的处理时间成为依赖于被施加随机的噪声的输入数据101的处理时间,由此作为定时攻击对策。

***实施方式的效果***

如以上所述,本实施方式的学习识别装置200由于使学习识别部102的处理时间依赖于被施加随机的噪声的输入数据101,因此能够防御着眼于输入数据101和处理时间的关系的定时攻击。

实施方式2.

以下,说明与实施方式1的不同点。

在本实施方式中,示出追加使向学习识别部102的输入数据101的输入时刻随机化的输入时刻扩散部401来作为定时攻击对策的实施方式。

图3是学习识别装置200的结构图。

学习识别装置200具有时间控制部111。

时间控制部111具有输入控制部112。

输入控制部112具有输入时刻扩散部401。

输入时刻扩散部401使向学习识别部102的输入数据101的输入时刻随机化。

学习识别装置200通过在学习识别部102之前追加使输入时刻随机化的输入时刻扩散部401,使输入数据101和学习识别装置200的处理时间互不依赖。

接下来说明动作。

图4是示出该实施方式的学习识别装置200的学习识别方法的动作的流程图500。以下的处理通过处理器910执行学习识别程序来实现。

首先,在步骤S501中,输入到学习识别装置200的输入数据101被输入到输入时刻扩散部401。

接下来,在步骤S502中,输入时刻扩散部401使输入数据101的向学习识别部102的输入时刻随机化。

具体而言,输入时刻扩散部401使向接收部901的输入数据101的接收时刻至向学习识别部102的输入数据101的输出时刻的时间随机化。

输入时刻的随机化通过虚拟处理或者等待处理等实现。

接下来,在步骤S503中,输入时刻扩散部401依照随机化的输入时刻,将输入数据101输入到学习识别部102。

最后,在步骤S504中,学习识别部102将学习识别结果作为输出数据103输出。

***实施方式的特征***

本实施方式的学习识别装置200的特征在于,通过在学习识别部之前追加处理输入数据的单元,使输入数据101和学习识别装置200的处理时间互不依赖。

本实施方式的学习识别装置200的特征在于,利用使向学习识别装置200的学习识别部的输入定时随机化的单元,实现处理输入数据的单元。

本实施方式的学习识别装置200利用使输入数据101的输入时刻随机化的输入时刻扩散部401,使学习识别装置200的处理时间成为依赖于随机化的输入时刻的处理时间,由此作为定时攻击对策。

***实施方式的效果***

如以上所述,本实施方式的学习识别装置200使学习识别装置200的处理时间依赖于随机化的输入时刻,所以能够防御着眼于输入数据101和处理时间的关系的定时攻击。

实施方式3.

以下,说明与实施方式1的不同点。

接下来,示出在追加了使学习识别部102的输出时刻随机化的输出时刻扩散部601的情况下成为定时攻击对策的实施方式。

图5是学习识别装置200的结构图。

学习识别装置200通过在学习识别部102之后追加使输出时刻随机化的输出时刻扩散部601,使输入数据101和学习识别装置200的处理时间互不依赖。

学习识别装置200具有时间控制部111。

时间控制部111具有输出控制部113。

输出控制部113对输出数据103施加处理来变更学习识别装置200的处理时间。

输入控制部112具有输出时刻扩散部601。

输出时刻扩散部601使输出数据103的输出时刻随机化。

该实施方式的学习识别装置200通过在学习识别部102之后追加使学习识别装置200的输出数据103的输出时刻随机化的输出时刻扩散部601,使输入数据101和学习识别装置200的处理时间互不依赖。

接下来说明动作。

图6是示出该实施方式的学习识别装置200的学习识别方法的动作的流程图700。以下的处理通过处理器910执行学习识别程序实现。

首先,在步骤S701中,输入到学习识别装置200的输入数据101被输入到学习识别部102。

接下来,在步骤S702中,从学习识别部102输出的学习识别结果被输入到输出时刻扩散部601。

接下来,在步骤S703中,输出时刻扩散部601使学习识别装置200的输出数据103的输出时刻随机化。

具体而言,输出时刻扩散部601使从学习识别部102的输出数据103的输入时刻至向发送部902的输出时刻的时间随机化。

输出时刻的随机化通过虚拟处理或者等待处理等实现。

最后,在步骤S704中,输出时刻扩散部601依照随机化的输出时刻,将从学习识别部102输出的学习识别结果作为输出数据103,输出给发送部902。

***实施方式的特征***

本实施方式的学习识别装置200的特征在于,通过在学习识别部102之后追加处理输出数据103的单元,使输入数据101和学习识别装置200的处理时间互不依赖。

本实施方式的学习识别装置200的特征在于,利用使学习识别装置200的输出定时随机化的单元,实现处理输出数据103的单元。

本实施方式的学习识别装置200通过输出时刻扩散部601使输出数据103的输出时刻随机化而使学习识别装置200的处理时间成为依赖于随机化的输出时刻的处理时间,作为定时攻击对策。

***实施方式的效果***

如以上所述,本实施方式的学习识别装置200使学习识别装置200的处理时间与输入数据101无关而依赖于随机化的输出数据103的输出时刻,所以能够防御着眼于输入数据101和处理时间的关系的定时攻击。

实施方式4.

以下,说明与实施方式1的不同点。

在本实施方式中,示出使学习识别部102的处理时间恒定来作为定时攻击对策的实施方式。

图7是学习识别装置200的结构图。

学习识别装置200具有时间控制部111。

时间控制部111具有输出控制部113。

输出控制部113具有时间戳生成部801和输出时刻调整部803。

时间戳生成部801将向时间戳生成部801的输入数据101的输入时刻记录为时间戳802。

输出时刻调整部803使用时间戳802,使从输入数据101的输入时刻至输出数据103的输出时刻的时间成为恒定。

输出时刻调整部803对时间戳802表示的输入数据101的输入时刻加上一定的时间,作为输出数据103的输出时刻。

学习识别装置200在学习识别部102之前追加记录向时间戳生成部801的输入数据101的输入时刻的时间戳生成部801,在学习识别部102之后追加使学习识别部102的处理时间成为恒定的输出时刻调整部803,由此使输入数据101和学习识别装置200的处理时间互不依赖。

接下来说明动作。

图8是示出该实施方式的学习识别装置200的学习识别方法的动作的流程图900。以下的处理通过处理器910执行学习识别程序来实现。

首先,在步骤S901中,输入到学习识别装置200的输入数据101被输入到时间戳生成部801。

接下来,在步骤S902中,时间戳生成部801生成与输入数据101的输入时刻对应的时间戳802。

时间戳802包括向时间戳生成部801的输入数据101的输入时刻。

时间戳802被存储到存储器921。

接下来,在步骤S903中,时间戳生成部801将把时间戳802记录到存储器921的输入数据101,输入给学习识别部102。

接下来,在步骤S904中,学习识别部102将学习识别结果输入给输出时刻调整部803。

接下来,在步骤S905中,输出时刻调整部803参照由时间戳生成部801生成的时间戳802,使处理时间成为恒定。

具体而言,时间戳生成部801将对时间戳802表示的输入时刻加上一定的时间而得到的时刻,作为学习识别结果的输出时刻。

处理时间的恒定化通过虚拟处理或者等待处理等实现。

最后,在步骤S906中,输出时刻调整部803依照处理时间被恒定化的输出时刻,将从学习识别部102输出的学习识别结果作为输出数据103,输出给发送部902。

***实施方式的特征***

本实施方式的学习识别装置200的特征在于,通过在学习识别部102之后追加处理输出数据103的单元,使输入数据101和学习识别装置200的处理时间互不依赖。

本实施方式的学习识别装置200的特征在于,利用在学习识别装置200的学习识别部102之前生成时间戳且参照时间戳802以使学习识别部102的处理时间成为恒定的方式设定学习识别装置200的输出定时的单元,实现处理输出数据103的单元。

本实施方式的学习识别装置200通过记录输入数据101的输入时刻的时间戳生成部801、和使学习识别部102的处理时间成为恒定的输出时刻调整部803,与输入数据101无关地调整输出数据103的输出时刻。

***实施方式的效果***

如以上所述,本实施方式的学习识别装置200以使学习识别装置200的处理时间成为恒定的方式,调整输出数据103的输出时刻,所以能够防御着眼于输入数据101和处理时间的关系的定时攻击。

实施方式5.

以下,说明与实施方式1的不同点。

在本实施方式中,示出对学习识别部102内的各神经网络层1001的感知机处理1002实施定时攻击对策的实施方式。

图9是学习识别装置200的结构图。

学习识别部102具有由神经网络层1001构成的多个层的处理。

学习识别装置200追加使学习识别部102内的各神经网络层1001的感知机处理的处理结果的输出时刻随机化或者成为恒定的输出时刻调整部1003,由此使输入数据101和学习识别部102的处理时间互不依赖。

学习识别装置200具有时间控制部111。

时间控制部111具有处理控制部114。

处理控制部114控制学习识别部102的处理时刻来变更学习识别部102的处理时间。

处理控制部114具有多个输出时刻调整部1003。

输出时刻调整部1003在神经网络层1001的各层配置于后面。

神经网络层1001和输出时刻调整部1003相对应,神经网络层1001的数量和输出时刻调整部1003的数量相同。但是,输出时刻调整部1003有1个以上即可。

输出时刻调整部1003使学习识别部102的各层的输出时刻随机化,或者使学习识别部102的各层的学习时刻成为恒定。

学习识别装置200通过对学习识别部102内的神经网络层1001的各层的感知机处理1002追加使输出时刻随机化或者成为恒定的输出时刻调整部1003,使输入数据101和学习识别部102的处理时间互不依赖。

接下来说明动作。

图10是示出该实施方式的学习识别装置200的学习识别方法的动作的流程图1100。以下的处理通过处理器910执行学习识别程序来实现。

首先,在步骤S1101中,输入到学习识别装置200的输入数据101被输入到学习识别部102。

接下来,处理器910将从步骤S1102至步骤S1105的处理,直至神经网络层1001的全部层的运算结束为止在各层中循环处理。

在步骤S1103中,神经网络层1001执行感知机处理1002。

接下来,在步骤S1104中,神经网络层1001将感知机处理1002的运算结果的输出,输入给输出时刻调整部1003。

接下来,在步骤S1105中,输出时刻调整部1003接受神经网络层1001的运算结果作为中间数据109,使中间数据109的输出时刻成为恒定或者随机。

具体而言,输出时刻调整部1003接受多个感知机处理1002的多个处理结果作为多个中间数据109,使多个中间数据109的输出时刻成为随机或者恒定而输出。

多个中间数据109的输出时刻的恒定化或者随机化通过虚拟处理或者等待处理等实现。

输出时刻调整部1003通过接收多个中间数据109并同时输出多个中间数据109,使中间数据109的输出时刻成为恒定。

或者,输出时刻调整部1003通过接收多个中间数据109并在相互随机的时刻输出多个中间数据109,使多个中间数据109的输出时刻随机化。

多个中间数据109的输出时刻的恒定化或者随机化也可以作为感知机处理1002内的一部分来实现。

最后,在步骤S1106中,在神经网络层1001的全部层的运算结束后,学习识别部102将学习识别结果作为输出数据103,输出给发送部902。

***实施方式的特征***

本实施方式的学习识别装置200的特征在于,通过在学习识别装置200的学习识别部内的各层的感知机处理1002之间追加处理中间数据109的单元,变更学习识别部102的处理时间,使输入数据和学习识别装置200的处理时间互不依赖。

本实施方式的学习识别装置200的特征在于,利用使学习识别装置200的学习识别部内的各层的多个中间数据109的输出定时随机化或者成为恒定的单元,实现处理中间数据109的单元。

***实施方式的效果***

如以上所述,本实施方式的学习识别装置200使多个中间数据109的输出时刻成为恒定或者随机而变更学习识别部102的处理时间,所以能够防御着眼于输入数据101和处理时间的关系的定时攻击。

***变形例***

图11是示出本实施方式所涉及的学习识别装置200的其他结构的图。

在图11中,变更了图9所示的学习识别装置200的输出时刻调整部1003。

图11所示的输出时刻调整部1003并非从神经网络层1001的所有感知机处理1002作为中间数据109接受,而是从神经网络层1001的所有感知机处理1002中的一部分的感知机处理1002作为中间数据109接受。

在输出时刻调整部1003未接受中间数据109的情况下,感知机处理1002的中间数据109被直接输入到接下来的神经网络层1001。

实施方式6.

在该实施方式中,说明与实施方式1的不同点。

图12是示出本实施方式所涉及的学习识别装置200的结构的图。

在图12中,将图1所示的学习识别装置200的处理器910变更为电子电路909。

学习识别装置200具备电子电路909、存储器921、辅助存储装置922、通信接口923、以及记录介质920。

电子电路909是实现时间控制部111和学习识别部102的功能的专用的电子电路。

电子电路909具体而言是单一电路、复合电路、程序化的处理器、并行程序化的处理器、逻辑IC、GA、ASIC、或者FPGA。GA是Gate Array的简称。ASIC是Application SpecificIntegrated Circuit的简称。FPGA是Field-Programmable Gate Array的简称。

时间控制部111和学习识别部102的功能既可以用1个电子电路实现,也可以分散到多个电子电路来实现。

在本实施方式中,时间控制部111和学习识别部102的功能也可以用软件实现。

或者,时间控制部111和学习识别部102的功能也可以用硬件实现。

或者,也可以时间控制部111和学习识别部102的一部分的功能用电子电路实现,剩余的功能用软件实现。

处理器和电子电路各自还被称为处理线路。即,在学习识别装置200中,时间控制部111和学习识别部102的功能通过处理线路实现。

虽然未图示,也可以将实施方式1以外的学习识别装置200的处理器910变更为电子电路909。

***其他实施方式***

在上述实施方式中,说明了一边学习一边进行识别作业的学习识别装置200,但也可以不是学习识别装置200而是进行学习的学习装置,也可以是进行识别作业的识别装置。

以上,说明了多个实施方式,但也可以组合这些实施方式中的2个以上的实施方式而实施。或者也可以部分性地实施这些实施方式中的1个实施方式或者2个以上的实施方式的组合。此外,本发明不限定于这些实施方式,能够根据需要进行各种变更。

- 音频模型学习方法、语音识别方法、音频模型学习装置、语音识别装置、音频模型学习程序及语音识别程序

- 学习装置、学习方法、识别装置、识别方法和程序