测试芯片延时的拟合方法和装置

文献发布时间:2023-06-19 09:41:38

技术领域

本发明涉及芯片检测技术领域,尤其涉及一种测试芯片延时拟合方法和装置。

背景技术

在使用测试芯片对待测芯片进行测试的过程中,电信号传输存在物理延时。物理延时的产生是由多种原因造成的,例如电场的传播时间、电路中设定电压建立的稳定时间、印刷电路板的线长等。在不同的测试条件下,这个延时并不是一个固定值,而是随测试对象和测试环境不同而不同的变化值。当对测试芯片的驱动信号和比较信号有较严格的时序要求时,就需要调整信号延时量,以便满足时序限制。在现有技术中,对信号延时的预估和调整都是依靠测试工程师的经验和实验设备的测量来实现。

随着芯片的性能逐渐增强,芯片的工作频率也逐渐升高。为了对芯片进行测试,测试信号的频率需要与芯片的工作频率一致。当测试信号的频率超过1GHz时,测试芯片的驱动信号和比较信号的调整精度需要达到纳秒级别。而通过经验和实验来调整延时的方法的调整效率低,精度差,不具备稳定性,这样就不能满足对高性能芯片的测试要求。

因此,需要提供一种高效、稳定且准确的测试芯片延时预估方法。

发明内容

有鉴于此,本发明提出了一种测试芯片延时的拟合方法和装置,其能够高效、稳定且准确地预估测试芯片的延时。

根据本发明的第一方面,提供了一种测试芯片延时的拟合方法,包括:

获取多组训练数据,每组训练数据包括所述测试芯片在测试环境中的输入电压测量值以及所述测试芯片的延时测量值,

采用多元线性回归的方式对所述多组训练数据进行拟合,得到拟合方程,其中所述测试芯片的延时为因变量,所述测试芯片的输入电压为自变量。

根据本发明一优选实施例,所述测试芯片具有输出的测试信号DUT,所述输入电压测量值包括VIH、VIL、VOH和VOL的测量值,其中,VIH控制DUT的最高电压,VIL控制DUT的最低电压,VOH和VOL均为所述测试芯片的比较器的参考电压。由于拟合方程的限制,设定VOH=VOL,测试范围在0-3之间。

根据本发明一优选实施例,所述延时为所述测试芯片的比较延时或驱动延时。

根据本发明一优选实施例,所述拟合方程为:

h(x)=θ

其中,θ

根据本发明一优选实施例,采用线性回归的方式对所述输入信号和所述延时进行拟合,得到拟合方程包括:

建立所述测试芯片的延时的损失函数;

通过最小化所述损失函数求解参数θ

根据本发明一优选实施例,所述拟合方程的矩阵和向量表示为:h

其中,θ表示参数矩阵,X表示自变量向量,h

所述损失函数为:

所述参数矩阵的解为:θ=(x

其中,Y为所述延时测量值的向量。

根据本发明一优选实施例,所述方法还包括利用所述拟合方程计算所述测试芯片的比较延时和/或驱动延时。

根据本发明的第二方面,提供了一种测试芯片延时的拟合装置,包括:

获取单元,用于获取多组训练数据,每组训练数据包括所述测试芯片在测试环境中的输入电压测量值以及所述测试芯片的延时测量值,

拟合单元,用于采用多元线性回归的方式对所述多组训练数据进行拟合,得到拟合方程,其中所述测试芯片的延时为因变量,所述测试芯片的输入电压为自变量。

根据本发明一优选实施例,所述测试芯片具有输出的测试信号DUT,所述输入电压测量值包括VIH、VIL、VOH和VOL的测量值,其中,VIH控制DUT的最高电压,VIL控制DUT的最低电压,VOH和VOL相等且均为所述测试芯片的比较器的参考电压。

根据本发明一优选实施例,所述延时为所述测试芯片的比较延时或驱动延时。

根据本发明一优选实施例,所述拟合方程为:

h(x)=θ

其中,θ

根据本发明一优选实施例,所述拟合单元被配置为:

建立所述测试芯片的延时的损失函数;

通过最小化所述损失函数求解参数θ

根据本发明一优选实施例,所述拟合方程的矩阵和向量表示为:h

其中,θ表示参数矩阵,X表示自变量向量,h

所述损失函数为:

所述参数矩阵的解为:θ=(x

其中,Y为所述延时测量值的向量。

根据本发明一优选实施例,所述方法还包括计算单元,用于利用所述拟合方程计算所述测试芯片的比较延时和/或驱动延时。

根据本发明的第三方面,提供了一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时执行以上描述的方法。

由以上技术方案可以看出,本发明的技术方案利用多元线性回归对测试芯片的输入电压和延时进行拟合,得到拟合方程。通过得到的拟合方程可以实现芯片延时的高效、稳定且准确的估计。

附图说明

参照附图,本发明的公开内容将变得更易理解。本领域技术人员容易理解的是,这些附图仅仅用于举例说明本发明的技术方案,而并非意在对本发明的保护范围构成限定。图中:

图1为根据本发明实施例的芯片测试场景的示意图;

图2为根据本发明实施例的测试芯片延时的拟合方法的流程图;

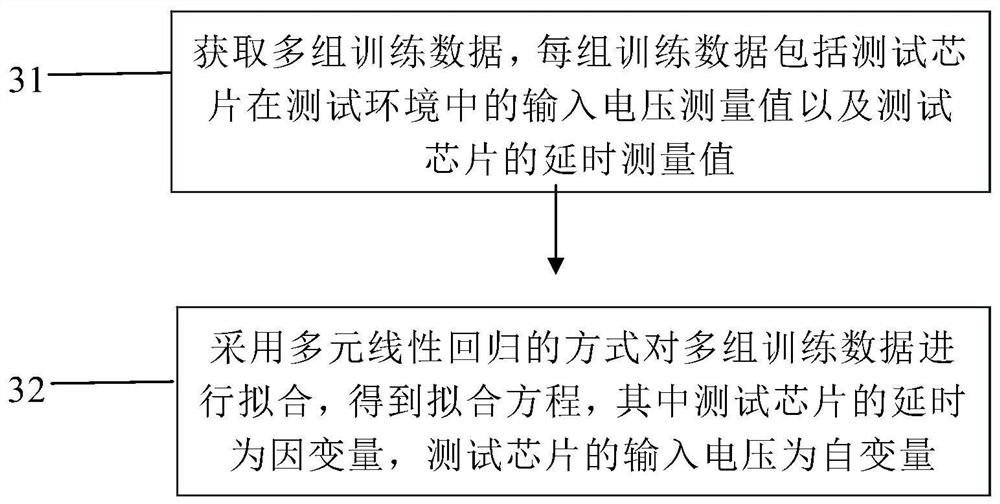

图3为根据本发明的实施例的测试芯片延时的拟合装置的结构示意图。

具体实施方式

为了使本发明的目的、技术方案和优点更加清楚,下面结合附图和具体实施例对本发明进行详细描述。

图1为根据本发明实施例的芯片测试场景的示意图。如图1所示,在对待测芯片进行测试时,需要使用专用的测试芯片向待测芯片发送测试信号DUT。为了产生需要的DUT信号,需要预先对FPGA芯片进行编程,以便驱动测试芯片产生需要的DUT信号。待测芯片接收DUT信号后产生输出信号并反馈给测试芯片的比较端。为了满足测试的时序要求,需要准确地预估芯片的驱动延时和比较延时。根据本发明的测试芯片延时的拟合方法可以实现对测试芯片的延时的准确预估。

图1中示出的测试芯片为美国ANALOG DEVICES公司的生产的型号为ADATE318的专用测试芯片。本发明的实施例中结合该芯片介绍本发明的方法。然而,本发明的方法和装置并不是仅适用于拟合ADATE318型测试芯片的延时,其他型号的测试芯片也可以使用本发明的方法和装置来进行芯片延时拟合。

图2为根据本发明实施例的测试芯片延时的拟合方法的流程图。如图1所示,该拟合方法包括:

步骤21:获取多组训练数据,每组训练数据包括测试芯片在测试环境中的输入电压测量值以及测试芯片的延时测量值。

步骤22:采用多元线性回归的方式对多组训练数据行拟合,得到拟合方程,其中测试芯片的延时为因变量,测试芯片的输入电压为自变量。

在步骤21中,多组训练数据是在例如图1所示的测量环境中实际测量得到的。每组测试数据可以包括测试芯片的输入电压测量值以及测试芯片的延时测量值。延时测量值可以是测试芯片的比较延时测量值或驱动延时测量值。具体地,可以首先测量测试芯片的各输入电压和此时的延时并记录,然后再改变输入电压值,测量新的一组输入电压值和对应的延时并记录。

结合图1的具体实施例,测试芯片具有输出的测试信号DUT,测试芯片的输入电压测量值包括VIH、VIL、VOH和VOL的测量值。其中,VIH控制DUT的最高电压,VIL控制DUT的最低电压,VOH和VOL相等且均为测试芯片的比较器的参考电压。在该实施例中,可以向测试芯片输入多组VIH、VIL、VOH和VOL,同时测量相应的比较延时和/或驱动延时,每组VIH、VIL、VOH和VOL的测量值和相应的比较延时和/或驱动延时为一组训练数据。为了达到良好的拟合效果,一般需要获取几百组训练数据。除了训练数据外,还可以获取多组测试数据,用于检验拟合方程的准确程度。测试数据与训练数据内容是相同的,因此采集的训练数据一部分(例如50%)可以用来生成拟合方程,另一部分可以留作测试拟合方程的准确程度的测试数据。

在步骤22中,采用多元线性回归的方式对步骤21中获得的多组训练数据行拟合,得到拟合方程。在拟合方程中,测试芯片的延时为因变量,测试芯片的输入电压为自变量。结合图1的具体实施例,测试芯片的延时(比较延时或驱动延时)与VIH,VIL,VOH(VOH与VOL相等)呈线性关系,将训练数据中VIH,VIL,VOH作为自变量,测试芯片的延时作为因变量,可以线性拟合测试芯片的延时。拟合方程为:

h(x)=θ

其中,θ

h

其中θ表示参数矩阵,X表示自变量向量,h

设训练数据中测量的比较延时或驱动延时的实际值为向量Y,通过建立一个损失函数来衡量测试芯片延时的估计值和实际值之间的误差的大小,将最小化损失函数作为一个约束条件来求出参数向量的最优解。损失函数如下:

该损失函数即为最小二乘法,通过方程3对参数θ求偏导数,并令偏导数为0,即可解出线性回归方程的系数矩阵θ=(x

为了验证以上得出的拟合方程的准确性,本发明的方法还可以包括验证以上拟合方程的步骤。根据本发明的一实施例,该步骤包括通过计算均方根误差来验证拟合方程的准确性。具体地,首先将测试数据集中的VIH、VIL和VOH以及以上计算出的系数矩阵代入拟合方程,求出测试集的测试芯片延时的预估值,然后计算预估值与实际值的均方根误差。通过均方根误差来评价拟合方程的准确性。均方根误差计算公式如下:

通过方程4,计算出测试数据集的均方根误差为0.21ns,且测试芯片的延时的实际值与预估值的绝对误差均在0.67ns以下,在误差允许的范围内。

以上是对本发明所提供方法进行的描述,下面结合实施例对本发明提供的装置进行详细描述。

图3为根据本发明的实施例的测试芯片延时的拟合装置的结构示意图。如图3所示,根据本实施例的芯片延时的拟合装置包括:获取单元41和拟合单元42。

获取单元41负责获取多组训练数据,每组训练数据包括测试芯片在测试环境中的输入电压测量值以及测试芯片的延时测量值。

多组训练数据是在例如图1所示的测量环境中实际测量得到的。每组测试数据可以包括测试芯片的输入电压测量值以及测试芯片的延时测量值。延时测量值可以是测试芯片的比较延时测量值或驱动延时测量值。具体地,可以首先测量测试芯片的各输入电压和此时的延时并记录,然后再改变输入电压值,测量新的一组输入电压值和对应的延时并记录。

结合图1的具体实施例,测试芯片具有输出的测试信号DUT,测试芯片的输入电压测量值包括VIH、VIL、VOH和VOL的测量值。其中,VIH控制DUT的最高电压,VIL控制DUT的最低电压,VOH和VOL相等且均为测试芯片的比较器的参考电压。在该实施例中,可以向测试芯片输入多组VIH、VIL、VOH和VOL,同时测量相应的比较延时和/或驱动延时,每组VIH、VIL、VOH和VOL的测量值和相应的比较延时和/或驱动延时为一组训练数据。为了达到良好的拟合效果,一般需要获取几百组训练数据。除了训练数据外,还可以获取多组测试数据,用于检验拟合方程的准确程度。测试数据与训练数据内容是相同的,因此采集的训练数据一部分(例如50%)可以用来生成拟合方程,另一部分可以留作测试拟合方程的准确程度的测试数据。

拟合单元42负责采用多元线性回归的方式对多组训练数据行拟合,得到拟合方程,其中测试芯片的延时为因变量,测试芯片的输入电压为自变量。

在拟合方程中,测试芯片的延时为因变量,测试芯片的输入电压为自变量。结合图1的具体实施例,测试芯片的延时(比较延时或驱动延时)与VIH,VIL,VOH(VOH与VOL相等)呈线性关系,将训练数据中VIH,VIL,VOH作为自变量,测试芯片的延时作为因变量,可以线性拟合测试芯片的延时。拟合方程为:

h(x)=θ

其中,θ

h

其中θ表示参数矩阵,X表示自变量向量,h

设训练数据中测量的比较延时或驱动延时的实际值为向量Y,通过建立一个损失函数来衡量测试芯片延时的估计值和实际值之间的误差的大小,将最小化损失函数作为一个约束条件来求出参数向量的最优解。损失函数如下:

该损失函数即为最小二乘法,通过方程3对参数θ求偏导数,并令偏导数为0,即可解出线性回归方程的系数矩阵θ=(x

为了验证以上得出的拟合方程的准确性,本发明还提供了验证以上拟合方程的验证单元。根据本发明的一实施例,验证单元通过计算均方根误差来验证拟合方程的准确性。具体地,验证单元首先将测试数据集中的VIH、VIL和VOH以及以上计算出的系数矩阵代入拟合方程,求出测试集的测试芯片延时的预估值,然后计算预估值与实际值的均方根误差。通过均方根误差来评价拟合方程的准确性。均方根误差计算公式如下:

通过方程8,计算出测试数据集的均方根误差为0.21ns,且测试芯片的延时的实际值与估计值的绝对误差均在0.67ns以下,在误差允许的范围内。

以上描述的装置实施例仅是示意性的。各单元的划分可以是基于逻辑功能的划分,在实际实现时可以采用其他的划分方式。例如多个单元可以结合或者可以集成到另一个单元或系统中。上述各个单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

上述各个单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读存储介质中。基于这样的理解,本发明的技术方案可以采用软件产品的形式体现,该计算机软件产品存储在一个存储介质中,包括若干指令用以使计算机设备的处理器执行本发明各个实施例的方法的全部或部分步骤。存储介质包括但不限于闪存盘、只读存储器(ROM)、随机存取存储器(RAM)、移动硬盘、磁盘或者光盘等可以存储程序代码的介质。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明保护的范围之内。

- 测试芯片延时的拟合方法和装置

- 数字电路延时测试方法、测试电路和集成电路芯片