一种录音信息传输的加密系统

文献发布时间:2023-06-19 11:02:01

技术领域

本发明涉及信息安全领域,具体涉及一种录音信息传输的加密系统。

背景技术

在国际商务谈判中,英语作为通用语言,经常作为各方谈判中的交流语言。但是在国际商务谈判中,为了维护各方的利益,需要对商务谈判中的交谈内容进行录音,然后将该录音传输至公司总部进行分析判断,以更好的进行下一步的商务活动。但是在录音传输的过程中,如何保证信息的安全性,是一个非常重要的问题。

数字录音是指将模拟音频信号经由模拟数字转换器记录到数字储存装置、需要音频回放时再将数字信号转换为模拟信号的过程。现有技术中的解决方案会采用将加密设备对录音数据进行加密存储,采用固定密匙的或者可变密匙的加密算法实现数据加密再进行数据传输。然而该种方式容易被破解,而且还需要进行复杂的加解密后才能进行本地上传,无法实现在线加解密实时传输。

发明内容

为背景技术中的问题,本发明提供一种录音信息传输的加密系统,其中一个技术方案为:

一种录音信息传输的加密系统,包括录音模块、处理器模块、存储器、可配置加解密芯片;

所述录音模块、存储器以及可配置加解密芯片均连接处理器模块;

所述处理器模块获取录音模块的录音数据,并选取随机位置处的特定长度的录音数据,并根据该特定长度的录音数据分析出梅尔倒谱系数,将所述梅尔倒谱系数结合个人特征参数形成配置参数;并将该配置参数以及加解密算法生成能够配置到可配置加解密芯片的原始二进制文件;

所述可配置加解密芯片可被处理器控制重新配置,并实现对存储器中的录音数据进行加解密运算。

进一步的,所述处理器和可配置加解密芯片之间还连接有第二存储器,用于存储原始二进制文件。

进一步的,所述可配置加解密芯片为FPGA芯片,所述FPGA芯片配置成被动配置模式,所述处理器模块控制FPGA芯片读取第二存储器中的原始二进制文件,并实现FPGA芯片在线重新配置。

进一步的,所述存储器也与FPGA芯片连接,用于存储加密后的录音数据。

进一步的,所述存储器为双口ROM,用于暂存录音模块的录音数据以及FPGA加密后的数据,所述FPGA将加密后的录音数据覆盖录音模块获取的原始录音数据。

进一步的,所述第二存储器为FLASH存储器,所述FLASH存储器仅用于存储配置FPGA的配置文件。

进一步的,所述处理器模块以STM32系列处理器为核心。

进一步的,所述录音模块中包括控制器以及与控制器连接的双口SRAM,控制器在获取数字音频数据后存储在双口SRAM中,处理器模块连接双口SRAM并获取存储在双口SRAM中的数字音频数据;所述控制器同时连接双口ROM并将数字音频数据同时存储在双口ROM上以供FPGA加密数据并覆盖。

本发明还公开了一种录音加解密方法,步骤如下:

S1、选取随机位置处的特定长度的录音数据;

S2、分析所述录音数据的特征参数;

S3、根据所述特征参数以及个人秘钥生成加解密算法配置参数;

S4、将所述配置参数以及加解密算法结合后生成原始二进制文件配置进可配置加解密芯片中;

S5、所述可配置加解密芯片对录音数据完成加解密操作。

优选的,所述S1中的选取方法为:读取录音时间长度,随机选取录音时间,根据录音强度断续时间确定特定长度的录音数据。

优选的,所述S2中的分析方法具体为:计算步骤S1中的录音数据的梅尔倒谱系数作为特征参数。

优选的,所述S3中的配置参数的生成步骤如下:将事先读取的录音设备持有人的个人特征参数如指纹数据或者设置的密码作为个人秘钥;读取步骤S2中的梅尔倒谱系数;将所述个人秘钥和梅尔倒谱系数组合形成配置序列,所述配置序列顺序或者倒序作为加解密算法的配置参数。

优选的,所述S3中的加解密算法可为AES加密解密算法(AES encryption anddecryption),所述配置参数为作为AES加密解密算法的密钥,所述密钥长度为192bit或者256bit。

优选的,所述S4中的可配置加解密芯片为FPGA芯片,所述原始二进制文件由配合FPGA芯片使用的软件生成并用于重新配置FPGA芯片。

优选的,所述S5中的加解密操作完成后将加解密操作后的数据存储在存储器中。

本发明采用个人特征以及录音数据特征作为数据加解密算法的密匙,并采用可重新配置的加解密算法,在对数据进行加解密操作后及时覆盖原始数据,防止录音数据被窃取,采用可重新配置密匙的加解密算法并根据随机选取的录音数据特征作为密匙,提升了数据采集过程以及数据采集后的数据安全程度,也提升了破解难度,实现了在线加解密实时传输。

本发明的技术方案不仅仅适用于英语录音信息传输的加密,还适用于其他语音信息的加密传输。

附图说明

图1为录音加解密方法流程图。

图2为步骤S3中的加解密算法的配置步骤。

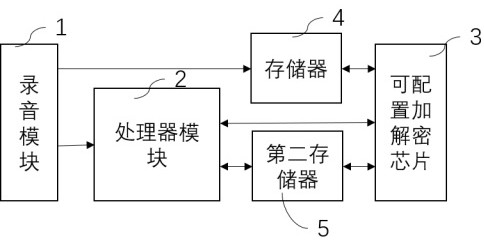

图3为录音加解密系统框图。

图4为录音加解密硬件架构图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例1

如图1-2所示,一种录音加解密方法,步骤如下:

S1、选取随机位置处的特定长度的录音数据;

S2、分析所述录音数据的特征参数;

S3、根据所述特征参数以及个人秘钥生成加解密算法配置参数;

S4、将所述配置参数以及加解密算法结合后生成原始二进制文件配置进可配置加解密芯片3中;

S5、所述可配置加解密芯片3对录音数据完成加解密操作。

作为一种优选的实施方式,所述S1中的选取方法为:读取录音时间长度,随机选取录音时间,根据录音强度断续时间确定特定长度的录音数据。

作为一种优选的实施方式,所述S2中的分析方法具体为:计算步骤S1中的录音数据的梅尔倒谱系数作为特征参数。

作为一种优选的实施方式,所述S3中的配置参数的生成步骤如下:将事先读取的录音设备持有人的个人特征参数如指纹数据或者设置的密码作为个人秘钥;读取步骤S2中的梅尔倒谱系数;将所述个人秘钥和梅尔倒谱系数组合形成配置序列,所述配置序列顺序或者倒序作为加解密算法的配置参数。

作为一种优选的实施方式,所述S3中的加解密算法可为AES加密解密算法(AESencryption and decryption),所述配置参数为作为AES加密解密算法的密钥,所述密钥长度为192bit或者256bit。

作为一种优选的实施方式,所述S4中的可配置加解密芯片3为FPGA芯片3’,所述原始二进制文件由配合FPGA芯片3’使用的软件生成并用于重新配置FPGA芯片3’。

作为一种优选的实施方式,所述S5中的加解密操作完成后将加解密操作后的数据存储在存储器4中。

实施例2

如图3-4所示,本发明还提供一种录音信息传输的加密系统,包括录音模块1、处理器模块2、存储器4、可配置加解密芯片3;

所述录音模块1、存储器4以及可配置加解密芯片3均连接处理器模块2;

所述处理器模块2获取录音模块1的录音数据,并选取随机位置处的特定长度的录音数据,并根据该特定长度的录音数据分析出梅尔倒谱系数,将所述梅尔倒谱系数结合个人特征参数形成配置参数;并将该配置参数以及加解密算法生成能够配置到可配置加解密芯片3的原始二进制文件;

所述可配置加解密芯片3可被处理器控制重新配置,并实现对存储器4中的录音数据进行加解密运算。

作为一种优选的实施方式,所述处理器和可配置加解密芯片3之间还连接有第二存储器5,用于存储原始二进制文件。

作为一种优选的实施方式,所述可配置加解密芯片3为FPGA芯片3’,所述FPGA芯片3’配置成被动配置模式,所述处理器模块2控制FPGA芯片3’读取第二存储器5中的原始二进制文件,并实现FPGA芯片3’在线重新配置。

作为一种优选的实施方式,所述存储器4也与FPGA芯片3’连接,用于存储加密后的录音数据。

作为一种优选的实施方式,所述存储器4为双口ROM4’,用于暂存录音模块1的录音数据以及FPGA芯片3’加密后的数据,所述FPGA芯片3’将加密后的录音数据覆盖录音模块1获取的原始录音数据。

作为一种优选的实施方式,所述第二存储器5为FLASH5’存储器4,所述FLASH5’存储器4仅用于存储配置FPGA芯片3’的配置文件。

作为一种优选的实施方式,所述处理器模块2以STM32处理器2’为核心;

作为一种优选的实施方式,所述录音模块1中包括控制器1-1以及与控制器1-1连接的双口SRAM 1-2,控制器在获取数字音频数据后存储在双口SRAM1-2中,STM32处理器2’连接双口SRAM1-2并获取存储在双口SRAM1-2中的数字音频数据;所述控制器1-1同时连接双口ROM4’并将数字音频数据同时存储在双口ROM4’上以供FPGA芯片3’加密数据并覆盖。

本发明采用个人特征以及录音数据特征作为数据加解密算法的密匙,并采用可重新配置的加解密算法,在对数据进行加解密操作后及时覆盖原始数据,防止录音数据被窃取,采用可重新配置密匙的加解密算法并根据随机选取的录音数据特征作为密匙,提升了数据采集过程以及数据采集后的数据安全程度,也提升了破解难度,实现了在线加解密实时传输。

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

- 一种录音信息传输的加密系统

- 一种防窃取的录音信息传输的加密方法