固态成像装置和电子设备

文献发布时间:2023-06-19 11:26:00

技术领域

本公开涉及一种通过执行光电转换进行成像的固态成像装置和包括该固态成像装置的电子设备。

背景技术

提出了一种将由设置在半导体层中的光电转换器生成的信号电荷暂时存储在设置在半导体层中的存储器中的固态成像装置(例如,参见PTL1)。

引用列表

专利文献

PTL 1:日本未审查专利申请公开第2005-347655号

发明内容

顺便提及,在这种固态成像装置中,在维持成像性能的同时,还期望更高的集成化。

因此,期望提供一种具有适于高集成化的配置的固态成像装置和包括这种成像装置的电子设备。

作为本公开的实施方案的固态成像装置包括:半导体层;光电转换器,其设置在所述半导体层中并通过光电转换生成与接收到的光量相对应的电荷;存储电容器,其设置在所述半导体层上并包括具有第一电膜厚度的第一绝缘膜;和第一晶体管,其设置在所述半导体层上并包括具有大于所述第一电膜厚度的第二电膜厚度的第二绝缘膜。

此外,作为本公开的实施方案的电子设备包括上面描述的成像装置。

在作为本公开的实施方案的成像装置和电子设备中,上面描述的配置可以使存储电容器的绝缘膜变薄,从而在不扩大存储电容器的占用面积的情况下增大存储电容器的电容。

附图说明

图1A是示出了根据本公开的第一实施方案的固态成像装置的功能的配置示例的框图。

图1B是示出了作为第一变形例的固态成像装置的功能的配置示例的框图。

图1C是示出了作为第二变形例的固态成像装置的功能的配置示例的框图。

图2是示出了在图1A中示出的固态成像装置中的一个传感器像素的电路配置示例的电路图。

图3是图2中示出的传感器像素的平面配置示例的平面图。

图4是图2中示出的传感器像素的断面配置示例的断面图。

图5A是图2中示出的传感器像素的制造方法的一个工序的断面图。

图5B是图5A之后的一个工序的断面图。

图5C是图5B之后的一个工序的断面图。

图5D是图5C之后的一个工序的断面图。

图5E是图5D之后的一个工序的断面图。

图5F是图5E之后的一个工序的断面图。

图5G是图5F之后的一个工序的断面图。

图6是示出了根据本公开的第二实施方案的固态成像装置中的一个传感器像素的电路配置示例的电路图。

图7是示出了图6中示出的传感器像素的一部分的断面配置示例的说明图。

图8是示出了根据本公开的第三实施方案的固态成像装置中的一个传感器像素的电路配置示例的电路图。

图9是包括图8中示出的传感器像素的一部分的断面配置示例的说明图。

图10是根据本公开的第四实施方案的固态成像装置中的一个传感器像素的平面配置示例的平面图。

图11是图10中示出的传感器像素的断面配置示例的断面图。

图12是包括根据本公开的第五实施方案的固态成像装置中的一个传感器像素的断面配置示例的说明图。

图13是包括根据本公开的第六实施方案的固态成像装置中的一个传感器像素的断面配置示例的说明图。

图14是包括根据本公开的第七实施方案的固态成像装置中的一个传感器像素的断面配置示例的说明图。

图15是包括根据本公开的第八实施方案的固态成像装置中的一个传感器像素的断面配置示例的说明图。

图16A是包括根据本公开的第九实施方案的固态成像装置中彼此相邻的两个传感器像素的断面配置示例的说明图。

图16B是包括作为图16A中示出的固态成像装置的变形例的固态成像装置的断面配置示例的说明图。

图17是包括根据本公开的第十实施方案的固态成像装置中彼此相邻的两个传感器像素的断面配置示例的说明图。

图18是电子设备的整体配置示例的示意图。

图19是示出了车辆控制系统的示意性配置的示例的框图。

图20是辅助说明车外信息检测部和成像部的安装位置的示例的图。

图21A是作为第三变形例的固态成像装置的主要部分的配置示例的断面图。

图21B是示出了作为图21A中示出的第三变形例的固态成像装置的主要部分的配置示例的电路图。

图22是作为第四变形例的固态成像装置的主要部分的配置示例的断面图。

图23是作为第五变形例的固态成像装置的主要部分的配置示例的断面图。

图24是作为第六变形例的固态成像装置的主要部分的配置示例的断面图。

图25是作为第七变形例的固态成像装置的主要部分的配置示例的断面图。

具体实施方式

下面参照附图对本公开的实施方案进行详细描述。需要注意的是,按照以下顺序进行描述。

1.第一实施方案

其中连接到电荷电压转换器的存储电容器中的第一绝缘膜的电膜厚度小于传输晶体管的栅极绝缘膜的电膜厚度的固态成像装置的示例

2.第二实施方案

其中作为电荷保持部的存储电容器中的第一绝缘膜的电膜厚度小于传输晶体管的栅极绝缘膜的电膜厚度的固态成像装置的示例

3.第三实施方案

其中通过开关部连接到电荷电压转换器的存储电容器中的第一绝缘膜的电膜厚度小于传输晶体管的栅极绝缘膜的电膜厚度的固态成像装置的示例

4.第四实施方案

其中放大晶体管的栅极绝缘膜的电膜厚度小于传输晶体管的栅极绝缘膜的电膜厚度的固态成像装置的示例

5.第五实施方案

其中存储电容器层叠在与光电转换器重叠的位置处的固态成像装置的示例

6.第六实施方案

其具有包括插头的垂直晶体管作为传输晶体管的固态成像装置的示例

7.第七实施方案

其中存储电容器是平坦型的n型MOS电容器的固态成像装置的示例

8.第八实施方案

其中存储电容器是包括凹凸结构的沟槽型MOS电容器的固态成像装置的示例

9.第九实施方案

进一步地包括不包括存储电容器的相邻像素的固态成像装置的示例10.第十实施方案

其中存储电容器跨越两个像素的两个光电转换器设置的固态成像装置的示例

11.电子设备的应用示例

12.移动体的应用示例

13.其他变形例

<1.第一实施方案>

[固态成像装置101的配置]

图1是示出了根据本技术的第一实施方案的固态成像装置101A的功能的配置示例的框图。

例如,固态成像装置101A是CMOS(互补金属氧化物半导体)图像传感器。固态成像装置101A通过接收来自被摄体的光并执行光电转换以生成图像信号来拍摄图像。

例如,固态成像装置101A包括像素阵列部111、垂直驱动器112、列信号处理器113、数据存储部119、水平驱动器114、系统控制器115和信号处理器118。

在固态成像装置101A中,像素阵列部111形成在半导体层11(后述的)上。例如,如垂直驱动器112、列信号处理器113、数据存储部119、水平驱动器114、系统控制器115和信号处理器118等外围电路形成在形成有像素阵列部111的同一半导体层11上。

像素阵列部111包括多个传感器像素110,每个传感器像素110包括光电转换器51(后述的)。光电转换器51生成与从被摄体接收到的光量相对应的电荷并存储电荷。如图1中示出的,传感器像素110分别沿水平方向(行方向)和垂直方向(列方向)排列。在像素阵列部111中,像素驱动线116沿行方向进行布线,其中每个像素行包括在行方向上排列成一条线的传感器像素110,垂直信号线(VSL)117沿列方向进行布线,其中每个像素列包括在列方向上排列成一条线的传感器像素110。

垂直驱动器112包括移位寄存器、地址解码器等。垂直驱动器112通过多条像素驱动线116向多个传感器像素110中的每一个传感器像素110提供信号等,以同时驱动像素阵列部111中所有多个传感器像素110或者以像素行为单位驱动多个传感器像素110。

例如,垂直驱动器112包括两个扫描系统,即,读出扫描系统和扫出扫描系统。读出扫描系统以行为单位对像素阵列部111的单位像素依次执行选择性扫描,以从单位像素读出信号。扫出扫描系统在读出扫描之前快门速度的时间对将要经过读出扫描系统的读出扫描的读出行执行扫出扫描。

通过扫出扫描系统的扫出扫描将来自读出行中的单位像素的光电转换器51的不必要的电荷扫出。这被称为"复位"。然后,通过由扫出扫描系统扫出不必要的电荷,即,通过复位,执行所谓的电子快门操作。这里,电子快门操作是指丢弃光电转换器51中的光电荷并且重新开始曝光,即,开始存储光电荷的操作。

将要通过读出扫描系统的读出操作读出的信号对应于紧接在前的读出操作或者电子快门操作之后接收到的光量。从紧接在前的读出操作的读出定时或者电子快门操作的扫出定时到当前读出操作的读出定时的时段是单位像素的光电荷存储时间,即,曝光时间。

从由垂直驱动器112选择性扫描的像素行的各个单位像素输出的信号通过各个垂直信号线117提供给列信号处理器113。对于像素阵列部111的每个像素列,列信号处理器113对通过垂直信号线117从所选择的行的各个单位像素输出的信号执行预定的信号处理,并且暂时保持已经经过信号处理的像素信号。

具体地,例如,列信号处理器113包括移位寄存器、地址解码器等,并对模拟像素信号等执行噪声去除处理、相关双采样、A/D(模拟/数字)转换A/D转换处理以生成数字像素信号。列信号处理器113将生成的像素信号提供给信号处理器118。

例如,水平驱动器114包括移位寄存器、地址解码器等,并依次选择与列信号处理器113的像素列相对应的单位电路。通过该水平驱动器114的选择性扫描,已经由列信号处理器113对每个单位电路进行了信号处理的像素信号被依次输出到信号处理器118。

例如,系统控制器115包括生成各种定时信号的定时生成器。系统控制器115基于由定时生成器生成的定时信号对垂直驱动器112、列信号处理器113和水平驱动器114执行驱动控制。

信号处理器118根据需要暂时将数据存储在数据存储部119中,同时对从列信号处理器113提供的像素信号执行如算术处理等信号处理,并输出包括各个像素信号的图像信号。

对于由信号处理器118进行的信号处理,数据存储部119暂时存储信号处理所需的数据。

需要注意的是,本技术的固态成像装置不限于图1A中示出的固态成像装置101A,并且例如,可以具有如图1B中示出的固态成像装置101B或者图1C中示出的固态成像装置101C等的配置。图1B是示出了作为根据本技术的第一实施方案的第一变形例的固态成像装置101B的功能的配置示例的框图。图1C是示出了作为根据本技术的第一实施方案的第二变形例的固态成像装置101C的功能的配置示例的框图。

在图1B的固态成像装置101B中,数据存储部119布置在列信号处理器113和水平驱动器114之间,并且从列信号处理器113输出的像素信号通过数据存储部119提供给信号处理器118。

此外,在图1C的固态成像装置101C中,数据存储部119和信号处理器118并排布置在列信号处理器113和水平驱动器114之间。在固态成像装置101C中,列信号处理器113以像素阵列部111的一列为单位或者以像素阵列部111的多列为单位执行A/D转换以将模拟像素信号转换成数字像素信号。

[传感器像素110的配置]

(电路配置示例)

接着,参照图2对设置在图1A的像素阵列部111中的传感器像素110的电路配置示例进行描述。图2示出了像素阵列部111中包括的多个传感器像素110中的一个传感器像素110的像素电路50的电路配置示例。

在图2示出的示例中,像素电路50包括光电转换器(PD)51、传输晶体管(TG)52、电荷电压转换器(FD)53、复位晶体管(RST)54、放大晶体管(AMP)55、选择晶体管(SEL)56和存储电容器(CP)57。

在该示例中,TG 52、RST 54、AMP 55和SEL 56中的每一个都是N型MOS晶体管。驱动信号S52、S54、S55和S56基于系统控制器115的驱动控制通过垂直驱动器112和水平驱动器114分别提供给TG 52、RST 54、AMP 55和SEL 56各自的栅电极。驱动信号S52、S54、S55和S56中的每一个都是其中高电平状态为激活状态(接通状态)并且低电平状态为非激活状态(断开状态)的脉冲信号。需要注意的是,在下文中,将驱动信号转成激活状态也被称为"接通驱动信号",而将驱动信号转成非激活状态也被称为"断开驱动信号"。

例如,PD 51是由PN结光电二极管构成的光电转换元件,并且接收来自被摄体的光,通过光电转换生成与接收到的光量相对应的电荷,并存储电荷。

TG 52连接在PD 51和FD 53之间,并且配置成根据施加到TG 52的栅电极的驱动信号S52将PD 51中存储的电荷传输到FD 53。TG 52是与本公开的"第一晶体管"和"传输晶体管"中的各者相对应的具体示例。

例如,RST 54具有连接到电源VDD1的漏极和连接到FD 53的源极。RST 54根据施加到其栅电极的驱动信号S54使FD 53初始化,即,复位。例如,在驱动信号S54被接通以接通RST 54的情况下,FD 53的电位被复位到电源VDD1的电压电平。即,FD 53被初始化了。

FD 53是PD 51中生成的电荷的传输目的地,并且是将从PD 51通过TG 52传输过来的电荷转换成电信号(例如,电压信号)并输出电信号的浮动扩散区域。FD 53连接到RST54,并且通过AMP 55和SEL 56连接到VSL 117。FD 53通过由金属等制成的布线W57进一步地连接到CP 57(参见后述的的图3和图4)。CP 57是与FD 53一起存储PD 51中生成并从PD 51传输的电荷的存储电容器。

例如,AMP 55具有连接到FD 53的栅极、连接到电源VDD2的漏极和连接到SEL 56的源极。AMP 55输出与FD 53的电位相对应的电信号。例如,SEL 56具有连接到AMP 55的漏极和连接到VSL 117的源极。当选择相应的传感器像素110时,SEL 56被接通,并且将已经从FD53经过AMP 55的电信号通过VSL 117输出到列信号处理器113。

(平面配置示例和断面配置示例)

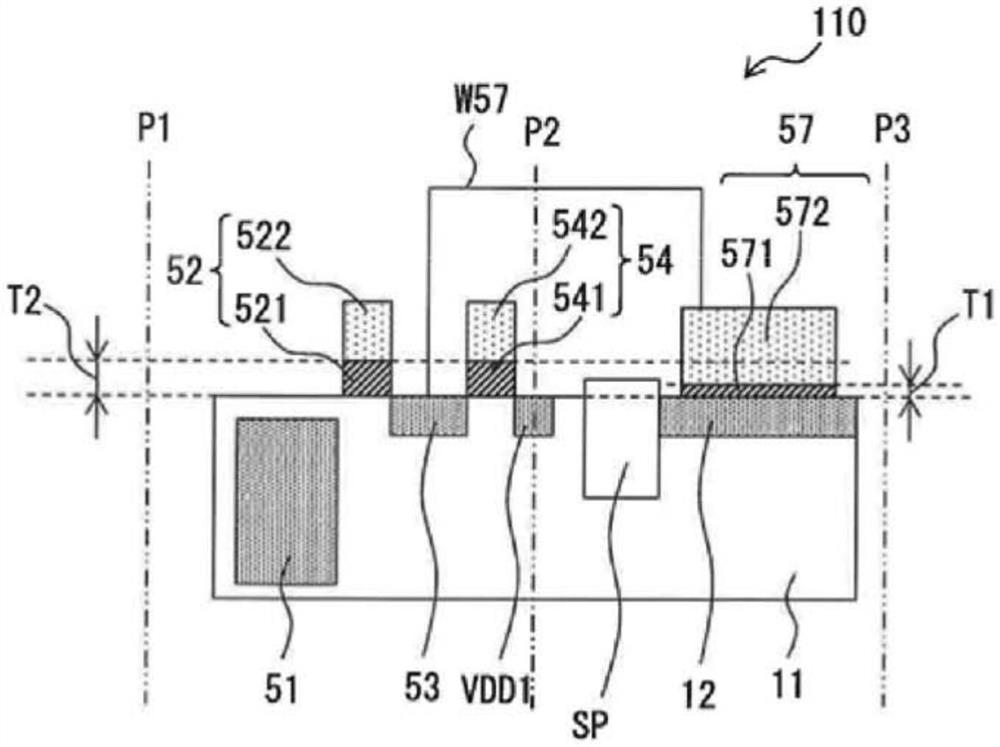

接着,对设置在图1A的像素阵列部111中的传感器像素110的平面配置示例和断面配置示例进行描述。图3示出了像素阵列部111中包括的多个传感器像素110中的一个传感器像素110的平面配置示例。此外,图4示出了一个传感器像素110的断面配置示例,并且对应于沿着图3中示出的切断线IV-IV获取的从箭头的方向观察的断面。需要注意的是,在图4中,从位置P1到位置P2的部分示出了沿Y轴方向的YZ断面,而从位置P2到位置P3的部分示出了沿X轴方向的XZ断面。

在图3示出的传感器像素110的示例中,PD 51占用传感器像素110的主要区域,并且FD 53、RST 54、AMP 55、SEL 56、CP 57、电源VDD1、电源VDD2和VSL 117设置在主要区域周围的区域中。TG 52设置于在Z轴方向(也被称为厚度方向或者深度方向)上与PD 51部分重叠的位置处。

如图3和图4中示出的,传感器像素110包括使用如Si(硅)等半导体材料形成的半导体层11、设置在半导体层11内部的PD 51和设置在半导体层11上的作为传输部的TG 52。TG 52在半导体层11上包括层叠结构,其中由氧化硅等构成的栅极绝缘膜521和栅电极层522依次层叠。类似地,RST 54在半导体层11上包括层叠结构,其中由氧化硅等构成的栅极绝缘膜541和栅电极层542依次层叠。FD 53设置在半导体层11的最上部的TG 52和RST 54之间。CP 57包括层叠在设置在半导体层11的最上部的杂质扩散层12上的绝缘膜571和层叠在绝缘膜571上的金属层572。FD 53通过布线W57连接到CP 57的金属层572。器件分离部SP设置在RST 54和CP 57之间。需要注意的是,在下文中,省略了器件分离部SP的描述。接触层12T(参见图3)设置在杂质扩散层12中。

这里,CP 57的绝缘膜571具有作为第一电膜厚度的膜厚度ET1和作为第一物理膜厚度的膜厚度T1。相反,TG 52的栅极绝缘膜521和RST54的栅极绝缘膜541中的每一个具有作为第二电膜厚度的膜厚度ET2和作为第二物理膜厚度的膜厚度T2。膜厚度ET2大于膜厚度ET1(ET1 电膜厚度是与通过将给定膜的物理膜厚度除以该给定膜的介电常数所获得的值(物理膜厚度/介电常数)成比例的参数,并且表示SiO 此外,CP 57的绝缘膜571、TG 52的栅极绝缘膜521和RST 54的栅极绝缘膜541可以分别由相同种类的材料,即,具有相同的介电常数的材料构成。然而,期望CP 57的绝缘膜571的介电常数高于TG 52的栅极绝缘膜521的介电常数和RST 54的栅极绝缘膜541的介电常数。这使得可以进一步地增大CP 57的存储电容,即,每单位像素占用面积的饱和电荷量。 (传感器像素110的操作) 接着,参照图2到图4,对传感器像素110的操作进行描述。在传感器像素110中,在读出在已经接收来自被摄体的光的PD 51中生成和存储的电荷时,基于系统控制器115的驱动控制,施加至TG 52的驱动信号S52被接通。这使得PD 51中存储的电荷通过TG 52从PD 51传输到FD 53。在电荷被传输到FD 53之后,FD 53将电荷转换成具有与每个电荷相对应的电平的电信号。此后,通过驱动信号S56接通SEL 56,使得来自FD 53电信号依次经过AMP 55和SEL 56,并通过VSL 117输出到列信号处理器113。 [传感器像素110的制造方法] 接着,参照图5A到图5G,对固态成像装置101A的制造方法进行描述。图5A到图5F中的每一个是固态成像装置101A的制造方法中的一个工序的断面图,并且是与图4相对应的断面图。 首先,如图5A中示出的,准备了嵌入了PD 51的半导体层11,并且通过离子注入在半导体层11的最上层的预定位置处形成杂质扩散层12。 接着,如图5B中示出的,例如,通过热氧化法或者溅射法沉积绝缘材料以覆盖半导体层11的整个表面,从而形成绝缘膜Z1。此时,将绝缘膜Z1调整成具有预定厚度T2。此后,在绝缘膜Z1上形成在与杂质扩散层12的部分区域重叠的位置处具有开口K1的抗蚀剂掩模RM1。 随后,如图5C中示出的,选择性地去除绝缘膜Z1的未被抗蚀剂掩模RM1覆盖的部分以形成开口Z1K,从而暴露杂质扩散层12的一部分。 此后,如图5D中示出的,去除抗蚀剂掩模RM1,然后选择性地形成绝缘膜Z2以填充开口Z1K。例如,绝缘膜Z2通过热氧化法、溅射法等沉积绝缘材料而获得。此时,将绝缘膜Z2调整成具有预定厚度T1。 接着,如图5E中示出的,形成栅电极材料膜M以覆盖绝缘膜Z1和绝缘膜Z2。此外,形成选择性地覆盖栅电极材料膜M的抗蚀剂掩模RM2。抗蚀剂掩模RM2包括部分RM2A到RM2C。这里,部分RM2A形成在将要形成TG 52的区域中。部分RM2A形成在将要形成RST 54的区域中。部分RM2C形成在将要形成CP 57的区域中。 此后,选择性地去除栅电极材料膜M的未被抗蚀剂掩模RM2覆盖的部分,然后去除抗蚀剂掩模RM2。因此,如图5F中示出的,分别在半导体层11上获得其中栅极绝缘膜521和栅电极层522依次层叠的TG52、其中栅极绝缘膜541和栅电极层542依次层叠的RST 54以及其中绝缘膜571和金属层572依次层叠在杂质扩散层12上的CP 57。 此后,如图5G中示出的,使用如光刻和离子注入等方法在半导体层11的最上层的预定位置处形成FD 53、电源VDD1等。需要注意的是,在图5A到图5G中,未示出AMP 55和SEL56;然而,通过与形成TG 52和RST 54的方法类似的方法,AMP 55和SEL 56可以与TG 52和RST 54同时形成。 最后,在形成布线W57等之后,完成了固态成像装置101A的制造。 [固态成像装置101A的效果] 如上所述,在根据本实施方案的固态成像装置101A中,在每个传感器像素110中,CP 57的绝缘膜571的膜厚度T1(膜厚度ET1)比像素电路50中包括的各晶体管,例如,TG 52的栅极绝缘膜521和RST 54的栅极绝缘膜541的膜厚度T2(膜厚度ET2)小。这使得在固态成像装置101A中,可以在没有增大CP 57的占用面积的情况下提高每个传感器像素110中的CP57的饱和电荷量。即,增大每个传感器像素110中的CP57的每单位面积的饱和电荷量。例如,这使得在固态成像装置101A中,可以提高每个传感器像素110中的PD 51的面积占用率,其使得可以实现传感器像素110的高集成化。 此外,在根据本实施方案的固态成像装置101A中,TG 52的栅极绝缘膜521的膜厚度T2(膜厚度ET2)大于CP 57的绝缘膜571的膜厚度T1(膜厚度ET1),使得可以对TG 52施加更高的电压,并且更快地将电荷从PD 51传输到FD 53。 <2.第二实施方案> [传感器像素210的配置] 图6示出了根据本技术的第二实施方案的传感器像素210中的像素电路50A的电路配置示例。此外,图7示出了传感器像素210的断面配置示例。 如图6中示出的,代替根据上面描述的第一实施方案的传感器像素110,传感器像素210包括在固态成像装置101A中,并且实现所谓的全局快门系统图像传感器(globalshutter system image sensor)。 全局快门系统是其中基本上所有像素的曝光同时开始并且所有像素的曝光同时结束的系统。这里,所有像素指的是除伪像素等之外的在图像中出现的部分中的所有像素。此外,在时间差和图像失真十分小的情况下,全局快门系统包括其中以多行(例如,几十行)为单位进行全局曝光代替对所有像素同时进行(全局曝光),同时移动要进行全局曝光的区域的系统。此外,全局快门系统还包括其中不是对图像中出现的部分中的所有像素而是对预定区域中的像素进行全局曝光的系统。 在图6示出的示例中,像素电路50A与像素电路50的不同之处在于在PD 51和FD 53之间进一步地包括电荷保持部(MEM)59来代替CP 57。此外,像素电路50A与像素电路50的不同之处在于代替TG 52包括第一传输晶体管(TG)52A和第二传输晶体管(TG)52B。TG 52A设置在PD 51和MEM 59之间,TG 52B设置在MEM 59和FD 53之间。像素电路50A进一步地包括电源VDD3作为PD 51中生成的电荷的传输目的地,并且包括PD 51和电源VDD3之间的排出晶体管(OFG)58。除这些点以外,像素电路50A具有与如上所述的第一实施方案的像素电路50基本上相同的配置。 如图7中示出的,在传感器像素210中,例如,电源VDD3、杂质扩散层12、FD 53、电源VDD1等形成在半导体层11的最上层中。OFG 58、TG 52A、MEM 59、TG 52B、RST 54等形成在半导体层11上。 OFG 58具有连接到电源VDD3的漏极和与连接在TG 52与PD 51之间的布线连接的源极。在半导体层11上,OFG 58包括其中由氧化硅等构成的栅极绝缘膜581和栅电极层582依次层叠的层叠结构。OFG 58根据施加到栅电极层582的驱动信号S58使PD 51初始化,即,复位。使PD 51复位意味着耗尽PD 51。 此外,OFG 58在TG 52和电源VDD3之间形成溢出路径,并且将从PD 51溢出的电荷排出到电源VDD3。因此,在根据本实施方案的传感器像素210中,可以实现其中OFG 58能够直接使PD 51复位的FD保持型全局快门(FD-holding type global shutter)。 MEM 59设置在PD 51和FD 53之间,并且是为了实现全局快门功能,暂时保持PD 51中生成和存储的电荷直到电荷被传输到FD 53的区域。在半导体层11上,MEM 59包括其中由氧化硅等构成的绝缘膜591和由多晶硅等构成的栅电极层592依次层叠的层叠结构。 TG 52A设置在PD 51和MEM 59之间,并且TG 52B设置在MEM 59和FD 53之间。在半导体层11上,TG 52A包括其中由氧化硅等构成的栅极绝缘膜521A和栅电极层522A依次层叠的层叠结构。TG 52A配置成根据施加到栅电极层522A的驱动信号S52A将PD 51中存储的电荷传输到MEM 59。在半导体层11上,TG 52B包括其中由氧化硅等构成的栅极绝缘膜521B和栅电极层522B依次层叠的层叠结构。TG 52B配置成根据施加到栅电极层522B的驱动信号S52B将暂时保持在MEM 59中的电荷传输到FD 53。例如,在传感器像素210中,在驱动信号S52A断开以断开TG 52A并且驱动信号S52B接通以接通TG 52B的情况下,保持在MEM 59中的电荷通过TG 52B被传输到FD 53。 这里,MEM 59的绝缘膜591具有作为第一电膜厚度的膜厚度ET1和作为第一物理膜厚度的膜厚度T1。绝缘膜591是与本公开的"第一绝缘膜"相对应的具体示例。相反,OFG 58的栅极绝缘膜581、TG 52A的栅极绝缘膜521A、TG 52B的栅极绝缘膜521B和RST 54的栅极绝缘膜541中的每一个都具有作为第二电膜厚度的膜厚度ET2和作为第二物理膜厚度的膜厚度T2。膜厚度ET2大于膜厚度ET1(ET1 此外,MEM 59的绝缘膜591与栅极绝缘膜581、521A、521B和541可以分别由相同种类的材料,即,具有相同的介电常数的材料构成。然而,期望MEM 59的绝缘膜591的介电常数高于栅极绝缘膜581、521A、521B和541的介电常数中的每一个介电常数。这使得可以进一步地增大MEM 59的存储电容,即,每单位像素占用面积的饱和电荷量。 在根据本实施方案的传感器像素210中,进一步地设置MEM 59,从而将电荷从PD51传输到MEM 59,使得可以实现存储器保持型全局快门(memory-holding type globalshutter)。具体地,在传感器像素210中,在施加到TG 52A的栅电极的驱动信号S52A接通以接通TG 52A的情况下,PD 51中存储的电荷通过TG 52A被传输到MEM 59。MEM 59是暂时保持PD 51中存储的电荷以实现全局快门功能的区域。TG 52B根据施加到TG 52B的栅电极层522B的驱动信号S52B将保持在MEM 59中的电荷传输到FD 53。例如,在驱动信号S52断开以断开TG 52A并且驱动信号S52B接通以接通TG 52B的情况下,保持在MEM 59中的电荷通过TG52B被传输到FD 53。 [传感器像素210的效果] 如上所述,根据本实施方案的传感器像素210能够在不增大MEM 59的占用面积的情况下提高MEM 59的饱和电荷量。即,在每个传感器像素210中,MEM 59的每单位面积的饱和电荷量提高。因此,在包括多个这种传感器像素210的全局快门系统固态成像装置中,可以实现传感器像素210的高集成化。 <3.第三实施方案> [传感器像素310的配置] 图8示出了根据本技术的第三实施方案的传感器像素310中的像素电路50B的电路配置示例。此外,图9示出了传感器像素310的断面配置示例。 如图8中示出的,除了根据上面描述的第一实施方案的传感器像素110之外,传感器像素310还包括设置在FD 53和CP 57之间的开关晶体管(FDG)60。除了这一点以外,传感器像素310具有与传感器像素110基本上相同的配置。如图9中示出的,例如,FDG 60包括设置在半导体层11的最上层中的杂质扩散层603、层叠在半导体层11上的栅极绝缘膜601和层叠在栅极绝缘膜601上的栅电极层602。基于系统控制器115的驱动控制,通过垂直驱动器112和水平驱动器114将驱动信号S60提供给栅电极层602。这里,向栅电极层602施加驱动信号S60使得FD 53和CP 57彼此连接。 在本实施方案中,进一步地包括FDG 60,使得可以在FD 53与CP 57之间的连接状态和FD 53与CP 57之间的断开状态之间自由地进行切换。此外,例如,栅极绝缘膜601的电膜厚度基本上与TG 52的栅极绝缘膜521的膜厚度ET2相同,并且大于CP 57的绝缘膜571的膜厚度ET1。例如,在栅极绝缘膜601、栅极绝缘膜521和绝缘膜571各自的构成材料相同的情况下,例如,栅极绝缘膜601的物理膜厚度基本上与TG 52的栅极绝缘膜521的膜厚度T2相同,并且大于CP 57的绝缘膜571的膜厚度T1。 [传感器像素310的效果] 如上所述,即使在根据本实施方案的传感器像素310中,CP 57的绝缘膜571的膜厚度T1(膜厚度ET1)小于像素电路50B中包括的各个晶体管的栅极绝缘膜,例如,TG 52的栅极绝缘膜521和FDG 60的栅极绝缘膜601的膜厚度T2(膜厚度ET2)。这使得可以预期与根据上面描述的第一实施方案的传感器像素110类似的效果。 <4.第四实施方案> [传感器像素410的配置] 图10示出了根据本技术的第二实施方案的传感器像素410的平面配置示例。此外,图11示出了传感器像素410的断面配置示例,并且对应于沿图10中示出的切断线XI-XI获取的从箭头的方向观察的断面。需要注意的是,在图11中,从位置P11到位置P12的部分和从位置P13到位置P14的部分中的每一个都示出了沿Y轴方向的YZ断面,并且从位置P12到位置P13的部分示出了沿X轴方向的XZ断面。 如图11中示出的,在半导体层11上,AMP 55包括其中由氧化硅等构成的栅极绝缘膜551和栅电极层552依次层叠的层叠结构。在根据上面描述的第一实施方案的传感器像素110中,例如,AMP 55的栅极绝缘膜具有比膜厚度T1(膜厚度ET1)大的膜厚度T2(膜厚度ET2)。相反,在根据本实施方案的传感器像素410中,例如,AMP 55的栅极绝缘膜551具有作为第三电膜厚度的膜厚度ET3和作为第三物理膜厚度的膜厚度T3。例如,栅极绝缘膜551的膜厚度ET3小于TG 52的栅极绝缘膜521的膜厚度ET2。此外,例如,在栅极绝缘膜551和栅极绝缘膜521各自的构成材料相同的情况下,即,在栅极绝缘膜551和栅极绝缘膜521分别由具有相同的介电常数的材料构成的情况下,栅极绝缘膜551的膜厚度T3小于栅极绝缘膜521的膜厚度T2。 需要注意的是,图11例举了膜厚度T3(膜厚度ET3)基本上与膜厚度T1(膜厚度ET1)相同的情况,但是膜厚度T3(膜厚度ET3)可以与膜厚度T1(膜厚度ET1)不同。 这里,AMP 55是与本发明的"第二晶体管"相对应的具体示例,并且栅极绝缘膜551是与本公开的"第三绝缘膜"相对应的具体示例。 [传感器像素410的效果] 如上所述,即使在根据本实施方案的传感器像素410中,CP 57的绝缘膜571的膜厚度T1(膜厚度ET1)小于传感器像素410中包括的各个晶体管的栅极绝缘膜,例如,TG 52的栅极绝缘膜521的膜厚度T2(膜厚度ET2)。这使得可以预期与根据上面描述的第一实施方案的传感器像素110类似的效果。 此外,在根据本实施方案的传感器像素410中,AMP 55的栅极绝缘膜551的膜厚度T3(膜厚度ET3)小于TG 52的栅极绝缘膜521和FDG 60的栅极绝缘膜601中每一个的膜厚度ET2(膜厚度ET2)。这使得可以降低AMP 55中的RTS噪声(随机电讯信号噪声(randomtelegraph signal noise))。 <5.第五实施方案> [传感器像素510的配置] 图12示出了根据本技术的第五实施方案的传感器像素510的整体配置示例。在传感器像素510中,存储电容器(CP)57层叠于在半导体层11的厚度方向上与光电转换器(PD)51重叠的位置处。在传感器像素510中,CP 57是连接到FDG 60的MOS电容器。除了这一点以外,传感器像素510具有与根据上面描述的第三实施方案的传感器像素310基本上相同的配置。 在传感器像素510中,可以根据被摄体照度在低转换效率的情况和高转换效率的情况之间进行切换。即,可以通过FDG 60的开/关操作切换FD 53的电容。例如,接通FDG 60使得FD 53连接到作为MOS电容器的CP 57。因此,FD 53的电容增加,并且转换效率降低。 [传感器像素510的效果] 如上所述,即使在根据本实施方案的传感器像素510中,CP 57的绝缘膜571的膜厚度T1(膜厚度ET1)也小于传感器像素510中包括的各个晶体管的栅极绝缘膜,例如,TG 52的栅极绝缘膜521和FDG 60的栅极绝缘膜601中每一个的膜厚度T2(膜厚度ET2)。这使得可以预期与根据上面描述的第一实施方案的传感器像素110类似的效果。 此外,在根据本实施方案的传感器像素510中,CP 57层叠在PD 51上,使得可以增大PD 51的形成面积与传感器像素510的占用面积的比率。这对固态成像装置的高集成化是有利的。 <6.第六实施方案> [传感器像素610的配置] 图13示出了根据本技术的第六实施方案的传感器像素610的整体配置示例。在传感器像素610中,代替TG 52设置了TG 61。TG 61是包括栅极绝缘膜611和栅电极612的垂直晶体管,栅电极612包括在半导体层11的厚度方向延伸的插头612a。插头612a插入在半导体层11中形成的在半导体层11的厚度方向上延伸的沟槽11TR中。头部612b设置在插头612a的上端。栅电极612通过覆盖沟槽11TR的内表面的栅极绝缘膜611与半导体层11分离。沟槽11TR具有完全被栅极绝缘膜611覆盖的壁面和底面。除这一点以外,传感器像素610具有与根据上面描述的第五实施方案的传感器像素510基本上相同的配置。 需要注意的是,TG 61是与本公开的"第一晶体管"和"垂直晶体管"中的各者相对应的具体示例。此外,栅极绝缘膜611是与本公开的"第二绝缘膜"相对应的具体示例。 在传感器像素610中,作为CP 57的绝缘膜571的电膜厚度的膜厚度ET1的最小值小于作为栅极绝缘膜611的电膜厚度的膜厚度ET2的最小值。因此,例如,在绝缘膜571的介电常数和栅极绝缘膜611的介电常数彼此相同的情况下,作为CP 57的绝缘膜571的物理膜厚度的膜厚度T1的最小值小于作为栅极绝缘膜611的物理膜厚度的膜厚度T2的最小值。这使得可以预期与根据上面描述的第一实施方案的传感器像素110类似的效果。 传感器像素610设置有作为垂直晶体管的TG 61。这使得可以使TG61的插头612a离PD 51更近。这使得更容易将电荷从PD 51传输到FD53。 <7.第七实施方案> [传感器像素710的配置] 图14示出了根据本技术的第七实施方案的传感器像素710的整体配置示例。例如,传感器像素710进一步地包括PD 51和CP 57之间的n 即使在传感器像素710中,作为CP 57的绝缘膜571的电膜厚度的膜厚度ET1的最小值小于作为栅极绝缘膜611的电膜厚度的膜厚度ET2的最小值。因此,在绝缘膜571的介电常数和栅极绝缘膜611的介电常数彼此相同的情况下,作为CP 57的绝缘膜571的物理膜厚度的膜厚度T1的最小值小于作为栅极绝缘膜611的物理膜厚度的膜厚度T2的最小值。这使得可以预期与根据上面描述的第一实施方案的传感器像素110类似的效果。 <8.第八实施方案> [传感器像素810的配置] 图15示出了根据本技术的第八实施方案的传感器像素810的整体配置示例。代替CP 57,传感器像素810包括存储电容器(CP)63,存储电容器(CP)63包括绝缘膜631和导电层632。在传感器像素810中,多个沟槽64TR形成在n 在传感器像素810中,作为CP 63的绝缘膜631的电膜厚度的膜厚度ET1的最小值小于作为栅极绝缘膜611的电膜厚度的膜厚度ET2的最小值。因此,例如,在绝缘膜631的介电常数和栅极绝缘膜611的介电常数彼此相同的情况下,作为CP 63的绝缘膜631的物理膜厚度的膜厚度T1的最小值小于作为栅极绝缘膜611的物理膜厚度的膜厚度T2的最小值。这使得可以预期与根据上面描述的第一实施方案的传感器像素110类似的效果。 如上所述,在传感器像素810中,代替CP 57,设置有包括凹凸结构的CP 63,并且绝缘膜631的表面积增大而大于绝缘膜571的表面积,使得可以增大CP 63的电容而大于CP 57的电容。 <9.第九实施方案> 图16A示出了根据本技术的第九实施方案的固态成像装置的主要部分的配置示例。根据本实施方案的固态成像装置包括彼此相邻布置的传感器像素910a和传感器像素910b。传感器像素910a具有与图14中示出的根据第七实施方案的传感器像素710基本上相同的配置。传感器像素910b设置在与半导体层11相邻的半导体层80中,并且包括光电转换器(PD)81、传输晶体管(TG)82、电荷电压转换器(FD)83、复位晶体管(RST)84、放大晶体管(AMP)85和选择晶体管(SEL)86。PD 81、TG 82、FD 83、RST 84、AMP 85和SEL 86分别具有与PD 51、TG 52、FD 53、RST 54、AMP 55和SEL 56相对应的功能。即,例如,与PD 51类似,传感器像素910b中的PD 81通过光电转换生成与接收到的光量相对应的电荷。 如上所述,不像传感器像素910a,传感器像素910b不包括存储电容器。因此,传感器像素910a中的CP 57存储通过PD 51生成的电荷并且也存储通过PD 81生成的电荷。 在根据本实施方案的固态成像装置中,例如,传感器像素910a的PD 51的灵敏度高于相邻传感器像素910b的PD 81的灵敏度。即,传感器像素910a中的PD 51的光接收面积大于传感器像素910b中的PD 81的光接收面积。因此,在根据本实施方案的固态成像装置中,包括CP 57的传感器像素910a被用作高灵敏度像素,并且传感器像素910b被用作低灵敏度像素,使得可以扩大动态范围。 需要注意的是,在图16A示出的固态成像装置中,传感器像素910b设置在与半导体层11不同的半导体层80中;然而,传感器像素910b可以设置在设置有传感器像素910a的同一半导体层11中。 此外,在图16A示出的固态成像装置中,CP 57在传感器像素910a和传感器像素910b之间共享。然而,本公开不限于此。例如,像作为图16A中的固态成像装置的变形例的图16B中的固态成像装置一样,CP 57可以不在传感器像素910a和传感器像素910b之间共享。在图16B的固态成像装置中,传感器像素910a中的CP 57没有连接到传感器像素910a的FD53,而是连接到传感器像素910b的FD 83。在图16B的固态成像装置中,由传感器像素910a的PD 51生成的电荷没有存储在CP 57中,并且由传感器像素910b的PD 81生成的电荷存储在CP 57中。 <10.第十实施方案> 图17示出了根据本技术的第十实施方案的固态成像装置的主要部分的配置示例。与根据上面描述的第九实施方案的固态成像装置类似,根据本实施方案的固态成像装置包括彼此相邻布置的传感器像素910a和传感器像素910b。然而,传感器像素910b设置在设置有传感器像素910a的同一半导体层11中。此外,在根据本实施方案的固态成像装置中,CP57在半导体层11的面内方向上跨越PD 51和PD 81二者设置,即,CP 57的一部分布置于在半导体层11的厚度方向上与PD 51和PD 81两者重叠的位置处。除这些点以外,根据本实施方案的固态成像装置(图17)具有与根据上面描述的第九实施方案的固态成像装置(图16)基本上相同的配置。 如上所述,在本实施方案中,一个CP 57设置成与彼此相邻的两个传感器像素910a和910b重叠,使得可以在不扩大由整个固态成像装置占用的面积的情况下进一步地增大CP57的电容。这在固态成像装置的高集成化方面是有利的。 <11.电子设备的应用示例> 图18是示出了作为应用本技术的电子设备的相机2000的配置示例的框图。 相机2000包括由透镜组等组成的光学部2001、应用上面描述的固态成像装置101等(以下被称为固态成像装置101等)的成像装置(成像设备)2002和作为相机信号处理电路的DSP(数字信号处理器)电路2003。此外,相机2000还包括帧存储器2004、显示部2005、记录部2006、操作部2007和电源部2008。DSP电路2003、帧存储器2004、显示部2005、记录部2006、操作部2007和电源部2008通过总线2009彼此连接。 光学部2001捕获来自被摄体的入射光(图像光)并在成像装置2002的成像面上形成图像。成像装置2002将通过光学部2001在成像面上形成图像的入射光的光量以像素为单位转换成电信号并输出电信号作为像素信号。 例如,显示部2005包括如液晶面板和有机EL面板等的面板式显示装置,并且显示由成像装置2002拍摄的移动图像或者静止图像。记录部2006将由成像装置2002拍摄的移动图像或者静止图像记录在如硬盘或者半导体存储器等记录介质中。 操作部2007由用户操作以对相机2000的各种功能发出操作指令。电源部2008适当地向DSP电路2003、帧存储器2004、显示部2005、记录部2006和操作部2007提供各种类型的电源作为操作这些供应目标的电源。 如上所述,将上面描述的固态成像装置101A等用作成像装置2002使得可以预期获得良好的图像。 <12.移动体的应用示例> 根据本公开的技术(本技术)可以适用于各种产品。例如,根据本公开的技术被实现为安装在诸如汽车、电动汽车、混合动力汽车、摩托车、自行车、个人移动装置、飞机、无人机、船舶、机器人等任何类型的移动体上的装置。 图19是示出了作为可以应用根据本公开的实施方案的技术的移动体控制系统的示例的车辆控制系统的示意性配置示例的框图。 车辆控制系统12000包括经由通信网络12001彼此连接的多个电子控制单元。在图19所示的示例中,车辆控制系统12000包括驱动系统控制单元12010、车身系统控制单元12020、车外信息检测单元12030、车内信息检测单元12040和综合控制单元12050。此外,微型计算机12051、声音/图像输出部12052和车载网络接口(I/F)12053被示出为综合控制单元12050的功能构成。 驱动系统控制单元12010根据各种程序控制与车辆的驱动系统相关的装置的操作。例如,驱动系统控制单元12010用作以下装置的控制装置:诸如内燃机或驱动电机等用于产生车辆的驱动力的驱动力产生装置;用于将驱动力传递至车轮的驱动力传递机构;用于调整车辆的转向角的转向机构;以及用于产生车辆的制动力的制动装置等。 车身系统控制单元12020根据各种程序控制设置到车身上的各种装置的操作。例如,车身系统控制单元12020用作无钥匙进入系统、智能钥匙系统、电动窗装置或诸如车头灯、车尾灯、刹车灯、转向信号灯或雾灯等各种灯的控制装置。在这种情况下,从作为钥匙的替代的便携式装置传输过来的无线电波或各种开关的信号能够输入至车身系统控制单元12020。车身系统控制单元12020接收这些输入的无线电波或信号,并且控制车辆的门锁装置、电动窗装置和灯等。 车外信息检测单元12030检测关于具有车辆控制系统12000的车辆的外部的信息。例如,车外信息检测单元12030与成像部12031连接。车外信息检测单元12030使成像部12031对车辆外部的图像进行成像,并且接收所拍摄的图像。在接收的图像的基础上,车外信息检测单元12030可以对诸如人、车辆、障碍物、标记或路面上的符号等物体执行检测处理或距这些物体的距离的检测处理。 成像部12031是光学传感器,其用于接收光并且输出与接收的光的光量对应的电信号。成像部12031可以输出电信号作为图像,或可以输出电信号作为关于测量距离的信息。此外,成像部12031接收的光可以是可见光,或可以是诸如红外线等不可见光。 车内信息检测单元12040检测关于车辆内部的信息。例如,车内信息检测单元12040与检测驾驶员状态的驾驶员状态检测部12041连接。驾驶员状态检测部12041例如包括对驾驶员进行成像的相机。在从驾驶员状态检测部12041输入的检测信息的基础上,车内信息检测单元12040可以计算驾驶员的疲劳程度或驾驶员的集中程度,或可以判断驾驶员是否正在打瞌睡。 微型计算机12051可以在关于车辆内部或外部的信息(该信息是由车外信息检测单元12030或车内信息检测单元12040获得的)的基础上计算驱动力产生装置、转向机构或制动装置的控制目标值,并向驱动系统控制单元12010输出控制命令。例如,微型计算机12051可以执行旨在实现先进驾驶员辅助系统(ADAS:advanced driver assistancesystem)的功能的协同控制,该功能包括:车辆的碰撞避免或撞击减轻、基于车间距离的跟车行驶、车辆速度维持行驶、车辆碰撞警告或车辆偏离车道警告等。 此外,微型计算机12051可以执行旨在用于自动驾驶的协同控制,其在关于车辆内部或外部的信息(该信息是由车外信息检测单元12030或车内信息检测单元12040获得的)的基础上通过控制驱动力产生装置、转向机构或制动装置等使车辆自主行驶,而不依赖于驾驶员的操作等。 此外,微型计算机12051可以在关于车辆外部的信息(该信息是由车外信息检测单元12030获得的)的基础上向车身系统控制单元12020输出控制命令。例如,微型计算机12051可以根据车外信息检测单元12030检测到的前方车辆或对向车辆的位置通过控制车头灯以从远光灯变为近光灯来执行旨在防止眩光的协同控制。 声音/图像输出部12052将声音和图像中的至少一种的输出信号传输到输出装置,该输出装置能够在视觉上或听觉上将信息通知车辆的乘客或车辆的外部。在图11的示例中,音频扬声器12061、显示部12062和仪表面板12063被示出为输出装置。例如,显示部12062可以包括车载显示器和平视显示器中的至少一者。 图20是示出了成像部12031的安装位置的示例的图。 在图20中,成像部12031包括成像部12101、12102、12103、12104和12105。 成像部12101、12102、12103、12104和12105例如设置在车辆12100的前鼻、侧视镜、后保险杠和后门上的位置以及车辆内部挡风玻璃的上部上的位置。设置到前鼻上的成像部12101和设置到车辆内部挡风玻璃的上部上的成像部12105主要获得车辆12100的前方的图像。设置到侧视镜上的成像部12102和12103主要获得车辆12100的侧面的图像。设置到后保险杠或后门上的成像部12104主要获得车辆12100的后方的图像。设置到车辆内部挡风玻璃的上部上的成像部12105主要用于检测前方车辆、行人、障碍物、信号、交通标志或车道等。 顺便提及,图20示出了成像部12101至12104的拍摄范围的示例。成像范围12111表示设置到前鼻上的成像部12101的成像范围。成像范围12112和12113分别表示设置到侧视镜上的成像部12102和12103的成像范围。成像范围12114表示设置到后保险杠或后门上的成像部12104的成像范围。例如,通过叠加由成像部12101至12104拍摄的图像数据,获得从上方观看到的车辆12100的俯瞰图像。 成像部12101至12104中的至少一者可以具有获得距离信息的功能。例如,成像部12101至12104中的至少一者可以是由多个成像元件构成的立体相机,或者可以是具有用于相位差检测的像素的成像元件。 例如,微型计算机12051可以在从成像部12101至12104获得的距离信息的基础上确定到成像范围12111到12114内的每个三维物体的距离和距离的时间变化(相对于车辆12100的相对速度),从而提取最近的三维物体作为前方车辆,特别地,该三维物体存在于车辆12100的行驶路径上并且以预定速度(例如,等于或大于0千米/小时)在与车辆12100基本相同的方向上行驶。此外,微型计算机12051可以预先设定在前方车辆前方要保持的车间距离,并且执行自动制动控制(包括跟车停止控制)或自动加速控制(包括跟车启动控制)等。因此,可以执行旨在用于自动驾驶的协同控制,其使得车辆自主行驶而不依赖于驾驶员的操作等 例如,微型计算机12051可以在从成像部12101至12104获得的距离信息的基础上将关于三维物体的三维物体数据分类为两轮车辆、标准尺寸车辆、大型车辆、行人、电线杆和其他三维物体的三维物体数据,提取分类后的三维物体数据,并使用所提取的三维物体数据来自动避开障碍物。例如,微型计算机12051将车辆12100周围的障碍物识别为车辆12100的驾驶员可以在视觉上识别的障碍物以及车辆12100的驾驶员难以在视觉上识别的障碍物。然后,微型计算机12051确定表示与每个障碍物碰撞的风险的碰撞风险。在碰撞风险等于或高于设定值并且因此存在碰撞可能性的情况下,微型计算机12051经由音频扬声器12061或显示部12062向驾驶员输出警告,并通过驱动系统控制单元12010执行强制减速或者避让转向。微型计算机12051由此可以辅助驱动以避免碰撞。 成像部12101至12104中的至少一者可以是检测红外线的红外摄像机。例如,微型计算机12051可以通过确定成像部12101至12104的拍摄图像中是否存在行人来识别行人。例如,通过在作为红外摄像机的成像部12101至12104的拍摄图像中提取特征点的程序以及通过对表示物体轮廓的一系列特征点执行图案匹配处理来确定是否是行人的程序来执行对行人的这种识别。当微型计算机12051确定成像部12101至12104的拍摄图像中存在行人并且因此识别出行人时,声音/图像输出部12052控制显示部12062,使得用于强调的方形轮廓线以叠加在识别出的行人上的方式显示。声音/图像输出部12052还可以控制显示部12062,使得表示行人的图标等显示在期望的位置处。 上面已经描述了可以应用根据本公开的技术的车辆控制系统的一个示例。根据本公开的技术可以应用于上面描述的部件中的成像部12031。具体地,图1等中示出的固态成像装置101A等适用于成像部12031。将根据本公开的技术应用于成像部12031使得可以预期车辆控制系统的优异操作。 <13.其他变形例> 虽然已经参照一些实施方案和变形例对本公开进行了描述,但是本公开不限于上面描述的实施方案等,并且可以以多种方式进行修改。例如,本公开的固态成像装置不限于包括上面描述的任意实施方案等中描述的像素电路的固态成像装置,并且可以包括包含各种像素电路中任一种像素电路的固态成像装置。 图21A是作为本公开的第三变形例的固态成像装置201的主要部分的配置示例的断面图。图21B是固态成像装置201的电路图。固态成像装置201包括彼此相邻布置的两个传感器像素PX1和PX2。传感器像素PX1包括嵌入半导体层200中的光电转换器PD1、设置在半导体层200的前表面200A附近的传输栅极TGL、电荷电压转换器FD1、电荷电压转换栅极FDG、复位晶体管RST1、放大晶体管AMP、选择晶体管SEL56和浮动电容器FC。这里,复位晶体管RST的在与电荷电压转换栅极FDG相反一侧的端部连接到电源VDD1。传感器像素PX2包括嵌入半导体层200中的光电转换器PD2,以及设置在半导体层200的前表面200A附近的传输栅极TGS和浮动电容器栅极FCG。这里,浮动电容器FC的第一端部连接到传感器像素PX1中的电源FCVDD,并且浮动电容器FC的第二端部连接到传感器像素PX2中的传输栅极TGS和浮动电容器栅极FCG之间的中间部分。在传感器像素PX1中,滤色器CF1和片上透镜LN1依次层叠在半导体层200的后表面200B上。类似地,在传感器像素PX2中,滤色器CF2和片上透镜LN2依次层叠在半导体层200的后表面200B上。遮光膜BM选择性地嵌入滤色器CF1和CF2中的每一个中。遮光膜BM设置在彼此相邻的传感器像素之间的边界部分中。在半导体层200的厚度方向上延伸的遮光壁BW设置在每个遮光膜BM的正下方。例如,遮光膜BM和遮光壁BW由金属制成,但不限于此。 在固态成像装置201中,传感器像素PX1中的光电转换器PD1和浮动电容器FC在半导体层200的厚度方向上彼此重叠地层叠。此外,传输栅极TGL是在半导体层200的厚度方向上延伸至光电转换器PD1的垂直型栅极。 此外,在固态成像装置201中,遮光膜BM嵌入滤色器CF1和CF2中的每一个中,但是本公开不限于此。例如,像作为图22中示出的本公开的第四变形例的固态成像装置202一样,包括滤色器CF1和CF2的层可以与包括遮光膜BM的层分开设置。 此外,在上面描述的各个实施方案中,垂直晶体管的栅电极的插头设置于在平面图中与光电转换器不同的位置处,但是本公开不限于此。此外,上面描述的各个实施方案已经举例说明了垂直晶体管的栅电极包括插头和覆盖插头的上端的帽,但是本公开不限于此。即,本公开包括图23到图25中示出的各个模式。 具体地,像在图23中示出的作为本公开的第五变形例的固态成像装置203一样,作为垂直晶体管的TG 61的栅电极612的插头612a可以设置于在平面图中与PD 51重叠的位置处,并且插头612a可以插入PD 51中。 此外,像在图24中示出的作为本公开的第六变形例的固态成像装置204一样,作为垂直晶体管的TG 61的栅电极612可以仅包括插头612a而不包括头部612b。 此外,像在图25中示出的作为本公开的第七变形例的固态成像装置205一样,作为垂直晶体管的TG 61的栅电极612可以仅包括插头612a而不包括头部612b,并且插头612a可以插入PD 51中。 此外,本公开的成像装置不限于检测可见光的光量分布并获得可见光的光量分布作为图像的成像装置,而是可以是获得接收到的红外光、X射线、粒子等的量的分布作为图像的成像装置。 如上所述,根据作为本公开的实施方案的固态成像装置和电子设备,该固态成像装置和电子设备适于像素的高集成化。需要注意的是,本公开的效果不限于此,并且可以是下面描述的任意效果。此外,本技术可以具有以下配置。 (1)一种固态成像装置,包括: 半导体层; 光电转换器,其设置在所述半导体层中并通过光电转换生成与接收到的光量相对应的电荷; 存储电容器,其设置在所述半导体层上并包括具有第一电膜厚度的第一绝缘膜;和 第一晶体管,其设置在所述半导体层上并包括具有大于所述第一电膜厚度的第二电膜厚度的第二绝缘膜。 (2)根据(1)所述的固态成像装置,进一步地包括第二晶体管,所述第二晶体管包括具有小于所述第二电膜厚度的第三电膜厚度的第三绝缘膜。 (3)根据(2)所述的固态成像装置,其中所述第二晶体管包括放大晶体管,并且所述第三绝缘膜包括所述放大晶体管的栅极绝缘膜。 (4)根据(1)到(3)中任一项所述的固态成像装置,其中所述存储电容器层叠于在所述半导体层的厚度方向上与所述光电转换器重叠的位置处。 (5)根据(4)所述的固态成像装置,其中 所述第一晶体管包括垂直晶体管,所述垂直晶体管包括沿所述半导体层的厚度方向延伸的栅电极作为第二导电层,并且 所述第二绝缘膜包括所述垂直晶体管的栅极绝缘膜。 (6)根据(5)所述的固态成像装置,其中所述第二绝缘膜的最小物理膜厚度大于所述第一绝缘膜的最大物理膜厚度。 (7)根据(5)或者(6)所述的固态成像装置,其中 所述垂直晶体管的栅电极包括插入形成在所述半导体层中并沿厚度方向延伸的沟槽中的插头,并且 所述沟槽具有完全被所述第二绝缘膜覆盖的壁面和底面。 (8)根据(1)到(7)中任一项所述的固态成像装置,其中所述存储电容器包括MOS电容器。 (9)根据(8)所述的固态成像装置,其中所述MOS电容器为平坦型。 (10)根据(8)所述的固态成像装置,其中所述MOS电容器为沟槽型。 (11)根据(5)到(10)中任一项所述的固态成像装置,其中所述存储电容器存储由所述光电转换器生成的所述电荷。 (12)根据(1)到(11)中任一项所述的固态成像装置,进一步地包括设置在所述半导体层中以与包括所述光电转换器和所述存储电容器的像素相邻布置的相邻像素,其中 所述相邻像素包括通过光电转换生成与接收到的光量相对应的电荷的相邻光电转换器,并且 所述存储电容器在所述半导体层的面内方向上跨越所述光电转换器和所述相邻光电转换器二者设置。 (13)根据(12)所述的固态成像装置,其中所述存储电容器存储由所述光电转换器生成的所述电荷,并且也存储由所述相邻光电转换器生成的所述电荷。 (14)根据(12)或者(13)所述的固态成像装置,其中所述光电转换器的灵敏度高于所述相邻光电转换器的灵敏度。 (15)根据(1)到(11)中任一项所述的固态成像装置,进一步地包括设置在所述半导体层中以与包括所述光电转换器和所述存储电容器的像素相邻布置的相邻像素,其中 所述相邻像素包括通过光电转换生成与接收到的光量相对应的电荷的相邻光电转换器,并且 所述存储电容器存储由所述相邻光电转换器生成的所述电荷。 (16)根据(1)到(15)中任一项所述的固态成像装置,其中所述第一晶体管包括将所述电荷从所述光电转换器传输到传输目的地的传输晶体管。 (17)根据(16)所述的固态成像装置,进一步地包括作为所述传输目的地的电荷电压转换器,所述电荷电压转换器设置在所述半导体层中并且将由所述光电转换器生成的所述电荷转换成电压。 (18)根据(17)所述的固态成像装置,其中所述存储电容器连接到所述电荷电压转换器。 (19)根据(17)或者(18)所述的固态成像装置,其中所述存储电容器包括作为所述传输目的地的电荷保持部,所述电荷保持部设置在所述光电转换器和所述电荷电压转换器之间,并在将由所述光电转换器生成的所述电荷传输到所述电荷电压转换器之前暂时保持所述电荷。 (20)根据(17)到(19)中任一项所述的固态成像装置,进一步地包括开关部,所述开关部设置在所述存储电容器和所述电荷电压转换器之间,并执行所述存储电容器与所述电荷电压转换器之间的电连接以及所述存储电容器与所述电荷电压转换器之间的电断开。 (21)根据(1)到(20)中任一项所述的固态成像装置,其中所述第一绝缘膜的第一介电常数高于所述第二绝缘膜的第二介电常数。 (22)根据(1)到(21)中任一项所述的固态成像装置,其中所述第一绝缘膜的第一物理膜厚度小于所述第二绝缘膜的第二物理膜厚度。 (23)一种固态成像装置,包括: 半导体层; 光电转换器,其设置在所述半导体层中并通过光电转换生成与接收到的光量相对应的电荷; 存储电容器,其设置在所述半导体层上并包括具有第一介电强度电压的第一绝缘膜;和 第一晶体管,其设置在所述半导体层上并包括具有比所述第一介电强度电压高的第二介电强度电压的第二绝缘膜。 (24)一种设置有固态成像装置的电子设备,所述固态成像装置包括: 半导体层; 光电转换器,其设置在所述半导体层中并通过光电转换生成与接收到的光量相对应的电荷; 存储电容器,其设置在所述半导体层上并包括具有第一电膜厚度的第一绝缘膜;和 第一晶体管,其设置在所述半导体层上并包括具有大于所述第一电膜厚度的第二电膜厚度的第二绝缘膜。 本申请要求于2018年11月19日向日本专利局提交的日本在先专利申请第JP2018-216342号和于2019年11月15日向日本专利局提交的日本在先专利申请第JP2019-206785号的权益,其全部内容通过引用的方式并入本文。 本领域技术人员应当理解的是,在所附权利要求或者其等同物的范围内,可以根据设计要求和其他因素进行各种变形、组合、次组合和改变。

- 固态成像元件、固态成像装置、电子设备以及固态成像元件的制造方法

- 固态成像装置、固态成像装置的制造方法和电子设备