硫族化物材料的保形无损伤封装

文献发布时间:2023-06-19 11:27:38

通过引用并入

PCT申请表作为本申请的一部分与本说明书同时提交。在同时提交的PCT申请表中所标识的本申请要求享有其权益或优先权的每个申请均通过引用全文并入本文且用于所有目的。

背景技术

半导体装置制造涉及形成内存堆栈,内存堆栈通常对于氧化与水气灵敏且可能无法耐受高温操作或暴露于能量物质。因此,在后续工艺之前内存堆栈通常受到封装。然而,沉积封装层的一些方法可能会损伤处理室的组件、或可能会损伤衬底材料。此外,一些技术可能无法形成充分薄与密封的层。

这里提供的背景描述是为了总体呈现本公开的背景的目的。当前指定的发明人的工作在其在此背景技术部分以及在提交申请时不能确定为现有技术的说明书的各方面中描述的范围内既不明确也不暗示地承认是针对本公开的现有技术。

发明内容

本文中提供了半导体衬底的处理方法。一方面涉及包含下列步骤的方法:提供包含一个或更多个暴露的硫族化物材料层的衬底;通过将所述一个或更多个暴露的硫族化物材料层暴露于脉冲式无卤素等离子体以沉积第一硅氮化物层;以及在沉积所述第一硅氮化物层之后,通过使用交替的含卤素含硅前体与含氮反应物的脉冲进行的原子层沉积在所述第一硅氮化物层上沉积第二硅氮化物层。

在多种实施方案中,所述第一硅氮化物层是利用脉冲等离子体式等离子体增强化学气相沉积来沉积的。

在一些实施方案中,在沉积所述第二硅氮化物层期间的所述含氮反应物的所述脉冲包含有氮气无氢气的脉冲与有氢气无氮气的脉冲。在多种实施方案中,在产生等离子体期间脉冲化所述含氮反应物。在一些实施方案中,在沉积所述第二硅氮化物层期间所述含氮反应物的所述脉冲包含有氮等离子体无氢的脉冲与有氢等离子体无氮的脉冲。

在一些实施方案中,在将所述第二硅氮化物层沉积至所述一个或更多个暴露的硫族化物材料层上方时,所述第一硅氮化物层防止所述一个或更多个暴露的硫族化物材料层受到损伤。

可以在所述一个或更多个暴露的硫族化物材料层的侧壁上将所述第一硅氮化物层沉积至介于约

在多种实施方案中,在包含硅烷前体与氨的环境中点燃所述脉冲式无卤素等离子体。例如,可以以含氮的混合物将所述硅烷前体导入至所述硅烷前体与氨环境。在一些实施方案中,在所述混合物中所述硅烷前体比氮的比值至少为约30:1。可以以含氢的混合物将氨导入所述硅烷前体与氨环境。在所述混合物中氨比氢的比值可至少为约30:1。

在多种实施方案中,在介于约5%至约20%的工作周期下脉冲化所述无卤素等离子体。

在一些实施方案中,在0W与每片衬底介于约150W至约250W的等离子体功率之间脉冲化所述无卤素等离子体。

在一些实施方案中,所述一个或更多个暴露的硫族化物材料层为双向(ovonic)阈值切换装置的一部分。

所述一个或更多个暴露的硫族化物材料层可以是相变装置的一部分。

在多种实施方案中,所述方法还包含,在沉积所述第一硅氮化物层之后并且在沉积所述第二硅氮化物层之前,将所述第一硅氮化物层暴露于后处理的等离子体以致密化所述第一硅氮化物层。

在一些实施方案中,所述第一硅氮化物层与所述第二硅氮化物层中的至少一者是在低于约250℃的衬底温度下沉积的。

所述含氮反应物可为无氢的。在一些实施方案中,所述含卤素的含硅前体包含碘、溴、或其组合。

在一些实施方案中,所述方法还包含,在沉积所述第一硅氮化物层之前,蚀刻包含所述一个或更多个暴露的硫族化物材料层的所述衬底,由此在不破坏真空的情况下进行所述蚀刻与所述第一硅氮化物层的所述沉积。

在一些实施方案中,在不破坏真空的情况下进行所述第一硅氮化物层的所述沉积与所述第二硅氮化物层的所述沉积。

另一方面涉及一种衬底处理方法,所述方法包含下列步骤:提供包含一个或更多个暴露的硫族化物材料层的衬底;通过下述方式在所述硫族化物材料上方形成封装双层,所述封装双层包含具有第一密度的第一硅氮化物层与具有第二密度的第二硅氮化物层:直接在所述一个或更多个暴露的硫族化物材料层上沉积具有所述第一密度的所述第一硅氮化物层;以及在具有所述第一密度的所述第一硅氮化物层上方沉积具有所述第二密度的所述第二硅氮化物层,其中所述第一密度小于所述第二密度,以及其中所述第一硅氮化物层位于所述一个或更多个暴露的硫族化物材料层与所述第二硅氮化物层之间。

在一些实施方案中,在将所述第二硅氮化物层沉积至所述一个或更多个暴露的硫族化物材料层上方时,所述第一硅氮化物层防止所述一个或更多个暴露的硫族化物材料层受到损伤。

在多种实施方案中,在所述一个或更多个暴露的硫族化物材料层的侧壁上,所述第一硅氮化物层沉积至介于约

所述第一硅氮化物层可利用脉冲等离子体式等离子体增强化学气相沉积进行沉积。

在一些实施方案中,所述第一硅氮化物层通过将所述一个或更多个暴露的硫族化物材料层暴露于脉冲式等离子体进行沉积。可以在无卤素的硅烷前体与氨的环境中点燃所述脉冲式等离子体。

在一些实施方案中,所述第一密度小于约2.5g/cm

在一些实施方案中,所述第二密度大于约2.6g/cm

在多种实施方案中,所述方法还包含,在沉积所述第一硅氮化物层之后且在沉积所述第二硅氮化物层之前,将所述第一硅氮化物层暴露于后处理的等离子体以将所述第一硅氮化物层致密化至介于所述第一密度与所述第二密度之间的密度。

在一些实施方案中,将所述第一硅氮化物层暴露于所述后处理的等离子体包含在氮与氦存在的情况下点燃所述后处理的等离子体持续介于约30秒至约60秒的持续时间。

可在比用于沉积所述第一硅氮化物层的等离子体功率大的等离子体功率下点燃所述后处理的等离子体。

可在具有比用于沉积所述第一硅氮化物层的室压强小的室压强的室中点燃所述后处理的等离子体。

在一些实施方案中,利用一或多个循环沉积所述第二硅氮化物层,每一所述循环包含含硅前体的脉冲、有氮等离子体无氢的脉冲、以及有氢等离子体无氮的脉冲。

在一些实施方案中,所述方法还包含,在沉积所述第一硅氮化物层之前,蚀刻包含所述一个或更多个暴露的硫族化物材料层的所述衬底,由此在不破坏真空的情况下进行所述蚀刻与所述第一硅氮化物层的所述沉积。

在一些实施方案中,在不破坏真空的情况下进行所述第一硅氮化物层的所述沉积与所述第二硅氮化物层的所述沉积。

另一方面涉及一种用于处理衬底方法,所述方法包含:蚀刻包含一个或更多个暴露的硫族化物材料层的衬底;在蚀刻所述衬底之后,在不破坏真空的情况下在所述一个或更多个暴露的硫族化物材料层上方形成封装双层。

所述方法还可以包含在所述蚀刻与所述封装双层的所述形成之间清洁所述衬底。

在一些实施方案中,在相同的设备中进行所述清理、所述蚀刻、以及所述封装双层的所述形成。

在一些实施方案中,所述封装双层是在介于约7Torr至约10Torr的室压强下形成。

针对上述的任何实施方案,所述封装双层可在低于250℃的衬底温度下形成。

在一些实施方案中,所述衬底被提供至具有介于约7Torr至约10Torr之间的室压强的处理室中。

另一方面涉及一种用于处理衬底的设备,所述设备包含:蚀刻模块,其用于蚀刻具有一个或更多个硫族化物材料层的半导体衬底,以在所述半导体衬底上形成具有堆栈形式的硫族化物材料的图案;沉积模块,其用于利用脉冲等离子体式等离子体增强化学气相沉积与等离子体增强原子层沉积在所述半导体衬底上沉积封装双层;以及晶片传送工具,其用于在不破坏真空的情况下在所述蚀刻模块与所述沉积模块之间传送所述半导体衬底。

所述设备还包含:清理模块,其用于清理所述半导体衬底。在一些实施方案中,所述设备还包含:介于所述蚀刻模块与所述沉积模块之间的微传送站。在一些实施方案中,所述蚀刻模块被配置成处于与所述沉积模块的压强不同的压强下。

另一方面涉及一种内存装置,其包含:内存堆栈,其包含硫族化物材料;以及第一硅氮化物层,其沉积在所述内存堆栈上方且封装所述硫族化物材料,所述第一硅氮化物层通过暴露于在无卤素的硅烷与含氮环境中点燃的等离子体的脉冲来沉积;以及第二硅氮化物层,其沉积在所述第一硅氮化物层上方,所述第二硅氮化物层是利用原子层沉积通过交替暴露于含卤素的硅前体与第二反应物来沉积的。

另一方面涉及一种内存装置,其包含:内存堆栈,其包含硫族化物材料;以及第一硅氮化物层,其在所述内存堆栈上方沉积至在所述内存堆栈的侧壁上的厚度介于约

在一些实施方案中,所述硫族化物材料为硫、硒、碲及其组合中的任一者。在一些实施方案中,所述第一硅氮化物层通过脉冲等离子体式等离子体增强化学气相沉积进行沉积。在一些实施方案中,所述第二硅氮化物层通过等离子体增强原子层沉积进行沉积。

这些和其它方面将在下面参照相关附图进一步说明。

附图说明

图1是示例性衬底的示意图。

图2A-2C是描述根据某些所公开的实施方案执行的示例性方法的操作的工艺流程图。

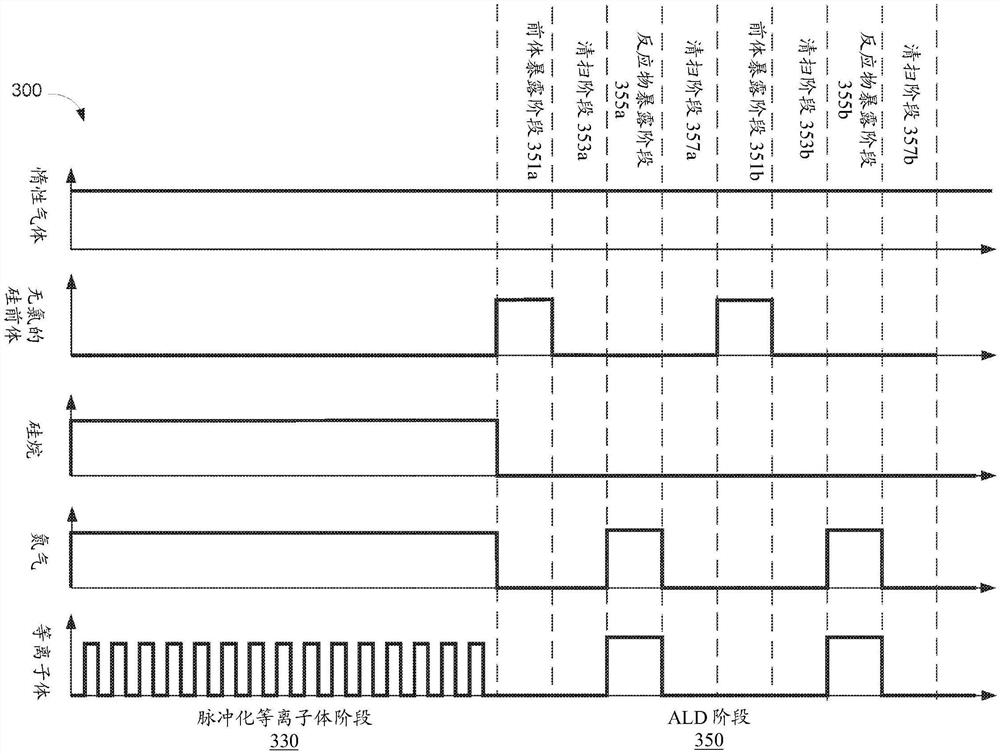

图3是显示根据某些所公开的实施方案所述的方法中的循环的实施例的时序图。

图4是用于执行所公开的实施方案的示例性处理室的示意图。

图5是用于执行所公开的实施方案的示例性处理工具的示意图。

图6是描绘根据某些公开的实施方案进行的实验中利用变化的工作周期沉积的硅氮化物膜的湿蚀刻率比的图形。

具体实施方式

在下面的描述中,阐述了许多具体细节以提供对所呈现的实施方案的透彻理解。在没有这些具体细节中的一些或所有的情形下可以实施所公开的实施方案。在其它情形下,未详细描述公知的处理操作,以防止不必要地模糊所公开的实施方案。虽然将结合具体的实施方案描述所公开的实施方案,但是应理解的是并不意在限制所公开的实施方案。

半导体制造工艺通常涉及沉积硅氮化物材料。在一示例中,在半导体装置制造中可使用硅氮化物作为扩散阻挡层、栅极绝缘体、侧壁间隔件以及封装层。保形的硅氮化物层也可用于其他应用中。例如,在制造内存结构期间可使用硅氮化物。一些内存结构包含用于位存储的金属氧化物材料。然而,当发展先进内存结构以得到更小的装置尺寸并改善效率时,遇到了新的挑战。先进的内存结构(如磁阻随机存取内存与相变化随机存取内存(PCRAM))依赖于用于位存储的新材料(非金属氧化物)。在一些内存装置中,双向阀值切换(OTS)硫族化物存在于堆栈上。OTS硫族化物对于各种气体及等离子体灵敏。例如,在PCRAM的情况中,金属硫族化物的相会决定位状态。一些示例性的硫族化物包含硫(S)、硒(Se)以及碲(Te)。这些新材料对于空气与湿气灵敏且可能需要封装层。当与适当的准金属离子如锗(Ge)、硒(Sb)等结合时,这些硫族化物会形成相变层。在一些情况中,内存装置包含锗锑碲(GST)材料。如果受到损伤,相变层可能会无法改变其相。相变层还对光灵敏。为了防止对相变层的任何损伤,可在相变层上方沉积保形的硅氮化物内存封装层。内存封装层具有极少甚至是没有其他化合物的污染且是在低温下沉积以防止损伤装置。相变化记忆体的有效封装涉及在低温下沉积高保形性、高密度的硅氮化物,以使经沉积的硅氮化物薄膜保护灵敏的硫族化物材料不受湿气和/或等离子体蚀刻化学品的攻击。此外,封装沉积工艺以及封装层本身不会与硫族化物材料反应、或产生挥发性副产物、或对下方材料造成组成改变。经蚀刻及清理的硫族化物材料还对氧灵敏,由于经氧化的硫族化物材料也会失去其待用作有效的PCRAM的特性。

虽然基于卤化物的原子层沉积具有充分反应性而能在低温如低于250℃的温度下形成高度保形的硅氮化物且不在OTS材料上形成挥发性的硫族氢化物,但基于卤化物的沉积可与GST硫族化物材料反应而形成钝化层,由此使一些GST硫族化物材料退化。

图1显示包含氧化物层101的衬底100。衬底100还包含钨层103、碳层105、硫族化物层107、第二碳层115、第二硫族化物层117、第三碳层125以及氮化物层109。

在一些制造工艺中,在衬底100的蚀刻与清理工艺后,可通过等离子体增强原子层沉积在衬底100上方沉积硅氮化物封装层(未显示)。然而,在一些膜生长的初始阶段中,钨层103、碳层105、硫族化物层107、第二碳层115以及第二硫族化物层117的暴露表面可能会受到损伤。例如,针对20个循环的硅氮化物沉积且每一循环中等离子体开启约60秒导致20分钟的等离子体暴露,可沉积

如图1中所示,如果使用含氯的硅前体在衬底上沉积封装层,则当用第二反应物点燃等离子体持续足以沉积具有期望厚度的封装层的持续时间时所产生的氯和/或氢自由基可能会造成氯化氢的形成,使得氯与铝、锗、或锑、或其他处理室材料金属(包含铁或铜)反应。这些材料(如氯化铝(AlCl

类似地,从含氮反应物(例如氨)所产生的等离子体可形成也会蚀刻硫族化物的自由氢离子、自由基以及其他等离子体物质。例如,氢等离子体可与碲或硒反应而分别形成碲化氢(H

在一些实施方案中,在等离子体增强原子层沉积工艺(PEALD)期间含碘硅烷或含溴硅烷与氮气反应,以在低温下形成高保形性硅氮化物且不形成挥发性氢化物。然而,虽然此类硅氮化物封装层可在低温(如低于约250℃)下沉积并且获得极高的阶梯覆盖率(高于约95%)且不形成挥发性的具硫族化物的副产物,但在反应物与更灵敏的GST相材料之间仍有一些反应。

本文中提供了包含阻挡层的多层封装层的形成方法,该阻挡层用于防止硫族化物材料与用于保形沉积硅氮化物层的含卤素的硅前体反应。例如,阻挡层防止二碘硅烷与硫族化物材料反应。在一些公开的实施方案中,阻挡层薄到足以作为能防止含卤素的硅前体与硫族化物材料之间发生反应的阻挡层,同时通过PEALD沉积在阻挡层上方的硅氮化物材料提供用于有效封装硫族化物材料的充分密封性、阶梯覆盖率以及质量。

在多种实施方案中,沉积封装双层。双层包含与硫族化物材料直接接触的阻挡层,由此分离硫族化物材料与保形沉积的硅氮化物材料。虽然双层可指两层材料,但应理解,也可沉积两个以上的层。本文中所述的阻挡层通过脉冲等离子体式等离子体增强化学气相沉积(PP-PECVD)进行沉积。在多种实施方案中,在沉积阻挡层之后,剩余的封装层由PEALD进行沉积。在多种实施方案中,PP-PECVD层的厚度对PEALD层的厚度的比值介于约1:5至约1:10之间。

某些公开的实施方案是在低于会导致被处理的衬底的硫族化物材料退化的温度下进行。例如,在一些实施方案中,某些公开的实施方案在低于约300℃、或低于约250℃的衬底温度下进行。应理解,本文中所述的衬底温度是指支撑受到处理的半导体衬底的基座、或衬底支撑件、或衬底支架被设定的温度。在一些实施方案中,在一些衬底温度下的操作涉及在处理前进行的“温度浸泡”。在“温度浸泡”期间,衬底被加热至工艺温度,在工艺温度处衬底将会经历本文中所述的各种操作。例如,所公开的方法可在低于约300℃,例如约250℃或约200℃、或介于约200℃至250℃之间、或低于约200℃、或低至约150℃、或低至100℃的温度下进行。因此,在一些实施方案中,将衬底暴露于温度浸泡以使在处理室中支撑衬底的基座可被设定至例如约250℃的温度,以将衬底加热至工艺温度并在处理前稳定该温度。

某些公开的实施方案适合用于在不损伤OTS与GST硫族化物堆栈中的裸露硫族化物材料的情况(如不形成具有硫族化物的挥发性副产物)下针对OTS与GST硫族化物堆栈形成有效的封装双层,并且同时维持至少约90%的高阶梯覆盖率以及至少约2.4g/cm

在多种实施方案中,双层为保形的。膜的保形性可通过阶梯覆盖率来进行测量。本文中所使用的“阶梯覆盖率”通过下列方式计算:侧壁上的沉积膜的平均厚度除以特征的上部处的沉积膜的平均厚度,然后将其乘以100以获得百分比。

虽然PP-PECVD层本身、或PEALD层本身可能不必然是保形的,但包含两层的双层可能是保形的。还应理解,PEALD层本身也可能是保形的,但如果单独沉积而不沉积PP-PECVD阻挡层,则可能会导致硫族化物与封装层的界面处的硫族化物材料的反应或退化。

在一些实施方案中,PP-PECVD层具有一些保形性,例如具有至少约50%的阶梯覆盖率。在一些实施方案中,以保形方式沉积PEALD层以使阶梯覆盖率至少为约70%、或至少为约90%、或至少为约95%。包含阻挡层与PEALD硅氮化物层两者的封装双层可达到高于约70%、或高于约90%、或介于约70%至约90%之间的阶梯覆盖率。

在一些实施方案中,经沉积的PP-PECVD或PEALD层或两者都经历后处理以改善双层的保形性。后处理工艺操作包含周期性地暴露于惰性气体并且在暴露于惰性气体期间点燃等离子体。例如,在一些实施方案中,在沉积封装层之后,可将封装层暴露于惰性气体等离子体(例如但不限于氩、氦、氮以及其组合)介于约10秒至约50秒的持续时间。在多种实施方案中,可通过在(1)PP-PECVD沉积和(2)暴露至惰性气体与等离子体两者之间循环而沉积封装层。

虽然本文中所述的示例涉及沉积硅氮化物封装层,但应理解,在一些实施方案中,针对阻挡层与PEALD可沉积其他材料。例如,本文中所述的封装双层可包含IV族元素的氮化物或碳化物,其中的任何一者都可以是经掺杂(如以氧掺杂)的或未经掺杂的。在多种实施方案中,封装层可为下列化学物中的任何一者或其组合中的任何一者:硅氮化物(SiN)、硅碳化物(SiC)、掺杂氧的硅碳化物(SiCO)、锗氮化物(GeN)、锗碳化物(GeC)以及掺杂氧的锗碳化物(GeCO)。包含锗的封装双层的有效性尤其令人惊讶,因为锗为半导体并且通常利用锗烷(GeH

所公开的实施方案可适合用于沉积具有各种厚度的封装层。在多种实施方案中,PP-PECVD层可沉积至介于约

图2A提供了显示根据某些公开的实施方案进行的方法的操作的工艺流程图。图2A的操作可在低于约300℃、或低于约250℃、或低于约150℃的温度下进行。

在图2A的操作230与250期间可使惰性气体流动。在多种实施方案中,使用惰性气体作为载气。示例性的载气包含氩气、氦气以及氖气。在一些实施方案中,可使用含氢载气。在一些实施方案中,可不使用含氢载气以减少双层中的含氢量。在一些实施方案中,在一些操作中使用载气作为清扫气体。在一些实施方案中,转移载气。可提供惰性气体以协助对处理室的压强和/或温度控制、液体反应物的蒸发、反应物和/或用于从处理室移除处理气体的扫除气体的更快速输送和/或处理室管线配置。

在操作210中,将衬底提供至处理室。下面参考图4与5更进一步说明示例性处理室。所提供的衬底可以是硅晶片,例如200-mm晶片、300-mm晶片、或450-mm晶片,其包含具有一或多层材料(例如介电材料、导电材料、或半导电材料)沉积于其上的晶片。下层的非限制性示例包含介电层与导电层,例如硅氧化物、硅氮化物、硅碳化物、金属氧化物、金属氮化物、金属碳化物、和金属层。

衬底包含经暴露的双向阈值切换(OTS)材料、或相变材料、或两者。衬底包含经暴露的硫族化物材料。例如,在一些实施方案中,衬底包含膜的堆栈,膜中的一些是硫族化物材料,其中衬底的经暴露表面包含硫族化物材料。硫族化物材料可包含硫、硒和碲。在多种实施方案中,衬底包含OTS材料和/或相变材料,其可包含下列元素中的任一或多者:砷、锗、锑、碲和硒。

在一些实施方案中,衬底包含堆栈如磁性隧道结。在一些实施方案中,衬底包含两个或更多个堆栈,堆栈中的每一个包含层,如图1中所示的层。堆栈之间的空间可能是窄的,使得堆栈之间的深宽比可介于约1:1至约60:1之间、或大于约1.5:1、或大于约4:1、或介于约1.5:1至60:1之间、或介于约1.5:1至40:1之间、或介于约1.5:1至20:1之间,例如约5:1。在一些实施方案中,堆栈之间的空间可被称为负的“特征”。在一些实施方案中,每一堆栈可被称为是正的“特征”。在一些实施方案中,所提供的衬底被图案化为具有正特征,每一正特征包含膜的堆栈,膜中的一些包含硫族化物材料,由此正特征在衬底上彼此分隔。在特征中每一膜堆栈上的硫族化物材料会被暴露。

一种堆栈可包含非挥发生的铁磁材料,例如(Co)、铁(Fe)、锰(Mn)、镍(Ni)、铂(Pt)、钯(Pd)、钌(Ru)以及其组合(如CoFe),且在两层铁磁材料之间可包含介电层,例如镁氧化物(MgO)层。一些堆栈材料可包含上述所列的铁磁层的任一者与硼的组合,例如CoFeB。

在操作230中,通过PP-PECVD将阻挡层沉积在OTS和/或相变材料上。在一些实施方案中,PP-PECVD阻挡层被沉积在OTS与相变材料两者上。在一些整合操作,例如蚀刻、清理以及其他操作中,在单一操作中只有OTS或相变材料受到暴露,但在一些情况中,在单一操作期间OTS与相变材料两者都同时受到暴露。

OTS膜可以与GST膜具有相同的元素,但是具有不同的比值以及额外的元素,例如砷与硅。在一些实施方案中,OTS可以是非晶膜。GST可以是具有特定化学配比的化合物且可在非晶材料与晶体结构之间切换。

在多种实施方案中,阻挡层被直接沉积在OTS和/或相变材料上,其中在暴露的OTS和/或相变材料与阻挡层之间并无任何其他膜层。

在多种实施方案中,通过PP-PECVD将阻挡层直接沉积在衬底的暴露的硫族化物表面上。在许多实施方案中,阻挡层直接沉积在暴露的硫族化物表面上且阻挡层与暴露的硫族化物表面之间并无任何中间层。

阻挡层通过PP-PECVD沉积。阻挡层的PP-PECVD的相关进一步解释与示例在下文参考图2B说明。

在多种实施方案中,在操作230中沉积的阻挡层可薄至约

在操作230中所沉积的阻挡层可以具有至少约50%的保形性。虽然在操作230中所沉积的阻挡层非常薄并且可能不是非常保形的,但阻挡层仍可提供阻挡以使在操作250中的后续沉积不会形成挥发性的副产物而使硫族化物材料暴露。在多种实施方案中,阻挡层的有效性通过下列方式判断:利用X射线荧光(XRF)进行测试的实验,判断出有多少硫族化物材料已挥发。在一些实施方案中期望的元素损失取决于硫族化物材料的元素。在一些实施方案中,利用某些公开的实施方案所形成的阻挡层能够达到少于约2%的元素损失,相对地,在不具有PP-PECVD下层的一些情况中达到高于5%的元素损失。在多种实施方案中,利用旋转浸泡清理设备进行侧壁着陆插塞触点的清理装饰测试,在横截面之后以穿透式电子显微镜(TEM)进行硫族化物材料的视觉测试。

在操作230之后,可进行选择性的后处理,其可在不破坏真空的情况下进行、或可在相同的处理室中进行、或可在不同的处理室中进行。后处理可涉及将所沉积的阻挡层暴露于被等离子体点燃的惰性气体。示例性的惰性气体包含氮气、氨以及稀有气体,如氦气与氩气。在一些实施方案中,尤其使用富氦的惰性气体。例如,在一些实施方案中,可使用包含氦与氮的惰性气体混合物。可根据待沉积的膜的类型以及在沉积工艺期间所使用的反应物来选择气体。后处理气体可包含纯氮气、纯氨、氮/氨混合物、纯氦气、氩/氦混合物以及其组合。也可使用其他稀有气体。在沉积阻挡层之后,可在相同的处理室中、或在不破坏真空的情况下使用惰性气体等离子体的后处理。即,在一些实施方案中,衬底可在处理室中由此沉积阻挡层,当衬底仍在相同处理室中时将衬底暴露于用于后处理的惰性气体等离子体。在一些实施方案中,衬底可在多站室中的处理站中,由此在第一站中于衬底上沉积阻挡层、在不破坏真空的情况下将衬底传送至第二站、然后在用于后处理的第二站中将衬底暴露于惰性气体等离子体。

在操作250中,以原子层沉积(ALD)在阻挡层上方沉积无氯保形封装层。在一些实施方案中,保形封装层是在阻挡层沉积之后沉积以形成多层封装层。有鉴于氯的腐蚀性,在沉积期间使用无氯反应物以防止形成挥发性的金属氯化物。PP-PECVD阻挡层并非完全无孔隙的,但能提供充分的阻挡以最小化其他卤素所造成的损伤。在多种实施方案中,利用PEALD进行沉积。下面参考图2C说明更进一步的实施方案。在一些实施方案中,在无氯保形封装层的沉积期间,等离子体是选择性的。如果在无氯保形封装层的沉积期间使用二碘硅烷作为含硅前体,则等离子体可能不是选择性的。一些含碘硅烷前体可以在无等离子体的情况下沉积,但在一些实施方案中,还包含对沉积层进行后处理以增大沉积层的密度。

在操作250中沉积的PEALD封装层的厚度可大于在操作230中所沉积的PP-PECVD封装层的厚度。在一些实施方案中,在充足的循环中沉积PEALD层以沉积至膜的期望厚度。可将任何合适数量的沉积循环包含在PEALD工艺中以沉积期望厚度的硅氮化物膜。例如,利用公开的实施方案可进行约50个沉积循环以在衬底上沉积膜。在一些实施方案中,在用于制造内存装置的膜堆栈上方的侧壁上,所沉积的硅氮化物膜的厚度可大于约

在操作250中所沉积的封装层可具有至少约95%、或约100%、或100%的阶梯覆盖率。在一些实施方案中,具有含硫族化物材料的材料堆栈的衬底在堆栈之间的深宽比为约5:1,操作250可涉及利用含碘前体与氨沉积阶梯覆盖率至少为约95%的硅氮化物。

在多种实施方案中,在真空下执行操作230与250。可在相同的处理室中、或在不破坏真空的情况下执行操作230与250。即,在一些实施方案中,衬底可以在处理室中,由此以PP-PECVD沉积阻挡层,同时,衬底位于相同处理室中,通过PEALD沉积封装层。在一些实施方案中,衬底可以位于多站室中的处理站中,由此在第一站中将PP-PECVD阻挡层沉积至衬底上、在不破坏真空的情况下将衬底传送至第二站以及在第二站中将PEALD封装层沉积至衬底上。

图2B提供了执行图2A的操作230的示例。在操作231中,连续地将衬底暴露于沉积前体与反应物。例如,在多种实施方案中,当在低于约300℃的温度下加热衬底时,连续的沉积前体与反应物流可以流至容纳衬底的处理室。

根据待沉积的封装层的类型,可利用各种反应物来沉积封装层。例如,可通过将衬底暴露于含硅前体与含氮反应物而执行硅氮化物封装层的沉积。

在许多实施方案中,沉积前体是含硅前体。在本文中所述的方法中使用的一般的含硅前体可具有以下结构:

其中R

在多种实施方案中,使用无卤素的含硅前体。例如,在一些实施方案中,可以使用氨硅烷或乙硅烷。不受特定理论的约束,相信将一些硫族化物材料暴露于含卤素的含硅前体可形成减少硫族化物材料在内存装置中起作用的能力的钝化层。

虽然在操作230期间可使用各种含硅前体,但针对具有充分扩散特性而能防止下伏的硫族化物材料暴露于在后续操作中所使用的沉积化学品的阻挡膜的沉积而言,聚硅烷(H

在一些实施方案中,含硅前体为烷氧基硅烷。可使用的烷氧基硅烷包含但不限于下列项:

H

H

含硅前体的示例包含:甲基硅烷;三甲基硅烷(3MS);乙基硅烷、丁硅烷;五硅烷;八硅烷;七硅烷;六硅烷;环丁硅烷;环庚硅烷;环己硅烷;环辛硅烷;环戊硅烷1,4-二氧杂-2,3,5,6四硅环己烷;二乙氧基甲基硅烷(DEMS);二乙氧基硅烷(DES);二甲氧基甲基硅烷;二甲氧基硅烷(DMOS);甲基-二乙氧基硅烷(MDES);甲基-二甲氧基硅烷(MDMS);八甲氧基十二硅氧烷(OMODDS);叔丁氧基乙硅烷;四甲基环四硅氧烷(TMCTS);四氧甲基环四硅氧烷(TOMCTS);三乙氧基硅烷(TES);三乙氧基硅氧烷(TRIES);以及三甲氧基硅烷(TMS或TriMOS)。

在一些实施方案中,含硅前体可以是具有氢原子的氨基硅烷,例如双二乙基氨基硅烷、二异丙基氨基硅烷、双(叔丁基氨基)硅烷(BTBAS)、或三(二甲基氨基)硅烷。氨基硅烷前体包含但不限于下列项:H

在多种实施方案中,使含硅前体在介于约10sccm至约200sccm之间、或介于约20sccm至约70sccm之间、或介于约40sccm至约60sccm之间的流率下流动。

用于与含硅前体反应的反应物取决于待沉积的材料。例如,对于沉积硅氮化物,所使用的反应物为含氮反应物。示例性的含氮反应物包含氮气与氨气。在多种实施方案中,含氮气体不含卤素。

使含氮反应物在介于约100sccm至约300sccm之间的流率下流动。在多种实施方案中,含硅前体比含氮反应物的比值介于约25sccm至约300sccm之间、或介于约130sccm至约170sccm之间。

在一些实施方案中,在操作231期间使惰性气体流动。硅前体比惰性气体的比值可以为约100:1。

在一些实施方案中,在从处理气体源输送含硅前体、含氮反应物、或此两种气体时,可将其稀释。例如,在一些实施方案中,以氢稀释含硅前体。在使用氢作为惰性气体的实施方案中,硅前体的流率比氢的流率的比值可以为约5:1。在使用含氮气体或气体混合物作为惰性气体的实施方案中,硅前体的流率比含氮气体或气体混合物的组合流率的比值可以介于约500:1。在一些实施方案中,含氮气体混合物包含氮气与氨气。在一些实施方案中,以氢稀释含氮反应物。稀释剂可为下列气体中的任何一或多者:氢气、氩气、氦气、氖气以及氪气。

在一些实施方案中,在沉积期间可使用氨稀释剂以减少等离子体中的氢浓度以及后续被掺入沉积层中的氢。此外,进行实验比较膜中的N-H键合相比于膜中的总N-H与Si-H键合与湿式蚀刻率的关系;数据显示,通过较少量的N-H键合能达到较低的湿式蚀刻率。进行另一实验比较膜应力与湿式蚀刻率的关系;结果显示,利用高压缩应力膜可实现低湿式蚀刻率。该两实验的组合表明,低应力膜可减少湿式蚀刻率,减少湿式蚀刻率也可以通过减少膜中的N-H键合实现。通过改变所使用的氨气的量可调制N-H键合的存在。在等离子体中的氢存在可在沉积期间造成硫族化物损伤且将氢掺入沉积封装层中可导致非所期望的湿式蚀刻率。在一示例中,可使用硅烷气体流率比氨气流率的比值来减少湿式蚀刻率。例如,在一些实施方案中,硅烷气体流率比氨气流率的比值可为约1:3(针对PP-PECVD膜),相比之下,非脉冲式膜可涉及约1:8的比值。可使用湿式蚀刻率作为判断膜质量的度量标准;例如,低湿式蚀刻率膜会具有高质量。

在一些实施方案中,PP-PECVD可涉及在沉积期间导入氢。氢对增加保形性有贡献,但在使用氢的情况下,执行PP-PECVD持续短的时间以防止造成氢与硫族化物材料之间的反应。例如,脉冲可介于约0.1ms至约10ms之间,且处理气体流动与脉冲化等离子体的总时间期间少于约50秒。

在操作233中,当沉积前体与反应物正在流动时,点燃并且脉冲化等离子体。在多种实施方案中,通过开启和关闭等离子体而脉冲化等离子体,其介于0W与“开启”状态之间,“开启”状态介于约80W/衬底至约250W/衬底之间。在多种实施方案中,通过在两等离子体状态-“低功率”状态与“高功率”状态之间点燃等离子体而脉冲化等离子体,“低功率”状态是介于约125W至约250W之间或约45W/站的等离子体功率,“高功率”状态是介于约250W至约1000W之间或约200W/站的等离子体功率。

不受特定理论的约束,相信,在不使用等离子体的情况下,使用CVD的热沉积工艺会沉积具有约2.1g/cm

在一些实施方案中,沉积层可以进一步进行后处理,尤其是未使用等离子体沉积的膜可进行后处理。即,在一些实施方案中,可对热沉积层进行后处理以增大密度并改善封装层特性。一示例性的后处理利用在具有氦气与氮气的环境中点燃的等离子体以低功率(如每站约100W)处理热沉积的膜持续介于约1分钟至约8分钟之间的期间。

在多种实施方案中,在将衬底暴露于沉积前体与反应物而沉积膜时,以短脉冲使等离子体脉冲化,短脉冲例如是具有介于约0.01ms至约5ms之间、或介于约0.02ms至约5ms之间、或介于约0.05ms至约5ms之间、或介于约0.05ms至约1.9ms之间、或介于约0.5ms至约1.9ms之间的脉冲期间的脉冲。在多种实施方案中,利用介于约100Hz至约6Hz之间的脉冲式频率脉冲化等离子体。

可在下列条件下脉冲化等离子体:脉冲频率介于约2Hz至约100kHz之间,工作周期的范围从约1%至约95%之间、或约2%至约20%之间。在多种实施方案中,工作周期为约10%。在多种实施方案中,工作周期影响沉积的膜的湿式蚀刻率。较低的湿式蚀刻率导致较低的湿式蚀刻率和较高质量的硅氮化物膜。在下面参考图6更详细讨论实验。

工作周期被定义为在具有持续时间T的期间内等离子体开启的时间期间。持续时间T包含在给定时间期间内脉冲式开启(ON)或高(HIGH)时间期间(等离子体处于ON状态或HIGH功率状态的时间期间)以及等离子体关闭(OFF)或低(LOW)时间期间(等离子体处于OFF状态或LOW功率状态的时间期间)。脉冲频率应被理解为1/T。例如,针对等离子体脉冲化时间段T=100μs,频率为1/T=1/100μs或10kHz。工作周期或工作比是占在时间段T中的分数或百分比,在该分数或百分比时间段期间,等离子体处于ON状态的时间段,使得工作周期或工作比为脉冲式ON时间除以T。例如,针对等离子体脉冲化时间段T=100μs,如果脉冲ON时间为70μs(使得等离子体处于ON状态的时间段为70μs),并且脉冲OFF时间为30μs(使得等离子体处于OFF状态的时间段为30μs),则工作周期为70%。在一些实施方案中,在脉冲步骤期间最短的RF开启时间可低至约5μsec。在一些实施方案中,最短的RF关闭时间可约为5μsec。根据工作周期与频率,可执行RF开启/RF关闭脉冲的各种组合。例如,在一些实施方案中,该操作可持续进行约0.01ms至约5ms之间、或介于约0.02ms至约5ms之间、或介于约0.05ms至约5ms之间、或介于约0.05ms至约1.9ms之间、介于约0.5ms至约1.9ms之间的期间。在操作233期间,可脉冲化等离子体数百次至数千次,具体取决于总的等离子体持续期间。在一些实施方案中,较高的工作周期可减少保形性,因为较高的工作周期会造成沉积工艺变得更像CVD而非ALD。

不受特定理论的约束,相信,脉冲化等离子体所实现的条件足以形成具有至少约30%、或至少约50%的阶梯覆盖率的阻挡层。PP-PECVD层的阶梯覆盖率确定用于使侧壁上具有适当膜覆盖率的沉积厚度。例如,如果沉积层具有低阶梯覆盖率,例如低于约40%,则可以使用沉积较厚的膜来实现介于约

不受特定理论的约束,在本文中所述的PP-PECVD沉积中,相信,当在每一脉冲后关闭等离子体或等离子体处于低状态时,反应性物质以下列顺序复合:电子消失/复合、离子复合以及自由基复合。由于脉冲极短(例如等离子体开启极短的时间,然后关闭较长的时间以允许沉积),因此当关闭等离子体时,电子与离子复合,从而消除在沉积材料时离子的方向性。自由基需要较长的时间复合,故沉积主要由自由基所驱动而非由离子驱动。接着自由基能深入高深宽比的特征(1.5:1-20:1,尤其适合于大于4:1的应用)中并且沉积具有至少充分保形性以甚至在特征底部处作为硫族化物材料与PEALD封装层之间的阻挡层的膜。然而应理解,在所有的实施方案中这可能不会发生。

在多种实施方案中,在操作233期间,在约

可执行操作233,使得在介于约5秒至约50秒的期间脉冲式等离子体。即,在约5秒至约50秒的时间期间内脉冲式等离子体多次。在一些实施方案中,进行操作233直到沉积的材料具有介于约

在多种实施方案中,操作231与233形成具有低保形性(例如至少约50%或约50%)的阻挡层。然而,只要阻挡层能具有防止下伏的硫族化物材料与后续工艺中所使用的其他化学品反应的功能,可能不期望阻挡层的高保形性。

尤其不期望发现,阻挡层薄至约

在操作231与233中所沉积的阻挡层形成具有至少约2.5g/cm

在一些实施方案中,如上所述,在操作233之后可进行选择性的后处理。在一些实施方案中,进行后处理以致密化PP-PECVD阻挡层。例如,在一些实施方案中,在PP-PECVD后阻挡层的密度会低于2.0g/cm

在操作230中所沉积的PP-PECVD阻挡层的密度小于在操作250中所沉积的PEALD层的密度。PP-PECVD阻挡层的密度可小于约2.5g/cm

即,在一些实施方案中,在脉冲化等离子体之后,关闭前体与反应物流两者,并且可以使惰性气体在无处理气体(无沉积前体,例如含硅前体,也没有反应物,例如含氮反应物)的情况下流至处理室,并且点燃等离子体以利用惰性气体等离子体处理经沉积的阻挡层。在一些实施方案中可进行后处理持续介于约30秒至约60秒的持续时间。

在一些实施方案中,后处理的等离子体功率可以大于在操作230、操作250、或两者期间所使用的等离子体功率。在一些实施方案中,后处理的等离子体所在的处理室的室压强小于在操作230期间所使用的室压强。

在一些实施方案中,后处理所用的处理室与在操作230与250所使用的处理室是分离的。在一些实施方案中,后处理是在不破坏真空的情况下在操作230与250之间执行的。例如,在一些实施方案中,操作230可在第一处理室中进行、后处理可在第二处理室中进行、而操作250可在第三处理室中进行,其中三个处理室皆为相同设备的一部分。在一些实施方案中,第一处理室与第三处理室可以是相同处理室;即,在不同的处理室中进行后处理之后,可将衬底传送回第一处理室以随后执行操作250。在一些实施方案中,三个处理室皆设定为不同的室压强。室压强也可取决于针对每一处理室中的沉积与后处理所选择的化学品以及封装双层的期望特性。

现参考图2C,针对图2C所述的操作提供了在图2A的操作250中于阻挡层上方沉积无氯保形封装层的技术的一示例。图2C可包含以ALD或PEALD沉积封装层的操作。在图2C之前,在衬底上提供利用PP-PECVD所沉积的阻挡层,例如硅氮化物阻挡层,使得阻挡层与衬底上的硫族化物材料直接接触,且在图2C中所沉积的封装层直接沉积于阻挡层上且两者之间并无其他的中间层。

本文中所述的实施方案涉及ALD沉积。ALD为一种利用依序自我限制性反应而沉积薄层材料的技术。一般而言,一个ALD循环包含输送至少一种反应物并使其吸附至衬底表面的操作以及接着使已吸附的反应物与一或多种反应物反应而形成至少一部分材料层的操作。例如,硅氮化物的沉积循环可包含下列操作:(i)输送/吸附硅前体;(ii)从处理室清扫硅前体;(iii)输送含氮反应物与选择性的等离子体;以及(iv)从处理室清扫含氮气体及/或等离子体。

不同于化学气相沉积(CVD)技术,ALD工艺使用表面中介沉积反应以逐层方式沉积膜。在ALD工艺的一示例中,包含表面活性位点的群落的衬底表面被暴露于以一定剂量提供至容纳衬底的处理室的第一前体(例如含卤素的硅前体)的气相分布。该第一前体的分子吸附至衬底表面上,其包含第一前体的化学吸附的物质和/或物理吸附的分子。应理解,当如本文中所述,化合物吸附至衬底表面上时,吸附层可包含该化合物以及该化合物的衍生物。例如,含碘的硅前体的吸附层可包含含碘硅前体以及含碘硅前体的衍生物。在第一前体配料之后,接着抽空处理室以移除大部分或全部的气相的剩余第一前体,因此大部分或仅有吸附物质留下来。在一些实施方案中,可能不会完全抽空处理室。例如,可抽空处理室,使得气相第一前体的分压低到足以缓和反应。

将第二反应物(例如含氮反应物)导入处理室PPG,使得这些第二反应物分子中的一些与吸附在表面上的第一前体反应。在一些工艺中,第二前体立即与所吸附的第一前体反应。在其他实施方案中,第二反应物仅在暂时施加活化源(例如等离子体)后才反应。在一些实施方案中,在第二反应物配料期间点燃等离子体。接着再次抽空处理室以移除未受束缚的第二反应物分子。如上所述,在一些实施方案中,可能不会完全抽空处理室。可使用额外的ALD循环建立膜厚度。

在某些实施方案中,ALD第一前体配料会部分饱和衬底表面。在一些实施方案中,ALD循环的配料阶段在前体接触衬底而均匀地饱和表面前结束。一般而言,在此点处关闭或转移前体流,然后只使清扫气体流动。通过在该亚饱和域中操作,ALD工艺减少循环时间并增加产量。然而,由于前体吸附不是饱和限制性的,因此经吸附的前体的浓度在衬底表面各处可能稍微不同。在亚饱和域操作的ALD工艺的示例提供于下列文献中:2013年10月23日申请的名称为“SUB-SATURATED ATOMIC LAYER DEPOSITION AND CONFORMAL FILMDEPOSITION,”的美国专利申请No.14/061,587(现为美国专利No.9,355,839),通过引用将其所有内容包含于此。

如所述的,在一些实现方案中,ALD方法包含等离子体活化。如本文中所述,本文中所述的ALD方法及设备可以是保形膜沉积(CFD)方法,下列文献中大致上说明了这种方法:2011年4月11日所申请的名称为“PLASMA ACTIVATED CONFORMAL FILM DEPOSITION,”的美国专利申请No.13/084,399(现为美国专利No.8,728,956),以及于2011年4月11日申请的名称为“SILICON NITRIDE FILMS AND METHODS,”的美国专利申请No.13/084,305,将其所有内容通过引用合并于此。

参考回图2C,在多种实施方案中,操作251-257构成一ALD循环。虽然图2C与下列图2C的叙述说明利用含碘及含溴硅前体以PEALD沉积硅氮化物封装层,但应理解,在一些实施方案中,在这些操作中所沉积的封装层可利用不同的前体与反应物来沉积,并且在一些情况中可不涉及点燃等离子体。

参考图2C,在操作251中,将衬底暴露于含卤素的硅前体,使得硅前体吸附至衬底表面上。在多种实施方案中,硅前体吸附至PP-PECVD阻挡层上。在一些实施方案中,硅前体吸附至PP-PECVD阻挡层上以及暴露的硫族化物材料上。然而在一些情况中,在硫族化物材料的堆栈之间的间隙中的PP-PECVD阻挡层的厚度可能会比硫族化物材料的堆栈的水平上部处的场域上的PP-PECVD阻挡层的厚度更薄,但在操作251中含卤素的硅前体仍可吸附至PP-PECVD硅氮化物阻挡层的暴露的表面上。

在多种实施方案中,含卤素的硅前体为无氯含卤素的硅前体。例如,在一些实施方案中,前体为含碘和/或含溴硅前体,使得含碘和/或含溴硅前体吸附至衬底表面上。使用含碘和/或含溴硅前体允许无氯沉积。

在多种实施方案中,硅前体为无氢的。例如,在多种实施方案中含碘和/或含溴硅前体可以以溴和/或碘原子完全取代。即,含碘前体和/或含溴前体可不具有氢原子。

术语“含碘硅前体”与“碘硅烷前体”在本文中可互换使用,并且两者皆指包含至少一个硅原子与至少一个碘原子的前体。

使用含碘硅前体使得能进行无氯沉积。示例性的含碘的硅前体包含二碘硅烷(DIS)、四碘硅烷、六碘乙硅烷等。

在一些实施方案中,使用含碘、或含溴、或含碘与溴的含硅前体而非含氯前体。在一些实施方案中,可使用无氯的含卤素硅烷,使得硅烷包含至少一个卤素原子。此类硅烷可具有化学式SiX

示例性的含碘硅前体包含二碘硅烷(DIS)、四碘硅烷、六碘硅烷等。在多种实施方案中,含溴的硅前体是完全卤化的。含溴的硅前体可以具有化学式Si

在操作251中,将衬底暴露于硅前体,使得硅前体吸附至包含PP-PECVD阻挡层的衬底表面上,以在PP-PECVD阻挡层上形成硅前体的吸附层。在一些实施方案中,硅前体为含碘和/或含溴硅前体,并且含碘和/或含溴硅前体以自限制方式吸附到衬底表面上,使得一旦活性位点被含碘和/或含溴的硅前体占据,就很少或没有额外的含碘和/或含溴的硅前体将被吸附在衬底表面上。例如,含碘和/或含溴的硅前体可以吸附在至少约60%的衬底表面上。在多种实施方案中,当含碘和/或含溴的硅前体流入室时,含碘和/或含溴的硅前体吸附在衬底表面上的活性位点上,从而在表面上形成含碘和/或含溴的硅前体的薄层。

在多种实施方案中,该层可以小于单层,并且可以具有介于约

在操作251中暴露于沉积前体的期间,PP-PECVD阻挡层保护硫族化物材料尤其是GST材料不与前体反应,由此保留硫族化物GST材料的轮廓与特性。PP-PECVD层防止硫族化物材料形成具有硅前体的盐。例如,在不存在PP-PECVD阻挡层且含碘硅前体被直接吸附至硫族化物材料的暴露表面上的情况下,硫族化物可以与含碘硅前体反应以形成含碘硫族化物的盐,该盐在硫族化物材料的表面上形成钝化层。虽然钝化层可能不会重新沉积在表面上而造成损伤,但其能使硫族化物材料的表面退化,降低其功能。类似地,含溴硅前体也可以与硫族化物反应,从而形成钝化层。然而,在暴露于用于通过PEALD进行的保形沉积的含卤素的硅前体之前,如果沉积在硫族化物材料上的PP-PECVD阻挡层存在,则硫族化物不会与硅前体反应,并且几乎没有形成钝化层,由此保留硫族化物材料。此外,含卤素的硅前体能吸附至PP-PECVD阻挡层而形成高度保形封装层,并且即使PP-PECVD阻挡层具有低保形性,PP-PECVD阻挡层会非常薄(例如约

在操作253中,处理室被任选地清扫以除去气相中的未吸附到衬底表面的过量的含碘的硅前体。清扫该室可以包括使清扫气体或打扫气体流动,清扫气体或打扫气体可以是在其它操作中使用的载气,或者可以是不同的气体。在一些实施方案中,清扫可包括抽空该室。示例性的清扫气体包含氩气、氮气、氢气和氦气。在一些实施方案中,操作253可以包含用于抽空处理室的一个或多个抽空子阶段。可替代地,应当理解,在一些实施方案中可以省略操作253。操作253可以具有任何适当的持续时间,例如介于约0秒和约60秒之间,例如约0.01秒。在一些实施方案中,增大一种或多种清扫气体的流率可以减少操作253的持续时间。例如,清扫气体流率可以根据各种反应物的热力学特性和/或处理室和/或处理室管道的几何特征进行调整以修改操作251的持续时间。在一非限制性实施例中,清扫阶段的持续时间可以通过调节清扫气体的流率进行调节。这可能会减少沉积循环时间,从而可以提高衬底吞吐量。在清扫后,该含碘和/或含溴的硅前体保持吸附在衬底表面上。

在操作255中,将衬底暴露于第二反应物以与含碘和/或含溴的硅前体的吸附层反应。注意,术语“第二反应物”可用于描述当在ALD循环中点燃等离子体时引入室的一种或多种气体。

在多种实施方案中,第二反应物为无氢的。例如,在一些实施方案中,使用氮气(N

在第二反应物的暴露期间,PP-PECVD阻挡层保护下伏的硫族化物材料尤其是GST材料,使其不与第二反应物反应。在多种实施方案中,PP-PECVD阻挡层的存在防止硫族化物材料与氮等离子体反应、防止在硫族化物表面上形成钝化层。PP-PECVD阻挡层也可防止来自ALD副产物(如碘化氢)的损伤。

在一些实施方案中,如果沉积的PP-PECVD层是充分厚的,例如至少约

在一些实施方案中,反应可以是热的。涉及使用氨(NH

在一些实施方案中,可以在操作255中任选地点燃等离子体。可以提供等离子体能量以将第二反应物(例如含氮气体)活化成离子和自由基以及其他活化物质,其与所吸附的硅前体层反应。在涉及等离子体的公开的实施方案中,等离子体可包括小于约1%的氢自由基,从而减少沉积期间对硫族化物或金属材料的蚀刻。在一些情况下,由于来自膜表面的氢原子可被氮等离子体提取而形成氢自由基,因此来自膜表面的残留氢可形成氢自由基。在一些实施方案中,在使用无氢的含氮反应物的情况下,等离子体不包含氢自由基。

在多种实施方案中,等离子体是原位等离子体,以使得等离子体在室中的衬底表面的正上方形成。原位等离子体可以以介于约0.2122瓦/平方厘米和约2.122瓦/平方厘米之间的每衬底面积的功率点燃。例如,对于处理4个300毫米晶片的室,功率范围可为介于约150W至约6000W之间、或者约600W至约6000W之间、或者介于约800W至约4000W之间。例如,用于ALD工艺的等离子体可通过使用两个电容耦合板施加射频(RF)场给气体而产生。这些板之间的气体通过RF场进行的电离点燃等离子体,从而在等离子体放电区域产生自由电子。这些电子被RF场加速,并且会与气相反应物分子发生碰撞。这些电子与反应物分子的碰撞可形成参与沉积过程的自由基物质。应该理解的是,RF场可以经由任何合适的电极耦合。在多种实施方案中,使用高频等离子体,其具有至少约13.56MHz,或至少约27MHz,或至少约40MHz,或至少约60MHz的频率。在一些实施方案中,可以使用基于微波的等离子体。电极的非限制性示例包括处理气体分配喷头和衬底支撑基座。应当理解,用于ALD工艺的等离子体可以通过与将RF场与气体电容耦合不同的一种或多种合适的方法形成。在一些实施方案中,等离子体是远程等离子体,使得第二反应物在室上游的远程等离子体发生器中点燃,然后输送到容纳衬底的室内。

返回图2C,在操作257中,任选地清扫室以移除被蚀刻掉的物质和任何残留的副产物。操作225713可以使用以上关于操作253描述的任何条件来进行清扫。

在图2C的操作259中,确定膜的所需的厚度是否已沉积。如果没有,则重复操作251-257足够的循环以沉积所需的膜厚度。任何适当数量的沉积循环可被包含在ALD工艺中,以沉积硅氮化物的所需的膜厚度。例如,大约50个沉积循环可被执行以使用所公开的实施方案在衬底上沉积膜。在一些实施方案中,在用于制造内存件的膜堆栈上的侧壁上沉积的硅氮化物膜的厚度可以大于约

在多种实施方案中,PEALD硅氮化物封装层所具有的密度大于PP-PECVD阻挡层的密度。在一些实施方案中,在操作251-259中沉积的PEALD硅氮化物封装层具有至少约2.75g/cm

包含PP-PECVD与PEALD膜两者作为封装层的双层相比于单一PP-PECVD膜和单一PEALD膜中的每一者具有较优的特性。例如,单一PP-PECVD阻挡层可能不足以提供保形性而在OTS或GST硫族化物材料上方提供密封封装层。另外,利用可能都是无氢的含卤素的硅前体与含氮反应物所沉积的单一PEALD封装层可能会因为含卤素的硅前体与硫族化物材料反应而仍造成钝化层形成在硫族化物材料的表面上。然而,当在PEALD封装层下方具有PP-PECVD阻挡层时,PP-PECVD阻挡层在硫族化物材料与含卤素的硅前体之间提供充分的阻挡,以防止含卤素的硅前体与硫族化物材料反应,且沉积在PP-PECVD层上方的PEALD封装层提供充分的密封性、高保形性以及低氢含量。本文中所述的双层方案涉及,在暴露于含卤素的硅前体之前,将PP-PECVD阻挡层直接沉积在硫族化物材料上。即,在多种实施方案中,PP-PECVD阻挡层利用无卤素的硅前体(例如硅烷或乙硅烷)沉积。

图3是显示根据某些所公开的实施方案的方法的一示例的示例性时序图。工艺300包含脉冲式等离子体阶段330与ALD阶段350。脉冲式等离子体阶段330可对应于图2A的操作230、或图2B的操作231与233。ALD阶段350可对应于图2B的操作250、或图2C的操作251-257。在示例性工艺300中显示下面将更进一步说明的两个ALD循环。在该特定的示例中,在脉冲式等离子体阶段330中利用硅烷与氮气作为氮反应物沉积硅氮化物PP-PECVD阻挡层,该硅烷与氮气也在ALD阶段中使用。在脉冲式等离子体阶段330中沉积硅氮化物PP-PECVD阻挡层之后,在ALD阶段350中利用两个ALD循环沉积硅氮化物PEALD封装层,硅氮化物PEALD封装层是利用无氯的硅前体(例如二碘硅烷)与氮气来沉积的。

在整个工艺300期间可使惰性气体流动。应理解,在一些实施方案中,惰性气体还具有清扫气体的功能。示例性的惰性气体包含氩气、氦气和氪气。可使用非氢的惰性气体以防止氢与硫族化物材料之间的反应。此外,应理解,虽然使用本文中所述的相同惰性气体作为惰性气体与清扫气体,但在一些实施方案中,这些气体可具有不同的组成。另外,在一些实施方案中,使用惰性气体作为载气以将一或多种处理气体输送至处理室。

在脉冲式等离子体阶段330(可对应于图2B的操作230)中,使惰性气体流动、关闭无氯的硅前体流、使硅烷反应物流动、还使氮反应物流动。如在脉冲式等离子体阶段330中所示,在ON与OFF阶段之间点燃等离子体多次。等离子体的脉冲化可对应于图2B的操作233。

ALD阶段350包含两个ALD循环。第一ALD循环包含前体暴露阶段351a(可对应于图2C的操作251)。在前体暴露阶段351a期间,使惰性气体流动、使无氯的硅前体流动、关闭硅烷反应物、还关闭氮反应物。将等离子体功率关闭且未点燃等离子体。

在清扫阶段353a(可对应于图2C的操作253)中,在无氯的硅前体、硅烷反应物以及氮反应物流皆关闭且还关闭等离子体时,使惰性气体流动。

在反应物暴露阶段355a(可对应于图2C的操作255)中,无氯的硅前体与硅烷反应物流关闭,但氮反应物流开启且点燃等离子体时,使惰性气体流动。

在清扫阶段357a(可对应于图2C的操作257)中,在无氯的硅前体、硅烷以及氮流关闭且还关闭等离子体时,使惰性气体流动。

在该示例中,由于在图2C的操作259中评估出膜尚未沉积至充分厚度,因此重复ALD循环。ALD的第二循环包含前体暴露阶段351b、清扫阶段353b、反应物暴露阶段355b以及清扫阶段357b。

在前体暴露阶段351b(可对应于图2C的操作251)中,使惰性气体流动以及使无氯的硅前体流动,但关闭硅烷流与氮流。在该阶段期间关闭等离子体。

在清扫阶段353b(可对应于图2C的重复操作253)中,使惰性气体流动,但关闭无氯的硅前体、硅烷以及氮气。在此阶段未点燃等离子体。

在反应物暴露阶段355b(可对应于图2C的重复操作255)中,使惰性气体流动,但关闭无氯的硅前体与硅烷气体流。在该阶段期间开启氮气流并且开启等离子体。

在清扫阶段357b(可对应于图2C的重复操作257)中,使惰性气体流动,但关闭无氯的硅前体、硅烷以及氮气流。在该阶段未点燃等离子体。

虽然在ALD阶段350中显示了两个ALD循环,但应当理解,在多种实施方案中,可使用两个以上的循环沉积封装层以形成具有一些期望特性(例如厚度、保形性、密度以及密封性)的封装层。

设备

图4绘出了具有用于保持低压环境的处理室主体402的原子层沉积(ALD)处理站400的一实施方案的示意图。多个ALD处理站400可以包含在通常低压处理工具环境中。例如,图5绘出了多站式处理工具500的一实施方案。在一些实施方案中,ALD处理站400的一个或一个以上的硬件参数(包含下文详细讨论的那些)可以由一个或一个以上的计算机控制器450以编程方式调节。例如,可程序化一或多个计算机控制器450以进行根据某些所公开的实施方案的PP-PECVD、PEALD、或两者。

ALD处理站400与反应物输送系统401a流体连通,以将处理气体输送至分配喷头406。反应物输送系统401a包含混合容器404,混合容器404用于混合和/或调节处理气体以输送至喷头406,所述处理气体例如无卤素的硅前体(例如硅烷)、含卤素的硅前体(例如含碘及/或含溴的硅气体)、氮气、含氮气体、氢气。一或多个混合容器入口阀420可控制处理气体至混合容器404的导入。在一些例如通过PP-PECVD进行的沉积的实施方案中,也可将氮等离子体、或氢等离子体输送至喷头406、或可在ALD处理站400中产生氮等离子体、或氢等离子体。

举例而言,图4的实施方案包含汽化点403,汽化点403用于汽化将供应至混合容器404的液体反应物。在一些实施方案中,汽化点403可以是加热的蒸发器。从这样的蒸发器产生的饱和的反应物蒸气会在下游输送管道凝结。不兼容气体暴露至凝结的反应物会产生小颗粒。这些小颗粒可能阻塞管道、阻碍阀操作、污染衬底等。处理这些问题的一些方法涉及清扫和/或排空输送管道以去除残留反应物。然而,清扫输送管道会增加处理站循环时间,降低处理站吞吐量。因此,在一些实施方案中,汽化点403下游的输送管道可以被热追踪。在一些示例中,混合容器304也可以被热追踪。在一个非限制性示例中,汽化点403下游的管道具有增大的温度分布,从约100℃延伸至在混合容器404处的约150℃。

在一些实施方案中,液体前体或者液体反应物可以在液体喷射器处汽化。例如,液体喷射器可以将液体反应物的脉冲喷射到混合容器上游的载体气体流中。在一个实施方案中,液体喷射器可以通过将液体从较高压闪变到较低压来汽化反应物。在另一个示例中,液体喷射器可以将液体雾化为接下来在加热的输送管中汽化的分散的微滴。较小的液滴比较大的液滴可以较快汽化,从而减小了在液体注入和完成汽化之间的延迟。较快的汽化可以减小汽化点403下游的管道长度。在一个方案中,液体喷射器可以直接装载到混合容器404。在另一个方案中,液体喷射器可以直接装载到喷头406。

在一些实施方案中,可以在汽化点403上游设置液体流控制器(LFC)来控制用于汽化并输送至处理站400的液体的质量流量。例如,LFC可以包含位于LFC下游的热质量流量计(MFM)。然后可以响应于由与MFM电通信的比例积分微分(PID)控制器提供的反馈控制信号,来调节LFC的柱塞阀。然而,其可以采取一秒或一秒以上来使用反馈控制以稳定液体流。这可以延长投配液体反应物的时间。因此,在一些实施方案中,LFC可以在反馈控制模式和直接控制模式之间动态切换。在一些实施方案中,这可以通过禁用PID控制器和LFC的感测管道来执行。

喷头406朝衬底412分配处理气体。在图4所示的实施方案中,衬底412位于喷头406下方,并且示出为安置在基座408上。喷头406可以具有任何适当的形状,并可以具有任何适当数量和布置的端口,以将处理气体分配至衬底412。

在一些实施方案中,基座408可以升高或降低以暴露衬底412给衬底412和喷头406之间的体积。应理解的是,在一些实施方案中,基座高度可以经由合适的计算机控制器450通过编程方式进行调节。

在另一种情况下,调节基座408的高度可以使得等离子体密度在点燃等离子体的实施方案中的工艺中的等离子体活化循环期间内改变。在处理阶段结束时,基座408可以在另一衬底传送阶段被降低以使得衬底412能从基座408移走。

在一些实施方案中,基座408可以通过加热器410进行温度控制。在一些实施方案中,在如在公开的实施方案中所述的沉积双层硅氮化物膜期间,基座408可以被加热到至少约250℃的温度,或者在一些实施方案中,加热到低于约300℃,例如约250℃的温度。在一些实施方案中,基座设定在介于约50℃和约300℃之间的温度,例如介于约200℃和约275℃之间的温度。在一些实施方案中,基座设定在介于约50℃和约300℃之间的温度。在一些实施方案中,基座设定在介于约200℃和约275℃之间的温度。

此外,在一些实施方案中,对于处理站400的压力控制可以由蝶形阀418提供。如在图4的实施方案中所示,蝶形阀418对由下游真空泵(未示出)提供的真空进行调节。然而,在一些实施方案中,对处理站400的压力控制还可以通过改变引入至处理站400的一种或多种气体的流率来调节。

在一些实施方案中,喷头406的位置可以相对于基座408调节以改变衬底412和喷头406之间的体积。此外,应当理解的是,基座408和/或喷头406的竖直位置可以通过本公开内容的范围内的任何合适的机构来改变。在一些实施方案中,基座408可包含用于旋转衬底412的方位的旋转轴线。应该理解的是,在一些实施方案中,这些示例性调节中的一种或多种可以通过一个或多个适当的计算机控制器450以编程方式执行。

在如上所述可以使用等离子体的一些实施方案中,喷头406和基座408电连接射频(RF)功率源414和匹配网络416来对等离子体提供功率。在一些实施方案中,等离子体的能量可通过控制处理站的压强、气体的浓度、RF源功率、RF源频率以及等离子体功率脉冲时序中的一个或多个来控制。例如,RF功率源414和匹配网络416可在任何合适的功率下进行操作,以形成具有所期望的组分的等离子体物质的等离子体。合适的功率的示例包含在上文中。同样,RF功率源414可以提供任何适当频率的RF功率。在一些实施方案中,RF功率源414可以被配置为控制彼此独立的高频RF功率源和低频RF功率源。示例性的低频RF频率可以包含,但不限于,介于0kHz和500kHz之间的频率。示例性的高频RF频率可以包含,但不限于,介于1.8MHz和2.45GHz之间的频率,或大于约13.56MHz、或大于27MHz、或大于40MHz、或大于60MHz的频率。应当理解,任何合适的参数可被离散地或连续地调制以提供用于表面反应的等离子体能量。

在一些实施方案中,等离子体可由一个或多个等离子体监控器原位监控。在一种情形中,等离子体功率可通过一个或多个电压、电流传感器(例如,VI探针)进行监控。在另一种情况下,等离子体密度和/或处理气体的浓度可以由一个或多个光发射光谱传感器(OES)来测量。在一些实施方案中,一个或多个等离子体参数可基于来自这样的原位等离子体监控器的测量结果通过编程方式进行调节。例如,OES传感器可用于反馈回路中以提供对等离子体功率的编程式控制。应理解的是,在一些实施方案中,可使用其它监控器来监控等离子体和其它工艺特性。这样的监控器可包含,但不限于,红外(IR)监控器、声学监控器、以及压力传感器。

在一些实施方案中,可以经由输入/输出控制(IOC)测序指令来提供用于控制器450的指令。在一个示例中,用于设置工艺阶段的条件的指令可被包含在工艺配方的相应的配方阶段中。在某些情况下,工艺配方阶段可按顺序排列,使得用于工艺阶段的所有指令与该工艺阶段同时执行。在一些实施方案中,用于设定一个或多个反应器参数的指令可以被包含在配方阶段中。在一些情况中,工艺配方阶段可依顺序配置,故一工艺阶段的所有指令系与该工艺阶段同步执行。在一些实施方案中,可将用以设定一或多个反应器参数的指令包含于一配方阶段中。例如,配方阶段可包含用于设定惰性气体和/或第一反应物气体(如无氯的硅烷)的流率的指令、用于设定载气(如氦气)的流率的指令、用以设定第二反应物气体(如氮气或氢气)的流率的指令以及用于脉冲化等离子体的指令。

在另一示例中,第一配方阶段可以包含用于设定惰性气体和/或反应物气体(例如,第一前体,如含碘的和/或含溴的硅前体)的流率的指令、用于设定载气(诸如氩气)的流率的指令;以及用于第一配方阶段的时间延迟指令。接下来的第二配方阶段可以包含用于调制或者停止惰性气体和/或反应物气体的流率的指令、用于调制载气或者清扫气体的流率的指令、以及用于第二配方阶段的时间延迟指令。第三配方阶段可以包含用于调节第二反应物气体(例如氮气)的流率的指令,用于在第三配方阶段期间点燃等离子体的指令,用于调节载气或清扫气体的流率的指令,以及用于第三配方阶段的时间延迟指令。随后的第四配方阶段可以包括用于调节惰性气体和/或反应物气体的流率或停止惰性气体和/或反应物气体的流动的指令,以及用于调节载气或清扫气体的流率的指令和用于第四配方阶段的时间延迟指令。应当理解,这些配方阶段可以在所公开的实施方案的范围内以任何合适的方式进一步细分和/或迭代。在一些实施方案中,控制器450可以包括以下关于图5的系统控制器550描述的任何特征。

如上所述,一个或一个以上的处理站可以包含在多站处理工具中。图5示出了多站式处理工具500的实施方案的概要视图,其具有入站装载锁502和出站装载锁504,其一者或者两者可以包含远程等离子体源。处于大气压的机械手506被配置为将晶片从通过舱508装载的盒经由大气端口510移动至入站装载锁502内。晶片由机械手506放置在入站装载锁502中的基座512上,关闭大气端口510,且抽空装载锁。当入站装载锁502包含远程等离子体源时,晶片在被引入处理室514之前,可以暴露至装载锁中的远程等离子体处理。此外,晶片另外也可以在入站装载锁502中加热,例如以移除湿气和吸附的气体。接下来,通向处理室514的室传输端口516被打开,并且另一机械手518将晶片放置到用于处理的处理站580、582、584中的一者中、或通向用于处理的处理站590的加载站中。虽然图5中的实施方案显示加载互锁装置,但应理解,在一些实施方案中,可使晶片直接进入处理站。

所示的处理室514包含四个处理站580、582、584以及590。处理站590可以是可移除的模块,并且可适合用于一次处理一个以上的衬底。在该示例中,处理站590包含四个子站,在图5所示的实施方案中编号为1-4。

每一站(580、582、584以及1、2、3、与4中的每一者)可具有经加热的基座以及气体管线入口。应明白,在一些实施方案中,每一处理站可具有不同或多重目的。例如,在一些实施方案中,处理站580可用于蚀刻衬底,处理站582可用于清理衬底,而处理站584可用于进行PP-PECVD。处理站590可用于进行PEALD。处理站可在PP-PECVD、ALD以及等离子体增强ALD工艺模式之间切换。附加地或替代地,在一些实施方案中,处理室514可以包含一或多对相匹配的ALD站与等离子体增强ALD处理站。虽然在所示的处理站590中包含四个子站,但应理解,根据本发明的处理室可具有任何适合数目的子站。此外,虽然多站工艺设备500包含四站(580、582、584、590),但应理解,在一些实施方案中,设备可包含比四站更多或更少的处理站,且每一站可以是可移除或可修改的模块。例如,在一些实施方案中,处理室可包含五或更多个处理站,但在其他实施方案中处理室可包含三个或更少的处理站。

图5显示了用于在多站处理工具500内传输晶片的晶片搬运系统518的实施方案。在一些实施方案中,晶片搬运系统可以在各种处理站之间和/或在处理站与装载互锁机构之间传输晶片。此外,处理站590可包含用于将晶片从另一装载站562移动至处理站590的分离晶片搬运系统560。应明白,可使用各种合适的晶片搬运系统。非限制性示例包含晶片转盘以及晶片搬运机械手。

在多种实施方案中,整合各种处理站可以解决占用面积缩减的问题并且切换以将晶片传输至在不同压强下操作的不同处理模块的能力。在一些实施方案中,主工具与上下快速循环压强的处理模块之间可存在定制的微传送站。

图5还绘出了采用来控制处理工具500的处理条件和硬件状态的系统控制器550的实施方案。系统控制器550可以包含一个或多个内存装置556、一个或多个质量存储装置554和一个或多个处理器552。处理器552可以包含计算机或者CPU、模拟和/或数字输入/输出连接、步进马达控制器板等。

在一些实施方案中,系统控制器550控制处理设备500的所有活动。系统控制器550执行存储在海量存储装置554、载入内存装置556、并由处理器552执行的系统控制软件558。可替代地,控制逻辑可以在控制器550中硬编码。特定应用集成电路、可编程逻辑装置(例如现场可编程栅极阵列、或者FPGA)等可以用于这些目的。在下面的讨论中,无论使用“软件”还是“代码”,可以使用功能上相当的硬编码的逻辑来取代。系统控制软件558可以包含用于控制时序、气体的混合、气体流率、室和/或站压强、室和/或站温度、晶片温度、目标功率电平、RF功率电平、衬底基座、卡盘和/或底座位置、以及由处理工具500执行的特定处理的其它参数的指令。系统控制软件558可以以任何适当的方式配置。例如,各种处理工具组件子程序或者控制对象可以写入以控制用于执行各种处理工具处理的处理工具组件的操作。系统控制软件558可以以任何适当的计算机可读编程语言来编码。

在一些实施方案中,系统控制软件558可以包含用于控制上述各种参数的输入/输出控制(IOC)测序指令。在一些实施方案中可以采用与系统控制器550关联的、存储在海量存储装置554和/或内存装置556的其它计算机软件和/或程序。用于该目的的程序或者程序段的示例包含衬底定位程序、处理气体控制程序、压力控制程序、加热器控制程序、以及等离子体控制程序。

衬底定位程序可以包含用于处理工具组件的程序代码,该处理工具组件用于将衬底装载到基座518,并控制衬底和处理工具500的其它部分之间的间隔。

处理气体控制程序可包含用于控制气体组成(例如,如本文所述的含碘的硅前体气体、和含氮气体、载气以及清扫气体)和流率的代码和任选地用于使气体在沉积之前流到一个或多个处理站中以稳定在处理站中的压强的代码。压强控制程序可以包含用于通过调节例如在处理站的排放系统中的节流阀、流入处理站内的气流等等来控制处理站内的压强的代码。

加热器控制程序可包含用于控制流向用于加热衬底的加热单元的电流的代码。可替代地,加热器控制程序可控制传热气体(如氦气)朝向衬底的传送。

等离子体控制程序可包含用于根据本文的实施方案设置施加到一个或多个处理站内的处理电极的RF功率电平的代码。

压强控制程序可以包含用于根据本文的实施方案保持反应室内的压强的代码。

在一些实施方案中,可以存在与系统控制器550相关联的用户界面。用户界面可以包含显示屏、设备和/或工艺条件的图形软件显示器、以及诸如定点装置、键盘、触摸屏、麦克风等用户输入装置。

在一些实施方案中,由系统控制器550调节的参数会涉及工艺条件。非限制性实例包含处理气体组成和流率、温度、压强、等离子体条件(例如,RF偏置功率电平)等。这些参数可以以配方的形式提供给用户,配方可以利用所述用户界面输入。

用于监控处理的信号可以由系统控制器550的模拟和/或数字输入连接件从各种处理工具传感器提供。用于控制处理的信号可以通过处理工具500的模拟和/或数字输出连接件输出。可被监控的处理工具传感器的非限制性实例包含质量流量控制器、压力传感器(例如压力计)、热电偶等等。经适当编程的反馈和控制算法可以与来自这些传感器的数据一起使用,以保持工艺条件。

系统控制器550可以提供用于执行上述沉积处理的程序指令。所述程序指令可以控制多种处理参数,如DC功率电平、RF偏置功率电平、压强、温度等。所述指令可以控制这些参数以根据本发明所描述的多种实施方案操作封装双层的原位沉积。

系统控制器550将通常包含一个或多个内存装置和被配置成执行指令的一个或多个处理器以使该设备将执行根据所公开的实施方案所述的方法。包含用于控制根据所公开的实施方案的处理操作的指令的机器可读的介质可以耦合到系统控制器550。

在一些实现方式中,系统控制器550是系统的一部分,该系统可以是上述实施例的一部分。这种系统可以包含半导体处理装置,该半导体处理装置包含一个或多个处理工具、一个或多个室、用于处理的一个或多个平台和/或具体的处理组件(晶片基座、气流系统等)。这些系统可以与用于控制它们在处理半导体晶片或衬底之前、期间和之后的操作的电子器件一体化。电子器件可以称为“控制器”,该控制器可以控制一个或多个系统的各种元件或子部件。根据处理要求和/或系统的类型,系统控制器550可以被编程以控制本文公开的任何工艺,包含控制处理气体输送、温度设置(例如,加热和/或冷却)、压强设置、真空设置、功率设置、射频(RF)发生器设置、RF匹配电路设置、频率设置、流速设置、流体输送设置、位置及操作设置、晶片转移进出工具和其它转移工具和/或与具体系统连接或通过接口连接的装载锁。

广义而言,系统控制器550可以定义为接收指令、发布指令、控制操作、启用清洁操作、启用端点测量等等的具有各种集成电路、逻辑、内存和/或软件的电子器件。集成电路可以包含存储程序指令的固件形式的芯片、数字信号处理器(DSP)、定义为专用集成电路(ASIC)的芯片和/或一个或多个微处理器或执行程序指令(例如,软件)的微控制器。程序指令可以是以各种单独设置的形式(或程序文件)传送到系统控制器550的指令,该设置定义用于在半导体晶片或系统上或针对半导体晶片或系统执行特定处理的操作参数。在一些实施方案中,操作参数可以是由工艺工程师定义的用于在制备晶片的一或多个(种)层、材料、金属、氧化物、硅、二氧化硅、表面、电路和/或管芯期间完成一个或多个处理步骤的配方(recipe)的一部分。

在一些实现方式中,系统控制器550可以是与系统集成、耦合或者说是通过网络连接系统或它们的组合的计算机的一部分或者与该计算机耦合。例如,系统控制器550可以在“云端”或者是fab主机系统的全部或一部分,从而可以允许远程访问晶片处理。计算机可以启用对系统的远程访问以监控制造操作的当前进程,检查过去的制造操作的历史,检查多个制造操作的趋势或性能标准,改变当前处理的参数,设置处理步骤以跟随当前的处理或者开始新的工艺。在一些实施例中,远程计算机(例如,服务器)可以通过网络给系统提供工艺配方,网络可以包含本地网络或互联网。远程计算机可以包含允许输入或编程参数和/或设置的用户界面,该参数和/或设置然后从远程计算机传送到系统。在一些实施例中,系统控制器550接收数据形式的指令,该指令指明在一个或多个操作期间将要执行的每个处理步骤的参数。应当理解,参数可以针对将要执行的工艺类型以及工具类型,系统控制器550被配置成连接或控制该工具类型。因此,如上所述,系统控制器550可以例如通过包含一个或多个分立的控制器而为分布式,这些分立的控制器通过网络连接在一起并且朝着共同的目标(例如,本文所述的工艺和控制)工作。用于这些目的的分布式控制器的实施例可以是与结合以控制室内工艺的一个或多个远程集成电路(例如,在平台水平或作为远程计算机的一部分)通信的室上的一个或多个集成电路。

在非限制性的条件下,示例的系统可以包含等离子体蚀刻室或模块、沉积室或模块、旋转清洗室或模块、金属电镀室或模块、清洁室或模块、倒角边缘蚀刻室或模块、物理气相沉积(PVD)室或模块、化学气相沉积(CVD)室或模块、ALD室或模块、原子层蚀刻(ALE)室或模块、离子注入室或模块、轨道室或模块、以及在半导体晶片的制备和/或制造中可以关联上或使用的任何其它的半导体处理系统。

如上所述,根据工具将要执行的一个或多个工艺步骤,系统控制器550可以与一个或多个其它的工具电路或模块、其它工具组件、组合工具、其它工具界面、相邻的工具、邻接工具、位于整个工厂中的工具、主机、另一个控制器、或者在将晶片的容器往来于半导体制造工厂中的工具位置和/或装载口搬运的材料搬运中使用的工具通信。

用于执行本文公开的方法的适当设备在2011年4月11日提交的名称为“等离子体激活的共形膜沉积”的美国专利申请No.13/084,399(现在的美国专利No.8,728,956);以及2011年4月11日提交的名称为“硅氮化物膜和方法”的美国专利申请No.13/084,305中进一步讨论并说明,这些专利中的每个整体并入本文。

本文所述的设备/工艺可以与光刻图案化工具或工艺结合使用,例如,用于制备或制造半导体器件、显示器、LED、光伏电池板等。通常,虽然不是必要地,这些工具/工艺将在共同的制造设施中一起使用或操作。膜的光刻图案化通常包含以下操作中的一些或所有,每个操作启用多个可行的工具:(1)使用旋涂或喷涂工具在工件,即,衬底,上涂覆光致抗蚀剂;(2)使用热板或加热炉或UV固化工具固化光致抗蚀剂;(3)使用例如晶片步进曝光机之类的工具使光致抗蚀剂暴露于可见光或紫外线或x-射线;(4)使抗蚀剂显影以便选择性地去除抗蚀剂并且从而使用例如湿式工作台之类的工具将其图案化;(5)通过使用干式或等离子体辅助蚀刻工具将抗蚀剂图案转印到下方的膜或工件上;并且(6)使用例如射频或微波等离子体抗蚀剂剥离器之类的工具去除抗蚀剂。

实验

实验1

在蚀刻与清理后,将衬底上的相变材料的堆栈暴露于二碘硅烷与氮等离子体的交替脉冲60秒以沉积

在蚀刻与清理后,将衬底上的相变材料的堆栈暴露于硅烷气体与氮气,并同时使等离子体在ON与OFF相之间脉冲化一定持续时间以沉积

实验2

在脉冲式等离子体PECVD的硅氮化物膜的三种不同工作周期上进行实验。在稀释的氢氟酸中评估湿式蚀刻率。第一硅氮化物膜是以100%工作周期沉积(连续等离子体开启,无脉冲化),相比于硅氧化物得到26.2的湿式蚀刻率比值。相对地,以30%工作周期脉冲式沉积的第二薄膜得到约5.3的湿式蚀刻率比值,以15%工作周期脉冲式沉积的第三薄膜得到约4.3的湿式蚀刻率比值。此类结果显示于图6中。这些结果表明,相比于不使用脉冲化所沉积的高湿式蚀刻率硅氮化物膜,使用PP-PECVD能大幅改善/降低湿式蚀刻率。实验结果显示湿式蚀刻率下降是与工作周期以及薄膜相关的。

结论

虽然上述实施例已经为了清楚理解的目的在一些细节方面进行了描述,但显而易见的是,某些变化和修改方案可在所附权利要求的范围内实施。应当注意的是,具有实施本发明的实施方案的工艺、系统和设备的许多替代方式。因此,本发明的实施方案应被视为是说明性的而不是限制性的,并且所述实施方案并不限于本文所给出的细节。此外,本文中所列举的范围在一些实施方案中应被理解为包含范围的端点值。

- 硫族化物材料的保形无损伤封装

- 硫代氨基甲酰基二硫烷基官能化脂环族化合物、其制备方法、含该化合物的填充的硫可硫化弹性体组合物和由其制造的制品