显示面板及其驱动电路

文献发布时间:2023-06-19 19:37:02

技术领域

本申请涉及显示技术领域,尤其涉及一种显示面板及其驱动电路。

背景技术

OLED,即有机发光二极管(Organic Light-Emitting Diode),又称为有机电激光显示(Organic Electroluminesence Display,OELD)。OLED显示屏比LCD更轻薄、亮度高、功耗低、响应快、对比度高、色域广、视角广,受到消费者青睐。通常在OLED面板制备出来之后,会因为对应R、G、B像素的LED发光亮度不同,会使用ACC(accurate color capture)调节,将R、G、B像素对应的Data灰阶进行调整,实现更真实的色彩显示或者满足不同白平衡的需求。通常ACC是通过降低高亮的像素(R/G/B)以匹配低亮度的像素(R/G/B)来实现。但是在R、G、B均为255灰阶时,无法再提升某一颜色来实现R、G、B配比。一般ACC调整时还会遇到非整数灰阶,因此还需要FRC(Frame rate control)功能提升色深才能实现,因此相对来说更为复杂,成本相对也较高。

因此,为了解决OLED中LED发光亮度不同,导致色彩显示不满足白平衡或不真实的问题,本领域技术人员亟需一种更加简单,效果更好的解决方案。

发明内容

本申请的目的是提供一种显示面板及其驱动电路,以提高显示面板的色彩显示真实性,降低显示面板的成本。

本申请公开了一种显示面板的驱动电路,所述显示面板包括多个像素,每个所述像素包括一个主像素和一个辅像素,同一所述像素中的所述主像素和所述辅像素的发光颜色相同;所述驱动电路包括设置在每个所述像素内的主像素驱动子电路和辅像素驱动子电路,所述主像素驱动子电路用于驱动所述主像素内的发光单元发光,所述辅像素驱动子电路用于驱动所述辅像素内的发光单元发光;同一所述像素内,所述主像素驱动子电路和所述辅像素驱动子电路连接同一条数据线或同一条扫描线;所述辅像素的灰阶低于所述主像素的灰阶。

可选的,所述驱动电路在以第一状态驱动时,所述主像素的灰阶在0-255范围内,所述辅像素的灰阶在0-127范围内;所述驱动电路以第二状态驱动时,所述主像素的灰阶在0-255范围内,所述辅像素的灰阶在0-255范围内。

可选的,同一所述像素内,所述主像素驱动子电路和所述辅像素驱动子电路连接同一条数据线和同一条扫描线;所述主像素驱动子电路包括:第一数据输入电路、第一电容电路、第一驱动电路和主发光单元;所述第一数据输入电路接入所述扫描线上的扫描信号和所述数据线上的数据信号,并在所述扫描信号的控制下将所述数据信号传输至第一节点,所述第一电容电路的一端连接所述第一节点,所述第一电容电路的另一端连接第二节点,所述第二节点接入第一电源信号;所述第一驱动电路连接所述第一节点、所述第二节点和所述主发光单元的一端,所述主发光单元的另一端接入第二电源信号;所述辅像素驱动子电路包括:第二数据输入电路、第二电容电路、第二驱动电路和辅发光单元;所述第二数据输入电路接入所述扫描线上的扫描信号和所述数据线上的数据信号,并在所述扫描信号的控制下将所述数据信号传输至第三节点,所述第二电容电路的一端连接所述第三节点,所述第二电容电路的另一端连接第四节点,所述第四节点接入所述第一电源信号;所述第二驱动电路连接所述第三节点、所述第四节点和所述辅发光单元的一端,所述辅发光单元的另一端接入所述第二电源信号;当前行所述扫描线在扫描时段中,所述扫描信号分为第一阶段和第二阶段,所述扫描信号在所述第一阶段为第一电平,所述扫描信号在所述第二阶段为第二电平,所述第一电平大于所述第二电平,所述第一数据输入电路和所述第二数据输入电路在所述第一阶段同时导通,所述第二数据输入电路在所述第二阶段保持导通,所述第一数据输入电路在所述第二阶段处于截止状态。

可选的,在当前行所述扫描线处于扫描时段时,同一条数据线上,所述数据信号在所述第一阶段的最小电平大于所述数据信号在所述第二阶段的最大电平;所述扫描信号在第二阶段的第二电平小于所述数据信号在所述第一阶段的最小电平。

可选的,在当前行所述扫描线处于扫描时段时,同一条数据线上,所述数据信号在所述第一阶段为15-25V,所述数据信号在所述第二阶段为0-10V,所述第一电平为30V±2V,所述第二电平为15V±2V,所述扫描信号的截止电平为-5V。

可选的,所述第一数据输入电路包括第一主动开关,所述第二数据输入电路包括第二主动开关,所述第一主动开关的控制端、输入端和所述第二主动开关的控制端、输入端分别连接同一条扫描线和同一条数据线;所述第一驱动电路包括第一驱动晶体管,所述第一驱动晶体管的栅极连接所述第一节点,所述第二驱动电路包括第二驱动晶体管,所述第二驱动晶体管的栅极连接所述第三节点;在所述扫描信号处于所述第一阶段时,所述第一主动开关和所述第二主动开关导通;在所述扫描信号处于所述第二阶段时,所述第二主动开关保持导通,所述第一主动开关截止。

可选的,所述第一驱动晶体管和所述第二驱动晶体的沟道的宽长比不同,所述第一驱动晶体管的饱和区工作电压范围为15-25V,所述第二驱动晶体管的饱和区工作电压范围为0-10V。

可选的,所述主像素的面积大于所述辅像素的面积。

可选的,每个所述像素还包括一个主像素,两个所述主像素和一个所述辅像素构成一个像素;两个所述主像素连接同一条扫描线或同一条数据线。

本申请还公开了一种显示面板,包括上述的显示面板的驱动电路。

本申请通过改变像素设计,通过主像素和辅像素配合的方式,通过将主像素和辅像素设计为不同的灰阶,在不增加数据线和扫描线的情况下,分时对主像素和辅像素分别充入不同的数据电压,实现不同的灰阶显示。且在显示出现不真实的情况下,可通过调整辅像素的电压,即调整辅像素的灰阶亮度,对该像素的亮度进行提升和降低,从而实现ACC调节,可实现更真实的色彩显示,也可满足不同的白平衡需求。相比于示例性技术中选择ACC和FRC的方案来说,本申请的方案更简单,实施起来更容易,而且能够达到实施ACC和FRC的方案相同的效果。且不需要时序控制器去完成ACC和FRC调节,相对来说释放了时序控制器的性能,成本更低。

附图说明

所包括的附图用来提供对本申请实施例的进一步的理解,其构成了说明书的一部分,用于例示本申请的实施方式,并与文字描述一起来阐释本申请的原理。显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。在附图中:

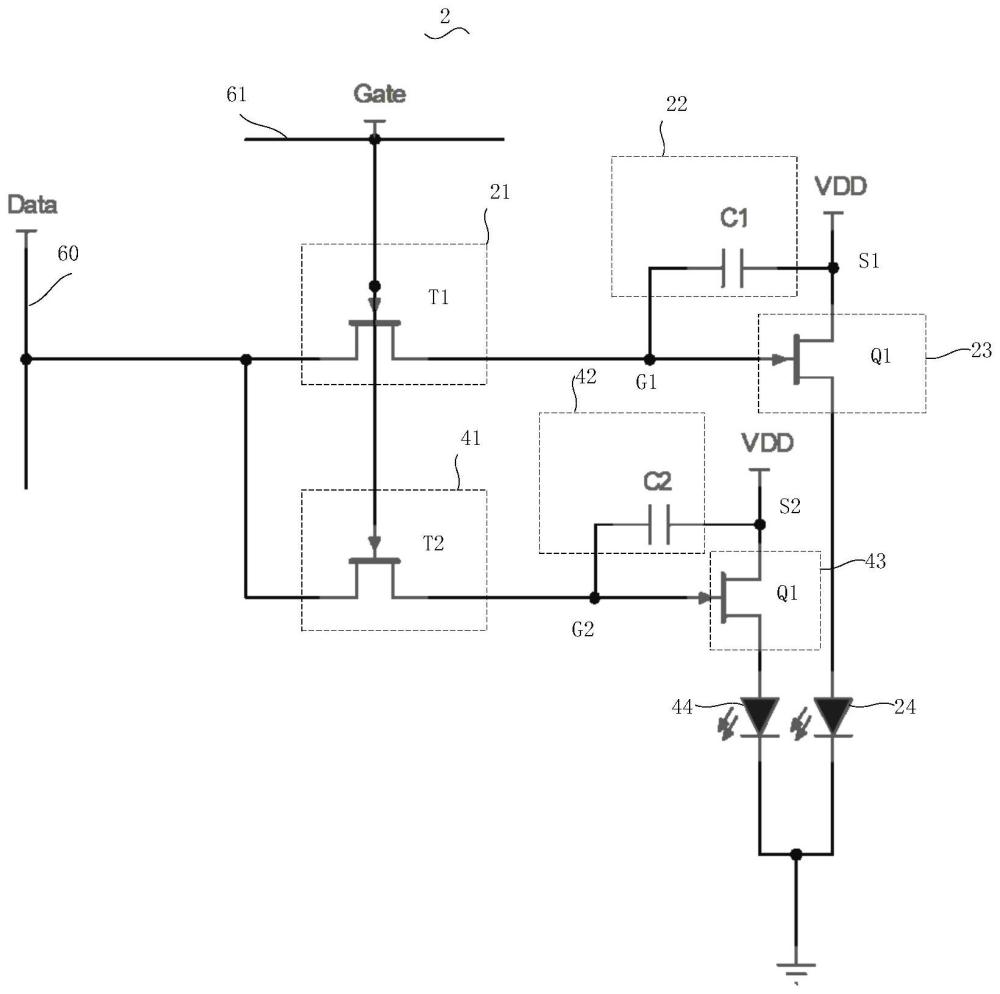

图1是本申请的显示面板的驱动电路的示意图;

图2是本申请的像素的排列示意图;

图3是本申请的当前像素对应的扫描线和数据线的驱动时序示意图;

图4是本申请的显示面板的示意图。

其中,1、显示面板;2、驱动电路;10、像素;11、主像素;12、辅像素;21、第一数据输入电路;22、第一电容电路;23、第一驱动电路;24、主发光单元;41、第二数据输入电路;42、第二电容电路;43、第二驱动电路;44、辅发光单元;60、数据线;61、扫描线;

具体实施方式

需要理解的是,这里所使用的术语、公开的具体结构和功能细节,仅仅是为了描述具体实施例,是代表性的,但是本申请可以通过许多替换形式来具体实现,不应被解释成仅受限于这里所阐述的实施例。

在本申请的描述中,术语“第一”、“第二”仅用于描述目的,而不能理解为指示相对重要性,或者隐含指明所指示的技术特征的数量。由此,除非另有说明,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征;“多个”的含义是两个或两个以上。另外,“上”、“下”、“左”、“右”、“竖直”、“水平”、等指示的方位或位置关系的术语,是基于附图所示的方位或相对位置关系描述的,仅是为了便于描述本申请的简化描述,而不是指示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本申请中的具体含义。

下面参考附图和可选的实施例对本申请作详细说明。

图1是本申请的显示面板的驱动电路的示意图,图2是本申请的像素的排列示意图,如图1-2所示,本申请公开了一种显示面板的驱动电路2,所述显示面板1包括多个像素10,每个所述像素10包括一个主像素11和一个辅像素12,同一所述像素10中的所述主像素11和所述辅像素12的发光颜色相同;所述驱动电路2包括设置在每个所述像素10内的主像素11驱动子电路和辅像素12驱动子电路,所述主像素11驱动子电路用于驱动所述主像素11内的发光单元发光,所述辅像素12驱动子电路用于驱动所述辅像素12内的发光单元发光;同一所述像素10内,所述主像素11驱动子电路和所述辅像素12驱动子电路连接同一条数据线60或同一条扫描线61;所述辅像素12的灰阶低于所述主像素11的灰阶。

本申请通过改变像素10设计,通过主像素11和辅像素12配合的方式,通过将主像素11和辅像素12设计为不同的灰阶,在不增加数据线60和扫描线61的情况下,分时对主像素11和辅像素12分别充入不同的数据电压,实现不同的灰阶显示。且在显示出现不真实的情况下,可通过调整辅像素12的电压,即调整辅像素12的灰阶亮度,对该像素10的亮度进行提升和降低,从而实现ACC调节,可实现更真实的色彩显示,也可满足不同的白平衡需求。相比于示例性技术中选择ACC和FRC的方案来说,本申请的方案更简单,实施起来更容易,而且能够达到实施ACC和FRC的方案相同的效果。且不需要时序控制器去完成ACC和FRC调节,相对来说释放了时序控制器的性能,成本更低。

参见图2所示,所述像素10包括红色像素R、绿色像素G和蓝色像素B等,红色像素R中包括红色主像素R2和红色辅像素R1,绿色像素G包括绿色主像素G2和绿色辅像素G1,蓝色像素B包括蓝色主像素B2和蓝色辅像素B1。本实施例中的红色像素有红色主像素和红色辅像素组成,其中,主像素11主要用于显示,而辅像素12可根据不同的显示效果,调整所需的驱动数据电压,从而让辅像素12显示不同灰阶,对主像素11进行补偿。本实施例中的红色主像素11和红色辅像素12可以左右排列或上下排列。

具体地,所述主像素11的面积大于所述辅像素12的面积。在实际显示中,其显示主要靠主像素11进行显示,将辅像素12的面积设置得稍小,例如在主像素11的二分之一至三分之一的范围内,不仅可以起到到主像素11的辅助作用,又不会因为辅像素12占用过大显示区面积造成亮度不足的问题。在本实施例中,进一步的可将红色主像素11、绿色主像素11和蓝色主像素11的面积设置为相同的,在实际中,由于不同颜色的像素10的实际亮度不同,而示例性技术中往往把各不同颜色像素10设置为不同大小,来实现更真实的色彩显示。但是在本实施例中,可将各颜色的主像素11的面积设置成相同的,通过调节辅像素12的灰阶,进而实现对主像素11的像素10亮度补偿。本实施例还可将各颜色的辅像素12设置的面积不同,进而使得辅像素12具有不同的补偿能力。

为了降低显示面板1的成本,且增加辅像素12后不增加显示面板1的数据线60和扫描线61的数量,本实施例可在同一所述像素10内,所述主像素11驱动子电路和所述辅像素12驱动子电路连接同一条数据线60和同一条扫描线61;具体包括:

所述主像素11驱动子电路包括:第一数据输入电路21、第一电容电路22、第一驱动电路232和主发光单元24;所述第一数据输入电路21接入所述扫描线61上的扫描信号和所述数据线60上的数据信号,并在所述扫描信号的控制下将所述数据信号传输至第一节点G1,所述第一电容电路22的一端连接所述第一节点G1,所述第一电容电路22的另一端连接第二节点S1,所述第二节点S1接入第一电源信号VDD;所述第一驱动电路232连接所述第一节点G1、所述第二节点S1和所述主发光单元24的一端,所述主发光单元24的另一端接入第二电源信号VDD;所述辅像素12驱动子电路包括:第二数据输入电路41、第二电容电路42、第二驱动电路432和辅发光单元44;所述第二数据输入电路41接入所述扫描线61上的扫描信号和所述数据线60上的数据信号,并在所述扫描信号的控制下将所述数据信号传输至第三节点G2,所述第二电容电路42的一端连接所述第三节点G2,所述第二电容电路42的另一端连接第四节点S2,所述第四节点S2接入所述第一电源信号;所述第二驱动电路432连接所述第三节点G2、所述第四节点S2和所述辅发光单元44的一端,所述辅发光单元44的另一端接入所述第二电源信号;当前行所述扫描线61在扫描时段中,所述扫描信号分为第一阶段和第二阶段,所述扫描信号在所述第一阶段为第一电平,所述扫描信号在所述第二阶段为第二电平,所述第一电平大于所述第二电平,所述第一数据输入电路21和所述第二数据输入电路41在所述第一阶段同时导通,所述第二数据输入电路41在所述第二阶段保持导通,所述第一数据输入电路21在所述第二阶段处于截止状态。

本实施例主要通过分时将不同电压的数据信号输入至辅像素12驱动电路2和主像素11驱动电路2中。主要利用的是第一输入电路和第二输入电路在第二阶段处于不同状态,从而使得第一阶段时为主像素11进行充电,在第二阶段时,为辅像素12进行充电。本实施例而言,减少了数据线60和扫描线61的使用,对原本的电路设计改进小,而且增大了像素10的开口率。

具体电路为:所述第一数据输入电路21包括第一主动开关T1,所述第二数据输入电路41包括第二主动开关T2,所述第一主动开关T1的控制端、输入端和所述第二主动开关T2的控制端、输入端分别连接同一条扫描线61和同一条数据线60;所述第一驱动电路232包括第一驱动晶体管Q1,所述第一驱动晶体管Q1的栅极连接所述第一节点,所述第二驱动电路432包括第二驱动晶体管Q2,所述第二驱动晶体管Q2的栅极连接所述第三节点;所述第一电容电路22包括第一电容C1,所述第二电容电路42包括第二电容C2,第一电容C1和第二电容C2的容量相同。在所述扫描信号处于所述第一阶段时,所述第一主动开关T1和所述第二主动开关T2导通;在所述扫描信号处于所述第二阶段时,所述第二主动开关T2保持导通,所述第一主动开关T1截止。

本实施例中,为了实现第二主动开关T2在第一阶段和第二阶段都能导通的目的,需要满足在当前行所述扫描线61处于扫描时段时,同一条数据线60上,所述数据信号在所述第一阶段的最小电平大于所述数据信号在所述第二阶段的最大电平;所述扫描信号在第二阶段的第二电平小于所述数据信号在所述第一阶段的最小电平。在第一阶段时,第一主动开关T1的Vgs大于第一主动开关T1的Vth,第二主动开关T2的Vgs大于第二主动开关T2的Vth。在第二阶段时,第一主动开关T1的Vgs小于第一主动开关T1的Vth,第二主动开关T2的Vgs仍然大于第二主动开关T2的Vth。即可实现在第一阶段时,第一主动开关T1和第二主动开关T2同时导通,在第二阶段时,第二主动开关T2导通,而第一主动开关T1截止。其中,第一主动开关T1和第二主动开关T2均为N型薄膜晶体管。

图3是本申请的当前像素10对应的扫描线61和数据线60的驱动时序示意图,参见图3所示,t1时段和t2时段为当前扫描线61对应的扫描时间,除t1和t2外的时段,例如t3时段为非扫描时段,此时,扫描线61上的电压为低电平VGL。在t1时刻,扫描线61上的扫描信号为第一电平VGH_H,数据线60上的数据信号为Data1;在t2时刻,扫描线61上的扫描信号为第二电平VGH_M,数据线60上的数据信号为Data2。

驱动电路2的驱动过程可包括三个阶段,在t1时段,扫描线61被送入第一电平VGH_H的扫描信号,此时第一主动开关T1的Vgs大于第一主动开关T1的Vth,第二主动开关T2的Vgs大于第二主动开关T2的Vth,第一主动开关T1和第二主动开关T2同时导通,主像素11的第一驱动晶体管Q1和辅像素12的第二驱动晶体管Q2的栅极被送入数据信号Data1,主发光单元24和辅发光单元44皆被点亮。但是这里不同的是,主发光单元24流入的是目标电流,而辅发光单元44流入的是非目标电流。但是由于t1的时间较短,此时辅发光单元44即使流入的是非目标电流,进而是非目标亮度,对整体显示效果影响不大。在t2时段,扫描线61上的扫描信号降为第二电平VGH_M,此时第一主动开关T1的Vgs小于第一主动开关T1的Vth,第二主动开关T2的Vgs仍然大于第二主动开关T2的Vth,对应的,第二主动开关T2导通,而第一主动开关T1截止。此时,数据线60上的数据信号为Data2,第二驱动晶体管Q2的栅极被送入数据信号Data2,第二驱动晶体管Q2流过的电流受Data2控制,此时辅发光单元44流入目标电流。在t2时段内,主发光单元24有第一电容C1维持电压。在t3时段内,扫描线61上的电压下降至VGL,第一主动开关T1和第二主动开关T2皆处于截止状态,第一驱动晶体管Q1和第二驱动晶体管Q2通过第一电容C1和第二电容C2维持该帧的主发光单元24和辅发光单元44的亮度,直到下一帧刷新。

需要说明的是本申请的驱动电路2是在最基础的2T1C驱动电路2上实现的,当然,本申请的思路并不限于最基础的2T1C电路,对于有阈值电压补偿,迁移率补偿,供电电压VDD补偿的驱动电路2同样适用。

具体为在当前行所述扫描线61处于扫描时段时,为实现T1在两个不同VGH下能正常开启和关闭,需满足data2(max)<data1(min),且VGH_M<data1(min)。例如可以在同一条数据线60上,所述数据信号在所述第一阶段为15-25V,所述数据信号在所述第二阶段为0-10V,所述第一电平为30V±2V,所述第二电平为15V±2V,所述扫描信号的截止电平为-5V。

具体地,所述第一驱动晶体管Q1和所述第二驱动晶体的沟道的宽长比不同,所述第一驱动晶体管Q1的饱和区工作电压范围为15-25V,所述第二驱动晶体管Q2的饱和区工作电压范围为0-10V。

需要理解的是,第一驱动晶体管Q1和第二驱动晶体管Q2需要在不同的数据信号(Data1、Data2)驱动下。如上述,第一驱动晶体管Q1在15-25V的驱动下,第二驱动晶体管Q2在0-10V的驱动下。具体可根据TFT饱和区漏源电流公式:

具体地,所述驱动电路2在以第一状态驱动时,所述主像素11的灰阶在0-255范围内,所述辅像素12的灰阶在0-127范围内;所述驱动电路2以第二状态驱动时,所述主像素11的灰阶在0-255范围内,所述辅像素12的灰阶在0-255范围内。

本实施例中,驱动电路2的第一状态指调节前的显示状态,是主像素11正常显示0-255灰阶,辅像素12的显示灰阶为0-127灰阶进行显示。此处为举例,辅灰阶最大值可根据实际情况进行调整,但为了能向上调节主像素11在255灰阶显示时的像素10亮度,不可将辅像素12的灰阶的最大值设置为255,此时无法提升辅像素12的灰阶。第二状态则是通过调节,使得以主像素11的灰阶在0-255范围内,所述辅像素12的灰阶在0-255范围内进行显示。可通过调节显示亮度时即类似ACC调节时,根据光学量测gamma曲线数据,改变辅像素12的充电data电压,可向上向下调整辅像素12灰阶,使得辅像素12超出127灰阶进行显示,以使得主像素11和辅像素12的亮度和达到需求亮度即可。

在另一实施例中,每个所述像素10还包括一个主像素11,两个所述主像素11和一个所述辅像素12构成一个像素10;两个所述主像素11连接同一条扫描线61或同一条数据线60。本实施例中,主要通过两个相邻的主像素11共用一个辅像素12的设计,例如上下排列设置的主像素11、辅像素12、主像素11设置,或左右排列的主像素11、辅像素12、主像素11设计。其中两个主像素11可以连接不同的数据线60相同的扫描线61或不同的扫描线61相同的数据线60。其驱动方式如上述提及的相同,采用分时为辅像素12提供数据电压的方式,在此不再进行赘述。本实施例中,减少了辅像素12的数量,从而提升了显示质量。

图4是本申请的显示面板1的示意图,参见图4所示,本申请还公开了一种显示面板1,包括上述的显示面板1的驱动电路2。本申请通过重新设计辅像素12和主像素11,并分时对其进行充电,改变辅像素12的data灰阶,可实现OLED面板的亮度向上向下补偿,实现ACC功能,且该设计电路不会增加数据线60和扫描线61,避免产生的额外成本。且该方法不需要FRC提升色深,减少了时序控制器的处理时间,亦可降低时序控制器的制作成本。

需要说明的是,本申请的发明构思可以形成非常多的实施例,但是申请文件的篇幅有限,无法一一列出,因而,在不相冲突的前提下,以上描述的各实施例之间或各技术特征之间可以任意组合形成新的实施例,各实施例或技术特征组合之后,将会增强原有的技术效果。

以上内容是结合具体的可选实施方式对本申请所作的进一步详细说明,不能认定本申请的具体实施只局限于这些说明。对于本申请所属技术领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本申请的保护范围。

- 一种显示面板的驱动电路和显示面板

- 一种栅极驱动电路及其驱动方法、显示面板、显示装置

- 一种驱动电路、驱动方法、显示面板和显示装置

- 像素驱动电路、显示面板及其驱动方法和显示装置

- 一种显示面板的驱动电路、驱动方法及显示装置

- 阵列上栅极驱动器电路、AMOLED显示面板的像素电路、AMOLED显示面板以及驱动AMOLED显示面板的像素电路的方法

- 半导体晶体管的制造方法、使用了由该方法制造的半导体晶体管的驱动电路、包括该驱动电路和显示元件的像素电路、该像素电路配置成行列状的显示面板、以及具有该显示面板的显示装置