芯片装置

文献发布时间:2023-06-19 10:00:31

技术领域

本发明涉及一种芯片装置,特别涉及一种通信器中的芯片装置。

背景技术

电子芯片装置在制造过程中容易产生裂痕(Crack),使得电子芯片装置的耦接状态不佳。此外,对于不同尺寸的通信器的需求,需要制作不同规格的电子芯片装置,使得成本增加。另外,电子芯片装置中的电容使电子芯片装置的所需面积增加。因此,要如何发展能够克服上述问题的相关技术为本领域重要的课题。

发明内容

本发明实施例包含一种芯片装置,包括电感、芯片与第一焊垫区。电感用以接收信号。芯片用以依据信号进行操作。第一焊垫区包括第一导电电极、第二导电电极与第三导电电极。第一导电电极位于一第一导电层,并耦接电感。第二导电电极位于一第二导电层。第三导电电极位于一第三导电层,并用以与第二导电电极共同形成至少一第一电容。第二导电层是配置于第一导电层与第三导电层之间。

本发明实施例还包含一种芯片装置,包括电感、芯片、第一电容、第二电容、至少一第一导线、至少一第二导线、至少一第三导线与至少一第四导线。电感用以接收信号。芯片用以依据信号进行操作。第二电容的第一端耦接电感,第二电容的第二端与第一电容的第一端共用导电电极。至少一第一导线耦接第一电容的第一端,并且用以沿第一方向延伸。至少一第二导线耦接第一电容的第一端,并且用以沿不同于第一方向的第二方向延伸。至少一第三导线耦接第一电容的第二端,并且用以沿第一方向延伸。至少一第四导线耦接第一电容的第二端,并且用以沿第二方向延伸。

附图说明

图1为根据本公开的一实施例所示出的通信器的示意图。

图2为根据本公开的一实施例所示出的芯片装置的功能方框图。

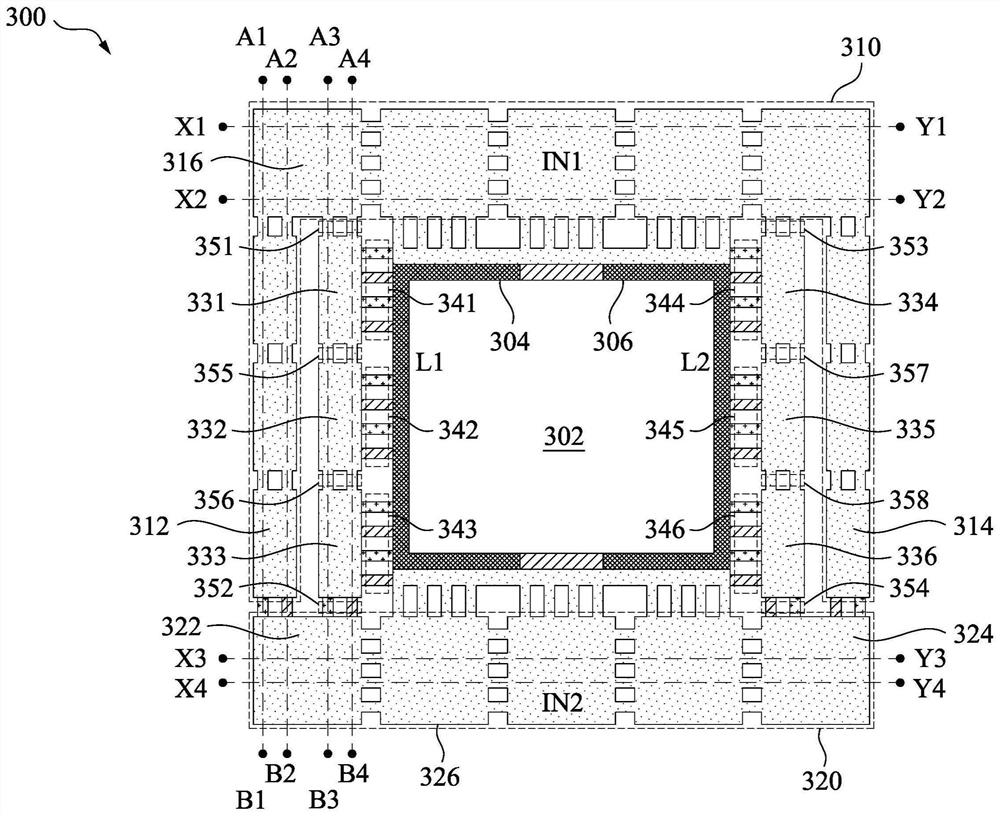

图3为根据本公开的一实施例所示出的芯片装置的结构示意图。

图4为根据本公开的一实施例所示出的芯片装置的结构示意图。

图5为根据本公开的一实施例所示出的芯片装置的结构示意图。

图6为根据本公开的一实施例所示出的芯片装置的结构示意图。

图7为根据本公开的一实施例所示出的芯片装置的结构示意图。

图8A至图8F为根据本公开的多个实施例所示出的芯片装置的剖面图。

附图标记说明:

100:通信器

102、106、601~604、701、702、807、808、817、818:区域

104、300、400、800、810、820、830、840、850:芯片装置

108:电感

S1、IN1、IN2:信号

202:调制器

204:整流器

206:直流转换器

208:负载

212、312、314、316、322、324、326:谐振电容

214:共用电容

216:稳压电容

251、252、253、254:节点

C1、C3:谐振电容值

C2、C4:稳压电容值

221、223、225、227、611~614、621~624、711~714、721~724:导线

VSS、VDD:参考电压信号

302:芯片

304、306:稳压电容

310、320:谐振电容组

331~336:共用电容

341~346、351~358、401~404、501~506:切割区

L1、L2:电源线

A1-B1~A4-B4、X1-Y1~X4-Y4:剖面线

M1~M3、M1'~M3'、802、804、806、812、814、816、822、824、826、832、834、836、842、844、846、852、854、856、806a、806b、816a、816b:导电电极

801、803、805、811、813、815、821、823、825、831、833、835、841、843、845、851、853、855:绝缘层

VA、VB1~VB3、VC1~VC4、VE1~VE5、VF1~VF5:通孔

具体实施方式

于本文中,当一元件被称为“连接”或“耦接”时,可指“电性连接”或“电性耦接”。“连接”或“耦接”亦可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、…等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。除非上下文清楚指明,否则该用语并非特别指称或暗示次序或顺位,亦非用以限定本发明。

除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括多个形式,包括“至少一个”。“或”表示“及/或”。如本文所使用的,术语“及/或”包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语“包括”及/或“包含”指定所述特征、区域、整体、步骤、操作、元件的存在及/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件及/或其组合的存在或添加。

以下将以附图公开本公开的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本公开。也就是说,在本公开内容部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些现有惯用的结构与元件在附图中将以简单示意的方式示出的。

图1为根据本公开的一实施例所示出的通信器的示意图。如图1所示,通信器100包含区域102、芯片装置104、区域106与电感108。在一些实施例中,电感108作为天线操作。举例来说,电感108用以接收如图2所示的信号S1,并且将信号S1传输至芯片装置104,使得芯片装置104可以依据信号S1进行操作。

在一些实施例中,电感108被布置在区域102中并且没有被布置在区域106中。在一些实施例中,电感108被禁止被布置在区域106中。在不同的实施例中,区域102与区域106具有不同的尺寸。在一些其他的实施例中,通信器100不包含区域106。

图2为根据本公开的一实施例所示出的芯片装置的功能方框图。如图2所示,芯片装置104耦接电感108。在一些实施例中,芯片装置104依据电感108接收的信号S1进行操作。

如图2所示,芯片装置104包含调制器(Modulator)202、整流器(Rectifier)204、直流转换器(DC-DC Converter)206、负载(Load)208、谐振电容212、共用电容214与稳压电容216。如图2所示,谐振电容212耦接于电感108与调制器202之间,调制器202与整流器204耦接于谐振电容212与稳压电容216之间,直流转换器206耦接于稳压电容216与负载208之间。

在一些实施例中,调制器202、整流器204与直流转换器206用以依据电感108接收的信号S1驱动负载208。在一些实施例中,谐振电容212用以依据电感108的电感值进行调整以使图1所示的通信器100达到所欲的谐振频率。在一些实施例中,稳压电容216用以存储电能以驱动芯片装置104。

在一些实施例中,谐振电容212的两端分别耦接电感108的两端。谐振电容212的一端用以接收信号IN1于节点251,谐振电容212的另一端用以接收信号IN2于节点252。在一些实施例中,稳压电容216的两端分别耦接整流器204的两端。稳压电容216的一端用以接收参考电压信号VDD于节点253,稳压电容216的另一端用以接收参考电压信号VSS于节点254。

在一些实施例中,共用电容214用以调整谐振电容212对应的谐振电容值C1或稳压电容216对应的稳压电容值C2。举例来说,当谐振电容212需要较大的谐振电容值C1时,共用电容214通过导线227与导线221与谐振电容212并联,以增加谐振电容值C1。此时导线223与导线225不导通。举另一例来说,当稳压电容216需要较大的稳压电容值C2时,共用电容214通过导线223与导线225与稳压电容216并联,以增加稳压电容值C2。此时导线221与导线227不导通。

在一些实施例中,调制器202、整流器204、直流转换器206与负载208被整合于芯片,例如图3中的芯片302中。在本发明实施例中,调制器202、整流器204、直流转换器206与负载208的配置方式并不限于上述实施例。调制器202、整流器204、直流转换器206与负载208其他配置方式亦在本公开思及的范围内。

图3为根据本公开的一实施例所示出的芯片装置的结构示意图。请参照图2与图3,芯片装置300为芯片装置104的实施例。如图3所示,芯片装置300包含芯片302、稳压电容304、306、谐振电容组310、320、共用电容331~336、切割区341~346与切割区351~358。在一些实施例中,谐振电容组310、320与共用电容331~336耦接天线,例如图2中的电感108,因此谐振电容组310、320与共用电容331~336被称为焊垫区。

请参照图2与图3,稳压电容304、306为稳压电容216的一实施例。谐振电容组310、320为谐振电容212的一实施例。共用电容331~336为共用电容214的一实施例。在一些实施例中,谐振电容组310、320分别用以接收信号IN1与信号IN2,对应节点251与252。在一些实施例中,稳压电容304、306为芯片302的电源线L1与L2的夹层电容。在一些实施例中,电源线L1与L2用以输出参考电压信号VDD与VSS。

在一些实施例中,芯片装置300的多个部件通过多条导线互相耦接,以降低裂痕(Crack)的影响。举例来说,如图3所示,谐振电容组310与芯片302之间具有多条导线,例如切割区341~346中的多条导线,使得当部分导线被裂痕影响时,芯片装置300能保持正常运行。

如图3所示,谐振电容组310包含谐振电容312、314与316,谐振电容组320包含谐振电容322、324与326。在一些实施例中,使用者通过检测谐振电容312至谐振电容314是否正常导通以确认谐振电容组310是否有异常。在一些实施例中,使用者通过检测谐振电容322至谐振电容324是否正常导通以确认谐振电容组320是否有异常。

在一些实施例中,共用电容331~336通过切割区341~346的多条导线耦接稳压电容304、306,以增加对应稳压电容304、306的稳压电容值C3(图未示)。在一些实施例中,共用电容331~336通过切割区351~354的导线耦接谐振电容组310、320,以增加对应谐振电容组310、320的谐振电容值C4(图未示)。在不同的实施例中,通过切割不同的切割区中的导线,共用电容331~336可以选择与稳压电容304、306并联或与谐振电容组310、320并联,以增加对应的稳压电容值C3或谐振电容值C4。在下方关于图4与图5的实施例有更详细的举例说明。

如图3所示,图3包含芯片装置300的剖面线A1-B1~A4-B4与X1-Y1~X4-Y4。剖面线A1-B1~A4-B4与X1-Y1~X4-Y4对应的剖面图在下方关于图8A至图8F的实施例有更详细的举例说明。

图4为根据本公开的一实施例所示出的芯片装置的结构示意图。请参照图3与图4,芯片装置400为芯片装置300的实施例。芯片装置400类似于芯片装置300,因此相同之处不再重复说明。芯片装置400与芯片装置300的不同之处在于,相较于芯片装置300包含切割区351~354,芯片装置400包含切割区401~404。

如图4所示,切割区401~404中的导线被切断,使得共用电容331~336不耦接谐振电容组310、320。此时,共用电容331~336通过切割区341~346中的导线耦接稳压电容304、306,使得共用电容331~336与稳压电容304、306并联,以增加对应的稳压电容值C3。

举例来说,若稳压电容304、306原本对应的电容值为39pF(皮法拉),而共用电容331~336对应的电容值为11pF,则对应的稳压电容值C3则为(39+11)pF,即50pF。

图5为根据本公开的一实施例所示出的芯片装置的结构示意图。请参照图3与图5,芯片装置500为芯片装置300的实施例。芯片装置500类似于芯片装置300,因此相同之处不再重复说明。芯片装置500与芯片装置300的不同之处在于,相较于芯片装置300包含切割区341~346,芯片装置500包含切割区501~506。

如图5所示,切割区501~506中的导线被切断,使得共用电容331~336不耦接稳压电容304、306。此时,共用电容331~336通过切割区341~346中的导线耦接谐振电容组310、320,使得共用电容331~336与谐振电容组310、320并联,以增加对应的谐振电容值C4。

举例来说,若谐振电容组310、320原本对应的电容值为100pF(皮法拉),而共用电容331~336对应的电容值为11pF,则对应的谐振电容值C4则为(100+11)pF,即111pF。

在一些实施例中,图4所示的切割区401~404与图5所示的切割区501~506的导线是通过激光切割法切断。

在本发明实施例中,共用电容331~336的配置方式并不限于上述实施例。共用电容331~336的其他数量或其他配置方式亦在本公开思及的范围内。

举例来说,请参照图3,在一些其他的实施例中,切割区351、341、355、352、354、358、344、345中对应的导线被切断,使得共用电容331不耦接谐振电容组310、320也不耦接稳压电容304、306,共用电容332、333、336不耦接谐振电容组310、320而耦接稳压电容304、306,共用电容334、335耦接谐振电容组310、320而不耦接稳压电容304、306。此时,谐振电容组310、320与两个共用电容334、335并联,而稳压电容304、306与三个共用电容332、333、336并联,因此共用电容331~336可以同时调整稳压电容304、306对应的稳压电容值C3与谐振电容组310、320对应的谐振电容值C4。举例来说若谐振电容组310、320原本对应的电容值为100pF,稳压电容304、306原本对应的电容值为39pF,而共用电容331~336中每一者对应的电容值为(11/6)pF,则稳压电容值C3为(39+11/2)pF,谐振电容值C4为(100+11/3)pF。

图6为根据本公开的一实施例所示出的芯片装置的结构示意图。请参照图3与图6,图6呈现谐振电容322及其周边的相关细节。如图6所示,谐振电容322由三层导电电极M1~M3构成。在一些实施例中,谐振电容322通过导电电极M3耦接天线,例如图2中的电感108,因此导电电极M3被视为焊垫区,而谐振电容322被视为与焊垫区共用导电电极M3的电容。

在一些实施例中,导电电极M1~M3分别位于三层不同的导电层。在一些实施例中,导电电极M1~M3在区域601~604互相重叠以形成夹层电容。在一些实施例中,导电电极M1包含导线611~614,导电电极M2包含导线621~624。在一些实施例中,导线613、623、614、624朝第一方向,例如图6所示的X方向延伸,导线611、621、612、622朝不同于第一方向的第二方向,例如图6所示的Y方向延伸。

请参照图3与图6,导线611、621耦接谐振电容312,切割区352中的导线612、622耦接共用电容333,导线613、623、614、624耦接谐振电容326。在一些实施例中,导线611、621分别用以接收信号IN1、IN2。

图7为根据本公开的一实施例所示出的芯片装置的结构示意图。请参照图3与图7,图7呈现共用电容331及其周边的相关细节。如图7所示,共用电容331由三层导电电极M1'~M3'构成。在一些实施例中,共用电容331通过导电电极M3'耦接天线,例如图2中的电感108,因此导电电极M3'被视为焊垫区,共用电容331被视为与焊垫区共用导电电极M3'的电容。

在一些实施例中,导电电极M1'~M3'分别位于三层不同的导电层。在一些实施例中,导电电极M1'~M3'在区域701、702互相重叠以形成夹层电容。在一些实施例中,导电电极M1'包含导线711~714,导电电极M2'包含导线721~724。在一些实施例中,导线713、723、714、724朝第一方向,例如图7所示的X方向延伸,导线711、721、712、722朝不同于第一方向的第二方向,例如图7所示的Y方向延伸。

请参照图3与图7,切割区351中的导线711、721耦接谐振电容316,切割区355中的导线712、722耦接共用电容332,导线713、723、714、724耦接稳压电容304。在一些实施例中,导线711、721分别用以接收信号IN1、IN2,导线712、722分别用以接收信号IN1、IN2。在一些实施例中,导线713、723分别用以接收参考电压信号VSS、VDD,导线714、724分别用以接收参考电压信号VSS、VDD。

图8A为根据本公开的一实施例所示出的芯片装置的剖面图。请参照图3与图8A,芯片装置800为芯片装置300的实施例,图8A示出的剖面图对应芯片装置300沿剖面线A1-B1或剖面线A3-B3的剖面图。如图8A所示,芯片装置800包含绝缘层801、803、805以及导电电极802、804、806以及区域807、808。在图8A所示的剖面图对应剖面线A3-B3时,区域807、808分别对应图3所示的切割区351、352。

请参照图6与图8A,在一些实施例中,导电电极802、804、806分别对应导电电极M1、M2、M3。如图8A所示,导电电极802、804、806构成对应图3所示的谐振电容组310、320以及共用电容331~333的多个夹层电容。

如图8A所示,导电电极806通过通孔VA耦接导电电极804。在一些实施例中,导电电极806包含导电电极806a、806b。导电电极806a用以接收信号IN1,导电电极806a用以接收信号IN2。

图8B为根据本公开的一实施例所示出的芯片装置的剖面图。请参照图3与图8B,芯片装置810为芯片装置300的实施例,图8B示出的剖面图对应芯片装置300沿剖面线A2-B2或剖面线A4-B4的剖面图。如图8B所示,芯片装置810包含绝缘层811、813、815以及导电电极812、814、816以及区域817、818。在图8B所示的剖面图对应剖面线A4-B4时,区域817、818分别对应图3所示的切割区351、352。

请参照图6与图8B,在一些实施例中,导电电极812、814、816分别对应导电电极M1、M2、M3。如图8B所示,导电电极812、814、816构成对应图3所示的谐振电容组310、320以及共用电容331~333的多个夹层电容。

如图8B所示,导电电极816通过通孔VB1、VB2耦接导电电极814,导电电极814通过通孔VB3耦接导电电极812。在一些实施例中,导电电极816包含导电电极816a、816b。导电电极816a用以接收信号IN1,导电电极816a用以接收信号IN2。

图8C为根据本公开的一实施例所示出的芯片装置的剖面图。请参照图3与图8C,芯片装置820为芯片装置300的实施例,图8C示出的剖面图对应芯片装置300沿剖面线X1-Y1的剖面图。如图8C所示,芯片装置820包含绝缘层821、823、825以及导电电极822、824、826。

请参照图6与图8C,在一些实施例中,导电电极822、824、826分别对应导电电极M1、M2、M3。如图8C所示,导电电极822、824、826构成对应图3所示的谐振电容组310、320的多个夹层电容。

如图8C所示,导电电极826通过通孔VC1、VC2耦接导电电极824,导电电极824通过通孔VC3、VC4耦接导电电极822。在一些实施例中,导电电极826用以接收信号IN1。

图8D为根据本公开的一实施例所示出的芯片装置的剖面图。请参照图3与图8D,芯片装置830为芯片装置300的实施例,图8D示出的剖面图对应芯片装置300沿剖面线X2-Y2的剖面图。如图8D所示,芯片装置830包含绝缘层831、833、835以及导电电极832、834、836。

请参照图6与图8D,在一些实施例中,导电电极832、834、836分别对应导电电极M1、M2、M3。如图8D所示,导电电极832、834、836构成对应图3所示的谐振电容组310、320的多个夹层电容。在一些实施例中,导电电极836用以接收信号IN1,导电电极834用以接收信号IN2。

图8E为根据本公开的一实施例所示出的芯片装置的剖面图。请参照图3与图8E,芯片装置840为芯片装置300的实施例,图8E示出的剖面图对应芯片装置300沿剖面线X4-Y4的剖面图。如图8E所示,芯片装置840包含绝缘层841、843、845以及导电电极842、844、846。

请参照图6与图8E,在一些实施例中,导电电极842、844、846分别对应导电电极M1、M2、M3。如图8E所示,导电电极842、844、846构成对应图3所示的谐振电容组310、320的多个夹层电容。

如图8E所示,导电电极846通过通孔VE1~VE5耦接导电电极844。在一些实施例中,导电电极846用以接收信号IN2,而导电电极842用以接收信号IN1。

图8F为根据本公开的一实施例所示出的芯片装置的剖面图。请参照图3与图8F,芯片装置850为芯片装置300的实施例,图8F示出的剖面图对应芯片装置300沿剖面线X3-Y3的剖面图。如图8F所示,芯片装置850包含绝缘层851、853、855以及导电电极852、854、856。

请参照图6与图8F,在一些实施例中,导电电极852、854、856分别对应导电电极M1、M2、M3。如图8F所示,导电电极852、854、856构成对应图3所示的谐振电容组310、320的多个夹层电容。

如图8F所示,导电电极856通过通孔VF1~VF5耦接导电电极854。在一些实施例中,导电电极856用以接收信号IN2,而导电电极852用以接收信号IN1。

在先前的作法中,电感所接触的导电电极通过单一通孔与其他导电电极耦接,使得电感与导电电极接触面的面积阻抗较大。相较于上述作法,本发明实施例中,电感耦接的导电电极具有多个通孔以降低电感与导电电极之间的面积阻抗。例如图8F所示出的实施例中,与电感108耦接的导电电极856具有多个通孔VF1~VF5,以降低电感108与导电电极856之间的面积阻抗。

综上所述,在本发明实施例中,谐振电容212与共用电容214包含焊垫区中的导电电极(例如谐振电容322中的导电电极M1~M3)的夹层电容,使得通信器100的所需面积降低。此外,如图3所示实施例中,共用电容331~336可以依据通信器100的需求选择增加稳压电容值C3或谐振电容值C4。另外,芯片装置300中的部件通过多条导线互相耦接,例如共用电容331~336通过切割区341~346的多条导线耦接稳压电容304、306,可以降低裂痕对芯片装置300的影响。

虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的构思和范围内,当可作些许的变动与润饰,故本发明的保护范围当视权利要求所界定者为准。

- 芯片拾取装置、芯片拾取方法、芯片剥离装置和芯片剥离方法

- 芯片卡模块装置、芯片卡装置和用于制造芯片卡装置的方法