多赫蒂放大器

文献发布时间:2023-06-19 10:18:07

技术领域

本发明涉及将2个放大器收纳在1个封装的多赫蒂放大器。

背景技术

在移动体通信中,发送用功率放大器一般要求高效率且低失真。另外,为了应对近年的高速且大容量的通信,使用高PAPR(Peak Average Power Ratio:峰值平均功率比)的调制波信号。在将高PAPR的信号通过功率放大器放大的情况下,为了满足失真的标准,使功率放大器以相对于饱和输出功率取回退(back off)的低平均输出功率工作。一般回退量和效率是相反的关系,因此使用高PAPR的情况下不能够期待高效率。能够解决该问题的被称为多赫蒂放大器的放大器以通信用基站为中心被广泛采用。

在多赫蒂放大器中,使用λ/4线路将偏置为AB级或者B级的主放大器、和偏置为C级的峰值放大器并列地合成。在一方的放大器的输出配置λ/4线路。在另一方的放大器的输入也配置λ/4线路。在大信号输入时,由于2个放大器相同地工作以同相被合成,因此显示与2合成放大器相同的特性,能够实现大饱和输出功率。另一方面,在小信号输入时,由于仅主放大器工作,且在主放大器的输出侧连接的λ/4线路作为阻抗变换器发挥功能,因此通过高负荷阻抗能够得到高效率。因此,多赫蒂放大器能够在宽输出功率范围内实现高效率。

多赫蒂放大器由于使用2个放大器,因此为了小型化,优选将2个放大器收纳在一个封装。另一方面,如果将多赫蒂放大器整体集成化,那么特性的微调困难。因此,优选仅将2个放大器和匹配电路的一部分收纳在封装,将能够调整的部分设置在封装外。但是,在邻接的输入端子间或者输出端子间的电磁耦合影响器件特性。认为这是因为与使用2组将1个放大器收纳在1个封装的半导体器件来构成多赫蒂放大器的情况比较,除了端子间距离缩短之外,在邻接的端子间通过的信号具有90度的相位差引起的。对于该问题提出了在封装内设置电屏蔽的方法,但电屏蔽的尺寸对小型化带来限制。另外,还提出将多赫蒂放大器的除分配电路和合成电路以外的部分全部封装化的方案(例如,参照专利文献1)。

专利文献1:日本特开2005-303771号公报

通过将除分配电路和合成电路以外的部分全部封装化,能够抑制电磁耦合,但如上所述存在特性的微调困难的问题。

发明内容

本发明为解决上述课题而完成,其目的在于得到抑制电磁耦合,并且能够容易地进行特性的微调的多赫蒂放大器。

本发明所涉及的多赫蒂放大器的特征在于具备:封装,具有相互邻接的第1输入端子和第2输入端子、以及相互邻接的第1输出端子和第2输出端子;第1输入匹配电路、第1延迟电路、第2输入匹配电路、第1放大器以及第1输出匹配电路,在上述封装的内部依次连接在上述第1输入端子与上述第1输出端子之间;第3输入匹配电路、第2放大器、第2输出匹配电路、第2延迟电路以及第3输出匹配电路,在上述封装的内部依次连接在上述第2输入端子与上述第2输出端子之间;以及第1匹配电路至第4匹配电路,在上述封装的外侧分别连接在上述第1输入端子、上述第2输入端子、上述第1输出端子以及上述第2输出端子。

在本发明中,将延迟电路内置在封装内,因此能够使封装的输入端子间和输出端子间的相位同相。由此,能够抑制因小型封装而产生的电磁耦合。另外,通过封装的外侧的匹配电路能够容易地进行多赫蒂放大器的特性的微调。

附图说明

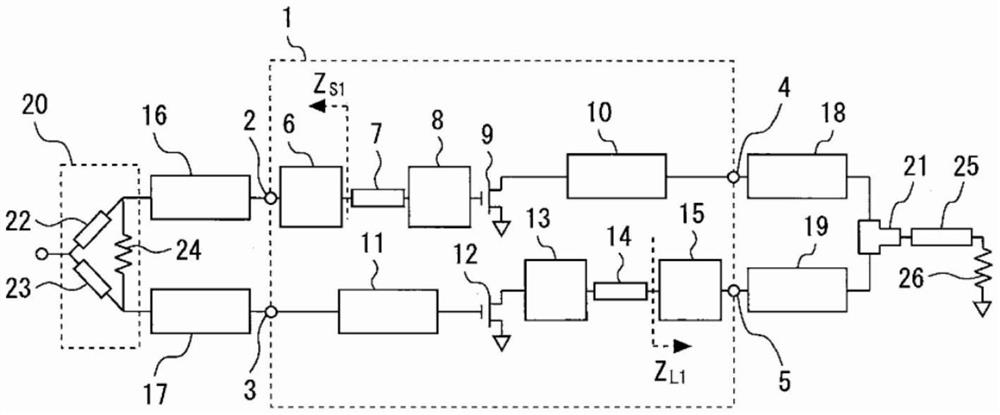

图1是表示实施方式1所涉及的多赫蒂放大器的图。

图2是表示实施方式1所涉及的多赫蒂放大器的封装的俯视图。

图3是表示实施方式1所涉及的多赫蒂放大器的封装的剖视图。

图4是表示实施方式1所涉及的第2放大器的输出匹配电路的阻抗变换的图。

图5是表示比较例所涉及的多赫蒂放大器的电路图。

图6是表示比较例所涉及的多赫蒂放大器的漏极效率的计算结果的图。

图7是表示比较例所涉及的多赫蒂放大器的增益的计算结果的图。

图8是表示实施方式1所涉及的多赫蒂放大器的漏极效率的计算结果的图。

图9是表示实施方式1所涉及的多赫蒂放大器的增益的计算结果的图。

图10是表示对端子间距离相对于饱和输出功率的影响进行计算的结果的图。

图11是表示改变延迟电路的电长度对实施方式1所涉及的多赫蒂放大器的饱和输出功率进行计算的结果的图。

图12是表示实施方式2所涉及的多赫蒂放大器的封装内部的等效电路图。

图13是表示实施方式2所涉及的多赫蒂放大器的封装内部的布局的俯视图。

图14是表示实施方式2所涉及的第2放大器的输出匹配电路的阻抗变换的图。

图15是表示实施方式3所涉及的多赫蒂放大器的图。

图16是表示实施方式3所涉及的多赫蒂放大器的封装内部的等效电路图。

图17是表示实施方式3所涉及的第1放大器的输出匹配电路的阻抗变换的图。

图18是表示实施方式3所涉及的第2放大器的输出匹配电路的阻抗变换的图。

具体实施方式

参照附图对实施方式所涉及的多赫蒂放大器进行说明。存在对相同的或者对应的构成要素标注相同的附图标记而省略重复说明的情况。

实施方式1

图1是表示实施方式1所涉及的多赫蒂放大器的图。封装1具有相互邻接的第1和第2输入端子2、3,与相互邻接的第1和第2输出端子4、5。

在封装1的内部且在第1输入端子2与第1输出端子4之间依次连接有第1输入匹配电路6、第1延迟电路7、第2输入匹配电路8、第1放大器9以及第1输出匹配电路10。在封装1的内部且在第2输入端子3与第2输出端子5之间依次连接有第3输入匹配电路11、第2放大器12、第2输出匹配电路13、第2延迟电路14以及第3输出匹配电路15。

第1放大器9和第2放大器12例如是GaN-HEMT。第1放大器9偏置为AB级或者B级。第2放大器12偏置为C级。在第1放大器9的栅极连接有第2输入匹配电路8等,在漏极连接有第1输出匹配电路10。在第2放大器12的栅极连接有第3输入匹配电路11,在漏极连接有第2输出匹配电路13等。

在封装1的外侧且在第1输入端子2、第2输入端子3、第1输出端子4以及第2输出端子5分别连接有第1至第4匹配电路16~19。在第1和第2匹配电路16、17也可以包括栅极偏置电路。在第3和第4匹配电路18、19也可以包括漏极偏置电路。

在封装1的外侧还设置有分配电路20和合成电路21。分配电路20将输入信号以同相位等分配为2个,分别经由第1和第2匹配电路16、17向第1和第2输入端子2、3输入。分配电路20是具有微带线(microstrip line)22、23和100Ω的电阻24的威尔金森分配电路,微带线22、23其特性阻抗是70.71Ω且具有输入信号的波长λ的1/4的电长度。

合成电路21将从第1和第2输出端子4、5经由第3和第4匹配电路18、19输入的信号合成为1个。在合成电路21的输出连接有匹配电路25和负荷26。负荷26的电阻值一般是50Ω。匹配电路25是特性阻抗为35.36Ω且具有输入信号的波长λ的1/4的电长度的微带线。

封装1的内部的电路例如由在介电常数是3~4且厚度是20~30mil左右的树脂基板上形成的金属图案和SMD(Surface Mount Device:表面贴装器件)部件而构成。封装1的内部的匹配电路由接合线的电感、MIM(Metal Insulator Metal:金属绝缘体金属)电容器、或者在介电常数为30~300的电介质基板上形成的微带线而构成。第1和第2延迟电路7、14是在介电常数为30~300的电介质基板上形成的微带线。

图2是表示实施方式1所涉及的多赫蒂放大器的封装的俯视图。图3是表示实施方式1所涉及的多赫蒂放大器的封装的剖视图。在散热片27之上安装有第1放大器9和第2放大器12等。第1和第2输入端子2、3,第1和第2输出端子4、5以及散热片27通过模制件28固定。但是,封装1并不局限于模制封装也可以是陶瓷封装。

第1至第3的输入匹配电路6、8、11与第1和第2匹配电路16、17设计为在大信号输入时信号能够向第1放大器9和第2放大器12的栅极无反射地输入。第1至第3输出匹配电路10、13、15与第3和第4匹配电路18、19设计为从第1放大器9和第2放大器12的漏极对输出侧进行观察的阻抗成为最佳负荷阻抗Z

从第1输入匹配电路6的输出端对输入侧进行观察的阻抗在输入信号的频率下为第1阻抗Z

从第1放大器9的漏极到合成电路21为止的匹配电路设计为通过相位在输入信号的频率下成为90度+180×N度(N是自然数)。另外,从第2放大器12的漏极到合成电路21的匹配电路设计为通过相位在输入信号的频率下成为0度+180×M(M是自然数)。这里对N=0,M=1的情况进行说明。通过这样设计,从合成电路21对第2放大器12侧进行观察的小信号时的阻抗是开放的。另外,第1放大器9的小信号时的负荷阻抗设定为比大信号时高2倍的阻抗。

图4是表示实施方式1所涉及的第2放大器的输出匹配电路的阻抗变换的图。通过第3输出匹配电路15和第4匹配电路19将阻抗从50Ω变换到Z

接着,将本实施方式的效果与比较例进行比较并说明。图5是表示比较例所涉及的多赫蒂放大器的电路图。在比较例中在封装1的外侧设置有第1延迟电路7和第2延迟电路14。第1延迟电路7和第2延迟电路14的微带线的特性阻抗是50Ω。因此,在封装1的第1和第2输入端子2、3间或者在第1和第2输出端子4、5间产生90度的相位差。因此,由路径间的干扰导致的影响大。

图6是表示比较例所涉及的多赫蒂放大器的漏极效率的计算结果的图。图7是表示比较例所涉及的多赫蒂放大器的增益的计算结果的图。粗线是端子间距离为1mm的情况,细线是端子间距离为100mm的情况。在比较例中,因端子间距离的缩小,可以确认饱和输出功率的降低、和回退时的效率降低。图8是表示实施方式1所涉及的多赫蒂放大器的漏极效率的计算结果的图。图9是表示实施方式1所涉及的多赫蒂放大器的增益的计算结果的图。在实施方式1中可以知道即使将端子间距离缩小到1mm特性也不会劣化。

图10是表示对端子间距离相对于饱和输出功率的影响进行计算的结果的图。横轴是端子间距离。纵轴是以能够忽略端子间的电磁耦合的端子间距离为100mm时的饱和输出功率为基准的饱和输出功率的相对变化。在比较例中,可以确认端子间距离小于大约10mm时观察到饱和输出的降低,在几毫米时大幅降低。另一方面,在实施方式1中,即使端子间距离是1mm,饱和输出功率的降低也微小。

图11是表示改变延迟电路的电长度对实施方式1所涉及的多赫蒂放大器的饱和输出功率进行计算的结果的图。横轴是以输入信号的1/4的电长度标准化的第1延迟电路7和第2延迟电路14的电长度。与一般的多赫蒂放大器相同地,第1延迟电路7和第2延迟电路14的电长度也可以不是严格的λ/4,只要在输入信号的波长λ的1/4±20%的范围内就能够期待相同的效果。

如以上说明,在本实施方式中,将延迟电路内置在封装内,因此能够使封装的输入端子间和输出端子间的相位同相。由此,能够抑制在小型封装产生的电磁耦合。另外,通过封装外侧的匹配电路能够容易地进行多赫蒂放大器的特性的微调。

实施方式2

图12是表示实施方式2所涉及的多赫蒂放大器的封装内部的等效电路图。图13是表示实施方式2所涉及的多赫蒂放大器的封装内部的布局的俯视图。与实施方式1不同,不是由微带线而是由集总参数(lumped parameter)来构成第1延迟电路7和第2延迟电路14。电感器29~36由接合线构成。电容器37~40是由在半导体基板上形成的MIM电容或者电介质基板上的金属图案和散热片构成的平行平板电容等。

与实施方式1的第2延迟电路14对应的是在串联连接的2个电感器35、36之间分路连接(shunt connected)电容器40的T型电路。图14是表示实施方式2所涉及的第2放大器的输出匹配电路的阻抗变换的图。该T型电路设计为不有助于阻抗变换,仅使通过相位延迟90度。相同地,与第1延迟电路7对应的是在串联接的2个电感器29、30之间分路连接电容器37的T型电路。

在实施方式1中由高介电常数基板构成第1延迟电路7和第2延迟电路14,但在实施方式2中由集总参数构成。因此,容易实现第1延迟电路7和第2延迟电路14的电路尺寸的小型化。另外,如图13所示,第1放大器9和第2放大器12的安装位置配置在相对于信号的行进方向不同的位置。因此,不仅能够抑制输入端子间和输出端子间的干涉,还能够抑制接合线间的干扰。

实施方式3

图15是表示实施方式3所涉及的多赫蒂放大器的图。在本实施方式中,在封装1的内部且在第1输入端子2与第1输出端子4之间依次连接有第1输入匹配电路41、第1放大器9以及第1输出匹配电路42。在封装1的内部且在第2输入端子3与第2输出端子5之间依次连接有第2输入匹配电路43、第2放大器12以及第2输出匹配电路44。

从第1输入端子2到第1放大器9的电长度在输入信号的波长λ的1/4±20%的范围内比从第2输入端子3到第2放大器12的电长度长。因此,第1输入匹配电路41使通过相位相对于第2输入匹配电路43延迟90度。

从第2放大器12到第2输出端子5的电长度在输入信号的波长λ的1/4±20%的范围内比从第1放大器9到第1输出端子4的电长度长。因此,第2输出匹配电路44使通过相位相对于第1输出匹配电路42延迟90度。

第2输出匹配电路44和第4匹配电路19与实施方式1相同地,设计为从第2放大器12的漏极端对输出进行观察的阻抗是最佳负荷阻抗Z

图16是表示实施方式3所涉及的多赫蒂放大器的封装内部的等效电路图。第1输入匹配电路41具有电感器45~47、电容器48以及微带线49。第2输入匹配电路43具有电感器50、51和电容器52。第1输出匹配电路42具有电感器53。第2输出匹配电路44具有电感器54、55和微带线56。

图17是表示实施方式3所涉及的第1放大器的输出匹配电路的阻抗变换的图。图18是表示实施方式3所涉及的第2放大器的输出匹配电路的阻抗变换的图。第1放大器9和第2放大器12都从50Ω阻抗变换到Z

实施方式1的第1延迟电路7和第2延迟电路14不有助于阻抗变换,但本实施方式的第1输入匹配电路41和第2输出匹配电路44有助于阻抗变换。因此,在实施方式1的效果的基础上,能够将阻抗变换多级化,因此能够期待广带域的特性。

附图标记说明

1…封装;2…第1输入端子;3…第2输入端子;4…第1输出端子;5…第2输出端子;6…第1输入匹配电路;7…第1延迟电路;8…第2输入匹配电路;9…第1放大器;10…第1输出匹配电路;11…第3输入匹配电路;12…第2放大器;13…第2输出匹配电路;14…第2延迟电路;15…第3输出匹配电路;16…第1匹配电路;17…第1匹配电路;18…第2匹配电路;19…第2匹配电路;20…分配电路;21…合成电路;29、30、35、36…电感器;37、40…电容器;41…第1输入匹配电路;42…第1输出匹配电路;43…第2输入匹配电路;44…第2输出匹配电路。

- 多赫蒂放大器和多赫蒂放大电路

- 陶赫蒂Doherty电路、多路陶赫蒂Doherty电路和基站设备