用于磁传感器的时序控制电路及应用系统

文献发布时间:2023-06-19 10:18:07

技术领域

本发明涉及传感器控制电路领域,具体涉及用于磁传感器的时序控制电路及应用系统。

背景技术

当前,各向异形磁阻(Anisotropic Magneto Resistance,AMR)效应是铁磁材料中的电阻率随磁化强度(外加磁场)和电流方向的改变而变化的现象,基于这一效应制作的磁阻传感器由于灵敏度高,便于集成化等优点得到了广泛的应用;由于AMR开关芯片是用于检测磁场的有或无,只要响应灵敏,实时的检测并非必要,普通的磁信号检测的时序控制电路的架构,对于分频次数多,计数周期长的应用来说,需要的组合逻辑运算电路规模大,运算量大,中间过程易产生毛刺,功耗比较大。

本发明通过数字控制电路,使芯片中功耗较大的磁阻桥,比较器等模拟电路周期性的处于工作-睡眠-工作状态,通过采样的方法确定磁场的有或无,可以有效的降低芯片的功耗。

发明内容

本发明所要解决的技术问题是普通的磁信号检测的时序控制电路的架构,普通架构只有一个快时钟电路,对于分频次数多,计数周期长的应用来说,需要的组合逻辑运算电路规模大,运算量大,中间过程易产生毛刺,功耗比较大,目的在于提供用于磁传感器的时序控制电路,通过引入了快慢两套时钟电路,清晰的组合逻辑控制电路来解决上述问题。

本发明通过下述技术方案实现:

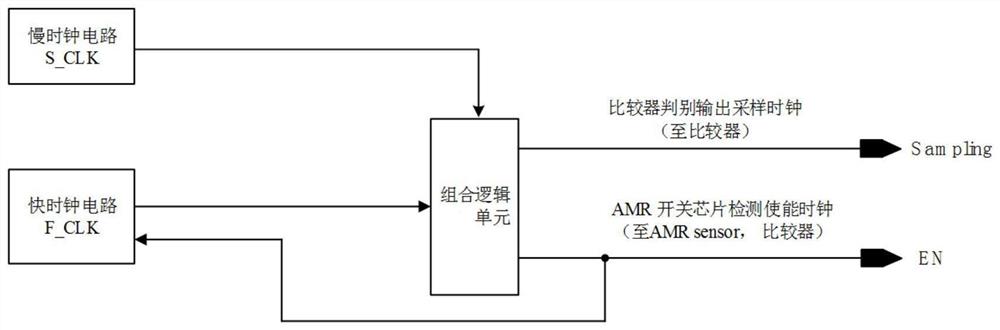

用于磁传感器的时序控制电路及应用系统,包括慢时钟电路、快时钟电路和组合逻辑单元,所述慢时钟电路控制组合逻辑单元,所述快时钟电路同时控制并响应于组合逻辑单元;其中,所述快时钟电路的输出F_CLK信号端连接组合逻辑单元的CLK_1端子,所述快时钟电路的输入EN信号端连接组合逻辑单元的EN输出端子;所述慢时钟电路的输出S_CLK信号端连接组合逻辑单元的CLK_2端子;所述POR信号端连接组合逻辑单元的POR端子,所述组合逻辑单元的Sampling端和EN端输出Sampling信号和EN信号,所述EN信号为高电平时,所述磁传感器芯片处于正常工作状态;所述EN信号用于控制磁传感器芯片中的开关器处于时序工作,所述Sampling信号用于对磁传感器芯片中的比较器的输出结果进行采样;通过数字控制电路,使芯片中功耗较大的快时钟电路,磁阻桥,比较器等模拟电路周期性的处于工作-睡眠-工作状态,通过采样的方法确定磁场的有或无,可以有效的降低芯片的功耗。

进一步,所述组合逻辑单元包括:与门And1、与门And3、与门And4、计数器、D类触发器DFF6、延时器Delay buffer1、延时器Delay buffer2、驱动缓冲器Driver buffer1和反相器INV1。

进一步,所述与门And1、与门And3和与门And4为二输入与门And。

进一步,所述时钟信号CLK_1端和POR信号端分别连接二输入与门AND1的输入端子,所述二输入与门AND1的输出端连接计数器的输入IN端子,所述计数器的输出为Sampling信号,所述计数器的输出端OUT接第一个延时缓冲器delay buffer1的输入端,所述delay buffer1的输出端连接二个延时缓冲器delay buffer2的输入端,所述第二个延时缓冲器delay buffer2的输出端和POR信号端连接二输入与门AND3,所述二输入与门AND3的输出端连接反相器INV1的输入端;反相器INV1的输出端连接复位信号Reset端,所述计数器Reset端子连接Reset信号端;所述POR信号端和时钟CLK_2信号端连接二输入与门AND4,所述二输入与门AND4的输出端连接D类触发器DFF6的输入时钟CLK端子,所述D类触发器DFF6的D输入端子连接电源VDD,所述D类触发器DFF6的Q输出端子连接驱动缓冲器driverbuffer1的输入端,所述驱动缓冲器driver buffer1的输出端连接EN信号端,所述D类触发器DFF6的CLR端子连接Reset信号端,所述D类触发器DFF6的

进一步,所述计数器包括D类触发器DFF1、D类触发器DFF2、D类触发器DFF3、D类触发器DFF4、D类触发器DFF5和二输入与门And2;所述输入IN信号端接D类触发器DFF1的输入时钟CLK端子,所述D类触发器DFF1的D输入端子接D类触发器DFF1的

其中,第三触发器DFF3的输出Q端子和第五触发器DFF5的输出Q端子分别接第二个二输入与门AND2的输入端子,构成一个模12的计数器;所述D类触发器DFF1、DFF2、DFF3、DFF4、DFF5的复位CLR端子同时连接Rest信号端。

进一步,用于磁传感器的时序控制电路的应用系统,包括时序控制电路和磁阻信号处理电路,所述磁阻信号处理电路响应于时序控制电路发出的使能信号EN和采样信号Sampling。

进一步,所述延时器Delay buffer1和延时器Delay buffer2由级联的偶数延时反相器串接构成,各级联反向器的尺寸根据延时需要设计其尺寸大小,所述驱动缓冲器Driver buffer1由级联的偶数驱动反相器串接构成,各级联反向器的尺寸根据驱动负载需要设计其尺寸大小,所述慢时钟的周期根据芯片的工作-睡眠周期来设计为1个慢时钟周期,其构成方式可以是基于RC充放电和比较器的架构来实现,快时钟其构成方式可以是基于RC充放电和比较器的架构来实现;其周期根据芯片的工作时间,组合逻辑的计数灵活设置。

本发明与现有技术相比,具有如下的优点和有益效果:

本发明用于磁传感器的时序控制电路,所述磁信号检测的时序控制电路引入了快慢两套时钟电路,组合逻辑运算量小,慢时钟电路工作电流低,快时钟工作时间短,有效的降低了开关芯片的功耗,另外组合逻辑控制电路逻辑清晰,运算量小,不易产生毛刺信号,可扩展性和实用性强。

附图说明

此处所说明的附图用来提供对本发明实施例的进一步理解,构成本申请的一部分,并不构成对本发明实施例的限定。在附图中:

图1为本发明芯片时序控制电路框架结构示意图。

图2为本发明控制电路结构示意图。

图3为本发明组合逻辑单元结构示意图。

图4为本发明计数器结构示意图。

图5为本发明芯片工作时序图。

图6为本发明芯片内部结构示意图。

图7为现有技术芯片内部结构示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本发明作进一步的详细说明,本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对本发明的限定。

在以下描述中,为了提供对本发明的透彻理解阐述了大量特定细节。然而,对于本领域普通技术人员显而易见的是:不必采用这些特定细节来实行本发明。在其他实例中,为了避免混淆本发明,未具体描述公知的结构、电路、材料或方法。

在整个说明书中,对“一个实施例”、“实施例”、“一个示例”或“示例”的提及意味着:结合该实施例或示例描述的特定特征、结构或特性被包含在本发明至少一个实施例中。因此,在整个说明书的各个地方出现的短语“一个实施例”、“实施例”、“一个示例”或“示例”不一定都指同一实施例或示例。此外,可以以任何适当的组合和、或子组合将特定的特征、结构或特性组合在一个或多个实施例或示例中。此外,本领域普通技术人员应当理解,在此提供的示图都是为了说明的目的,并且示图不一定是按比例绘制的。这里使用的术语“和/或”包括一个或多个相关列出的项目的任何和所有组合。

在本发明的描述中,需要理解的是,术语“前”、“后”、“左”、“右”、“上”、“下”、“竖直”、“水平”、“高”、“低”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明保护范围的限制。

实施例

如图1所示,本发明用于磁传感器的时序控制电路及应用系统,采用快慢两套时钟发生器,芯片采用工作-睡眠的方式,将芯片中功耗较大的快时钟电路,磁阻桥,比较器等模拟电路周期性的处于工作-睡眠-工作状态,通过采样的方法确定磁场的有或无。慢时钟电路工作电流极低,快时钟电路工作时间短,这样可以有效降低芯片的功耗,可以应用于各种磁阻开关芯片。芯片的工作--睡眠整个时间周期由慢时钟决定。芯片的工作时间及采样时间由慢时钟,快时钟,组合逻辑运算得到,所述电路包括快慢两套时钟电路,组合逻辑运算单元。本实施例中,为了阐明控制电路的工作方法,假定芯片的工作-睡眠周期设定为1个慢时钟周期,其中工作状态为12个快时钟周期,采样时间由单个延时单元的延时时间乘以延时单元个数设置,其后的时间芯片处于睡眠状态如图5所示。

上述所说的慢时钟的周期根据芯片的工作-睡眠周期来设计为1个慢时钟周期,其构成方式可以是基于RC充放电和比较器的架构来实现。

上述所说的快时钟其构成方式可以是基于RC充放电和比较器的架构来实现;其周期根据芯片的工作时间,组合逻辑的计数灵活设置。

上述所说组合逻辑运算单元为如图2所述,所述组合逻辑单元包括:与门And1、与门And3、与门And4、计数器、D类触发器DFF6、延时器Delay buffer1、延时器Delay buffer2、驱动缓冲器Driver buffer1和反相器INV1;所述与门And1、与门And3和与门And4为二输入与门And。

进一步,所述时钟信号CLK_1端和POR信号端分别连接二输入与门AND1的输入端子,所述二输入与门AND1的输出端连接计数器的输入IN端子,所述计数器的输出为Sampling信号,所述计数器的输出端OUT接第一个延时缓冲器delay buffer1的输入端,所述delay buffer1的输出端连接二个延时缓冲器delay buffer2的输入端,所述第二个延时缓冲器delay buffer2的输出端和POR信号端连接二输入与门AND3,所述二输入与门AND3的输出端连接反相器INV1的输入端;反相器INV1的输出端连接复位信号Reset端,所述计数器Reset端子连接Reset信号端;所述POR信号端和时钟CLK_2信号端连接二输入与门AND4,所述二输入与门AND4的输出端连接D类触发器DFF6的输入时钟CLK端子,所述D类触发器DFF6的D输入端子连接电源VDD,所述D类触发器DFF6的Q输出端子连接驱动缓冲器driverbuffer1的输入端,所述驱动缓冲器driver buffer1的输出端连接EN信号端,所述D类触发器DFF6的CLR端子(复位端)连接Reset信号端,所述D类触发器DFF6的

进一步,如图3所述,所述计数器包括D类触发器DFF1、D类触发器DFF2、D类触发器DFF3、D类触发器DFF4、D类触发器DFF5和二输入与门And2;所述输入IN信号端接D类触发器DFF1的输入时钟CLK端子,所述D类触发器DFF1的D输入端子接D类触发器DFF1的

其中,第三触发器DFF3的输出Q端子和第五触发器DFF5的输出Q端子分别接第二个二输入与门AND2的输入端子,构成一个模12的计数器;所述D类触发器DFF1、DFF2、DFF3、DFF4、DFF5的复位CLR端子同时连接Reset信号端。

进一步,延时缓存器delay buffer由级联的偶数延时反相器串接构成,各级联延时反相器其具体构成可由倒比管反相器加上RC器件构成。

进一步,驱动缓冲器driver buffer由级联的奇数反相器串联构成,各级联反向器的尺寸可由正比管反相器构成,根据驱动的负载大小设计驱动级联数,级联比例倍数。

可以理解:如图6所示,该时序控制电路及工作方法引入了快慢两套时钟电路,组合逻辑运算量小,慢时钟电路工作电流低,快时钟工作时间短,有效的降低了开关芯片的功耗,另外组合逻辑控制电路逻辑清晰,运算量小,不易产生毛刺信号,可扩展性和实用性强。

各模块之间的连接方式见图2。快时钟电路的输出F_CLK信号接组合逻辑单元的CLK_1端子,快时钟电路的输入EN信号接组合逻辑单元的EN输出端子;慢时钟电路的输出S_CLK信号接组合逻辑单元的CLK_2端子;POR信号(来自上电复位模块,上电复位模块这里不详细描述。)接组合逻辑运算单元的POR端子,组合逻辑运算单元输出Sampling,EN,reset信号。

一种信号检测时序控制电路工作方法,包含以下步骤:

①慢时钟的周期数根据芯片的工作-睡眠周期来构建。

②计数器的构建根据芯片的工作周期为多少个快时钟振荡器时钟周期来设计,本实例中为12个快时钟周期,因此可以构建一个5Bit10100的计数器。

③Sampling信号维持时间的构建根据芯片的采样时间来合理设计delay buffer及其级联数目。

④快时钟电路根据芯片的工作时间来合理设计。

⑤将①,②,③,④中各模块进行组合运算得到芯片的工作-睡眠以及采样工作时序。

对比如图6和如图7所示,现有技术的时序控制电路的架构,对于分频次数多,计数周期长的应用来说,需要的组合逻辑运算电路规模大,运算量大,中间过程容易产生毛刺,功耗比较大;

本发明的时序控制电路的架构,采用快慢两套时钟发生器,芯片采用工作-睡眠的方式,将芯片中功耗较大的快时钟,磁阻桥,比较器等模拟电路周期性的处于工作-睡眠-工作状态,通过采样的方法确定磁场的有或无。慢时钟电路工作电流极低,快时钟电路工作时间短,这样可以有效降低芯片的功耗,可以应用于各种磁阻开关芯片。芯片的工作--睡眠整个时间周期由慢时钟决定;芯片的工作时间及采样时间由慢时钟,快时钟,组合逻辑运算得到,所述电路包括:

慢时钟电路:特点是时钟周期比较长,消耗的电流极低,用于设定芯片的工作—睡眠周期。

快时钟电路:特点是时钟周期时间短,通过组合逻辑设定快时钟和开关芯片的工作时间。

组合逻辑运算单元:用于产生磁传感器芯片的检测使能EN信号,快时钟的使能信号及比较器判别输出的采样Sampling信号。

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 用于磁传感器的时序控制电路及应用系统

- 时序控制电路及具有该时序控制电路的前端总线电源