非易失性存储器编程顺序

文献发布时间:2023-06-19 11:22:42

背景技术

许多电子装置利用嵌入式或以其它方式连接的存储装置。通常,嵌入式或连接的存储装置包含非易失性存储器。主机是指利用存储装置的装置。可将主机连接到存储装置,或可将存储装置嵌入于主机内。主机系统的实例包含智能电话、笔记本电脑、台式计算机、服务器、智能电器、数码相机、摄像机等。

即使在非易失性存储器未连接到电源(例如,电池)时,非易失性存储器也允许存储和保持信息。非易失性存储器的实例包含快闪存储器(例如,NAND型和NOR型快闪存储器)、电可擦除可编程只读存储器(EEPROM)等。使用基于半导体的非易失性存储器的存储装置的一个实例是固态装置(“SSD”)。

由于多种因素,从非易失性存储器回读的数据可能与最初编程的数据不同。存在帮助恢复此类情形的多种技术,包含在写入数据时计算错误校正码(ECC)并在从非易失性存储器读取数据时检查ECC。然而,此类技术可能是费时的且可能不会成功。

附图说明

编号相似的元件在不同图中指代共同组件。

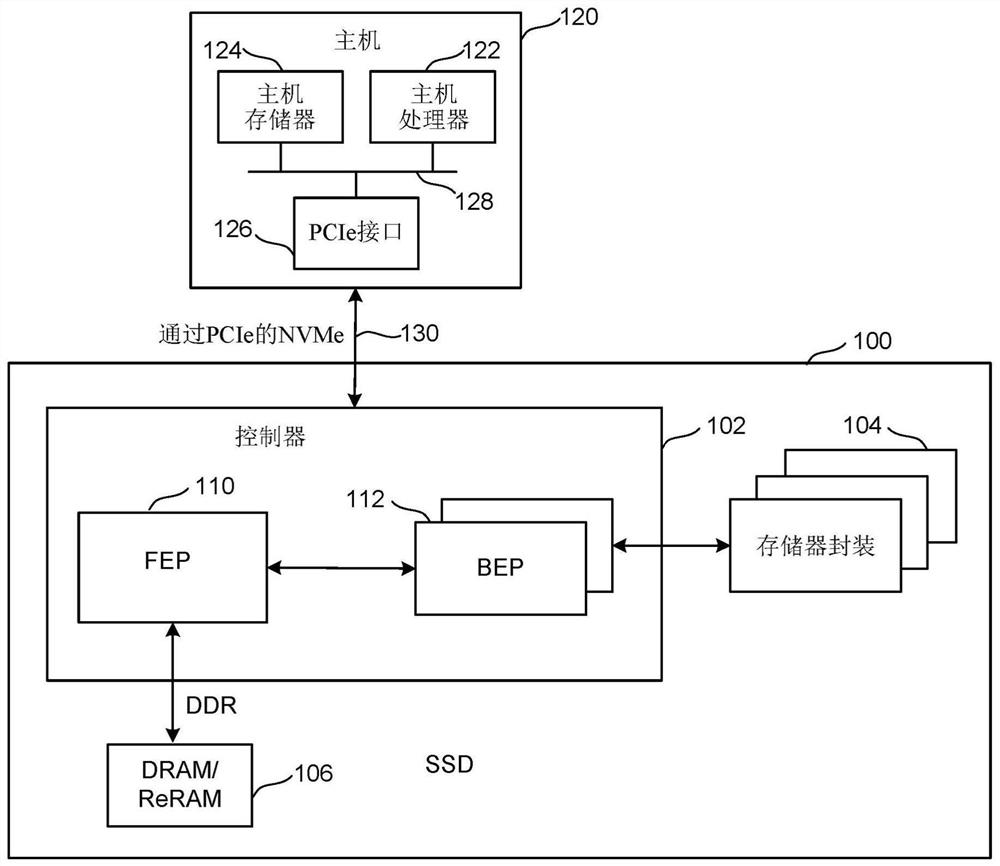

图1A是连接到主机的存储装置的一个实施例的框图。

图1B是前端处理器电路的一个实施例的框图。在一些实施例中,前端处理器电路是控制器的部分。

图1C是后端处理器电路的一个实施例的框图。在一些实施例中,后端处理器电路是控制器的部分。

图1D是存储器封装的一个实施例的框图。

图2是存储器裸片的一个实施例的框图。

图3是描绘非易失性存储器结构的细节的框图。

图4是包括图2的存储器结构326的示例3D配置中的块集合的存储装置的透视图。

图5A描绘图4的包含多个层的BLK0的一部分的示例横截面图。

图5B描绘图4的包含单一层的BLK0的一部分的示例横截面图。

图6描绘图5A的堆叠的区域524的近距视图。

图7A描绘与图5A的两层堆叠一致的3D配置中的子块中的NAND串的示例视图。

图7B描绘表示图7A的存储器单元或选择栅极晶体管中的任一个的示例晶体管。

图8描绘与图5和6到7A一致的BLK0中的控制栅极层。

图9A是存储器单元的数目对比阈值电压的曲线图,其中存储器单元各自存储三个位。

图9B描绘用于四状态存储器装置的阈值电压分布集合的一个实施例,其中每一存储元件存储两个数据位。

图9C是存储器单元的数目对比阈值电压的曲线图,其中每一存储元件存储单一数据位。

图10A描绘进行擦除操作的进程的一个实施例。

图10B是描述编程进程的一个实施例的流程图。

图11A和11B描绘具有粗糙阶段和精细阶段的多阶段编程操作的一个实例。

图12A和12B描绘多阶段编程操作的一个实例,其中将一个位存储在每一存储器单元每一阶段中。

图13是对非易失性存储器进行编程的进程的一个实施例的流程图,其包含改变字线的编程顺序。

图14是对非易失性存储器进行编程的进程的一个实施例的流程图,其包含相对于另字线集合而对字线集合使用不同的编程顺序。

图15A描绘可如何使用图14的进程来对元页进行编程的一个实例。

图15B和15C描绘用于对子块进行编程的两个可能顺序。

图15D描绘用于对存储器单元进行编程的可能顺序的实例。

图16描绘将元页编程到非易失性存储器中的进程的一个实施例的流程图。

图17是以不同顺序次序对NAND串进行编程的进程的一个实施例的流程图。

图18A是对下部层中的非易失性存储器单元进行编程的进程的一个实施例的流程图。

图18B是对上部层中的非易失性存储器单元进行编程的进程的一个实施例的流程图。

图19描绘以与另一三维存储器结构的层反转的顺序对一个三维存储器结构的一个层进行编程的进程的一个实施例的流程图。

图20是反转对NAND串进行编程的顺序的进程的一个实施例的流程图。

图21是反转对NAND串的一部分进行编程的顺序的进程的一个实施例的流程图。

图22A和22B描绘示出如何反转编程顺序可提供良好字线的更大连续信息块的表。

具体实施方式

提议用于编程非易失性存储器的技术,其中系统使用不同字线编程顺序以改进错误恢复。在一些实施例中,对字线集合进行编程的顺序随时间改变,其可改进错误恢复。在一些实施例中,变化是编程顺序的反转。在一些实施例中,以不同顺序对不同的字线集合进行编程,其可改进错误恢复。在一些实施例中,通过存储器裸片、存储器块(或“块”)和/或编程/擦除循环计数来改变(例如,反转)编程顺序。

非易失性存储系统中的基础存储单位是存储器单元。在一些存储装置中,存储器单元彼此结合,例如块或子块中的NAND串。每一NAND串包括串联连接于一个或多个漏极端选择栅极晶体管(被称作SGD晶体管)与一个或多个源极端选择栅极晶体管(被称作SGS晶体管)之间的多个存储器单元。SGD晶体管在连接到位线的NAND串的漏极端上。SGS晶体管在连接到源极线的NAND串的源极端上。此外,可将存储器单元与充当控制栅极的公共控制栅极线(例如,字线)一起布置。字线集合从块的源极端延伸到块的漏极端。存储器单元可以其它类型的串连接,并且还可以其它方式连接。

在三维(3D)存储器结构中,存储器单元可以布置成堆叠式的竖直NAND串,其中所述堆叠包括交替的导电和电介质层。导电层充当连接到存储器单元的字线。每一NAND串可具有与字线相交以形成存储器单元的柱形状。

在编程操作期间,根据字线编程顺序对存储器单元进行编程。举例来说,编程可以从块的源极侧的字线处开始,并前进到块的漏极端的字线。作为另一实例,编程可以在块的漏极端的字线处开始,并前进到块的源极侧的字线。本文中,短语“编程字线”意味着编程连接到字线的非易失性存储器单元。在一种方法中,在对物理邻接字线进行编程之前,对每一字线进行编程。字线可基于其物理位置以数字表示。举例来说,字线零(WL0)可以最接近于存储器单元块的一端,其中WL1紧接于WL0等。在一个可能字线编程顺序中,对第一字线WL0进行编程,接着对第二字线WL1进行编程等,直到对块中的最后一字线进行编程。编程操作可使用施加到对应的编程环或编程验证迭代中的字线的增大编程电压集合。还可以根据子块编程顺序对存储器单元进行编程,其中连接到字线的存储器单元是在一个子块进行编程,接着在下一子块中进行编程等。

本文中,短语“对字线集合进行编程”意味着对连接到所述集合中的第一字线的第一非易失性存储器单元进行编程,对连接到所述集合中的第二字线的第二非易失性存储器单元进行编程等。本文中,短语“以顺序次序对字线集合进行编程”意味着一次对一个字线进行编程,其中编程顺序从相同方向上的一个字线进行到紧相邻的字线。举例来说,可从WL0到WL95依序对字线进行编程。举例来说,顺序次序可以是WL0、WL1、WL2…WL94、WL95。并不需要从所述集合中的最低或最高编号字线开始顺序次序。举例来说,顺序次序可以是WL16、WL17…WL95、WL0、WL1…WL15。

每一存储器单元可以根据编程命令中的写入数据而与数据状态相关联。基于其数据状态,存储器单元将保持处于擦除状态或被编程为编程数据状态。举例来说,在每单元存储装置单一位(还被称作SLC或单层级单元)中,存在两个数据状态,包含已擦除状态和被编程状态。MLC或多层级单元作为多位存储器单元而每单元存储两个或更多个位。举例来说,在每单元存储装置两个位中,存在四种数据状态,包含已擦除状态和三个数据状态。在每单元存储装置三个位中,存在八种数据状态,包含已擦除状态和七个数据状态。

在一些实施例中,使用多阶段编程技术,其中编程操作包含多个阶段。多阶段编程技术的一个实例是在一个位编程到每一存储器单元每一阶段中时。在一些实施例中,在连接到字线的存储器单元上进行第一编程阶段,之后在连接到邻接字线的存储器单元上进行第一编程阶段,之后在连接到第一字线的存储器单元上进行第二编程阶段,之后在连接到第二字线的存储器单元上进行第二编程阶段。应注意,可仍在另一字线上进行第一编程阶段,随后在第二字线上进行第二编程阶段。本文中,此类多阶段编程技术被视为遵循依序字线编程顺序。在多阶段编程技术中,完成编程的阶段被称作最终阶段。

本文中公开用于改变编程顺序的技术。在一些实施例中,对字线集合进行编程的顺序随时间改变。举例来说,最初可以一种顺序对块或子块中的字线集合进行编程。在某一点处,可改变编程顺序。在一些实施例中,一个存储器块中的编程顺序与另一存储器块不同。第一和第二存储器块可以在相同存储器裸片上或在两个不同的存储器裸片上。

在一些实施例中,对字线集合进行编程的顺序随时间反转。举例来说,最初可在从块(或子块)的源极端到块(或子块)的漏极端的方向上依序对块或子块中的字线集合进行编程。在某一点处,可以反转编程顺序,使得可在从块(或子块)的漏极段到块(或子块)的源极端的方向上依序对字线集合进行编程。在一些实施例中,一个块中的编程顺序与另一块不同(例如,反转)。举例来说,可以从块的源极端到块的漏极端的顺序依序对第一块进行编程,且可在从块的漏极端到块的源极端的方向上对第二块进行编程。第一和第二块可以在相同存储器裸片上或在两个不同的存储器裸片上。

改变(例如,反转)字线集合的编程顺序可改进错误恢复。在一些情况下,当对字线集合进行编程时,其可以有利于错误恢复所述集合内早期进行编程的问题字线。问题字线的实例是相对于其它字线,对其进行编程更可能未通过的字线。在一个实施例中,改变(例如,反转)字线集合的编程顺序以将问题字线放置在所述顺序的较早处。在其它情况下,当对字线集合进行编程时,其可有利于错误恢复具有在所述顺序中随后进行编程的问题字线。在一个实施例中,改变(例如,反转)字线集合的编程顺序以将问题字线放置在所述顺序中的较晚处。在编程顺序中较早或较晚具有问题字线是否是优选的可能取决于所使用的错误恢复技术。

相对于对另字线集合进行编程的顺序而对字线集合使用不同编程顺序可改进错误恢复。在一个实施例中,存储器裸片集合中的一半具有以一种顺序进行编程的字线,而另一半以不同顺序进行编程。举例来说,存储器裸片集合中的一半具有以一种顺序次序进行编程的字线,而另一半以那个顺序次序的反转进行编程。如果例如基于在存储器裸片中对字线进行编程的顺序创建冗余数据,那么对不同的字线集合使用不同编程顺序(例如,反转)可有助于改进错误恢复。举例来说,备用存储器裸片可用于存储冗余数据,其可能由来自另一存储器裸片的按位互斥或(XOR)数据形成。使其数据进行异或运算(XORed)的字线集合(来自每一裸片的一个字线)可被称为磁条。冗余数据可能够从一个存储器裸片上的数据由于例如缺陷字线而无法读取的情况中恢复。然而,利用一些错误恢复技术,如果存在两个存储器裸片无法读取数据,那么冗余数据将不能够恢复数据。使用不同编程顺序可将问题字线放置到不同磁条中,其可降低由于两个问题字线处于同一磁条中所致的不可恢复的错误的几率。

图1A是连接到主机的存储装置的一个实施例的框图。存储装置100可实施本文中所提议的技术来反转依序编程顺序。许多不同类型的存储装置可以与本文中所提议的技术一起使用。一个示例存储装置是固态装置(SSD);然而,也可使用其它类型的存储装置。存储装置100包括控制器102、用于存储数据的非易失性存储器104和本地存储器(例如DRAM/ReRAM)106。在一个实施例中,本地存储器106是任选的。控制器102包括前端处理器电路(FEP)110和一个或多个后端处理器电路(BEP)112。在一个实施例中,FEP 110电路实施于ASIC上。在一个实施例中,每一BEP电路112实施于单独ASIC上。用于BEP电路112和FEP电路110中的每一个的ASIC实施于相同半导体上,使得将控制器102制造呈芯片上系统(SoC)形式。FEP 110和BEP 112都包含其自身处理器。在一个实施例中,FEP 110和BEP 112充当主从配置,其中FEP 110是主而每一BEP 112是从。举例来说,FEP电路110实施快闪转译层,其进行存储器管理(例如,垃圾收集、耗损均衡等)、逻辑到物理地址转译、与主机通信、DRAM(本地易失性存储器)的管理和SSD(或其它非易失性存储装置)的总体操作的管理。BEP电路112在FEP电路110的请求下管理存储器封装/裸片中的存储器操作。举例来说,BEP电路112可进行读取、擦除和编程进程。另外,BEP电路112可进行缓冲器管理、设定FEP电路110所需的特定电压层级、进行错误校正、控制到存储器封装的触发模式接口等。在一个实施例中,每一BEP电路112负责其自身的存储器封装集合。控制器102是控制电路的一个实例。

在一个实施例中,非易失性存储器104包括多个存储器封装。每一存储器封装包含一个或多个存储器裸片。因此,将控制器102连接到一个或多个非易失性存储器裸片。在一个实施例中,存储器封装104中的每一存储器裸片利用NAND快闪存储器(包含二维NAND快闪存储器和/或三维NAND快闪存储器)。在其它实施例中,存储器封装可包含其它类型的存储器。

控制器102经由接口130与主机120通信,所述接口130通过PCI高速(PCIe)实施NVM高速(NVMe)。为与存储装置100一起工作,主机120包含主机处理器122、主机存储器124和连接到总线128的PCIe接口126。主机存储器124是主机的物理存储器,且可以是DRAM、SRAM、非易失性存储器或另一类型的存储器。主机120在存储装置100外部且与其分离。在一个实施例中,存储装置100嵌入于主机120中。

图1B是FEP电路110的一个实施例的框图。图1B展示PCIe接口150与主机120通信且主机处理器152与所述PCIe接口通信。主机处理器152可以是所属领域中已知的适用于实施的任何类型的处理器。主机处理器152与芯片上网络(NOC)154通信。NOC是集成电路上的通信子系统,通常在SoC的内核之间。NOC可跨越同步和异步时钟域或使用无时钟异步逻辑。NOC技术将联网理论和方法应用于芯片上通信,且带来优于常规总线和横杆互连件的显著改进。相较于其它设计,NOC改进SoC的可扩展性和复杂SoC的功率效率。NOC的线和链路由多个信号共享。由于NOC中的所有链路可同时对不同数据包进行操作,因此实现高层级并行度。因此,随着集成子系统的复杂度不断增加,相比于先前通信架构(例如,专用点对点信号线、共享总线或具有桥接器的分段总线),NOC提供增强的性能(例如吞吐量)和可扩展性。NOC 154连接到存储器处理器156、SRAM 160和DRAM控制器162并与其通信。DRAM控制器162用于操作DRAM(例如,DRAM 106)并与其通信。SRAM 160是由存储器处理器156使用的本地RAM存储器。存储器处理器156用于运行FEP电路并进行多种存储器操作。NOC还与两个PCIe接口164和166通信。在图1B的实施例中,SSD控制器将包含两个BEP电路112;因此,存在两个PCIe接口164/166。每一PCIe接口与BEP电路112中的一个通信。在其它实施例中,可存在大于小于两个BEP电路112;因此,可存在超过两个PCIe接口。

图1C是BEP电路112的一个实施例的框图。图1C展示用于与FEP电路110通信(例如,与图1B的PCIe接口164和166中的一个通信)的PCIe接口200。PCIe接口200与两个NOC(芯片上网路)202和204通信。在一个实施例中,可将两个NOC合并为一个较大NOC。通过XOR引擎(224/254)和ECC引擎(226/256)将每一NOC(202/204)连接到SRAM(230/260)、缓冲器(232/262)、处理器(220/250)以及数据路径控制器(222/252)。ECC引擎226/256用于进行错误校正,如所属领域中已知。XOR引擎224/254用于XOR数据,使得数据可经合并且以可在存在UECC失效的情况下恢复的方式存储。在一个实施例中,XOR引擎224/254形成不同数据页的按位XOR。可将XOR结果存储于存储器封装104中。在ECC引擎226/256不能够成功地校正从存储器封装104回读的数据页中的所有错误的情况下,可以从存储器封装104存取所存储的XOR结果。随后可基于所存储XOR结果恢复数据页,连同用于形成XOR结果的其它数据页。

将数据路径控制器222连接到接口模块以用过四个通道来与存储器封装通信。因此,顶部NOC 202与用于与存储器封装通信的四个频道的接口228相关联,且底部NOC 204与用于与存储器封装通信的四个额外的通道的接口258相关联。每一接口228/258包含四个触发模式接口(TM接口)、四个缓冲器以及四个调度器。存在用于通道中的每一个的一个调度器、缓冲器以及TM接口。处理器可以是所属领域中已知的任何标准处理器。数据路径控制器222/252可以是处理器、FPGA、微处理器或其它类型的控制器。XOR引擎224/254和ECC引擎226/256是专用硬件电路,被称为硬件加速器。在其它实施例中,XOR引擎224/254和ECC引擎226/256可以实施于软件中。调度器、缓冲器以及TM接口是硬件电路。

接口228/258(单独或组合地)可被称为存储器接口,其配置成连接到非易失性存储器(例如,存储器封装104)。处理器220/250、数据路径控制器222/252、XOR224/254、ECC226/256中的一个或多个的组合在本文中可以被称为处理器电路。缓冲器232/262、SRAM230/260和/或NOC 202/204也可被视为处理器电路的一部分。

图1D是存储器封装104的一个实施例的框图,所述存储器封装104包含连接到存储器总线(数据线和芯片启用线)294的多个存储器裸片300。存储器总线294连接到触发模式接口296用于与BEP电路112TM接口通信(参看例如图1C)。在一些实施例中,存储器封装可包含连接到存储器总线和TM接口的较小控制器。存储器封装可具有一个或多个存储器裸片。在一个实施例中,每一存储器封装包含八个或16个存储器裸片;然而,也可实施其它数目的存储器裸片。本文所述的技术不限于任何特定数目的存储器裸片。

图2是存储器裸片300的一个实施例的功能框图。图1D的一个或多个存储器裸片300中的每一个可实施为图2的存储器裸片300。图2中描绘的组件为电路。在一个实施例中,每一存储器裸片300包含控制电路310、存储器结构326以及读取/写入电路328,以上所有都是电路。存储器结构326可通过行解码器324由字线定址且通过列解码器332由位线定址。读取/写入电路328包含多个感测块350(包含SB1、SB2、…、SBp)(感测电路),且允许并行地读取或编程多个存储器单元中的一页(或多页)数据。在一个实施例中,每一感测块包含连接到位线的感测放大器和锁存器集合。锁存器存储待写入的数据和/或已读取的数据。感测块包含位线驱动器。

通过存储器裸片接口318在控制器102与存储器裸片300之间传送命令和数据。存储器裸片接口318的实例包含触发模式接口和开放式NAND快闪接口(ONFI)。还可使用其它I/O接口。

控制电路310与读取/写入电路328协作以在存储器结构326上进行存储器操作(例如,写入、读取、擦除等)。在一个实施例中,控制电路310包含状态机312、芯片上地址解码器314以及功率控制模块316。状态机312提供存储器操作的裸片层级控制。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,控制电路310包含例如寄存器、ROM熔丝和其它存储装置的缓冲器,以用于存储例如基本电压和其它参数的默认值。可将默认值和其它参数存储在存储器结构326的区域中。

芯片上地址解码器314在由控制器102使用的地址与由解码器324和332使用的硬件地址之间提供地址接口。功率控制模块316控制在存储器操作期间供应到字线和位线的功率和电压。功率控制模块316可包含用于产生电压的电荷泵。

出于本文档的目的,控制电路310(单独或与读取/写入电路328和解码器324/332组合)包括连接到存储器结构326的控制电路。这种控制电路是进行下文流程图描述的功能的电路。在其它实施例中,控制电路可仅由为电路的控制器102(或其它控制器)以及进行下文流程图所描述的功能的软件(例如,固件)组成。在一个实施例中,控制电路是控制器,其中控制器是不使用硬件的电路。在另一替代方案中,控制电路包括进行下文流程图中所描述的作用的控制器102和控制电路310。在另一实施例中,控制电路包括单独或与控制器102组合的状态机312(和/或微控制器和/或微处理器)。在另一替代方案中,控制电路包括进行下文流程图中所描述的功能的控制器102、控制电路310、读取/写入电路328和解码器324/332。在其它实施例中,控制电路包括操作非易失性存储器的一个或多个电路。

在一个实施例中,存储器结构326包括非易失性存储器单元的单块三维存储器阵列,其中多个存储器层级形成于单一衬底(例如晶片)上方。存储器结构可包括在具有安置于硅(或其它类型的)衬底上方的有源区域的存储器单元阵列的一个或多个物理层级中单片式形成的任何类型的非易失性存储器。在一个实例中,存储器结构326的非易失性存储器单元包括具有电荷捕获材料的竖直NAND串,例如以全文引用的方式并入本文中的美国专利9,721,662中所描述。在另一实施例中,存储器结构326包括非易失性存储器单元的二维存储器阵列。在一个实例中,非易失性存储器单元是利用浮动栅极的NAND快闪存储器单元,例如描述于例如以全文引用的方式并入本文中的美国专利9,082,502中。还可使用其它类型的存储器单元(例如,NOR型快闪存储器)。

存储器结构326中包含的存储器阵列架构或存储器单元的确切类型不限于上述实例。许多不同类型的存储器阵列架构或存储器单元技术可用于形成存储器结构326。出于本文所提出的新要求保护的实施例的目的,不需要特定非易失性存储器技术。用于存储器结构326的存储器单元的合适技术的其它实例包含ReRAM存储器、磁阻存储器(例如MRAM、自旋转移力矩MRAM、自旋轨道力矩MRAM)、相变存储器(例如PCM)等。用于存储器结构326的架构的合适技术的实例包含二维阵列、三维阵列、交叉点阵列、堆叠式二维阵列、竖直位线阵列等。

ReRAM或PCMRAM交叉点存储器的一个实例包含以通过X线和Y线(例如字线和位线)存取的交叉点阵列布置的可逆电阻开关元件。在另一实施例中,存储器单元可包含导电桥接存储器元件。导电桥接存储器元件还可被称作可编程金属化单元。导电桥接存储器元件可基于固体电解质内离子的物理迁移而用作状态改变元件。在一些情况下,导电桥接存储器元件可包含两个固体金属电极,一个电极相对惰性(例如钨)且另一电极电化学活性(例如银或铜),两个电极之间具有固体电解质的薄膜。随着温度增大,离子的迁移率也增加,使得导电桥接存储器单元的编程阈值减小。因此,导电桥接存储器元件可具有随温度变化的广泛范围的编程阈值。

磁阻存储器(MRAM)通过磁性存储元件存储数据。所述元件由两个通过薄绝缘层分隔开的铁磁板形成,所述铁磁板中的每一个可保持磁化。两个板中的一个为设定成特定极性的永久磁体;另一板的磁化可改变以与存储存储器的外部场的磁化匹配。存储装置由此类存储器单元的网格建立。在一个关于编程的实施例中,每一存储器单元位于一对写入线之间,所述对写入线布置成彼此成直角、与单元平行、一条在单元上方且一条在单元下方。当电流通过所述对写入线时,产生感应磁场。

相变存储器(PCM)利用硫族化物玻璃的独特性质。一个实施例使用Ge

所属领域的普通技术人员将认识到,本文中所描述的技术不限于单一特定存储器结构,而是覆盖在如本文中所描述且如所属领域的普通技术人员所理解的本技术的精神和范围内的许多相关存储器结构。

图3描绘存储器结构326的实例。在一个实施例中,存储器结构326是划分成多个平面的存储器单元阵列。在图3中,将存储器结构326划分成两个平面:平面382和平面384。在其它实施例中,可使用多于或少于两个平面。在一些实施例中,将每一平面划分成多个存储器擦除块(例如,块0到1023,或另一量)。在某些存储器技术(例如2D/3D NAND和其它类型的快闪存储器)中,存储器擦除块(或“存储器块”或“块”)是用于擦除操作的存储器单元的最小单元。也就是说,每一擦除块含有在单一擦除操作中一起擦除的最小数目的存储器单元。也可使用其它擦除单位。在用于实施本文中所主张的解决方案的其它实施例的其它存储器技术(例如,MRAM、PCM等)中,存储器单元可以经覆写而无擦除操作且因此可能不存在擦除块。

每一存储器擦除块包含许多存储器单元。存储器擦除块的设计、大小和组织取决于针对存储器结构326的架构和设计。如本文中所用,存储器擦除块是共用字线和位线的连续的存储器单元集合;例如图3的擦除块i包含共用字线WL0_i、WL1_i、WL2_i和WL3_i且共用位线BL0到BL69,623的存储器单元。

在一个实施例中,存储器擦除块(参看块i)含有通过位线(例如,位线BL0到BL69,623)和字线(WL0、WL1、WL2、WL3)存取的NAND串集合。图3展示串联连接以形成NAND串的四个存储器单元。尽管描绘每一NAND串中包含四个单元,但可以使用多于或少于四个(例如,16、32、64、128、256或另一数目的存储器单元可以在NAND串上)。通过漏极选择栅极将NAND串的一个端子连接到对应位线,且通过源极选择栅极将另一端子连接到源极线。尽管图3展示69,624个位线,但也可使用不同数目个位线。

通常将每一存储器擦除块和/或每一存储器单元划分成多页。在一个实施例中,页是编程单位和读取单位。也可使用其它编程单位。通常将一个或多个数据页存储在一行存储器单元中举例来说,可以将一个或多个数据存储在连接到通用字线的存储器单元中。页包含用户数据和附加项数据(也被称为系统数据)。附加项数据通常包含已根据所述页的用户数据计算的标头信息和错误校正码(ECC)。控制器102(或其它组件)在将数据写入到阵列中时计算ECC以及在从阵列读取数据时检查所述ECC。在一个实施例中,页包含存储在连接到通用字线的所有存储器单元中的数据。

术语元块用以指包括多个物理块的逻辑构筑体。举例来说,元块可以由来自多个存储器裸片中的每一个的一个或多个物理块形成。在一些情况下,元块包含来自多个存储器裸片中的每一个的单一物理块。在一些情况下,元块可包含在单一存储器裸片上的超过一个物理块,例如当元块包含在存储器裸片上的用于每一平面的物理块。

存储于连接到通用字线的存储器单元中的数据页被称作物理页。在一些实施例中,以元页单位对数据进行编程。元页是包括多个物理页的逻辑构筑体。举例来说,元页可以由多个存储器裸片中的每一个上的一个或多个物理页形成。在一些情况下,元页包含来自多个存储器裸片中的每一个的单一物理页。在一些情况下,元页可在单一存储器裸片上包含超过一个物理页,例如在元页包含用于存储器裸片上的每一平面的物理页时。元页包括遍和可同时读取和编程的元块的所有物理页。

在上文所论述的实例中,擦除单位是存储器擦除块且编程和读取单位是页。也可使用其它操作单位。可一次一字节、1K字节、512K字节等存储/写入/编程、读取或擦除数据。本文所述的所主张解决方案不要求特定操作单位。在一些实例中,系统在相同操作单位下进行编程、擦除以及读取。在其它实施例中,系统在不同操作单位下进行编程、擦除以及读取。在一些实例中,系统进行编程/写入以及擦除,而在其它实例中,系统仅需要进行编程/写入,而不需要擦除,这是因为系统可进行编程/写入零和一(或其它数据值)且可能由此覆写先前存储的信息。

图4是包括图2的存储器结构326的示例3D配置中的块集合的存储装置400的透视图。衬底401上有存储器单元(存储元件)的示例块BLK0、BLK1、BLK2和BLK3以及具有供所述块使用的电路的外围区域。外围区域402沿着每一块的边缘延伸,而外围区域403在块集合的端部处。电路可包含电压驱动器,可将所述电压驱动器连接到块的控制栅极层、位线和源极线在一种方法中,共同驱动块中处于共同高度的控制栅极层。衬底401还可以承载块下方的电路和沿导电路径图案化以载送电路的信号的一个或多个下部金属层。块形成于存储装置的中间区域404中。在存储装置的上部区域405中,沿导电路径图案化一个或多个上部金属层以载送电路的信号。每一块包括存储器单元的堆叠区域,其中堆叠的交替层级表示字线。在一种可能的方法中,每一块具有相对的分层侧,竖直接触件从所述分层侧向上延伸到上部金属层以形成与导电路径的连接。虽然作为实例描绘了四个块,但可使用在x和/或y方向上延伸的两个或更多个块。

在一种可能的方法中,块在平面中,且所述平面在x方向上的长度表示到字线的信号路径在一个或多个上部金属层中延伸的方向(字线或SGD线方向),且所述平面在y方向上的宽度表示到位线的信号路径在一个或多个上部金属层中延伸的方向(位线方向)。z方向表示存储装置的高度。还可将块布置在多个平面中。

图5A描绘图4的包含NAND串502n和504n的BLK0的一部分的示例横截面图。块包括两个层中交替的导电和电介质层的堆叠506,所述两个层包含下部层508(例如,第一层或底层)和上部层510(例如,第二层或顶层)。所述层通过由电介质材料形成的接口(IF)(或接口区域或接头)分离。导电层包括SGS、WLDS、WL0到WL47、WLDL、WLDU、WL48到WL95、WLDD和SGD(0)。WLDS、WLDL、WLDU和WLDD是连接到没有资格存储用户数据的假存储器单元的假字线或导电层,WL0到WL47是连接到有资格存储用户数据的数据存储器单元的下部层中的数据字线或导电层,且WL48到WL95是上部层中的数据字线。仅作为实例,所述堆叠包含96个数据字线,且所述数据字线均匀地划分于两个层之间。DL是接口外部的示例电介质层,且DLIF是接口的电介质层。

沿着上部层的底部(或源极端)514、下部层的顶部(或漏极端)516和下部层的底部(或源极端)518和堆叠描绘了上部层的顶部(或漏极端)512和堆叠。每一层具有相对于NAND串的漏极端和源极端限定的漏极端和源极端。

WLDL和WLDU为邻接接口的未选定字线的实例,且WL0到WL47和WL48到WL95分别为下部层和上部层中非邻接接口的未选定字线的实例。

NAND串各自分别包括存储器孔520或522,所述存储器孔520或522填充有形成邻接字线的存储器单元的材料。举例来说,参见堆叠的区域524,其在图6中更详细地展示。存储器孔在本文中还可被称作柱。

堆叠形成于衬底526上。在一种方法中,阱区528是衬底中的n型源极扩散层或阱。阱区与块中的每一存储器单元串的源极端接触。在一个可能的实施方案中,n型阱区528又形成于p型阱区530中,所述p型阱区530又形成于n型阱区532中,所述n型阱区532又形成于p型半导体衬底534中。在一种方法中,n型源极扩散层可由平面中的所有块共享,且形成将电压提供到每一NAND串的源极端的源极线SL。

NAND串502n具有在堆叠506的底部538处的源极端536和在堆叠的顶部542处的漏极端540。可以跨堆叠周期性地提供金属填充的狭缝,作为延伸穿过堆叠的互连件,以便将源极线连接到堆叠上方的线。狭缝可在字线的形成期间使用且随后用金属填充。通孔可在一端连接到NAND串的漏极端且在另一端连接到位线。

在一种方法中,存储器单元块包括交替的控制栅极和电介质层的堆叠,且存储器单元布置在堆叠中的竖直延伸的存储器孔中。

在一种方法中,每个块包括阶状边缘,其中竖直互连件连接到每一层(包含SGS、WL和SGD层),且向上延伸到电压驱动器的水平路径。

绝缘填充区544将块分离成子块,其中NAND串502n和504n在不同子块中。

图5A描绘用于块具有多个层的实施例的块的一部分。并不需要块具有多个层。图5B描绘用于块具有单一层的实施例的块的一部分。图5B描绘两个NAND串552n和554n。块包括交替的导电和电介质层的堆叠556。导电层包括SGS、WLDS、WL0到WL95、WLDD和SGD(0)。

描绘了堆叠的顶部(或漏极端)562以及堆叠的底部(或源极端)568。在这个实施例中,堆叠可视为单一层,其中单一层具有相对于NAND串的漏极端和源极端限定的漏极端562和源极端568。

NAND串各自分别包括存储器孔570或572,所述存储器孔570或572填充有形成邻接字线的存储器单元的材料。

NAND串552n具有在堆叠556的底部568处的源极端586和在堆叠的顶部562处的漏极端590。可以跨堆叠周期性地提供金属填充的狭缝,作为延伸穿过堆叠的互连件,以便将源极线连接到堆叠上方的线。狭缝可在字线的形成期间使用且随后用金属填充。通孔可在一端连接到NAND串的漏极端且在另一端连接到位线。

绝缘填充区594将块分离成子块,其中NAND串552n和554n在不同子块中。

图6描绘图5A的堆叠的区域524的近距视图。区域包含接口下方的三个字线WL46、WL47和WLDL,以及接口上方的三个字线WLDU、WL48和WL49。一般来说,NAND串包括连接到对应的字线的存储器单元。这个实例包含分别连接到字线WL49、WL48、WLDU、WLDL、WL47和WL46的存储器单元602、604、606、608、610和612。字线或字线层由电介质层和DLIF间隔开,所述电介质层在接口外部各自具有厚度或高度d1(第一距离),所述DLIF在接口中具有更大厚度或高度d2(第二距离)。d1和d2也是单元间距离,或邻接存储器单元之间沿着z轴或竖轴的距离。在一种方法中,d2是高度d1的至少1.5到4倍。DLIF可为由电介质材料制成的聚合层,所述电介质材料沉积在彼此顶部上的一个或多个单独层中。接口的厚度或高度d2大于数据存储器单元之间的电介质层的高度。

存储器单元606连接到WLDU,且邻接接口并在接口上方。存储器单元608连接到WLDL,且邻接接口并在接口下方。这些存储器单元是接口存储器单元。第二距离横跨接口。在一些情况下,由于难以控制沿接口的通道区,因此可将存储器单元606和608设置为没有资格存储用户数据的假存储器单元。在这种情况下,WLDU和WLDL是假字线。

蚀刻穿过堆叠的每一层的存储器孔具有锥形形状,例如,在顶部较宽且在底部较窄。因此,下部层中的顶部字线层或存储器单元处的存储器孔直径dy大于上部层中的底部字线层或存储器单元处的存储器孔直径dx。直径dz表示存储器孔的最宽区域。这个加宽区域用于容纳上部层的存储器孔部分中相对于下部层中的存储器孔部分的较小未对准。所增加的DLIF厚度d2是由于进程容限问题而提供,且还通过在两个层中的存储器孔部分之间提供转换区来容纳未对准。因此,存储器孔的直径沿存储器孔的高度突然部分地变化。

可沿着存储器孔的侧壁沉积多个层或膜。所述层可符合接口中变化的直径。举例来说,所述层可包含阻断氧化物/块高k材料614、电荷捕获层616(例如,氮化硅(Si3N4)或其它氮化物)、隧穿层618(例如,氧化物)和通道620层(例如,多晶硅)。电介质芯622(例如二氧化硅)填充存储器孔的剩余部分。柱520或立柱可由存储器孔内的材料形成为NAND串的有源区域。参考WL49作为实例,字线层可包含金属阻障624和导电金属作为控制栅极。举例来说,提供控制栅极628、630、632、634、636和638。NAND串可视为具有浮体通道,因为通道的长度没有形成在衬底上。当对存储器单元进行编程时,将电子存储在与存储器单元相关联的电荷捕获层的一部分中。将这些电子从通道吸引到电荷捕获层中并穿过隧穿层。存储器单元的Vth与所存储的电荷量成比例地增加。在擦除操作期间,电子返回到通道。

图7A描绘与图5A的两层堆叠一致的3D配置中的子块中的NAND串的示例视图。每一子块包含彼此连接的多个NAND串或其它存储器单元集合,其中针对每一子块描绘一个示例NAND串。集合中的存储器单元可串行地彼此连接。举例来说,SB0、SB1、SB2和SB3分别包括示例NAND串502n、504n、706n和708n。在这个实例中,每一NAND串具有一个SGD晶体管、一个漏极侧假存储器单元、96个数据存储器单元(其中48个在接口IF上方,即,连接到WL48到WL95,且48个在接口下方,即,连接到WL0到WL47)、一个源极侧假存储器单元和一个SGS晶体管。

在块BLK0中,每一子块包括在x方向上延伸且具有共同SGD线的NAND串集合。NAND串502n、504n、706n和708n分别在子块SB0、SB1、SB2和SB3中。可一次在一个子块中进行块的编程。在每一子块内,可遵循依序字线编程顺序。举例来说,可从源极端到漏极端或替代地从漏极端到源极端对字线进行编程,一次一个字线。在一些实施例中,使用多阶段编程技术,其中在连接到字线的存储器单元上进行第一编程阶段,之后在连接到第二(邻接)字线的存储器单元上进行第一编程阶段,之后在连接到第一字线的存储器单元上进行第二编程阶段,之后在连接到第二字线的存储器单元上进行第二编程阶段。应注意,可仍在另一字线上进行第一编程阶段,随后在第二字线上进行第二编程阶段。本文中,此类多阶段编程技术被视为遵循依序字线编程顺序。在多阶段编程技术中,完成编程的阶段被称作最终阶段。

可以相同字线编程顺序或不同字线编程顺序对不同子块进行编程。举例来说,可从源极侧到漏极端依序对子块中的一个或多个的第一集合进行编程,且可从漏极端到源极侧依序对子块中的一个或多个的第二集合进行编程。子块的上部层和下部层可共用相同依序字线编程顺序,或具有不同依序字线编程顺序。举例来说,可从WL48到WL95依序对子块的上部层进行编程,且可从WL47到WL0依序对子块的下部层进行编程。

NAND串502n、504n、706n和708n分别具有通道712a、714a、716a和718a。每一通道可从源极端选择栅极晶体管连续延伸到漏极端选择栅极晶体管。

NAND串502n包含SGS晶体管721;源极侧假存储器单元722,连接到WLDS;下部层数据存储器单元723、724、725、726、727、728、729…612、610,连接到WL0到WL47;邻接接口的假存储器单元608和606,分别连接到WLDL和WLDU;上部层数据存储器单元604…735、736…737,连接到WL48到WL95;漏极侧假存储器单元738,连接到WLDD;和SGD晶体管739,连接到SGD(0)。

类似地,NAND串504n包含SGS晶体管741;源极侧假存储器单元742,连接到WLDS;下部层数据存储器单元743、744、745、746、747、748、749…750、751,连接到WL0到WL47;邻接接口的假存储器单元752和753,分别连接到WLDL和WLDU;上部层数据存储器单元754…755、756…757,连接到WL48到WL95;漏极侧假存储器单元758,连接到WLDD;和SGD晶体管759,连接到SGD(1)。

NAND串706n包含SGS晶体管761;源极侧假存储器单元762,连接到WLDS;下部层数据存储器单元763、764、765、766、767、768、769…770、771,连接到WL0到WL47;邻接接口的假存储器单元772和773,分别连接到WLDL和WLDU;上部层数据存储器单元774…775、776…777,连接到WL48到WL95;漏极侧假存储器单元778,连接到WLDD;和SGD晶体管779,连接到SGD(2)。

NAND串708n包含SGS晶体管781;源极侧假存储器单元782,连接到WLDS;下部层数据存储器单元783、784、785、786、787、788、789…790、791,连接到WL0到WL47;邻接接口的假存储器单元792和793,分别连接到WLDL和WLDU;上部层数据存储器单元794…795、796…797,连接到WL48到WL95;漏极侧假存储器单元798,连接到WLDD;和SGD晶体管799,连接到SGD(3)。

在这一实例中,假存储器单元606、753、773和793邻接接口且在接口上方,且假存储器单元608、752、772和792邻接接口且在接口下方。

选定子块是含有经读取或被编程的选定存储器单元的子块。如所提及,对于给定字线,可在读取操作中读取一个子块中的存储器单元。未选定子块是不含有经读取或被编程的选定存储器单元的子块。举例来说,在图7A中,如果SB0是选定子块,那么SB1到SB3是未选定子块。如果WLn=WL_sel=WL5,那么存储器单元728和连接到SB0中的WL5的其它存储器单元是选定存储器单元。存储器单元748、768和788和分别连接到SB1、SB2和SB3中的WL5的其它存储器单元是未选定存储器单元的实例。同样在这一实例中,存储器单元729、749、769和789和分别连接到SB0、SB1、SB2和SB3中的WLn+1=WL6的其它存储器单元是未选定存储器单元的实例,且存储器单元727、747、767和787和分别连接到SB0、SB1、SB2和SB3中的WLn-1=WL4的其它存储器单元是未选定存储器单元的实例。

图7B描绘表示图7A的存储器单元或选择栅极晶体管中的任一个的示例晶体管800。晶体管包括控制栅极CG、漏极D、源极S和通道CH,且可表示例如存储器单元或选择栅极晶体管。

图8描绘与图5A和6到7A一致的BLK0中的控制栅极层。控制栅极层布置在堆叠506中且包含层SGS、WLDS、WL0到WL47、WLDL、WLDU、WL48到WL95、WLDD和SGD(0)到SGD(3)。SGS控制栅极层是块所共有的。任选地,可针对每一子块提供单独SGS控制栅极层。另外,每一子块中描绘四个示例存储器孔。如所提及,选择栅极晶体管和存储器单元可沿着NAND串中的每一存储器孔形成。举例来说,SGD晶体管739、739a、739b和739c描绘于SGD0(0)中,且假存储器单元738描绘于WLDD中。

本文中所论述的存储器系统可经擦除、被编程以及读取。在成功编程进程结束时(经验证),存储器单元的阈值电压视需要应在经编程存储器单元的一个或多个阈值电压分布内或在经擦除存储器单元的阈值电压分布(范围)内。图9A示出存储三个数据位的MLC存储器单元的示例阈值电压分布(范围)。然而,其它实施例可使用每存储器单元其它数据容量(例如,每一存储器单元一个、两个、四个或五个数据位)。图9A展示八个阈值电压分布,对应于八个数据状态。第一阈值电压分布(数据状态)S0表示被擦除的存储器单元。系统使用擦除验证参考电压Vme来测试存储器单元是否经充分擦除。其它七个阈值电压分布(数据状态)S1到S7表示被编程的存储器单元,且因此也被称为经编程状态。每一阈值电压分布(数据状态)对应于数据位集合的预定值。编程到存储器单元中的数据与单元的阈值电压层级之间的特定关系取决于单元所采用的数据编码方案。在一个实施例中,使用格雷码(Graycode)分配将数据值分配给阈值电压范围,使得如果存储器的阈值电压错误地偏移到其相邻数据状态,那么仅会影响一个位。

图9A还展示用于从存储器单元读取数据的七个读取参考电压(也被称作读取比较电压)Vr1、Vr2、Vr3、Vr4、Vr5、Vr6和Vr7。通过测试(例如进行感测操作)给定存储器单元的阈值电压是否高于或低于所述七个读取参考电压,系统可确定存储器单元处于哪一数据状态(即,S0、S1、S2、S3、…)。

图9A还展示七个验证参考电压(也被称作编程验证目标)Vv1、Vv2、Vv3、Vv4、Vv5、Vv6和Vv7。在将存储器单元编程到数据状态S1时,系统将测试那些存储器单元是否具有大于或等于Vv1的阈值电压。在将存储器单元编程到数据状态S2时,系统将测试所述存储器单元是否具有大于或等于Vv2的阈值电压。在将存储器单元编程到数据状态S3时,系统将确定存储器单元是否具有大于或等于Vv3的阈值电压。在将存储器单元编程到数据状态S4时,系统将测试那些存储器单元是否具有大于或等于Vv4的阈值电压。在将存储器单元编程到数据状态S5时,系统将测试那些存储器单元是否具有大于或等于Vv5的阈值电压。在将存储器单元编程到数据状态S6时,系统将测试那些存储器单元是否具有大于或等于Vv6的阈值电压。在将存储器单元编程到数据状态S7时,系统将测试那些存储器单元是否具有大于或等于Vv7的阈值电压。图9A的示例电压是Vr1=0v、Vr2=1v、Vr3=2v、Vr4=3v、Vr5=4v、Vr6=5v、Vr7=6v、Vv1=0.4v、Vv2=1.4v、Vv3=2.4v、Vv4=3.4v、Vv5=4.4v和Vv6=5.4v、Vv7=6.4v。

在被称为全序列编程的一个实施例中,可将存储器单元从经擦除数据状态S0直接编程到经编程数据状态S1到S7中的任一个。举例来说,可首先擦除待进行编程的存储器单元群,使得所述群中的所有存储器单元都处于经擦除数据状态S0。随后,使用编程进程将存储器单元直接编程为数据状态S1、S2、S3、S4、S5、S6和/或S7。举例来说,在将一些存储器单元从数据状态S0编程到数据状态S1的同时,将其它存储器单元从数据状态S0编程到数据状态S2和/或从数据状态S0编程到数据状态S3等。图9A的箭头表示全序列编程。本文所描述的技术也可与除全序列编程以外的其它类型编程(包含但不限于多状态/多阶段编程)一起使用。在一些实施例中,数据状态S1到S7可重叠,其中控制器102依赖于ECC算法以识别正确数据。

图9B描绘用于四状态存储器装置的阈值电压分布集合的一个实施例,其中每一存储元件存储两个数据位。提供第一阈值电压(Vth)分布902用于经擦除(Er状态)存储元件。三个Vth分布904、906和908分别表示经编程状态A、B和C。在一个实施例中,Er状态下的阈值电压和A、B和C分布中的阈值电压是正值。在另一实施例中,用于Er状态的阈值电压分布是负值,而用于A状态、B状态和C状态分布的阈值电压分布是正值。

还提供三个读取参考电压Vra、Vrb和Vrc用于从存储元件读取数据。通过测试给定存储元件的阈值电压是否高于或低于Vra、Vrb和Vrc,系统可确定存储元件所处的状态,例如编程条件。

此外,提供三个验证参考电压Vva、Vvb和Vvc。当将存储元件编程到A状态、B状态或C状态时,系统将测试那些存储元件是否分别具有大于或等于Vva、Vvb或Vvc的阈值电压。

在图9B的实例中,多状态存储元件存储两个不同的页的数据:下部页和上部页。通过阈值电压分布902、904、906和908来描绘四种状态。这些状态和其表示的位是Er状态(11)、A状态(01)、B状态(00)和C状态(10)。对于Er状态,两个页存储“1”。对于A状态,下部页存储“1”且上部页存储“0”。对于B状态,两个页存储“0”,对于C状态,下部页存储“0”且上部页存储“1”。应注意,尽管已将特定位图案分配给所述状态中的每一个,但还可指派不同位图案。

图9C示出用于SLC存储器单元的示例阈值电压分布(范围)。如上文所论述,SLC存储器单元可经擦除或被编程。当经擦除时,SLC存储器单元具有在经擦除阈值电压分布(范围)E中的阈值电压。当被编程时,SLC存储器单元具有在被编程阈值电压分布(范围)P中的阈值电压。

图9C还展示读取参考电压(也被称作读取比较电压)Vrs、验证参考电压(也被称作编程验证目标)Vvs和擦除验证目标Vse。当从E到P进行编程时,系统使存储器单元的阈值电压升高直到其达到至少Vvs。当从P到E进行擦除时,系统使存储器单元的阈值电压降低直到其达到至少Vse。为读取存储SLC数据的存储器单元,系统测试存储器单元的阈值电压是否小于或大于Vrs。用于图9C的示例电压是Vse=Vr2=1v、Vrs=1.2v和Vvs=2.4v。

图10A描绘进行擦除操作的进程的一个实施例。关于非易失性存储器单元的NAND串来描述所述进程。NAND串包含在NAND串的每个端上选择晶体管。举例来说,第一选择晶体管可以是漏极侧选择晶体管,其具有耦合到位线的其端子中的一个(例如,漏极)。第二选择晶体管可以是源极侧选择晶体管,其具有耦合到源极线的其端子中的一个。所述进程可在许多NAND串上并行地进行。因此,进程可用于将字线集合擦除。所述进程可用于擦除例如图5A、5B、6和7A中所描绘的NAND串。在一些实施例中,选定层(例如,上部层510或下部层508)内的NAND串的仅一部分作为一单位经擦除。

步骤1002设定初始稳定状态擦除电压(Ver)的量值。在一个实施例中,所述进程进行双侧GIDL擦除。将擦除电压脉冲施加到位线和源极线。在一个实施例中,擦除电压脉冲的稳定状态量值对于位线和源极线是不同的。在一个实施例中,稳定状态擦除电压的量值对于位线和源极线是相同的。步骤1002是指将电压施加到不邻接选择晶体管的位线和源极线的端部。

步骤1004设定初始选择栅极电压(Vsg)的量值。本文中,Vsg可被称为擦除电压,因为其有助于在选择晶体管的两个端子之间产生GIDL电压。将选择栅极电压(Vsgd)脉冲提供到连接到漏极侧选择晶体管的控制栅极的漏极侧选择线(例如,SGD)。将选择栅极电压(Vsgs)脉冲提供到连接到源极侧选择晶体管的控制栅极的源极侧选择线(例如,SGS)。Vsgd和Vsgs的量值可彼此相同或彼此不同。

步骤1006包含施加擦除条件。步骤1006可包含将电压脉冲施加到位线、源极线、连接到漏极侧选择晶体管的选择线、连接到源极侧选择晶体管的选择线和连接到存储器单元的控制栅极的字线。可将相同量值或不同量值的擦除电压施加到位线和源极线。在一个实施例中,漏极选择线和源极选择线保持浮动。可将擦除启用电压施加到字线。步骤1006可包含控制多种信号的定时。

步骤1006可包含从源极和漏极端两个为存储器串的通道充电(例如,增大电压),且在连接到存储器单元的控制栅极的字线上将低电压设定为例如0V。在一个实施例中,为通道充电包含将合适的电压施加到漏极侧和/或源极侧选择栅极以产生GIDL电流。

步骤1008包含对NAND串进行擦除验证测试。通常,这种测试涉及设定对于连接到串上存储器单元的控制栅极字线的擦除验证电压(例如,Vme),同时感测存储器串中的电流。如果电流足够高,那么视为NAND串通过验证测试。如果在决策步骤1010处,NAND串通过擦除验证测试,那么在1012步骤处完成擦除操作。如果在决策步骤1010处,NAND串未通过擦除验证测试,那么在步骤1014处继续所述进程。

步骤1014包含确定是否待递增选择栅极电压。如果是,那么在步骤1016中递增选择栅极电压。无论选择栅极电压是否递增,都在步骤1018中递增擦除电压。接着,通过返回到步骤1006进行擦除程序的下一次重复。擦除重复(或环)通常涉及施加擦除条件,接着进行验证测试,但是在一些情况下,省略验证测试。

图10B是描述编程进程的一个实施例的流程图。通过存储器裸片300响应来自控制器102的指令、数据和一个或多个地址来进行图10B的进程。图10B的进程也可用于实施上文所论述的全序列编程。图10B的进程还可用于实施多阶段编程操作(例如图11A到11B中的多阶段实例和图12A到12B中的多阶段实例)的每一阶段。另外,图10B的进程可用于对连接到相同字线的存储器单元进行编程。在一个实施例中,控制器102指示存储器裸片300应对哪一字线(以及哪一块或子块)进行编程。因此,控制器102能够管理对字线进行编程的顺序。

通常,在编程操作期间(通过选定字线)施加到控制栅极的编程电压以一系列编程脉冲的形式施加。在编程脉冲之间,存在验证脉冲集合以进行验证。在许多实施方案中,编程脉冲的量值随着每一连续脉冲增大预定步长。在图10B的步骤1050中,将编程电压(Vpgm)初始化为起始量值(例如,约12到16V或另一合适层级),且将由状态机维持的程序计数器PC初始化为1。在步骤1052中,将编程信号的编程脉冲Vpgm施加到选定字线(经选择用于编程的字线)。在一个实施例中,将同时进行编程的存储器单元群全部连接到相同字线(选定字线)。未选定字线接收一个或多个增压电压(例如,约7到11伏)以进行所属领域中已知的增压方案。如果应对存储器单元进行编程,那么将对应位线接地。另一方面,如果存储器单元应保持在其当前阈值电压下,那么将对应位线连接到Vdd以抑制编程。在步骤1052中,将编程脉冲同时施加到连接到选定字线的所有存储器单元,使得同时对连接到选定字线的所有存储器单元进行编程。也就是说,同时或在重叠时间期间(两个都被视为并行)对所述存储器单元进行编程。以这种方式,除非所述存储器单元已被锁定而无法编程,否则连接到选定字线的所有存储器单元将同时改变其阈值电压。

在步骤1054中,使用适当的验证参考电压集合进行一个或多个验证操作来验证适当的存储器单元。在一个实施例中,验证进程是通过应用测试被选定用于编程的存储器单元的阈值电压是否已达到适当验证参考电压来进行的。

在步骤1056中,确定所有存储器单元是否已达到其目标阈值电压(通过)。如果是,那么编程进程完成且成功,因为所有选定存储器单元都被编程且验证为其目标状态。在步骤1058中报告“通过”状态。在1056中,如果确定并非所有存储器单元都已达到其目标阈值电压(未通过),那么编程进程继续到步骤1060。

在步骤1060中,系统对尚未达到其对应的目标阈值电压分布的存储器单元的数目进行计数。也就是说,系统对到目前为止未能通过验证进程的存储器单元的数目进行计数。这种计数可通过状态机、控制器或其它逻辑进行。在一个实施方案中,感测块中的每一者将存储其对应的单元的状态(通过/未通过)。在一个实施例中,存在一个总计数,其反映未能通过上一验证步骤的当前正进行编程的存储器单元的总数。在另一实施例中,保存每一数据状态的单独计数。

在步骤1062中,确定来自步骤1060的计数是否小于或等于预定限值。在一个实施例中,预定限值为在存储器单元页的读取进程期间可通过错误校正码(ECC)校正的位数目。如果未通过的存储器单元的数目小于或等于预定限值,那么编程进程可能停止且在步骤1058中报告“通过”状态。在此情形中,足够的存储器单元被正确地编程,使得可在读取过程期间使用ECC校正尚未完成编程的较少剩余存储器单元。在一些实施例中,步骤1060将对每一页未通过的单元、每一目标数据状态或其它单元的数目进行计数,且那些计数将单独地或共同地与步骤1062中的阈值进行比较。

在另一实施例中,预定限值可小于可在读取进程期间通过ECC校正的位数目以允许未来错误。当编程页面的不到所有存储器单元或比较仅一个数据状态(或少于所有状态)的计数时,预定限值可为在存储器单元页的读取进程期间可通过ECC校正的位数目的一部分(成比例或不成比例)。在一些实施例中,并不预定限值。替代地,限值基于已针对页面计数的错误数、所进行的编程/擦除循环的数目或其它准则而改变。

如果未通过存储器单元的数目不小于预定限值,那么在步骤1064处继续编程进程,且针对编程限值(PL)检查编程计数器PC。编程限值的实例包含12、20和30;然而,可使用其它值。如果编程计数器PC不小于编程限值PL,那么编程进程被视为未通过,且在步骤1068中报告未通过状态。这是编程错误的一个实例。如果编程计数器PC小于编程限值PL,那么在步骤1066处继续所述进程,在此期间,编程计数器PC递增1且编程电压Vpgm步进到下一量值。举例来说,下一脉冲将具有比前一脉冲大一步长(例如,0.1到0.5伏的一步长)的量值。在步骤1066之后,所述进程循环回到步骤1052,且将另一编程脉冲施加到选定字线,从而进行图10B的编程进程的另一重复(步骤1052到1066)。

一般来说,在验证操作和读取操作期间,将选定字线连接到电压(参考信号的一个实例),所述电压的层级特定用于每一读取操作(例如,参看图9A的读取参考电压Vr1、Vr2、Vr3、Vr4、Vr5、Vr6和Vr7)或验证操作(例如,参看图9A的验证参考电压Vv1、Vv2、Vv3、Vv4、Vv5、Vv6和Vv7)以便确定有关的存储器单元的阈值电压是否已达到此类层级。在施加字线电压之后,测量存储器单元的传导电流以确定存储器单元是否响应于施加到字线的电压而接通(传导电流)。如果测量出传导电流大于特定值,那么假设存储器单元接通,且施加到字线的电压大于存储器单元的阈值电压。如果并未测量到传导电流大于所述特定值,那么假设存储器单元并未接通,且施加到字线的电压不大于存储器单元的阈值电压。在读取或验证进程期间,在未选定存储器单元的控制栅极处提供有一个或多个读取通过电压,使得这些存储器单元将用作通过栅极(例如,无论这些存储器单元是否被编程或擦除,都传导电流)。

用于测量读取或验证操作期间存储器单元的传导电流的方式有许多。在一个实例中,通过传导电流对感测放大器中的专用电容器放电或充电的速率来测量存储器单元的传导电流。在另一实例中,选定存储器单元的传导电流允许(或不能允许)包含所述存储器单元的NAND串对对应位线进行放电。在一段时间之后测量所述位线上的电压,以查看所述位线是否已放电。应注意,本文所描述的技术可与所属领域中已知用于检验/读取的不同方法一起使用。也可使用所属领域中已知的其它读取和验证技术。

在一些实施例中,控制器102从主机(或客户端、用户等)接收请求以将主机数据(从主机接收的数据)编程到存储器系统中。在一些实施例中,控制器102将待进行编程的主机数据布置成数据单位。举例来说,控制器102可将主机数据布置成页、部分页(页的子集)、字线单位、块、巨型块或其它单位。

如上所述,可使用图10B的进程来实施多阶段编程操作。图11A到11B描绘具有粗糙阶段(图11A)接着精细阶段(图11B)的多阶段编程操作的一个实施例。图12A到12B描绘多阶段编程操作的一个实施例,其中将一个位编程到每一存储器单元每一阶段中。在一些实施例中,针对多阶段编程操作的每一阶段进行图10B的进程一次。

图11A描绘多阶段编程操作的第一阶段,其包含将存储器单元从已擦除状态(S0)编程到被编程数据状态S1到S7中的任一个,类似于全序列编程。然而,胜于使用标准验证参考电压(例如,Vv1、Vv2、Vv3、Vv4、Vv5、Vv6和Vv7),图11A的进程使用各自略微低于对应标准验证参考电压的验证参考电压(例如,Vv1'、Vv2'、Vv3'、Vv4'、Vv5'、Vv6'和Vv7')的替代集合。因此,图11A的阈值电压可被认为是在比图9A的阈值电压更低的电压下的中间阈值电压分布(或中间数据状态)。应注意,抑制对待在数据状态S0下的已擦除状态S0下的存储器单元进行编程。

图11B描绘多阶段编程操作的第二(和上一)阶段,其包含对存储器单元进行编程以紧固阈值分布。因此,使用标准验证参考电压(例如,Vv1、Vv2、Vv3、Vv4、Vv5、Vv6和Vv7)将存储器单元从图11A的中间阈值电压分布(或中间数据状态)编程为图11B的最终或目标阈值电压分布(或数据状态)。图11A被称作粗糙阶段且图11B作为精细阶段。粗糙阶段还可被称作粗略阶段或有雾阶段。精细阶段还可被称作高准确度阶段。在一个实施例中,针对给定字线进行图11A的粗糙阶段,接着针对下一字线进行粗糙阶段。针对下一字线的粗糙阶段可对给定字线产生干扰,进而扩宽中间阈值电压分布,其可能在读取数据时产生错误。然而,在针对下一字线的粗糙阶段后接着进行图11B的精细阶段,去除或减小来自下一字线的干扰影响。应注意,抑制对待在数据状态S0下的已擦除状态E下的存储器单元进行编程。

在一个实施例中,粗糙-精细编程方案实施于位-成本可伸缩(BiCs)架构中。图11A和11B描绘其中将存储器单元编程为每一存储器单元三个位的实例。在一个实施例中,将存储器单元编程为每一存储器单元四个位(在本文中被称作“QLC”,方形层级单元)。粗糙-精细编程方案可通过减小粗糙与精细之间的阈值电压(Vt)差来显著地补偿相邻字线干扰(“NWI”)影响。粗糙-精细编程方案可用于对每一单元存储两个、三个、四个、五个或超过五个位的存储器单元进行编程。

在一个实施例中,在给定字线上进行图11A中所描绘的第一编程阶段后,在序列稍后的另一字线上进行图11A中所描绘的第一编程阶段。然后,在给定字线上进行图11B中所描绘的第二编程阶段。举例来说,当从WL0到WL96依序对字线进行编程时,序列可以如表I中所描绘。标记第一通过和第二通过的列中的编号指示编程阶段进行的顺序。如本文所定义,对字线进行编程的顺序次序是进行最终编程阶段的顺序。在表I中,最终阶段是第二阶段,但在一些多阶段编程进程中可能存在更多阶段。因此,表I中的字线依序编程顺序是WL0、WL1…WL95。

表II描述对于一个实施例的序列,其中从WL95到WL0依序进行编程。应注意,表II中的序列是相对于表I中的序列反转WL编程序列的一个实例。因此,表II中的字线依序编程顺序是WL95、WL94…WL0。

图12A到12B描绘可如何使用多阶段编程技术来通过每一编程阶段将一个位编程到每一存储器单元中。这个实例是用于每一存储器单元两个位,但可以扩展到每一存储器单元更大的位数目。图12A描绘第一阶段且图12B描绘第二阶段。

在第一编程阶段中,针对选定字线WLn对下部页进行编程。如果下部页将保持数据1,那么存储元件状态保持在状态Er(分布1200)下。如果待将数据编程为0,那么WLn上的存储元件的阈值电压升高,使得将存储元件编程为中间(LM或下部-中部)状态(分布1202)。

图12B描绘二阶段编程技术的第二(和最终)阶段的一个实施例。将A状态存储元件从Er状态分布1200编程到A状态分布1204,将B状态存储元件从LM状态分布1202编程到B状态分布1206,且将C状态存储元件从LM状态分布1202编程到C状态分布1208。

在一个实施例中,在给定字线上进行图12A中所描绘的第一编程阶段后,在序列稍后的另一字线上进行图12A中所描绘的第一编程阶段。然后,在给定字线上进行图12B中所描绘的第二编程阶段。举例来说,当从WL0到WL96依序对字线进行编程时,序列可以如上表I中所描绘。图12A和12B中的多阶段编程进程可以例如在上文所论述的表II中反转。

如上所述,错误恢复技术可能是费时的且可能不会成功。本文中所公开的技术用于编程顺序反转。在一些实施例中,对字线集合进行编程的顺序在某一点处反转。举例来说,最初可在从块(或子块)的源极端到块(或子块)的漏极端的方向上依序对块或子块中的字线集合进行编程。在某一点处,可以反转编程顺序,使得可在从块(或子块)的漏极段到块(或子块)的源极端的方向上依序对字线集合进行编程。

反转对字线集合的依序编程顺序可改进错误恢复。在一些情况下,当对字线集合进行编程时,其可以有利于具有所述集合内较早进行编程的问题字线。在一个实施例中,反转字线集合的依序编程顺序以将问题字线放置在所述序列中的较早处。在其它情况下,当对字线集合进行编程时,其可有利于问题字线在所述集合中较晚地进行编程。

图13是对非易失性存储器进行编程的进程1300的一个实施例的流程图,其包含改变字线的编程顺序。进程1300可用于改变对字线集合进行编程的顺序。在一个实施例中,改变是反转所述字线集合的依序编程顺序。然而,进程1300不限于反转依序编程顺序。在一个实施例中,进程1300用于对三维结构(例如存储装置400)中的非易失性存储器单元进行编程。三维结构具有一个或多个层。在一个实施例中,三维结构具有单一层。在一个实施例中,三维结构具有多个层。在一个实施例中,控制电路配置成独立于上方或下方层中的存储器单元将一个层中的存储器单元擦除。

在一个实施例中,进程1300用于对存储器单元块(例如图7A中的BLK0)进行编程。在一个实施例中,进程1300用于对存储器单元的子块(例如图7A中的子块SB0)进行编程。在一个实施例中,进程1300用于对块或子块中的一个层进行编程。举例来说,进程1300可用于对包含图7A中的字线WL0到WL47的下部层进行编程。作为另一实例,进程1300可用于对上部层(例如图7A中的字线WL48到WL95)进行编程。作为又一实例,进程1300可用于对单层装置(例如图5B中所描绘的实施例)中的WL0到WL95进行编程或用于对多层装置(例如图5A中所描绘的实施例)中的WL0到WL95进行编程。进程1300不限于前述实例。进程1300可与例如图9A中所描绘的全序列编程技术或例如图11A到11B或12A到12B中所描绘的多阶段编程技术一起使用。

步骤1302包含以第一顺序对非易失性存储器装置中的字线集合进行编程。如在本文中所提及,短语“对字线集合进行编程”意味着对连接到所述集合中的第一字线的第一非易失性存储器单元进行编程,对连接到所述集合中的第二字线的第二非易失性存储器单元进行编程等。本文中,短语“以一顺序对字线集合进行编程”意味着利用从所述字线集合中的一个字线进行到下一个字线的编程顺序一次对一个字线进行编程。可以任何顺序布置所述字线集合。

在一个实施例中,步骤1302包含以第一顺序次序对非易失性存储器装置中的字线集合进行编程。本文中,短语“以顺序次序对字线集合进行编程”意味着利用从在相同方向上的一个字线进行到紧邻接的字线的编程顺序一次对一个字线进行编程。举例来说,可从WL0到WL95依序对字线进行编程。作为另一实例,可从WL95到WL0依序对字线进行编程。并不需要从最低或最高编号字线开始顺序次序。换句话说,并不需要从字线集合的物理端处的字线开始顺序次序。举例来说,顺序次序可以是WL16、WL17…WL95、WL0、WL1…WL15。

步骤1304包含将字线集合擦除。本文中,短语“将字线擦除”或类似短语意味着将连接到字线的非易失性存储器单元擦除。因此,将字线集合擦除意味着将连接到所述集合中的字线的非易失性存储器单元擦除。在一个实施例中,字线集合是擦除单位。在一个实施例中,字线集合包含至少一个擦除单位。擦除单位是存储器单元用于擦除操作的最小单位。因此,当字线集合是擦除单位时,将所述集合连接到擦除单位中的所有存储器单元。在一个实施例中,以单位形式将块中的所有字线擦除。在一个实施例中,以单位形式将子块中的所有字线擦除。在一个实施例中,以单位形式将层中的所有字线擦除。举例来说,可以单位形式擦除上部层中的字线(例如,WL48到WL95),而不擦除下部层中的字线中的任一个(例如,WL0到WL47)。

步骤1306包含确定是否改变(例如,反转)对字线集合进行编程的顺序。可基于多个因素得出这一确定,包含(但不限于)编程/擦除循环计数和是否发现缺陷。编程/擦除循环计数是指字线集合已通过编程/擦除循环的次数。在一个实施例中,当编程/擦除循环计数超出阈值时,改变字线的编程顺序。缺陷可以是非易失性存储装置中的任何缺陷。缺陷的一个实例是某一字线经历异常高的错误计数。错误计数是指当反转读取已从其被编程状态翻转时存储在一群存储器单元中的位数。可通过ECC引擎226/256确定错误。

在一个实施例中,确定是基于非易失性存储装置中是否存在缺陷。缺陷可以在包含字线集合的块或子块内,但并非必需如此。缺陷可以是不同块或子块。然而,此缺陷可表明可存在与被编程块(或子块)类似的缺陷的可能性。举例来说,如果在一个块中发现结合WL95的缺陷,那么这可能表明与被编程的块中的WL95类似的缺陷的可能性。

如果确定不改变编程顺序,那么控制转到步骤1302。如果确定改变编程顺序,那么控制转到步骤1308。

步骤1308包含以与第一顺序不同的第二顺序对字线集合进行编程。应注意,由于可基于编程/擦除循环确定使用第二顺序,因此可规定第二顺序通过编程/擦除循环来改变编程顺序。作为一实例,第一顺序可能将从WL0到WL95依序对字线进行编程,且第二顺序可能将最高编号字线中的一个或多个移动到编程顺序中的较早处。举例来说,可以编程顺序中的第一或至少较早地对WL95进行编程。因此,在这一实例中第二顺序是非依序的。

在一个实施例中,步骤1308包含以与第一顺序次序不同的第二顺序次序对字线集合进行编程。举例来说,如果从WL0到WL95依序对第一字线集合进行编程,那么可以从WL16到WL96依序且随后从WL0到WL15依序对第二字线集合进行编程。应注意,由于确定可基于编程/擦除循环使用第二顺序次序,因此可以规定第二顺序次序通过编程/擦除循环来改变编程顺序。

在一个实施例中,步骤1308包含以第一顺序次序的反转的第二顺序次序对字线集合进行编程。举例来说,如果从WL0到WL95依序对第一字线集合进行编程,那么可以从WL95到WL0依序对第二字线集合进行编程。另一方面,如果从WL95到WL0依序对第一字线集合进行编程,那么可以从WL0到WL95依序对第二字线集合进行编程。下文论述反转顺序次序的其它实例。

如上所述,改变(例如,反转)字线集合的依序编程顺序可改进错误恢复。在一些情况下,当对字线集合进行编程时,其可以有利于具有所述集合内较早进行编程的问题字线。问题字线的实例是相对于其它字线,对其进行编程更可能未通过的字线。在一个实施例中,改变字线集合的编程顺序以将问题字线放置在编程序列中的较早处。举例来说,在步骤1306中,可确定给定裸片上的WL95倾向于成为问题字线(例如,更可能为缺陷的)。可针对所述裸片上的所有块改变编程顺序,以在编程顺序较早的放置WL95。此改变还可在逐块基础上进行。

在其它情况下,当对字线集合进行编程时,其可有利于问题字线在所述集合中较晚地进行编程。举例来说,在步骤1306中,可确定给定裸片上的WL0倾向于成为问题字线(例如,更可能为缺陷的)。可针对所述裸片上的所有块改变编程顺序,以在编程顺序较早的放置WL0。这一反转还可在逐存储器块基础上进行。

同样,在一些情况下,在给定存储器裸片上发现问题字线可表明另一存储器裸片上类似定位的字线可能是问题字线。因此,改变一个存储器裸片上的编程顺序的决策可基于从另一存储器裸片上获得的信息。

在一些实施例中,第一字线集合中的编程顺序与第二字线集合不同(例如,反转)。举例来说,可以从WL0到WL95的顺序依序对第一字线集合进行编程且可从WL95到WL0依序对第二字线集合进行编程。第一和第二字线集合可以是元块的一部分。第一和第二字线集合可以在相同存储器裸片上或在两个不同的存储器裸片上。相对于对另字线集合进行编程的顺序次序来反转对字线集合进行编程的顺序次序可改进错误恢复。作为一实例,如果例如基于在不同存储器裸片中对字线进行编程的顺序创建冗余数据,那么这可有助于改进错误恢复。

图14是对非易失性存储器进行编程的进程1400的一个实施例的流程图。进程1400描述以第一顺序对第一字线集合进行编程且以与第一顺序不同的第二顺序对第二字线集合进行编程。在一个实施例中,第一顺序是第一顺序次序且第二顺序是与第一顺序次序不同的第二顺序次序。在一个实施例中,第二顺序次序是第一顺序次序的反转。在一个实施例中,由于改变(例如,反转)字线集合中的一个的编程顺序,但不改变(例如,反转)另一集合的顺序,因此进行进程1400。换句话说,在一个时间点,以相同顺序对两个字线集合均进行编程。接着,在字线集合中的一个上,但不在另一字线集合上进行例如进程1300的进程。

然而,并不必需在字线集合中的一个上进行例如进程1300的进程来进行进程1400。在一个实施例中,在对第一和第二字线集合进行编程的第一时间进行进程1400。在一个实施例中,在非易失性存储装置的整个寿命中,以与第一字线集合不同的(例如,反转)顺序对第二字线集合进行编程。

在一个实施例中,进程1400用于对三维结构(例如存储装置400)中的非易失性存储器单元进行编程。三维结构具有一个或多个层。在一个实施例中,三维结构具有单一层。在一个实施例中,三维结构具有多个层。在一个实施例中,控制电路配置成独立于上方或下方层中的存储器单元将一个层中的存储器单元擦除。

步骤1402包含以第一顺序对非易失性存储器装置中的第一字线集合进行编程。在一个实施例中,第一顺序是顺序次序。然而,并不要求编程依序通过完整的第一字线集合。举例来说,非依序编程顺序可以是WL0、WL2、WL1、WL4、WL3、WL6、WL5等。非依序编程顺序的另一实例将使用加扰器以使编程顺序随机化。可以基于若干字线的信息块进行这种加扰。举例来说,可以随机顺序WL1、WL3、WL0、WL2对WL0到WL3进行编程。也可在所述集合中的其它群的字线(例如,WL4到WL95)上进行加扰。所述群可全部具有相同大小,但并非必需如此。对于每一群的加扰种可以相同或不同。

第一字线集合在第一三维结构中。第一字线集合的一个实例是图5A或5B中的BLK0中的WL0到WL 95。在一些情况下,一次对块中的一个子块进行编程,在此情况下,第一字线集合可以是子块中的一个(例如,SB0)中的WL0到WL95。第一字线集合的另一实例是一个层中的字线。举例来说,第一字线集合可以是BLK0的下部层中的WL0到WL47。替代地,第一字线集合可以是BLK0的上部层中的WL48到WL95。

步骤1404包含以与第一顺序不同的第二顺序对非易失性存储器装置中的第二字线集合进行编程。在一个实施例中,第二顺序和第一顺序都是依序的,其中第二顺序次序是第一顺序次序的反转。举例来说,如果从WL0到WL95依序对第一字线集合进行编程,那么可以从WL95到WL0依序对第二字线集合进行编程。在一个实施例中,在相同方向上但在不同字线处开始对第一和第二字线集合进行编程。举例来说,如果从WL0到WL95依序对第一字线集合进行编程,那么可以从WL16到WL95依序且随后从WL0到WL15依序对第二字线集合进行编程。

在一个实施例中,以非依序方式对第一和第二字线集合进行编程。如上所述,可在若干字线的信息块上进行加扰。然而,可以与第一集合不同的方式对第二字线集合进行随机分组(或加扰)。举例来说,如果以随机顺序WL1、WL3、WL0、WL2对第一集合中的WL0到WL3进行编程,那么可以随机顺序WL2、WL1、WL0、WL3对第二集合中的WL0到WL3进行编程。对第一集合和第二集合使用不同随机顺序可有助于改进错误恢复。

第二字线集合处于第二三维结构中。第一和第二字线集合处于对应的第一和第二三维结构的相同层级处。举例来说,如果第一字线集合是块中的WL0到WL 95,那么第二字线集合也是字线是不同块(其可以在相同存储器裸片或不同存储器裸片上)中的WL0到WL 95。作为另一实例,如果第一字线集合是子块(例如,BLK0的SB0)中的WL0到WL95,那么第二字线集合是另一子块中的WL0到WL95。另一子块可以在相同块或不同块中。另一子块可以在相同存储器裸片或另一存储器裸片上。作为又一实例,如果第一字线集合是一个层中的字线(例如,下部层中的WL0到WL47),那么第二字线集合是相同层级下的层中的字线(在这一实例中,下部层中的WL0到WL47)。在这一行实例中,第一和第二字线集合可以在相同块中的不同子块中,可以在相同存储器裸片上的不同块中,或可以在不同存储器裸片上。应注意,第一和第二三维结构可以是相同三维结构。然而,在一些实施例中,第一和第二三维结构是不同三维结构。

在一个实施例中,同时对第一和第二字线集合进行编程。本文中,短语“同时对第一和第二字线集合进行编程”意味着控制器102调度电路以进行第一和第二字线集合的编程,使得第一和第二字线集合的编程能够同时进行。因此,电路能够同时对对应的第一和第二字线集合进行编程。同样,在第一或第二集合已完成编程之前,控制器102调度对于第一和第二集合两个的指令。举例来说,控制器102可调度用于两个不同存储器裸片(其含有第一和第二字线集合)的指令,使得可同时进行编程。然而,由于例如每一存储器裸片何时执行指令等因素,第一和第二字线集合的实际编程可能或可能不同时进行。

在一个实施例中,第一字线集合在第一存储器裸片300上且第二字线集合在第二存储器裸片300上。因此,可以规定第二顺序通过存储器裸片改变编程顺序。在这种情况下,存储器控制器102可向每一存储器裸片发布单独指令以对对应的字线进行编程。应注意,第一编程顺序和第二编程顺序可各自依序,在此情况下,可规定第二顺序次序通过存储器裸片改变编程顺序。

在一个实施例中,第一字线集合和第二字线集合在相同存储器裸片上的不同存储器块中。因此,可以规定第二顺序通过存储器块改变编程顺序。在这种情况下,存储器控制器102可向相同存储器裸片发布指令来对对应的字线进行编程。应注意,第一编程顺序和第二编程顺序可各自依序,在此情况下,可规定第二顺序次序通过存储器块改变编程顺序。

在一个实施例中,进程1400用于对元页进行编程。图15A描绘可如何使用进程1400来对元页进行编程的一个实例。图15A关于在八个存储器裸片中的每一个上对一个块进行编程的实例。将三个位编程到每一存储器单元中。这一实例中的块中存在96个字线。在一个实施例中,将每一存储器单元块各自划分成四个子块,例如SB0、SB1、SB2和SB3(参见例如图7A)。因此,块含有1152个物理页(96个字线×3个位/存储器单元×4个子块)。在这一实例中连接到字线的存储器单元的数目等于一页。

图15A的表1500经组织成列出字线(WL)的第一列(WL)。子块并未明确地描绘于图15A中。因此,应注意,通过对四个子块中的每一个的每一字线三个页进行编程得出用于每一字线的12个物理页。图15B和15C展示用于可如何对子块进行编程的两个替代方式。图15A中的表1500具有用于八个存储器裸片(裸片0到裸片7)中的每一个的单独列以展示将哪一页编程到哪一字线/平面组合中用于所述存储器裸片。

在图15A的实例中,在存储器裸片0到存储器裸片7中对1152个元页(页0到页1151)进行编程。在这一实例中,元页具有八个物理页。将元页的每一物理页编程到一个存储器裸片中。举例来说,将元页0的一个物理页编程到裸片0的WL0、裸片2的WL0、裸片4的WL0、裸片6的WL0、裸片1的WL95、裸片3的WL95、裸片5的WL95和裸片7的WL95中的每一个中。在一个实施例中,同时对元页的物理页进行编程。

以从最低页码到最高页码的顺序次序对每一存储器裸片中的字线进行编程。举例来说,从WL0依序到WL95对裸片0进行编程。从WL95依序到WL0(其为裸片1的反转)对裸片1进行编程。

在一个实施例中,针对全部四个子块对一个字线进行编程,随后进行到块中的下一字线。图15B描绘用于对子块进行编程的一种可能的顺序。表1510描绘用于裸片0的可对字线和子块进行编程的顺序,符合表1500中的实例。举例来说,用于裸片0的顺序可以是:WL0/SB0、WL0/SB1、WL0/SB2、WL0/SB3、WL1/SB0、WL1/SB1、WL1/SB2、WL1/SB3、…、WL95/SB0、WL95/SB1、WL95/SB2、WL95/SB3。表1515描绘用于裸片1的可对字线和子块进行编程的顺序,符合表1500中的实例。用于裸片1的顺序可以是:WL95/SB0、WL95/SB1、WL95/SB2、WL95/SB3、WL94/SB0、WL94/SB1、WL94/SB2、WL94/SB3、…、WL0/SB0、WL0/SB1、WL0/SB2、WL0/SB3。

在图15B的实例中,以顺序SB0、SB1、SB2、SB3在每一裸片中对子块进行编程。当反转字线编程的顺序时,也有可能反转子块编程的顺序。图15C描绘用于对子块进行编程的一种可能的顺序。表1520描绘用于裸片0的可对字线和子块进行编程的顺序,符合表1500中的实例。实例与表1510中的实例相同。表1525描绘用于裸片1的可对字线和子块进行编程的顺序,符合表1500中的实例。用于裸片1的顺序可以是:WL95/SB3、WL95/SB2、WL95/SB1、WL95/SB0、WL94/SB3、WL94/SB2、WL94/SB1、WL94/SB0、…、WL0/SB3、WL0/SB2、WL0/SB1、WL0/SB0。

在一个实施例中,对子块中的所有字线进行编程,随后对下一子块中的任何字线进行编程。图15D描绘对一个存储器单元块进行编程的实例,其中对子块中的所有字线进行编程,随后对下一子块中的任何字线进行编程。将三个位编程到每一存储器单元中。在这些实例中,存在96个字线和四个子块。表1540描绘可如何针对裸片0来对字线子块进行编程的一个实例。表1550描绘可如何针对裸片1来对字线和子块进行编程的一个实例以及针对裸片0的表1540的实例。表1560描绘可如何针对裸片1来对字线和子块进行编程的另一实例以及针对裸片0的表1540的实例。表1550与1560之间的差异在于子块编程顺序经反转。

现参看表1540,子块编程顺序可以是(例如)SB0、SB1、SB2、SB3。举例来说,用于裸片0的顺序可以是:WL0/SB0、WL1/SB0、WL2/SB0、…、WL95/SB0、WL0/SB1、WL1/SB1、WL2/SB1、…、WL95/SB1、…、WL0/SB2、WL1/SB2、WL2/SB2、…、WL95/SB2、…、WL0/SB3、WL1/SB3、WL2/SB3、…、WL93/SB3、WL94/SB3、WL95/SB3。现参看表1550,用于裸片1的顺序可以是:WL95/SB3、WL94/SB3、WL93/SB3、…、WL0/SB3、WL95/SB2、WL94/SB2、WL93/SB2、…、WL0/SB2、…、WL95/SB1、WL94/SB1、WL93/SB1、…、WL0/SB1、…、WL95/SB0、WL94/SB0、WL93/SB0、…、WL0/SB0。在这一实例中,在裸片1中(相对于裸片0)反转串的编程顺序。然而,在另一实施例中,以相同顺序(例如,SB0、SB1、SB2、SB3)对串进行编程,同时反转对字线进行编程的顺序。现参看表1560,用于裸片1的顺序可以是:WL95/SB0、WL94/SB0、WL93/SB0、…、WL0/SB0、WL95/SB1、WL94/SB1、WL93/SB1、…、WL0/SB1、…、WL95/SB2、WL94/SB2、WL93/SB2、…、WL0/SB2、…、WL95/SB3、WL94/SB3、WL93/SB3、…、WL0/SB3。

相对于如图14和15A到15D中所描绘的对另字线集合进行编程的顺序次序来反转对字线集合进行编程的顺序次序可改进错误恢复。举例来说,除了裸片0到裸片7之外,可能存在由裸片0到裸片7中的数据形成的冗余裸片。在一个实施例中,备用存储器裸片可用于存储冗余数据,其可能由来自存储器裸片0到裸片7的按位互斥或(XOR)数据形成。举例来说,可对表1500中的每一物理页进行按位XOR。使用页0作为实例,应注意WL0涉及存储器裸片0、裸片2、裸片4和裸片6。然而,对于页0,WL95涉及存储器裸片1、裸片3、裸片5和裸片7。在一个实施例中,冗余数据可用于恢复数据,其条件是来自八个裸片中的七个的数据是可用的。如在表1500中,反转编程顺序增大冗余数据将能够恢复数据的几率。

图16描绘将元页编程到非易失性存储器中的进程1600的一个实施例的流程图。将参考图15A到15D解释进程1600;然而,进程1600不限于图15A到15D中的实例。

步骤1602包含将元页编程到第一存储器裸片集合中的最低编号字线中且编程到第二存储器裸片集合中的最高字编号字线中。步骤1602可包含同时将元页的不同物理页编程到存储器裸片中的每一个中。在一个实施例中,最低编号字线最接近于源极线且最高编号字线最接近于位线。在一个实施例中,最低编号字线最接近于NAND串的源极端且最高编号字线最接近于NAND串的漏极端。

步骤1602可包含控制器102向每一存储器裸片发布指令以对元页的其对应的物理页进行编程。在一些实施例中,控制器102利用元页的物理页形成冗余数据。举例来说,控制器102通过进行物理页的按位XOR形成冗余页。控制器102可将冗余页存储在备用存储器裸片中。在稍后时间无法从物理页中的一个的物理位置中读取所述物理页的情况下,控制器102可使用冗余页来恢复物理页的内容。

参看图15A,将页0到11编程到裸片0、裸片2、裸片4和裸片6的WL0中。另外,将页0到11编程到裸片1、裸片3、裸片5和裸片7的WL95中。

参看图15B,将页0到2编程到裸片0的WL0/SB0中,将页3到5编程到裸片0的WL0/SB1中,将页6到8编程到裸片0的WL0/SB2中,且将页6到8编程到裸片0的WL0/SB3中。另外,将页0到2编程到裸片0的WL95/SB0中,将页3到5编程到裸片0的WL95/SB1中,将页6到8编程到裸片0的WL95/SB2中,且将页6到8编程到裸片0的WL95/SB3中。图15C描绘用于裸片1的子块的编程顺序的替代方案。

在一实施例中,符合图15D,将页0到2编程到裸片0的WL0/SB0中。另外,将页0到2编程到裸片0的WL95/SB3中。图15C描绘用于裸片1的子块的编程顺序的替代方案,其中将页0到2编程到裸片0的WL95/SB0中。

步骤1604包含递增用于第一存储器裸片集合的选定字线的编号。

步骤1606包含递减用于第二存储器裸片集合的选定字线的编号。

步骤1608包含将另一元页编程到用于第一存储器裸片集合中的选定字线的当前数目中且编程到第二存储器裸片集合的当前字线中。在实施例中,符合图15A,将页12到23编程到裸片0、裸片2、裸片4和裸片6的WL1中。另外,将页12到23编程到裸片1、裸片3、裸片5和裸片7的WL94中。

步骤1610是确定是否存在更多待编程的元页。如果是,那么控制转到步骤1604。进行步骤1604到1608以将当前元页编程到存储器裸片中。当存在更多待编程的元页时,进程结束。可在对所有字线进行编程之前结束进程。在这种情况下,当存在更多待编程的元页时,进程可以从编程中断处开始。

在一些实施例中,系统对NAND串进行编程。在一些实施例中,NAND串驻存在具有一个或多个层的三维结构中。举例来说,图5A描绘具有两个层的三维结构。在一些实施例中,当出现编程顺序反转时,系统独立地处理每一层。然而,当出现编程顺序反转时,系统并非必需独立地处理每一层。另外,如在图5B的实施例中,NAND串可驻存在单一层中。

图17是以不同顺序次序对两个集合的NAND串的选定层进行编程的进程1700的一个实施例的流程图。进程1700可用于对驻存在三维结构中的NAND串进行编程。三维结构具有一个或多个层。因此,在一个实施例中,每一NAND串驻存在超过一个层上。在一个实施例中,每一NAND串完全地驻存在单一层内。每一层具有相对于NAND串的漏极端和源极端限定的漏极端和源极端。

被编程的选定层在用于每一NAND串集合的三维结构的相同层级处。举例来说,选定层可以是用于两个NAND串的下部层508,或选定层可以是用于两个集合的NAND串的上部层510(参看图5A)。在一个实施例中,每一NAND串集合驻存在三维结构的单一层中。举例来说,选定层可以是图5B中的完整堆叠556。

在进程1700中,以另一集合的NAND串的选定层的反转顺序对一集合的NAND串的选定层进行编程。在一个实施例中,两个集合的NAND串驻存在相同块的不同子块中。在一个实施例中,两个集合的NAND串驻存在相同存储器裸片的不同块中。在一个实施例中,两个集合的NAND串驻存在不同存储器裸片中。在一个实施例中,两个集合的NAND串驻存在元块的不同块中。进程1700不限于前述实例。

步骤1702包含以第一顺序次序对第一三维结构中的第一集合的NAND串的第一层中的第一非易失性存储器单元进行编程。第一非易失性存储器单元驻存在第一三维结构的第一层内。第一顺序次序是从第一层的漏极端到源极端。

步骤1704包含以第二顺序次序对第二三维结构的第二集合NAND串的第二层中的第二非易失性存储器单元进行编程。第二非易失性存储器单元驻存在第二三维结构的第二层内。第二顺序次序是从第二层的源极端到漏极端。第二层和第一层在对应的第一和第二三维结构的相同层级处。举例来说,第一和第二层可各自是下部层508。作为另一实例,第一和第二层可各自是上部层510。在一个实施例中,如在图5B中,NAND串驻存在单一层中。

图18A是对两个不同块或子块的下部层中的非易失性存储器单元进行编程的进程1800的一个实施例的流程图。进程1800用于以另一下部层的反转顺序对一个下部层进行编程。进程1800提供对于进程1700的一个实施例的其它细节。

步骤1802包含以第一顺序次序从下部层的源极端到下部层的漏极端来对第一块或子块的下部层进行编程。步骤1802可包含从下部层的源极端到下部层的漏极端依序对下部层中的字线进行编程。举例来说,关于图7A,从WL0到WL47依序对字线进行编程。在一个实施例中,对块(例如,BLK0)中的字线进行编程。在一个实施例中,对子块(例如,SB0)中的字线进行编程。

步骤1804包含以第二顺序次序从层的漏极端到层的源极端来对第二块或子块的下部层进行编程。步骤1804可包含从下部层的漏极端到下部层的源极端依序对下部层中的字线进行编程。举例来说,关于图7A,从WL47到WL0依序对字线进行编程。在步骤1802中的对块进行编程的情况下,接着在步骤1804中对块进行编程。在步骤1802中对子块进行编程的情况下,接着在步骤1804中对子块进行编程。

图18B是对两个不同块或子块的上部层中的非易失性存储器单元进行编程的进程1820的一个实施例的流程图。进程1820用于以另一上部层的反转顺序对一个上部层进行编程。进程1820提供对于进程1700的一个实施例的其它细节。进程1820描述上部层的编程,然而进程1800描述下部层的编程。因此将不会详细地描述进程1820。步骤1822包含以第一顺序次序从下部层的源极端到下部层的漏极端来对第一块或子块的上部层进行编程。步骤1822可包含从下部层的源极端到下部层的漏极端依序对上部层中的字线进行编程。步骤1824包含以第二顺序次序从层的漏极端到层的源极端来对第二块或子块的上部层进行编程。步骤1824可包含从下部层的漏极端到下部层的源极端依序对上部层中的字线进行编程。

图19描绘以与另一三维存储器结构的层反转的顺序对一个三维存储器结构的一个层进行编程的进程1900的一个实施例的流程图。进程1900提供用于图17、18A和18B的其它细节。

步骤1902包含将用于第一集合的NAND串的选定字线设定为第一层中的最低编号字线。步骤1902还包含将用于第二集合NAND串的选定字线设定为用于第二层的最高编号字线。作为一个实例,如果第一和第二层各自是下部层508,那么将用于第一层的选定字线设定为WL0且将用于第二层的选定字线设定为WL47。作为另一实例,如果第一和第二层各自是上部层510,那么将用于第一层的选定字线设定为WL48且将用于第二层的选定字线设定为WL95。作为另一实例,如果如图5B中三维结构具有单一层,那么将用于第一层的选定字线设定为WL0且将用于第二层的选定字线设定为WL95。可由控制器102进行步骤1902。

步骤1904包含对用于第一集合的NAND串的选定字线进行编程。步骤1906包含对用于第二集合NAND串的选定字线进行编程。步骤1904可包含控制器102将编程指令发送到一个或多个存储器裸片。存储器裸片300可使用例如状态机312、芯片上地址解码器314、功率控制316、行解码器324、列解码器332和/或读写电路328来进行编程。读写电路328含有感测块350,所述感测块350可用于在编程期间控制到位线的电压以及在编程验证期间感测位线。

步骤1906包含确定是否存在更多待编程的字线。控制器102可进行步骤1906。如果存在更多待编程的字线,那么控制转到步骤1908。步骤1908包含递增用于第一集合的NAND串的选定字线。步骤1908还包含递减用于第二集合NAND串的选定字线。可由控制器102进行步骤1908。在步骤1908后,控制转到步骤1904。重新调用步骤1904a是为对用于第一集合的NAND串的选定字线进行编程且重新调用步骤1904b是为对用于第二集合NAND串的选定字线进行编程。当层中不存在更多待编程的字线(步骤1906=无)时,进程结束。

在一些实施例中,系统反转对特定NAND串进行编程的顺序。图20是反转对NAND串进行编程的顺序的进程2000的一个实施例的流程图。图20描述对完整NAND串进行编程。NAND串可以在单一层结构中,例如图5B中的NAND串;或在多层结构中,例如图5A中的NAND串。在一个实施例中,在子块(例如,图7A中的SB0)中的NAND串上进行进程2000。在一个实施例中,在块(例如,图7A中的BLK0)中的NAND串上进行进程2000。在一个实施例中,在元块中的NAND串上进行进程2000。元块可由不同存储器裸片中的块形成。

步骤2002包含在第一方向上关于NAND串的顶部和底部对三维结构中的NAND串进行编程。步骤2002包含从NAND串的一端到NAND串的另一端来对NAND串进行编程。在一个实施例中,从源极端到漏极端依序对NAND串进行编程。在一个实施例中,从漏极端到源极端依序对NAND串进行编程。

步骤2004包含确定是否反转对NAND串进行编程的顺序次序。在一个实施例中,确定是基于作为NAND串的子块或块内是否存在缺陷。在一个实施例中,确定是基于作为NAND串的不同子块或块中是否存在缺陷。

如果确定不反转顺序次序,那么控制转到步骤2002。如果确定反转顺序次序,那么控制转到步骤2006。应注意,擦除NAND串的步骤并未明确地描绘于图20中,但可在进行步骤2002或2006之前,将NAND串擦除。

步骤2006包含以第二顺序次序关于NAND串的顶部和底部来对NAND串进行编程。步骤2006包含从NAND串的一端到NAND串的另一端来对NAND串进行编程。如果在步骤2002中从源极端到漏极端依序对NAND串进行编程,那么在步骤2006中从漏极端到源极端依序对NAND串进行编程。如果在步骤2002中从漏极端到源极端依序对NAND串进行编程,那么在步骤2006中从源极端到漏极端依序对NAND串进行编程。

如上所述,一些NAND串可驻存在具有多个层的三维结构中。在一些实施例中,系统反转在一个层中进行编程的顺序,但不一定反转在另一层中进行编程的顺序。图21是反转对NAND串的一部分进行编程的顺序次序的进程2100的一个实施例的流程图。NAND串驻存在具有多个层的三维结构中,例如在图5A和7A中。被编程的NAND串的部分含有三维结构的一个层中的存储器单元。在一个实施例中,在子块(例如,图7A中的SB0)中的NAND串上进行进程2100。在一个实施例中,在块(例如,图7A中的BLK0)中的NAND串上进行进程2100。在一个实施例中,在元块中的NAND串上进行进程2100。元块可由不同存储器裸片中的块形成。

步骤2102包含以第一顺序次序关于层的顶部和底部对NAND串的一个层进行编程。层具有关于NAND串的漏极和源极端限定的漏极端和源极端。步骤2102包含从层的一端到层的另一端来对NAND串进行编程。在一个实施例中,从层的源极端到漏极端依序对NAND串进行编程。在一个实施例中,从层的漏极端到源极端依序对NAND串进行编程。

步骤2104包含确定是否反转对NAND串的层进行编程的顺序次序。在一个实施例中,确定是基于作为NAND串的子块或块内是否存在缺陷。在一个实施例中,确定是基于作为NAND串的不同子块或块中是否存在缺陷。

如果确定不反转顺序次序,那么控制转到步骤2102。如果确定反转顺序次序,那么控制转到步骤2106。应注意,擦除NAND串的步骤并未明确地描绘于图21中,但可在进行步骤2102或2106之前,将NAND串擦除。

步骤2106包含以第二顺序次序关于层的顶部和底部来对NAND串进行编程。步骤2106包含从层的一端到层的另一端来对NAND串进行编程。如果在步骤2102中从层的源极端到漏极端依序对NAND串进行编程,那么在步骤2106中从层的漏极端到源极端依序对NAND串进行编程。如果在步骤2102中从层的漏极端到源极端依序对NAND串进行编程,那么在步骤2106中从层的源极端到漏极端依序对NAND串进行编程。

图22A和22B描绘示出如何反转编程顺序可提供良好字线的更大连续信息块的表。图22A描绘展示八个存储器裸片中的每一个中哪一物理字线是良好和不良的表2202。存储器裸片0、裸片3和6中的字线WL93、WL94和WL95是不良的。存储器裸片1和裸片7中的字线WL0、WL1和WL2是不良的。这在字线WL3到WL92之间的留下良好字线的连续信息块2204,其是90个连续字线。

图22B描绘展示由于反转裸片中的一些的编程顺序而引起被称作逻辑字线的表2212。确切地说,在存储器裸片1和裸片7中反转字线编程顺序,所述存储器裸片1和裸片7是其中WL0到WL2是不良的裸片。反转用于这两个存储器裸片的字线编程顺序将有效地将不良字线放置在编程顺序结束时。这通过展示不良字线目前逻辑上在用于存储器裸片1和裸片7的WL93、WL94和WL95处而描绘于表2212中。另一存储器裸片尚未使其编程顺序反转。净结果是字线的逻辑上连续的信息块2214目前是从逻辑字线WL0到WL92,其是93个逻辑字线。因此,通过反转存储器裸片1和裸片7中的编程顺序,连续信息块已从90个字线增长到93个字线。

具有愈大连续信息块2214可使得更容易地管理编程。作为一个实例,元页可以由连续信息块2214中的93个良好逻辑字线形成。通过更小连续信息块2204,一个选项是不使用任一裸片中的字线WL0、WL1、WL2、WL93、WL94或WL95中的任一个,其产生比图22B的实例更小的存储。

所公开技术的第一方面包含非易失性存储装置,包括非易失性存储器单元;字线,连接到非易失性存储器单元;和控制电路,连接到非易失性存储器单元和字线。控制电路配置成以第一顺序次序对字线集合进行编程。控制电路配置成在以第一顺序次序对字线集合进行编程后,将字线集合擦除。字线集合包括擦除单位。控制电路配置成在所述擦除后,以第二顺序次序对字线集合进行编程。第二顺序次序与第一顺序次序不同。

在第一方面的进一步中的所公开技术的第二方面中,第二顺序次序通过存储器裸片、存储器块和编程/擦除循环中的至少一个改变编程顺序。

在第一或第二方面的进一步中的所公开技术的第三方面中,第二顺序次序是第一顺序次序的反转。

在第一到第三方面中的任一个的进一步中的所公开技术的第四方面中,控制电路进一步配置成响应于确定非易失性存储装置中存在缺陷而将对字线集合进行编程的方向从第一顺序次序反转为第二顺序次序。

在第一到第四方面中的任一个的进一步中的所公开技术的第五方面中,响应于字线集合的编程/擦除循环计数超出阈值将对字线集合进行编程的方向从第一顺序次序反转为第二顺序次序。

在第一到第五方面中的任一个的进一步中的所公开技术的第六方面中,字线集合是第一字线集合。控制电路进一步配置成以第一顺序次序对第二字线集合进行编程,同时以第二顺序次序对第一字线集合进行编程,其中第二字线集合包括擦除单位。

在第一到第六方面中的任一个的进一步中的所公开技术的第七方面中,控制电路进一步配置成将元页的第一物理页编程到第一字线集合的第一字线中,且将元页的第二物理页编程到第二字线集合的第二字线中。

在第一到第七方面中的任一个的进一步中的所公开技术的第八方面中,控制电路进一步配置成利用第一物理页和第二物理页形成冗余数据。控制电路进一步配置成存储冗余数据。控制电路进一步配置成使用冗余数据恢复第一物理页或第二物理页。

在第一到第八方面中的任一个的进一步中的所公开技术的第九方面中,非易失性存储装置包括多个存储器裸片,第一字线集合驻存在多个存储器裸片中的第一存储器裸片中,且第二字线集合驻存在多个存储器裸片中的第二存储器裸片中。

在第一到第九方面中的任一个的进一步的所公开技术的的第十方面中,非易失性存储装置进一步包括其中驻存第一字线集合的第一三维结构和其中驻存第二字线集合的第二三维结构。第一字线集合和第二字线集合驻存在对应的第一和第二三维结构的相同层级中。

在第一到第九方面中的任一个的进一步中的所公开技术的第十一方面中,非易失性存储器单元被配置为各自具有漏极端和源极端的NAND串。另外,控制电路进一步配置成从源极端到漏极端对字线集合进行编程从而以第一顺序次序对字线集合进行编程。另外,控制电路进一步配置成从漏极端到源极端对字线集合进行编程从而以第二顺序次序对字线集合进行编程。

在第一到第十一方面中的任一个的进一步的所公开技术的的第十二方面中,非易失性存储装置进一步包括三维结构,所述三维结构包括多个层,字线集合驻存在三维结构的第一层中。控制电路进一步配置成从第一层的第一端到第二端依序对字线集合进行编程从而以第一顺序次序对字线集合进行编程。控制电路配置成从第一层的第二端到第一端依序对字线集合进行编程从而以第二顺序次序对字线集合进行编程。

在第一到第十二方面中的任一个的进一步中的所公开技术的第十三方面中,控制电路配置成使用多阶段编程操作对字线集合中的每一字线进行编程,其中在以第一顺序在第一选定字线后的字线上进行多阶段编程操作的至少一个阶段后,完成第一选定字线的多阶段编程操作的最后阶段。

所公开技术的一个实施例包含一种操作非易失性存储器的方法。所述方法包括以第一顺序次序从子集的第一端到第二端对三维结构中的NAND串上的非易失性存储器单元的子集进行编程。所述方法包括在以第一顺序次序对子集进行编程后确定三维结构内存在缺陷。所述方法包括在以第一顺序次序对子集进行编程后,将非易失性存储器单元的子集擦除。所述方法包括响应于确定三维结构内存在缺陷而以第二顺序次序从子集的第二端到第一端对非易失性存储器单元的子集进行编程。

所公开技术的一个实施例包含非易失性存储装置,其包括多个三维结构。每一三维结构包括NAND串,所述NAND串包括非易失性存储器单元。每一NAND串包括漏极端和源极端。每一三维结构包括一个或多个层。每一层包括相对于NAND串的漏极端和源极端限定的漏极端和源极端。非易失性存储装置进一步包括用于以第一顺序对三维结构中的第一个的第一层中的第一NAND串上的第一非易失性存储器单元进行编程的构件。第一非易失性存储器单元驻存在第一层中。非易失性存储装置进一步包括用于以第二顺序对三维结构中的第二个的第二层中的第二NAND串上的第二非易失性存储器单元进行编程的构件。第一层和第二层驻存在对应的第一和第二三维结构的相同层级处。

用于以第一顺序对三维结构中的第一个的第一行中的第一NAND串上的第一非易失性存储器单元进行编程的构件包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于以第一顺序对三维结构中的第一个的第一层中的第一NAND串进行编程的构件进行进程1900。在一个实施例中,用于以第一顺序对三维结构中的第一个的第一层中的第一NAND串进行编程的构件进行进程1400。

用于以第二顺序对三维结构中的第二个的第二层中的第二NAND串上的第二非易失性存储器单元进行编程的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于以第二顺序对三维结构中的第二个的第二层中的第二NAND串上的第二非易失性存储器单元进行编程的构件进行进程1900。在一个实施例中,用于以第二顺序对三维结构中的第二个的第二层中的第二NAND串上的第二非易失性存储器单元进行编程的构件进行进程1400。

在一个实施例中,用于以第一顺序对三维结构中的第一个的第一层中的第一NAND串上的第一非易失性存储器单元进行编程的构件包括用于以第一顺序次序对第一非易失性存储器单元进行编程的构件。在一个实施例中,用于以第二顺序对三维结构中的第二个的第二层中的第二NAND串上的第二非易失性存储器单元进行编程的构件包括用于以第一顺序次序的反转的第二顺序次序对第二非易失性存储器单元进行编程的构件。

用于以第一顺序次序对三维结构中的第一个的第一NAND串上的第一非易失性存储器单元进行编程的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于以第一顺序次序对三维结构中的第一个中的第一NAND串上的第一非易失性存储器单元进行编程的构件进行进程1900。

用于以第一顺序次序的反转的第二顺序次序对第二非易失性存储器单元进行编程的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于以第一顺序次序的反转的第二顺序次序对第二非易失性存储器单元进行编程的构件进行进程1900。

非易失性存储装置的一个实施例进一步包含用于将元页的第一物理页编程到第一非易失性存储器单元的第一群中的构件;和用于将元页的第二物理页编程到第二非易失性存储器单元的第二群中的构件。

用于将元页的第一物理页编程到第一非易失性存储器单元的第一群中的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于将元页的第一物理页编程到第一非易失性存储器单元的第一群中的构件进行进程1600。

用于将元页的第二物理页编程到第二非易失性存储器单元的第二群中的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于将元页的第二物理页编程到第二非易失性存储器单元的第二群中的构件进行进程1600。

非易失性存储装置的一个实施例进一步包含用于以第一顺序次序从第三层的源极端到漏极端来对第三三维结构的一个或多个层中的第三层中的第三NAND串上的非易失性存储器单元进行编程的构件;用于在以第一顺序次序对第三NAND串上的非易失性存储器单元进行编程后将第三NAND串上的非易失性存储器单元擦除的构件;和用于在所述擦除后以第二顺序次序从第三层的漏极端到源极端来对第三NAND串上的非易失性存储器单元进行编程的构件。

用于以第一顺序次序从第三层的源极端到漏极端来对第三三维结构的一个或多个层中的第三层中的第三NAND串上的非易失性存储器单元进行编程的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于以第一顺序次序从第三行的源极端到漏极端来对第三三维结构的一个或多个层中的第三层中的第三NAND串上的非易失性存储器单元进行编程的构件进行进程1900。

用于在以第一顺序次序对第三NAND串上的非易失性存储器单元进行编程后将第三NAND串上的非易失性存储器单元擦除的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于在以第一顺序次序对第三NAND串上的非易失性存储器单元进行编程后将第三NAND串上的非易失性存储器单元擦除的构件进行图10A的进程。

用于将元页的第二物理页编程到第二非易失性存储器单元的第二群中的构件可包含控制器102、控制电路310(其可包含状态机312、芯片上地址解码器314、功率控制316)、行解码器324、列解码器332、读写电路328和/或感测块350中的一个或多个。控制器102可包含FEP 110和BEP 112。在一个实施例中,状态机312可由软件进行编程。在其它实施例中,状态机312不使用软件且完全实施于硬件(例如,电路)中。在一些实施例中,状态机312可由微控制器或微处理器替代。在一个实施例中,用于将元页的第二物理页编程到第二非易失性存储器单元的第二群中的构件进行进程1600。

出于本文的目的,说明书中对“实施例”、“一个实施例”、“一些实施例”或“另一实施例”的引用可用于描述不同的实施例或相同的实施例。

出于本文的目的,连接可以是直接连接或间接连接(例如,通过一个或多个其它部分)。在一些情况下,当元件被称为连接或耦合到另一元件时,所述元件可以直接连接到另一元件或中间中间元件间接连接到另一元件。当一个元件被称为直接连接到另一个元件时,则所述元件与另一元件之间不存在中间元件。如果两个装置直接或间接连接,使得这两个装置可以在它们之间传送电子信号,那么所述两个装置“通信”。

出于本文的目的,术语“基于”可以被理解为“至少部分基于”。

出于本文的目的,在没有额外上下文的情况下,例如“第一”目标、“第二”目标和“第三”目标的数值术语的使用可能并不暗示目标的顺序,而是可替代地用于标识目的以标识不同的目标。

出于本文的目的,术语目标的“集合”可以指目标中的一个或多个的“集合”。

已出于说明和描述的目的呈现前述详细描述。其并不意欲为穷尽的或将本发明限制于所公开的精确形式。鉴于以上教示,许多修改和变化是可能的。选择所描述的实施例以最佳地解释所提出技术的原理和其实际应用,从而使所属领域的其它技术人员能够在各种实施例中以及适合于预期的特定用途的各种修改中最好地利用所述技术。希望范围由所附权利要求书定义。

- 非易失性存储器编程顺序

- 用于非易失性存储器的优化页编程顺序