利用额外电力网格补偿压降的方法与电路系统

文献发布时间:2023-06-19 11:45:49

技术领域

本公开涉及一种解决电路中压降的技术,特别是涉及利用布设额外的电力网格电力线补偿电路系统的压降的方法与相关系统。

背景技术

随着集成电路(Integrated Circuit,IC)制程技术的演进,一个芯片中可以容纳的电路组件(cell)密度更大,电路组件之间的线路更多且其宽度更窄,而芯片中这些电路组件的工作电压(operating voltage)的电压需求也更小,不过,随着在芯片上设计供电的电力网格(power mesh)传输电力的导线宽度变得更窄时,导线的等效电阻值上升,进而造成压降,对一个电路系统而言,这可能导致芯片无法运作的问题。

此外,集成电路上的各电路可以制作于多层结构中的各层中,以容纳更多的电路组件,不过这也更容易产生电力网格供电不易以及压降的问题。

设于集成电路上的电力网格可以参考图1显示的示意图,在多层结构的集成电路设计中,可以在特定几层中布设电力网格,如图式中不同层但交错的第一电力线101与第二电力线102,纵横交错的电力线形成所述电力网格,用以供电给不同层中设计的各种功能的电路组件105,各个电路组件105之间除了供应工作电压的电力线外,还设计有传输信号的信号线路107。

若要处理其中压降的问题时,一般的做法包括可以修改电源设计(如位置)、通过增加去耦合电容的方式补偿衰减的电压,或是依据压降情况提供补偿电压等方式。

发明内容

说明书公开一种利用额外电力网格补偿压降的方法与电路系统,其中电路系统如一集成电路,具有多层半导体组件结构,其中的一层或多层形成有多个电路组件,多个电路组件之间设有信号线路,并在原本布局中的一层或多层上布设一电力网格,电力网格包括有多条纵向电力线与多条横向电力线。

根据所述方法的目的之一,可以通过布设额外的电力网格电力线补偿电路系统中原本电路形成的压降,所述方法包括,先于电路系统的电路布局上切分为一个或多个区域,再对各区域执行布线溢出分析,得出各区域的布线溢出率,之后可以根据这些区域个别的布线溢出率的高低排序,以决定布设额外的电力网格电力线,达到补偿电路系统的压降的目的。

优选地,所述电路系统的一层切分为一个或多个区域,在此层中闲置的金属导线布设所述额外的电力网格电力线。

优选地,于执行布线溢出分析时,可根据电路系统中切分的各区域的布线线路、用为电力系统中多个电路组件之间信号线路的线路,以及用于电力网格的电力线等数据,能够以已被用为信号线路与电力网格的电力线所占用的面积除以相同区域内的全部布线线路占用的面积,得出布线溢出率。

进一步地,在决定如何布设额外电力线的考虑中,影响布线溢出率的因素还包括电路系统中电路布局中各金属导线的宽度,这些金属导线的宽度所占面积、系统设定的压降补偿比例,以及/或系统设定所要改善电路系统的电子迁移的程度等因素,用以决定布设额外的电力网格电力线的位置与数量。

为使能更进一步了解本公开的特征及技术内容,请参阅以下有关本公开的详细说明与图式,然而所提供的图式仅用于提供参考与说明,并非用来对本公开加以限制。

附图说明

图1显示集成电路中电力网格的范例示意图;

图2显示一个片上系统的多层立体结构示意图;

图3显示芯片中电路组件工作电压下降与时间的关系曲线;

图4显示利用芯片电路布局的仿真程序分析各区域压降的仿真示图;

图5显示利用额外电力网格补偿压降的方法中分析布线溢出的实施例流程图;

图6显示布线线路与电子迁移效应的关系曲线;

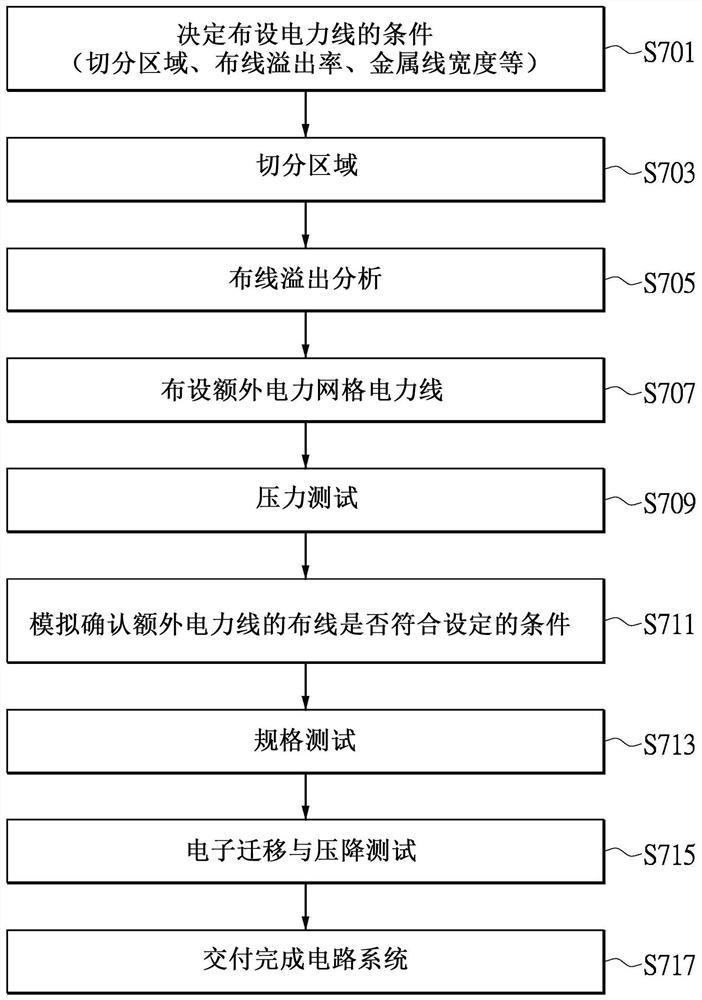

图7显示实现利用额外电力网格补偿压降的方法的实施例流程图;

图8显示布设额外电力网格的电力线的局部示意图;

图9显示利用额外电力网格补偿压降的方法形成的电路系统实施例示意图;

图10显示一个利用额外电力网格补偿压降的方法形成的电力网格实施例示意图。

具体实施方式

以下是通过特定的具体实施例来说明本公开的实施方式,本领域技术人员可由本说明书所公开的内容了解本公开的优点与效果。本公开可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不悖离本公开的构思下进行各种修改与变更。另外,本公开的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本公开的相关技术内容,但所公开的内容并非用以限制本公开的保护范围。

应当可以理解的是,虽然本文中可能会使用到“第一”、“第二”、“第三”等术语来描述各种组件或者信号,但这些组件或者信号不应受这些术语的限制。这些术语主要是用以区分一组件与另一组件,或者一信号与另一信号。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

而现今半导体制程采用层层堆栈的方式进行电路布局,每一层可以个别光罩处理后设计出各种不同功能的逻辑电路形成的电路组件。并在线路设计时,在特定几层布局上设计出连接电源与每个电路组件之间的电力网格,在相同或不同层上设计各种电路组件,整个系统通过电力网格搭配穿孔或是联机提供电力给每个电路组件,而电路组件之间或与外部系统之间以多个信号线路联机,因此在电路布局设计时,在芯片上已经布设有各种金属导线。

对于一个片上系统(System-on-Chip,SoC)而言,每一个逻辑电路的设计都会产生不同程度的压降(IR_Drop),压降是指出现在集成电路(IC)中电压下降的现象,主要理由是因为半导体制程技术的精进使得半导体芯片中电力网格(power mesh)上的金属导线的宽度越来越窄,导致导线上电阻值上升进而造成压降,对一个电路系统而言,压降可能是局部的,也可能是全面的。

此外,当半导体先进制程继续发展,并已经增进到奈米等级,在此尺度下,上述压降的现象对于集成电路(IC)中的逻辑电路将产生更大的影响,因此对于所述压降的宽容度也会愈小,如此,本说明书所提出的方案通过优化电力网格的方式可以降低整体集成电路的压降,可以有效改善压降产生的影响。

如此,说明书提出一种利用额外电力网格补偿压降的方法与电路系统,电路系统主要如利用半导体制程制作的集成电路(芯片),其中布设有电路布局,利用额外电力网格补偿压降的方法的技术概念是,随着制程上精密度的进步以及日渐降低的工作电压,为了补偿电力网格因为种种原因产生的压降,所述利用额外电力网格补偿压降的方法利用分析布线溢出(routing overflow)的结果得出芯片电路布局(layout)中的各区布线溢出率(overflow rate),可以得出芯片布局中布线溢出率比较小(密度较小)的区域按比例多补上一些电力网格,其中方法是在已经设计好的布局中选定一些可利用(available)的布线线路(route track)成为电力网格上的电力线,以再利用布线线路成为电力网格的方式达到补偿压降的效果。

图2显示一个片上系统的多层立体结构实施例示意图。

图中显示一集成电路2简化后的多层结构示意图,主要多层结构中的电路组件形成于一半导体层20之上,保护层26之下,此范例显示其中有八层电路结构层,各层间以绝缘层24隔开,由底至顶包括多层金属层(221、222……至228)。此集成电路2形成一个电路系统,其中金属层(221、222……至228)中的部分或全部依据电路系统的设计形成各种电路组件。所述多层结构的层数并非用于限制说明书所揭示电路系统的实施方式。

根据应用利用额外电力网格补偿压降的方法的电路系统实施例,集成电路2中的电路组件可设于部分结构层中,如金属层221~226,电路组件之间设计有金属导线,电力网格可制作在金属层227~228上,各层上的电路组件与电力线可以穿孔(via)与布线线路相互电性连接。

根据利用额外电力网格补偿压降的方法的技术目的之一,就是再利用芯片电路布局中可利用的布线线路成为电力网格的电力线,以此方式将降低原本压降造成工作电压不足或不稳的问题,图3显示芯片中电路组件工作电压(纵轴)下降与时间的关系,其中曲线301显示在芯片开始运作时,其中特定电路组件因为导线的电阻造成的压降情形,随着时间(横轴)一久也逐渐稳定在一个电压值内。

曲线303为利用额外电力网格补偿压降的方法得到压降补偿的电压曲线,如图显示,补偿后仍有压降,但已经改善,其中可以根据整体电路设计的需求调整改善的目标,同时调整补偿的电力线设计,图中显示改善的幅度为X%(如10%),改善后的压降也是随着时间增长压降变化也趋于稳定。

在所述利用额外电力网格补偿压降的方法中执行压降分析,这是一个计算机仿真的方法,其中步骤是将电力输入至一个芯片电路布局中,再以仿真程序得出各电路布局中各个区域的工作电压,以得出压降分布,有关在电路布局中压降分析的示意图可参考图4,其中显示利用一种布线路线察觉电力网格分析方法(route track aware opt power meshir_drop analysis)得出一个芯片电路布局中压降的状态,再以图像处理的方式用色块标示出各区域的压降程度,即图中显示利用芯片电路布局的仿真程序分析各区域压降程度的仿真图。

其中方法是,先将一或多种电压值输入电路布局,分次计算不同位置或电路组件的工作电压的压降情形,可再予以统计电压值,所述布线路线察觉电力网格的方式为检测各区域输出电压得出压降,形成一个压降分布图,设有一个基准,各区域压降值与此基准比对后,可得各区域压降的比例,在此例中,产生出图中圈出的几个区域为有较大压降的区域401、403、405与407。

根据所揭示的利用额外电力网格补偿压降的方法的目的,为通过布设于电路布局上的额外电力网格以补偿上述分析方法得出的压降,而布设额外电力网格的电力线的建议位置可通过布线溢出的分析得出,其中主要的方式如图5所示分析布线溢出的实施例流程图。

一开始,如步骤S501,先依据需求与所需的精密度逻辑上切分为多个区域,其目的是分区判断布线溢出率,若为多层的半导体组件结构,即逐层切分为多个区域,并分别进行布线溢出的分析。

在步骤S503中,取得多层结构的芯片中每层的电路布局,包括其中各个区域中设计的布线线路以及已经被占用的线路,被占用的线路例如为设计提供给电路组件的信号线路。举例来说,以电路系统的仿真程序而言,根据布局设计,布局中电路组件之间的信号线路为已知,原本电力网格的纵横电力线为已知,而闲置的金属导线的部分也为已知,因此可以执行布线溢出分析。

接着,如步骤S505,在各区域中,布线溢出率的表示方法可为多种,其中之一可以将被占用的线路占用的面积除以相同区域内的全部布线线路占用的面积,以得出布线溢出率,如步骤S507。得出布线溢出率后,从这个定义下的布线溢出率可得到各区域布线溢出的变化,也同时提供了不同的电力网格布线的建议。

根据一实施例,所建议布设额外电力线的方案还可考虑整体电路系统所设定要达到的一压降补偿比例,例如10%,也就是说,再利用原本芯片上闲置的金属导线时,可以依照压降补偿的需求(如补偿10%压降)选择布设额外电力线的位置(区域)与数量(面积占比)。

所述布线溢出率反映出占用的布线密度,使得电路系统可以根据布线的密度大小补上比例不等的电力网格电力线。举例来说,布线溢出率低的部位表示占用的布线线路的密度较小,也就建议可以加上较多的电力网格的电力线,也就是利用其中闲置的金属导线作为电力网格额外的电力线;反之,布线溢出率较高的部位表示占用布线线路密度较大,建议加上较少的电力网格的电力线,甚至是不再利用其中线路作为电力线之用。

经布线溢出分析后,得出各区域中布线溢出率的高低排序,其中有较高与较低布线溢出率的区域,较高布线溢出率表示其中具有较少可利用的布线线路的机率,为制程中预留较少的闲置金属导线(dummy metal)的区域;反之,若得出有低布线溢出率的区域,表示这些区域预留较多的闲置金属导线,即可用于布设补偿压降的电力网格的电力线,这样的话可以在不用增加硬件成本的情况下得到补偿压降的效果。

在一实施例中,以所得出的布线溢出率,加上电路系统中电路布局的全部金属导线的宽度的面积占比,可决定布设额外的电力网格电力线的位置与数量。然而,根据实施例,若要权衡出可以布设电力线的程度时,除了上述整个电力系统对于压降补偿的程度外,还应考虑如以下实施例所描述解决多少电子迁移现象的需求。

经过布线溢出分析后,电路系统可得到了一个或多个不同的电力网格布线的建议,除达到补偿压降的目的外,还可藉此避免芯片中金属导线的电子迁移(Electromigration,EM)效应,这是用于避免导线上因为电子迁移造成离子扩散的问题。可参考图6显示布线线路与电子迁移效应的关系曲线。

图6中的曲线表示布线线路的数量(或面积占比)与电子迁移效应的关系,曲线显示原始的芯片电路布局具有一定比例的电子迁移现象,可以通过再利用闲置的金属导线改善电子迁移现象。然而,此关系曲线显示布线线路的数量也不是愈多愈好,而是在增加布线线路作为电力线达一比例(Y%,如5%)时,可以有效改善电子迁移的现象,如改善的电子迁移比例达60%。之后,当布线线路达一定数量(或面积)或更多时,要以增加布线线路来解决电子迁移现象,效果也受到限制。

因此,再利用原本芯片上闲置的金属导线时,除上述考虑补偿压降的比例(X%)外,还可以依照所需改善电路系统中线路的电子迁移的程度(对应电力线占比Y%)选择布设电力线的位置与数量。

图7显示实现利用额外电力网格补偿压降的方法的实施例流程图。

在此图例流程中,先将芯片布局根据需要处理的精密度切割为一个或多个区域(可选择全部电路布局为一个区域),在步骤S701中,即在所切割的多个区域中决定布设电力线的条件,如所述布线溢出率与金属线宽度等,接着即如步骤S703,将整个芯片布局依照实际需求将整个电路布局切分为多个进行后续分析的区域。

举例来说,先定义出每层电路布局切分后的区域(grid(n,n)),共n乘n个区域,多个区域以数组形式表示,共计有$num(1,1)、$num(1,2)…、$num(n,n),之后逐区进行布线溢出分析(步骤S705),可以得出每个区域的布线溢出的大小与方案,并进而得出布线溢出率,再予以排序,得出布线溢出率相对较低至高的排序,布线溢出率相对较低者为可增加电力线布局的优先选择区域,即可如此执行布设额外电力网格的电力线(步骤S707)。

然而,其中仍有权衡的条件,而不是仅选择布线溢出率低的区域进行额外布设电力线,例如,可以布线溢出率配合金属导线的宽度(面积占比)决定额外布设电力线,以不占用整体布线线路的一个特定比例(如5%)作为选择增加电力线的位置与数量的限制条件。因此,即便在某些区域中具有可以布设额外电力线的空间,但仍可能受限于电路系统设定的整体布线线路的比例限制,因此在大于所述特定比例的区域将不会被列入增加额外电力网格电力线的选择中。

接着,如步骤S709,执行一压力测试,压力测试可以是一种软件仿真程序,对完成上述布线与额外增加电力网格电力线的电路系统输入各种不同数值的电压,在步骤S711,可以根据模拟运作与输出结果确认所述额外电力线的布线是否符合设定的条件。完成压力测试后,若通过测试,还有后续测试。

当决定了额外电力网格电力线的布线后,除上述条件外,还须考虑后续制程的规格,进行如步骤S713中的规格测试,这可以是晶圆厂提出的制程规格,称为设计规则检核(Design Rule Check,DRC),也就是电路系统中的电路布局需要符合实际制作时的规格。其中,设计规则检核是将所设计的电路系统(如IC)导入晶圆厂提供的检核工具中,检核多层半导体结构中各层的规则,进行除错和验证,以符合制程规范。

通过上述检核后,还可在步骤S715中,对整体电子迁移与压降测试,也就是在决定布设额外电力网格电力线时,还应考虑整体电路系统能够改善电子迁移现象的程度,改善的程度有其极限,因此决定一适当布设电力线的位置与数量,过多增加电力线并无益处。对于压降测试则是量测完成布设额外电力线的电路系统的压降,计算是否达到预期补偿压降的效果。

最后,当完成上述布局设计与检核后,如步骤S717,即可交付后续制作以完成电路系统。在此一提的是,说明书提出的利用额外电力网格补偿压降的方法的检核步骤并不限于上述流程,步骤之间仍可以前后置换。

接着显示应用利用额外电力网格补偿压降的方法制作的电路系统的实施例示意图,如图8所示电力网格的电力线的局部示意图。

在显示的电力网格中,原始设计电力线包括纵向电力线801与横向电力线803,而通过上述方法额外增加的电力线包括纵向新增电力线805与横向新增电力线807。

所述电路系统包括有多层半导体组件结构,即如集成电路,其中电路组件形成于其中的一层或多层,电路布局中还包括了多个电路组件之间的信号线路,根据实际需求,可在一层或多层上布设电力网格,电力网格的布设一般来说可以根据设计选择在特定几层中,也可为电路组件少的几层中,电力网格可为多条纵向电力线与多条横向电力线所组合的结构。

图9则是显示利用额外电力网格补偿压降的方法形成的电路系统实施例示意图。图中的电力网格包括上述局部图显示的纵向电力线801与横向电力线803,加上纵向新增电力线805与横向新增电力线807。其余部分为电路系统的电路组件88,以及组件之间的信号线路89,在示意所示的布局中,所述电力线(801、803、805与807)、电路组件88与信号线路89可以为多层半导体结构的电路系统中的特定某层的结构,或是分别设于不同层的结构。

图10显示一个利用额外电力网格补偿压降的方法形成的电力网格实施例示意图,其中表示一个电路系统中的网格电力线,根据上述实施例可知,布设额外电力网格电力线的主要考虑为布线溢出率,但也根据需求可以权衡出要增加电力线的区域,并且电力线数量并非愈多愈好,而会考虑到整体效能的极限。因此,整体上来看不一定是平均分布在整个电路布在线,而可能产生此例中电力线密度较大的区域100以及密度较小的区域110。

综上所述,根据说明书所提出的利用额外电力网格补偿压降的方法与电路系统,根据实施例之一,为提出针对半导体芯片设计中以增加额外电力网格补偿压降的方案,主要的技术手段就是先分析芯片设计时的布线溢出(routing overflow)的情况,先得出电路布局上的各区域布线溢出率,藉此找到可以补上电力网网格线的适当位置,例如是布线线路密度比较小的部位,可以按照密度大小补上比例不等的电力网格的电力线,以补偿整体电路布局的压降。

以上所公开的内容仅为本公开的优选可行实施例,并非因此局限本公开的权利要求范围,所以凡是运用本公开说明书及图式内容所做的等效技术变化,均包含于本公开的权利要求范围内。

【符号说明】

第一电力线 101

第二电力线 102

电路组件 105

信号线路 107

集成电路 2

半导体层 20

保护层 26

绝缘层 24

金属层 221,222,223,224,225,226,227,228

曲线 301,303

较大压降的区域 401,403,405,407

纵向电力线 801

横向电力线 803

纵向新增电力线 805

横向新增电力线 807

电路组件 88

信号线路 89

密度较大的区域 100

密度较小的区域 110

步骤 S501~S507分析布线溢出的流程

步骤 S701~S717实现利用额外电力网格补偿压降的流程。

- 利用额外电力网格补偿压降的方法与电路系统

- 一种利用有源电力滤波器进行谐波电流补偿的方法