一种在GPDPU模拟器上高效执行矩阵加法的数据流处理方法

文献发布时间:2023-06-19 12:13:22

技术领域

本发明涉及矩阵加法的运算,具体而言,涉及一种在GPDPU模拟器上高效执行矩阵加法的数据流处理方法。

背景技术

在处理器体系结构的研究中,模拟器占有举足轻重的地位。模拟器技术贯穿于整个系统开发的过程之中:开发前期使用模拟器进行粗粒度模拟,以选择出最优的解决方案;开发期间对各种微结构进行验证;开发后期用模拟器进行软件开发及测试。在整个硬件系统投入运行后,还可以基于模拟器获取单纯依靠硬件系统无法得到的剖析(profiling)信息,对系统进行瓶颈分析及性能优化。在计算机基础研究过程中,模拟器可以模拟出各种现有体系结构甚至未来的新型体系结构,从而可以促进微结构和系统软件的研究。

指令的执行依靠数据来驱动,一旦操作数齐备该条指令就可以执行,利用图扩展的方式,规范不同指令之间的依赖关系,可以使得数据在不同指令之间流动起来。使用这种方式,提前将指令映射到各处理单元(PE),并设定好指令之间的依赖关系,将不再需要额外逻辑,指令执行完毕后,自动送给依赖关系指定的后续指令。相对于控制流结构,数据流结构不存在指令计数器,指令启动执行的时机取决于操作数具备与否,并且执行顺序由指令间的依赖关系决定。换言之,只要有足够多的处理单元(PE),凡是相互间不存在数据相关的指令,都可以并行执行,极大程度上提高了指令的并行性和处理器结构的浮点利用率。另外,数据流指令之间直接通信,不再需要共享寄存器堆或者共享缓存来实现数据交互,减少了访存次数,提高了存储带宽的有效利用率。同时,数据流计算模式中的执行单元都相对简单,没有分支预测逻辑、乱序执行控制逻辑、重排序队列、保留站等复杂控制逻辑和存储单元,因此数据流执行单元的集成度较高,具有更高能效比。

矩阵加法的输入是要相加的两个矩阵,其大小必须一致为mxn,一般矩阵加法才有定义,然后矩阵加法的具体操作是相应位置相加,这就会导致矩阵加法的访存次数是计算次数的三倍,使得在传统处理器上的计算部件利用率不高,同时跳转控制也会使得访存效率不高。传统的控制流处理器CPU能够提供各种通用计算但由于内存瓶颈以及指令计数器的影响,对于某种高性能计算(如矩阵加法)性能并不高,同时由于访存的原因,给计算部件供数的速度极低,导致计算部件利用率低。

中国专利CN110008436A公开了一种基于数据流架构的快速傅里叶变换方法、系统和存储介质,其是在数据流处理器上完成的傅里叶变换,并不是更为常见的矩阵加法操作;

中国专利CN110941451A公开了一种数据流处理器指令映射方法及系统、装置,其中阐述了数据流处理器及其相关的指令,但并未对矩阵加法高效计算的具体设计方法做出阐述。

综上,矩阵加法具有访存比计算操作多的特点,现有技术并没有对矩阵加法这一普遍而又常见的算子在GPDPU上的实现与优化有阐述。

发明内容

本发明提供一种在GPDPU模拟器上高效执行矩阵加法的数据流处理方法,用以使矩阵加法在GPDPU上能够更高效率的完成。

为达到上述目的,本发明提供了一种在GPDPU模拟器上高效执行矩阵加法的数据流处理方法,其包括:

启动GPDPU的模拟器;

使用DMA从内存读取数据以及指令并将其输入至SPM,其中,数据为待求和的矩阵A和矩阵B,指令为驱动GPDPU执行矩阵加法操作的数据流指令;

根据矩阵A和矩阵B的大小,将矩阵A和矩阵B分别按行平均划分为M个子矩阵;

令每个子矩阵分别对应一个task,每个子矩阵内部的数据对应一个subtask;

为每个subtask配置N个PE,每个PE对应子矩阵内部数据量的1/N;

为每个PE分别配置数据流指令中的load指令的取数地址;

每个subtask对应的N个PE采用SIME32模式执行数据流指令,以完成加和运算,其中,M个task之间为并行执行;

输出矩阵A和矩阵B相加后的结果矩阵。

在本发明的一实施例中,执行矩阵加法操作的数据流指令包括load指令、add指令以及store指令。

在本发明的一实施例中,M为4,N为16。

本发明提供的在GPDPU模拟器上高效执行矩阵加法的数据流处理方法针对矩阵加法访存比计算操作多的特定以及GPDPU的特点,提高了执行矩阵的加法的执行效率、访存带宽以及计算部件的利用率;根据GPDPU上的计算资源以及计算模式,对输入数据按照task与subtask进行了划分,配合GPDPU的SIMD32部件以及相应的指令来计算矩阵加法,提高了计算资源的利用率,同时对不同规模的矩阵加法运算自适应。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

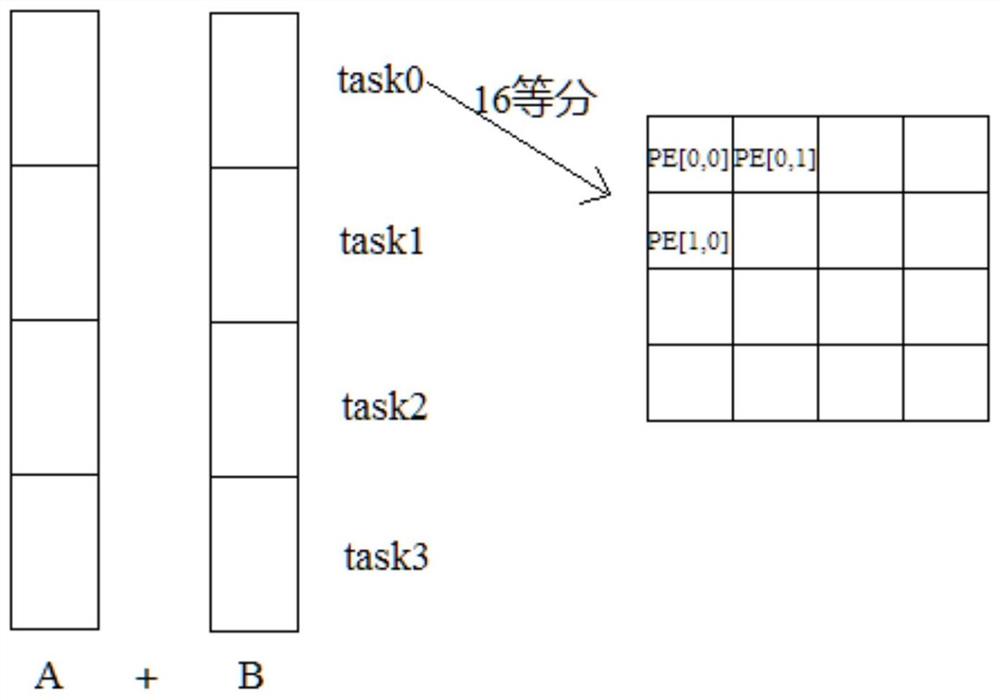

图1为本发明一实施例的矩阵计算示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有付出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明提供了一种在GPDPU模拟器上高效执行矩阵加法的数据流处理方法,其包括:

启动GPDPU的模拟器;

使用DMA从内存读取数据以及指令并将其输入至SPM,其中,数据为待求和的矩阵A和矩阵B,指令为驱动GPDPU执行矩阵加法操作的数据流指令;

根据矩阵A和矩阵B的大小,将矩阵A和矩阵B分别按行平均划分为M个子矩阵;

令每个子矩阵分别对应一个task,每个子矩阵内部的数据对应一个subtask;

为每个subtask配置N个PE,每个PE对应子矩阵内部数据量的1/N;

为每个PE分别配置数据流指令中的load指令的取数地址;

每个subtask对应的N个PE采用SIME32模式执行数据流指令,以完成加和运算,其中,M个task之间为并行执行;

输出矩阵A和矩阵B相加后的结果矩阵。

本领域技术人员已知,执行矩阵加法操作的数据流指令包括load指令、add指令以及store指令。每个PE的数据流指令中的两条load指令的取数地址,例如第一个PE对应的node(数据流图中的计算节点)分别从矩阵A的起始位置与矩阵B的起始位置取数,第二个PE从矩阵A与矩阵B起始位置的某个偏移处取数(这个偏移是第一个PE计算完加法的数据量)。

如图1所示为本发明一实施例的矩阵计算示意图,本实施例采用的矩阵A和矩阵B均为16*1024的float矩阵,需要16*1024次计算,本实施例中令M为4,N为16,即采用4task(task0~task3)模式,task0配置的指令是访存与计算前1/4数据量的加法,task1配置的指令是在第一个的基础上加上偏移,访存与计算1/4-2/4数据量的加法,task2配置的指令继续偏移,计算2/4-3/4数据量的加法,task3访存与计算最后1/4数据量的加法。同task类似的4分总数据,16个PE对应的16个node将每个task的数据16等分,每个PE对应的一个node依次负责其中一块。如上所述,设置好访存指令取数的偏移,使16个task能真正意义上的同时并行执行。

本实施例中,每个task需要进行4*1024次计算,16个PE且采用SIME32模式计算,则每个PE需要进行4*1024/(16*32)=8次运算,则每个csv指令文件中均有16个LDN、8个FADD以及8个STD。因此在task0中,PE[0,0]计算了前8个数(8次计算)的加法。Task0负责了前1/4个复数的加法。

本发明提供的在GPDPU模拟器上高效执行矩阵加法的数据流处理方法针对矩阵加法访存比计算操作多的特定以及GPDPU的特点,提高了执行矩阵的加法的执行效率、访存带宽以及计算部件的利用率;根据GPDPU上的计算资源以及计算模式,对输入数据按照task与subtask进行了划分,配合GPDPU的SIMD32部件以及相应的指令来计算矩阵加法,提高了计算资源的利用率,同时对不同规模的矩阵加法运算自适应。

本领域普通技术人员可以理解:附图只是一个实施例的示意图,附图中的模块或流程并不一定是实施本发明所必须的。

本领域普通技术人员可以理解:实施例中的装置中的模块可以按照实施例描述分布于实施例的装置中,也可以进行相应变化位于不同于本实施例的一个或多个装置中。上述实施例的模块可以合并为一个模块,也可以进一步拆分成多个子模块。

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的精神和范围。

- 一种在GPDPU模拟器上高效执行矩阵加法的数据流处理方法

- 一种单指令多数据流结构上的数据处理方法及处理器