具有多通道的高带宽存储器

文献发布时间:2023-06-19 12:19:35

背景技术

一种称为HBM(高带宽存储器)的存储器装置具有一种结构,在所述结构中堆叠各自具有多个通道的存储器芯片。所述通道可彼此异步地且非排他性地操作。由于相异数据路径分别指派到通道,HBM可高速地输入或输出大量数据。

当从控制器请求对一般HBM中的某个通道的存取时,选择包含在堆叠存储器芯片中的任一者中的存储器单元阵列。因此,当存取集中在同一通道中时,电流消耗集中在同一存储器芯片的同一区中,这可能导致电力电势的改变。

发明内容

本文公开用于具有多个通道的高带宽存储器的实例设备。在本公开的一个方面中,一种设备包含:控制芯片;多个存储器芯片,其堆叠在所述控制芯片上,所述多个存储器芯片包含第一及第二存储器芯片;以及多个通路导体,其连接在所述多个存储器芯片与所述控制芯片之间。所述第一及第二存储器芯片中的每一者被划分为包含第一通道的多个通道。所述多个通路导体包含电连接在所述第一存储器芯片中的所述第一通道与所述控制芯片之间的第一通路导体,以及电连接在所述第二存储器芯片中的所述第一通道与所述控制芯片之间的第二通路导体。所述第一及第二存储器芯片大体上同时将从所述第一通道读取的读取数据分别输出到所述第一及第二通路导体。

额外地或替代地,所述第一及第二存储器芯片分别从所述第一及第二通路导体同时接收待写入所述第一通道的写入数据。

额外地或替代地,所述第一存储器芯片中的所述第一通道位于与所述第二存储器芯片中的所述第一通道相同的平面位置。

额外地或替代地,所述第一及第二存储器芯片中的每一者中的所述第一通道具有包含第一存储体的多个存储体,且所述第一存储器芯片中的所述第一存储体位于与所述第二存储器芯片中的所述第一存储体不同的平面位置。

额外地或替代地,所述第一及第二存储器芯片中的每一者具有分别连接到所述第一及第二通路导体的第一及第二读取FIFO电路。

额外地或替代地,所述第一存储器芯片具有共同指派到所述第一及第二通路导体的第一读取FIFO电路,且所述第二存储器芯片具有共同指派到所述第一及第二通路导体的第二读取FIFO电路。

额外地或替代地,所述第一读取FIFO电路可操作地连接到所述第一通路导体而没有可操作地连接到所述第二通路导体,且其中所述第二读取FIFO电路可操作地连接到所述第二通路导体而没有可操作地连接到所述第一通路导体。

额外地或替代地,所述第一及第二通路导体彼此邻近布置。

额外地或替代地,所述第一及第二存储器芯片中的每一者被划分为包含所述第一通道及第二到第四通道的四个通道。

额外地或替代地,所述多个存储器芯片进一步包含第三及第四存储器芯片,且所述第三及第四存储器芯片中的每一者被划分为包含第五到第八通道的四个通道。

额外地或替代地,所述多个存储器芯片进一步包含第五到第八存储器芯片,所述第五及第六存储器芯片中的每一者被划分为包含所述第一到第四通道的四个通道,且所述第七及第八存储器芯片中的每一者被划分为包含所述第五到第八通道的四个通道。

额外地或替代地,所述第一通路导体共同连接到所述第一及第五存储器芯片中的所述第一通道,且所述第二通路导体共同连接到所述第二及第六存储器芯片中的所述第一通道。

额外地或替代地,所述第一及第二存储器芯片中的所述第一通道以及所述第五及第六存储器芯片中的所述第一通道中的一者被排他性地激活。

在本公开的另一方面中,一种设备包含第一存储器芯片,其输出第一n位数据;第二存储器芯片,其堆叠在所述第一存储器芯片上,所述第二存储器芯片输出第二n位数据;及第一及第二n位通路导体,其穿透至少所述第一存储器芯片。响应于读取命令,同时将所述第一及第二n位数据分别输出到所述第一及第二n位通路导体,借此并行输出2n位数据。

额外地或替代地,所述第一n位通路导体可操作地连接到所述第一存储器芯片而没有可操作地连接到所述第二存储器芯片,且所述第二n位通路导体可操作地连接到所述第二存储器芯片而没有可操作地连接到所述第一存储器芯片。

额外地或替代地,所述第一及第二n位通路导体进一步穿透所述第二存储器芯片。

额外地或替代地,进一步包含的是穿透至少所述第一存储器芯片的第三及第四n位通路导体。所述第一及第二存储器芯片分别进一步输出第三及第四n位数据。响应于另一读取命令,同时将所述第三及第四n位数据分别输出到所述第三及第四n位通路导体,借此与所述2n位数据异步地并行输出另一2n位数据。

在本公开的另一方面中,一种设备包含第一存储器芯片;第二存储器芯片,其堆叠在所述第一芯片上;及第一及第二通路导体,其穿透至少所述第一存储器芯片。所述第一及第二存储器芯片中的每一者被划分为包含第一通道的多个通道。所述第一存储器芯片中的所述第一通道包含共同指派到所述第一及第二通路导体的第一读取FIFO电路。所述第二存储器芯片中的所述第一通道包含共同指派到所述第一及第二通路导体的第二读取FIFO电路。所述第一读取FIFO电路可操作地连接到所述第一通路导体而没有可操作地连接到所述第二通路导体。所述第二读取FIFO电路可操作地连接到所述第二通路导体而没有可操作地连接到所述第一通路导体。

额外地或替代地,所述第一及第二通路导体彼此邻近布置。

额外地或替代地,所述第一及第二存储器芯片中的所述第一通道被同时激活,使得数据被并行地经由导体输出到所述第一及第二通路导体。

附图说明

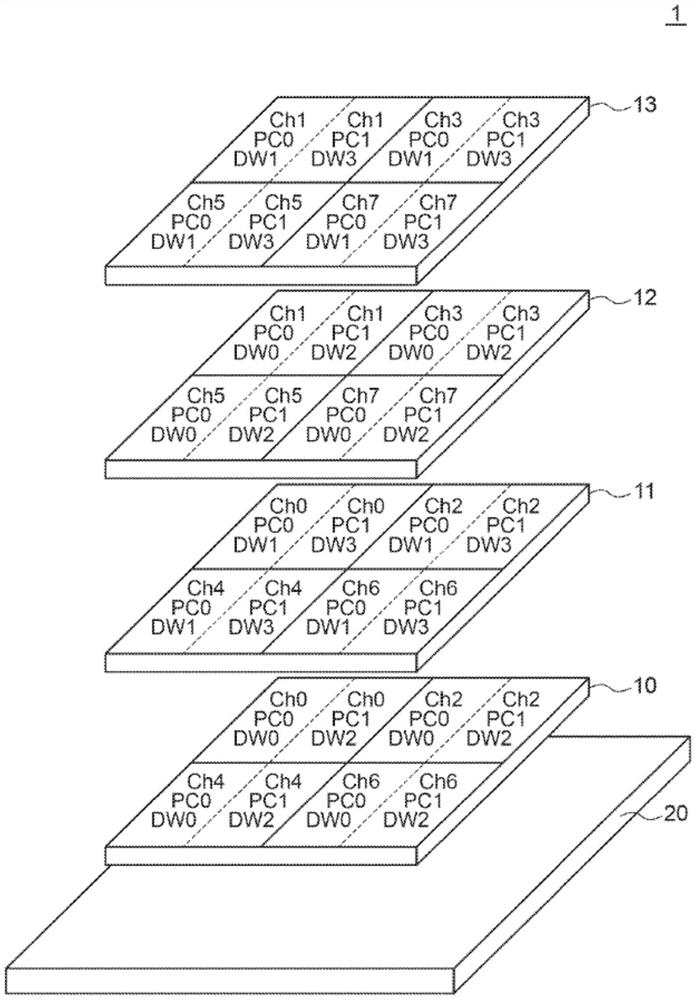

图1是展示根据本公开的半导体装置的实例的示意分解透视图。

图2是用于解释包含在根据本公开的半导体装置中的存取路径的实例的示意性分解透视图。

图3A及3B是展示存储器芯片的平面图的平面视图。

图4展示使用八个存储体进行无缝读取存取的方式的示意图。

图5是展示布置在通路形成区中的通路导体的布局的图。

图6是展示布置在通路形成区的一个区域中的通路导体的布局的表。

图7是展示通路导体与存储器单元阵列之间连接关系的实例的电路图。

图8是展示布置在通路形成区中的通路导体的另一布局的图。

图9A及9B是分别展示布置在预定区域中的通路导体的布局的表。

图10是展示通路导体与存储器单元阵列之间连接关系的另一个实例的电路图。

图11是展示根据本公开的半导体装置的另一实例的示意性分解透视图。

具体实施方式

下面将参考附图详细解释本发明的各种实施例。下文详细描述参考附图,所述附图通过说明的方式展示其中可实践本发明的特定方面及实施例。对这些实施例进行足够详细的描述以使所属领域的技术人员能够实践本发明。可利用其它实施例,且可在不背离本发明的范围的情况下进行结构、逻辑及电改变。各种实施例不一定互斥,因为一些所公开实施例可与一或多个其它所公开实施例组合以形成新实施例。

图1中所展示的半导体装置1具有控制芯片20及堆叠在控制芯片20上的四个存储器芯片10到13。存储器芯片10到13例如是DRAM(动态随机存取存储器)。存储器芯片10到13中的每一者被划分为四个通道,并且通道可彼此独立地操作。因此,将例如数据输入/输出端子、地址端子、命令端子及时钟端子的端子指派到通道中的每一者。存储器芯片10及11被划分为通道Ch0、Ch2、Ch4及Ch6,且存储器芯片12及13被划分为通道Ch1、Ch3、Ch5及Ch7。因此,半导体装置1具有包含总共八个通道的配置。分别指派到通道Ch0到Ch7的例如数据输入/输出端子、地址端子、命令端子及时钟端子的端子通过经提供以穿透存储器芯片10到13的通路导体连接到控制芯片20。

如在图1中所展示,包含在存储器芯片10及11中的通道Ch0及包含在存储器芯片12及13中的通道Ch1在平面视图中位于相同位置,包含在存储器芯片10及11中的通道Ch2及包含在存储器芯片12及13中的通道Ch3在平面视图中位于相同位置,包含在存储器芯片10及11中的通道Ch4及包含在存储器芯片12及13中的通道Ch5在平面视图中位于相同位置,并且包含在存储器芯片10及11中的通道Ch6及包含在存储器芯片12及13中的通道Ch7在平面视图中位于相同位置。通道Ch0到Ch7中的每一者被划分为伪通道PC0及PC1。当将存取通道Ch0到Ch7中的一者时,通过指定伪通道PC0或PC1来执行存取。同一通道中的两个伪通道PC0及PC1不能被同时存取。同时,可异步地及非排他性地存取不同通道Ch0到Ch7。

在本实施例中,每通道的I/O位的数目是144位,其中128位是实际数据,且16位是ECC(错误校正代码)数据。128位实际数据的一半,即64位被指派到伪通道中的一者,即伪通道PC0,且其余64位被指派到另一个伪通道PC1。八位ECC数据被指派到伪通道PC0及PC1中的每一者。指派到伪通道PC0的64位数据由包含32位的群组DW0(DWord0)及包含32位的群组DW1(DWord1)构成。类似地,指派到伪通道PC1的64位数据由包含32位的群组DW2及包含32位的群组DW3构成。四位ECC数据指派到群组中的每一者。

构成同一通道中的同一伪通道的两个群组被分别指派到不同存储器芯片。举例来说,在通道Ch0的伪通道PC0中,群组DW0被指派到存储器芯片10,且群组DW1被指派到存储器芯片11。因此,举例来说,当对通道Ch0的伪通道PC0发出读取请求时,分别从存储器芯片10及11并行输出32位数据。如在图2中所展示,指派到通道Ch0中的伪通道PC0的群组DW0的通路导体31及指派到通道Ch0中的伪通道PC0的群组DW1的通路导体32被独立地提供。也就是说,控制芯片20及存储器芯片10到13以一对一的关系连接,并且一个通路导体没有指派到多个存储器芯片。因此,即使当存储器芯片10到13当中的操作速度由于工艺变化而存在差异时,数据也不会在通路导体中发生冲突。此外,用一个存取激活的存储器单元阵列被分配到两个存储器芯片,且因此也可抑制由于电流消耗的集中而引起的电力电势的改变。

图3A是展示存储器芯片10及12的平面图的平面视图,且图3B是展示存储器芯片11及13的平面图的平面视图。如在图3A及3B中所展示,每一通道中的伪通道中的每一者被划分为包含存储体B0到B15的16个存储体。存储器芯片上的存储体B0到B15的位置在存储器芯片10及12与存储器芯片11及13之间不同。存储器芯片10及12上的存储体B0到B15的位置与存储器芯片11及13上的存储体B0到B15的位置相差180度。因此,构成同一通道中的相同伪通道的存储体B0到B15的平面位置在两个存储器芯片之间不同。举例来说,包含在通道Ch0的伪通道PC0中的存储体B0的平面位置在存储器芯片10与存储器芯片11之间不同。

图4是展示并行执行对通道Ch0中的伪通道PC0的存取及对通道Ch4中的伪通道PC0的存取的实例的图。在图4中所展示的实例中,在通道Ch0及Ch4中的每一者中执行使用八个存储体的无缝读取存取。在本实施例中,即使在执行此无缝读存取的情况下,也可分配经存取存储体的位置,且因此,由于电流消耗的集中而导致的电力电势的改变可被抑制。

在图3A及3B所展示的通路形成区30中,布置穿透存储器芯片的多个通路导体。如在图5中展示布置在通路形成区30中的通路导体的布局。图5中所展示的信号SID0到SID3是分别对应于存储器芯片10到13的片ID。举例来说,对应于存储器芯片10的通道Ch0中的伪通道PC0的群组DW0的通路导体布置在区域31中。类似地,对应于存储器芯片11的通道Ch0中的伪通道PC0的群组DW1的通路导体布置在区域32中。包含在图5中所展示的区域31及32中的通路导体分别对应于图2中所展示的通路导体31及32。

当对通道Ch0中的伪通道PC0执行读取存取时,从存储器芯片10读取的32位读取数据通过布置在区域31中的通路导体供应到控制芯片20,并且从存储器芯片11读取的32位读取数据通过布置在区域32中的通路导体供应到控制芯片20。大体上同时传送从存储器芯片10读取的32位读取数据及从存储器芯片11读取的32位读取数据。当对通道Ch0中的伪通道PC0执行写入存取时,待写入存储器芯片10的32位写入数据通过布置在区域31中的通路导体从控制芯片20供应到存储器芯片10,并且待写入存储器芯片11中的32位写入数据通过布置在区域32中的通路导体从控制芯片20供应到存储器芯片11。大体上同时传送待写入存储器芯片10的32位写入数据及待写入存储器芯片11的32位写入数据。用于将地址信号供应到存储器芯片10到13的多个通路导体布置在区域33中。

图6是布置在区域31中的通路导体的布局的表。如在图6中所展示,布置在区域31中的通路导体包含分别对应于数据DQ0R到DQ31R的32个通路导体及分别对应于数据DQ0F到DQ31F的32个通路导体。数据DQ0R到DQ31R是与时钟信号的上升边缘同步地同时输入/输出的32位的数据,并且数据DQ0F到DQ31F是与时钟信号的下降边缘同步地同时输入/输出的32位的数据。例如对应于数据掩码信号DM0R到DM3R及DM0F到DM3F的通路导体以及对应于读取时钟信号及写入时钟信号的通路导体的其它通路导体也包含在区域31中。在图6中所展示的实例中,成对数据(例如,数据DQ0R及数据DQ0F)彼此邻近布置。

图7是展示通路导体与存储器单元阵列之间连接关系的实例的电路图。在图7中所展示的实例中,包含内部缓冲器43、读取FIFO电路44、并-串转换电路45及输出缓冲器46的读取路径,以及包含输入接收器47、串-并转换电路48及内部缓冲器49的写入路径并行连接在通路导体41与对应于数据DQ0R的存储器单元阵列42之间。类似地,包含内部缓冲器53、读取FIFO电路54、并-串转换电路55及输出缓冲器56的读取路径,以及包含输入接收器57、串-并转换电路58及内部缓冲器59的写入路径并行连接在通路导体51与对应于数据DQ0F的存储器单元阵列52之间。以此方式,在图7中所展示的实例中,读取路径及写入路径被个别地指派到通路导体中的每一者。

图8展示布置在通路形成区30中的通路导体的另一布局。在图8中所展示的实例中,不针对存储器芯片中的每一者集体布置对应于同一通道中的相同伪通道的多个通路导体,即,对于群组DW及对应于两个群组DW的多个通路导体中的每一者,混合在一个区域中。举例来说,对应于通道Ch0中的伪通道PC0的群组DW0及群组DW1的通路导体以混合方式布置在区域34及35中。

图9A及9B分别展示布置在区域34及35中的通路导体的布局。如在图9A及9B中所展示,虽然布置在区域34及35中的通路导体的布局与布置在图6中所展示的区域31中的通路导体的布局相同,但是在行方向上邻近的通路导体被指派到不同存储器芯片。也就是说,布置在列A、C、E及G中的通路导体被指派到存储器芯片10(SID0/DW0),且布置在列B、D、F及H中的通路导体被指派到区域34中的存储器芯片11(SID1/DW1)。同时,布置在列A、C、E及G中的通路导体被指派到存储器芯片11(SID1/DW1),且布置在列B、D、F及H中的通路导体被指派到区域35中的存储器芯片10(SID0/DW0)。

图10是展示通路导体与存储器单元阵列之间的连接关系的另一实例的电路图,并展示适用于其中通路导体的布局是图8、9A及9B中所展示的布局的情况的实例。在图10中所展示的实例中,输出缓冲器62、输入接收器63、并-串转换电路64及串-并转换电路65被指派到对应于数据DQ0R的通路导体61,且输出缓冲器72、输入接收器73、并-串转换电路74及串并转换电路75被指派到对应于数据DQ0F的通路导体71。存储器单元阵列81经由内部缓冲器82及读取FIFO电路83共同指派到并-串转换电路64及74,并且经由内部缓冲器84共同指派到串-并转换电路65及75。然而,路径中的一者被去激活并且没有可操作地连接到存储器单元阵列81。举例来说,当对应于通路导体61的输出缓冲器62、输入接收器63、并-串转换电路64及串-并转换电路65被激活时,对应于通路导体71的输出缓冲器72、输入接收器73、并-串转换电路74及串-并转换电路75被去激活。因此,通路导体71及存储器单元阵列81没有可操作地彼此连接。在此情况下,通路导体61及存储器单元阵列81可操作地彼此连接。

以此方式,当以图8、9A及9B中所展示的布局布置通路导体时,邻近通路导体被指派到不同存储器芯片,且因此内部缓冲器82及84以及读取FIFO电路83可被共同指派到两个通路导体。这使得内部缓冲器82及84以及读取FIFO电路83的数目减半,且因此可减小芯片面积。

在图11中所展示的半导体装置2具有控制芯片20,及堆叠在控制芯片20上的八个存储器芯片10到17。也就是说,半导体装置2具有其中将四个存储器芯片14到17添加到图1中所展示的半导体装置1的配置。存储器芯片14到17分别具有与存储器芯片10到13的地址配置相同的地址配置,而芯片地址(SID)除外。举例来说,可使用芯片地址的最低有效位来执行存储器芯片10到13及存储器芯片14到17的选择。

因此,举例来说,当向通道Ch4中的伪通道PC0发出读取请求并且当芯片地址的最低有效位为0(零)时,选择存储器芯片10及11,使得32位读取数据通过指派到通道Ch4中的伪通道PC0的群组DW0的通路导体91从存储器芯片10输出,并且32位读取数据通过指派到通道Ch4中的伪通道PC0的群组DW1的通路导体92从存储器芯片11输出。在此情况下,不存取包含在存储器芯片14及15中的通道Ch4的伪通道PC0。另一方面,当向通道Ch4中的伪通道PC0发出读取请求并且芯片地址的最低有效位为1时,选择存储器芯片14及15,使得32位读取数据通过通路导体91从存储器芯片14输出,并且32位读取数据通过通路导体92从存储器芯片15输出。在此情况下,不存取包含在存储器芯片10及11中的通道Ch4的伪通道PC0。如上文描述,与图1中所展示的半导体装置1相比,图11所展示的半导体装置2中的存储器芯片的数目增加一倍,且因此控制芯片20与存储器芯片10到17之间的连接具有一对二的关系。

存储器芯片的数目没有具体限制。举例来说,也可能在控制芯片上堆叠十二个存储器芯片。在此情况下,控制芯片与存储器芯片之间的连接具有一对三的关系。此外,存储器芯片的数目也可能是两个。

尽管已在某些优选实施例及实例的上下文中公开本发明,但所属领域的技术人员将理解,本发明延伸超出特定公开的实施例到本发明的其它替代实施例及/或用途以及其明显修改及等效物。另外,基于此公开内容,本发明范围内的其它修改对于所属领域的技术人员将是显而易见的。还预期,可对实施例的特定特征及方面进行各种组合或子组合,并且仍落入本发明的范围内。应理解,所公开实施例的各种特征及方面可彼此组合或替代以便形成所公开发明的变化模式。因此,希望本文所公开的本发明的至少一些的范围不应受上文描述的特定公开实施例的限制。

- 具有多通道的高带宽存储器

- 具有高带宽、强抗干扰的多通道数据传输系统及传输方法