制造用于外延生长基于镓的III-N合金层的衬底的方法

文献发布时间:2024-01-17 01:15:20

技术领域

本发明涉及制造用于外延生长基于镓的III-N合金层(即,氮化镓(GaN)层、氮化铝镓(AlGaN)层或氮化铟镓(InGaN)层)的衬底的方法,涉及制造这种III-N合金层的方法以及涉及用于在这种III-N合金层中制造高电子迁移率晶体管(HEMT)的方法。

背景技术

III-N半导体(特别是氮化镓(GaN)、氮化铝镓(AlGaN)或氮化铟镓(InGaN))似乎是特别有前景的,特别是关于形成高功率发光二极管(LED)和在高频下工作的电子器件,诸如,高电子迁移率晶体管(HEMT)或其它场效应晶体管(FET)。

就这些III-N合金难以以大尺寸的块状衬底的形式找到而言,它们通常通过异质外延(heteroepitaxy),即,通过在由不同材料制成的衬底上外延来形成。

这种衬底的选择特别是考虑了衬底材料与III-N合金之间晶格参数的差异和热膨胀系数的差异。具体地,这些差异越大,在III-N合金层中形成晶体缺陷(诸如,位错)的风险就越大,并且产生易于引起过度应变的高机械应力的风险就越大。

最常考虑用于III-N合金的异质外延的材料是蓝宝石和碳化硅(SiC)。

除了其晶格参数与氮化镓的较小差异之外,碳化硅对于高功率电子应用是特别优选的,因为其热导率明显高于蓝宝石的热导率,并且因此允许在部件操作期间产生的热能更容易地耗散。

在射频(RF)应用中,寻求使用半绝缘碳化硅,即,电阻率通常高于或等于10

硅将使得制造成本显著降低,并且可以取得大尺寸的衬底,但是硅上III-N合金类型的结构受到超过20GHz的RF传播损耗和不良散热的不利影响。

复合结构(诸如,SopSiC或SiCopSiC结构)也已经被研究[1],但尚未证明是完全令人满意的。这些结构分别包括在多晶SiC衬底上的单晶硅层或单晶SiC层(旨在形成用于氮化镓的外延生长的晶种层)。尽管多晶SiC是廉价的材料,其可以以大尺寸的衬底的形式获得并且良好地散热,但是这些复合结构由于在单晶硅或SiC层与多晶SiC衬底之间的交界面处存在氧化硅层而受到不利影响,该氧化硅层形成阻碍热从III-N合金层向多晶SiC衬底耗散的热障。

发明内容

因此,本发明的一个目的是补救上述缺点以及特别是与半绝缘SiC衬底的尺寸和成本相关的限制。

因此,本发明的目的是提供一种制造用于外延生长基于镓的III-N合金的衬底的方法,特别是以形成RF损耗被最小化并且散热被最大化的HEMT或其它高频、高功率电子器件。

为此,本发明提供了一种制造用于外延生长氮化镓(GaN)、氮化铝镓(AlGaN)或氮化铟镓(InGaN)层的衬底的方法,所述方法包括以下连续步骤:

-提供单晶碳化硅供体衬底,

-将离子物质植入到所述供体衬底中,以形成限定待转移的单晶SiC薄层的弱化区域,

-经由接合层将所述供体衬底接合到第一受体衬底,

-沿着所述弱化区域分离所述供体衬底,以将SiC薄层转移到所述第一受体衬底,

-在所述SiC薄层上执行厚度大于1μm的半绝缘SiC层(30)的外延生长,

-将所述半绝缘SiC层接合到第二受体衬底,所述第二受体衬底具有高电阻率,

-去除所述接合层的至少一部分,以分离所述第一受体衬底,

-去除被转移的单晶SiC薄层,以露出所述半绝缘SiC层。

“高频”在本文中是指高于3kHz的频率。

“高功率”在本文中是指通过晶体管的栅极植入的高于0.5W/mm的功率。

“高电阻率”在本文中是指高于或等于100Ω.cm的电阻率。

“半绝缘碳化硅”在本文中是指电阻率高于或等于10

该方法允许包括半绝缘SiC层的衬底(基于硅或可以大尺寸获得的低成本高电阻材料),该半绝缘SiC层的晶体质量在散热和RF损耗限制方面适于要形成的III-N合金层的随后外延生长并且使最终结构受益于其良好性能。由于半绝缘SiC层与硅衬底(或高电阻率的另一材料的衬底)直接接触,因此该结构还不包含热障。

因为硅与碳化硅之间的晶格参数的差异,包括通过直接在高电阻率的硅衬底上外延形成半绝缘SiC层的方法将导致在半绝缘SiC中形成大量位错。相比之下,根据本发明的方法使得可以使用单晶SiC层作为用于半绝缘SiC生长的晶种,该单晶SiC层的质量是最佳的,因为该单晶SiC层通过从供体衬底的转移而获得。

此外,扮演临时载体角色的第一受体衬底的使用允许SiC的硅面在方法的各个步骤中最佳地定向。

根据该方法的有利但可选的特征,其可以单独实施或以其任何技术上可能的组合实施:

-所述第一受体衬底和所述供体衬底的热膨胀系数之差小于或等于3×10

-所述第一受体衬底是晶体质量低于所述供体衬底的晶体质量的SiC衬底;

-转移到所述第一受体衬底的单晶SiC薄层具有小于1μm的厚度;

-所述接合层由在所述半绝缘SiC层的外延生长期间保持热稳定并且能够从被转移的SiC层与所述第一受体衬底之间的交界面去除的材料形成;

-所述接合层是氮化硅层或氮化镓层;

-去除所述接合层的至少一部分包括化学蚀刻、通过激光剥离和/或施加机械应力;

-所述半绝缘SiC层通过在SiC的外延生长期间掺杂钒来形成;

-所述半绝缘SiC层通过同时沉积硅、碳和钒形成;

-所述第二受体衬底是电阻率高于或等于100Ω.cm的硅衬底;

-外延的半绝缘SiC层具有介于在1μm至5μm之间的厚度;

-所述第二受体衬底是具有高于或等于100Ω.cm的电阻率的多晶SiC衬底或多晶AlN衬底;

-外延的半绝缘SiC层的厚度小于或等于80μm;

-所述方法还包括回收从被转移的层分离的供体衬底的部分的步骤,以形成新的供体衬底;

-离子物质通过所述供体衬底的硅面被植入,并且所述供体衬底的硅面被接合到所述第一受体衬底,使得在已经去除被转移的单晶SiC薄层之后,露出所述半绝缘SiC层的硅面。

本发明的另一个主题涉及一种在使用已经描述的方法获得的衬底上制造基于镓的III-N合金层的方法。

所述方法包括以下步骤:

-提供使用如上所述的方法制造的衬底,

-在所述衬底的半绝缘SiC层上执行氮化镓层的外延生长。

在某些实施方式中,氮化镓层具有介于1μm至2μm之间的厚度。

本发明的另一个主题涉及在这种III-N合金层中制造高电子迁移率晶体管(HEMT)的方法。

所述方法包括以下步骤:

-使用如上所述的方法通过外延制造氮化镓层、氮化铝镓层或氮化铟镓层,

-通过在所述层上外延不同于所述层的材料的III-N材料层来形成异质结,

-形成与所述异质结齐平的晶体管的沟道,

-在所述沟道上形成所述晶体管的源极、漏极和栅极。

附图说明

本发明的进一步的特征和优点将从以下参考附图的详细描述中变得明显,其中:

图1是单晶SiC供体衬底的示意性截面图;

图2是图1的供体衬底的示意性截面图,在该衬底中,通过植入离子物质形成弱化区域,以限定待转移的薄层;

图3是覆盖有可去除接合层的临时载体的示意性截面图;

图4是图3的临时载体经由可去除接合层接合到图2的供体衬底的示意性截面图;

图5是沿着弱化区域分离供体衬底以将单晶SiC薄层转移到临时载体的示意性截面图;

图6是转移到临时载体的单晶SiC薄层在其自由表面已经被抛光之后的示意性截面图;

图7是在被转移的单晶SiC薄层上通过外延形成半绝缘SiC层的示意性截面图;

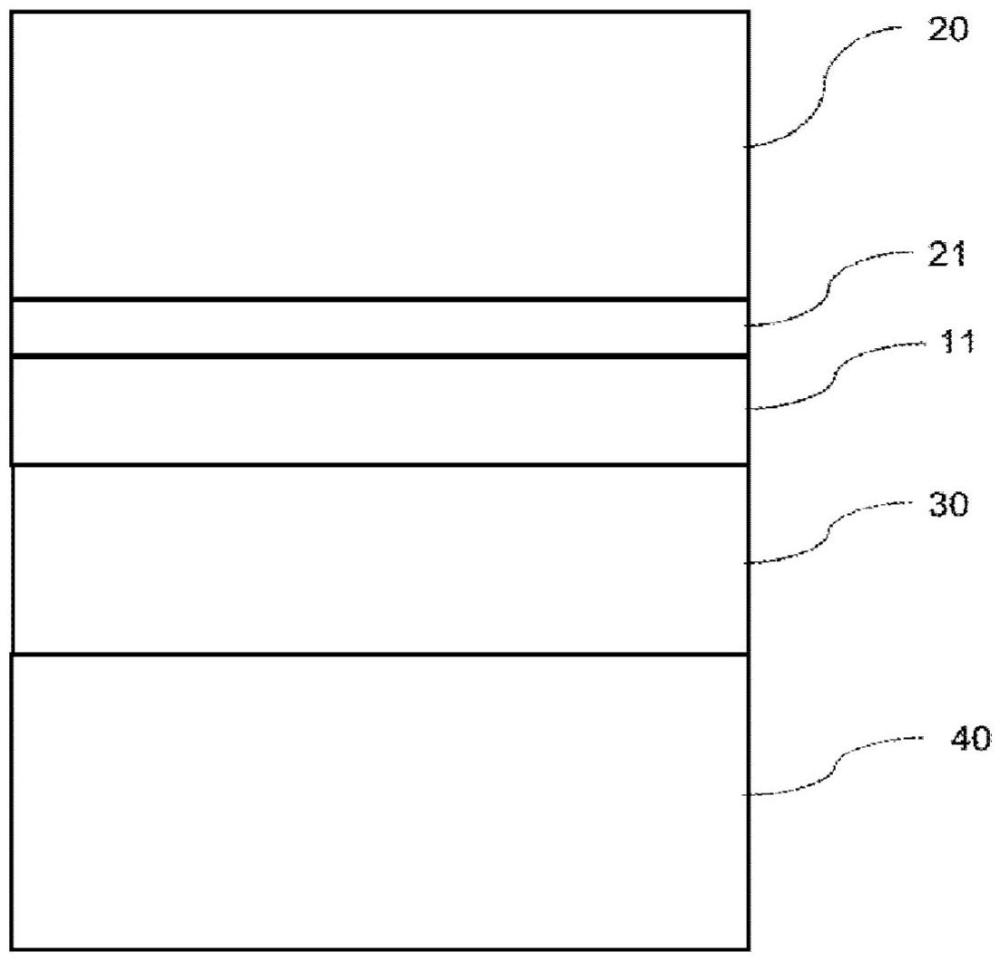

图8是图7的结构经由外延的半绝缘SiC层接合到受体衬底的示意性截面图;

图9是从图8的结构去除临时载体的示意性截面图;

图10是在已经去除单晶SiC薄层之后的受体衬底和外延的半绝缘SiC层的示意性截面图;

图11是在半绝缘SiC层上通过外延形成的GaN层的示意性截面图;

图12是通过在GaN层上外延不同于GaN的III-N合金层而形成的异质结的示意性截面图。

为了附图的易读性,各种层不必按比例示出。

具体实施方式

本发明提供了一种制造用于基于镓的二元或三元III-N合金的外延生长的衬底的方法。所述合金包括氮化镓(GaN)、氮化铝镓(Al

该方法使用掺杂半导体单晶碳化硅(SiC)的供体衬底,被转移到第一受体衬底的所述掺杂半导体单晶碳化硅(SiC)的薄层将作为生长半绝缘SiC层的晶种。在文本的其余部分中,将考虑经由Smart Cut

为此,将选择具有优异晶体质量的单晶SiC衬底(即,特别是无位错的衬底)。

在某些实施方式中,供体衬底可以是单晶SiC块状衬底。在其它实施方式中,供体衬底可以是复合衬底,其包括单晶SiC的表面层和另一材料的至少一个其它层。在这种情况下,单晶SiC层将具有大于或等于0.5μm的厚度。

碳化硅有各种晶型(也称为多型)。最常见的是4H、6H和3C型。优选地,单晶碳化硅选自4H和6H多型,但是可以使用任何多型来实现本发明。

在附图中,已经示出了单晶SiC的块状衬底10。

如本身已知的,如图1所示,这种衬底具有硅面10-Si和碳面10-C。

目前,GaN的外延工艺主要在SiC的硅面上实施。然而,在SiC的碳面上生长GaN并非不可能。在该方法的实施过程中,供体衬底的取向(硅面/碳面)根据用于生长GaN层的SiC的面来选择。

参考图2,将离子物质植入到供体衬底10中,以形成限定单晶SiC薄层11的弱化区域12。植入的物质通常包括氢和/或氦。本领域技术人员将能够定义所需的植入剂量和能量。

当供体衬底是复合衬底时,植入被执行为到所述衬底的单晶SiC的表面层中。

优选地,通过供体衬底的硅面10-Si植入离子物质。如将在下面看到的,供体衬底的这种取向使得可以在用于生长GaN层的最终衬底的表面处放置SiC的硅面,这是更有利的。然而,如果设想在SiC的碳面上生长GaN层,则必须通过供体衬底的碳面10-C植入离子物质。

优选地,单晶碳化硅薄层11具有小于1μm的厚度。具体地,这样的厚度在工业规模上可用Smart Cut

参考图3,还提供了第一受体衬底20。

所述第一受体衬底的主要功能是在单晶SiC层11从供体衬底的转移和在单晶SiC层上生长半绝缘SiC层之间暂时保持单晶SiC层11。

为此,第一受体衬底被选择为具有基本上等于碳化硅的热膨胀系数的热膨胀系数,以在半绝缘SiC的外延期间不产生应力或应变。因此,特别有利的是,第一受体衬底和供体衬底(或在复合供体衬底的情况下为单晶SiC层)的热膨胀系数之差小于或等于3×10

优选地,第一受体衬底也由SiC制成,以最小化热膨胀系数的差异。特别有利地,第一受体衬底20是晶体质量低于供体衬底的晶体质量的SiC衬底。这意味着第一受体衬底可以是多晶SiC衬底,或者实际上是单晶SiC的衬底但是其可以包括所有类型的位错(与为了确保GaN的外延层的质量而针对优异的晶体质量选择的供体衬底的单晶SiC相反)。这种较低晶体质量的衬底具有比与供体衬底相同质量的衬底更便宜的优点,同时完全适合于临时载体的功能。

参考图4,包括单晶SiC薄层11的供体衬底10接合到第一受体衬底20。

为了确保供体衬底与第一供体衬底的良好接合,在所述衬底之间的交界面处形成接合层21。

在图3中,接合层21被形成在第一受体衬底20上,但是在未示出的其它实施方式中,接合层可以被形成在供体衬底上(在薄层11的那一侧上),或者实际上部分在供体衬底上并且部分在第一受体衬底上。

接合层由在薄层11上的半绝缘SiC的后续外延生长期间保持热稳定的材料形成。

作为指示,由于4H-或6H-SiC的外延是在通常高于1500℃的温度下执行的,所选择的接合层的材料在此温度下不会劣化或降解。

此外,接合层的材料能够例如通过选择性蚀刻从被转移的单晶SiC层与第一受体衬底20之间的交界面去除,该选择性蚀刻可选地由等离子体辅助。

根据一个优选实施方式,接合层是氮化硅层或氮化镓层。所述层的厚度通常介于10nm至几百纳米之间。

参考图5,供体衬底沿着弱化区域12分离。以本身已知的方式,分离可以由热处理、机械作用或这些手段的组合引起。

该分离的效果是将单晶SiC薄层11转移到第一受体衬底20。供体衬底的剩余部分10’可选地被回收以用于另一用途。

如图6所示,被转移的单晶SiC层11的自由面是碳面11-C(硅面11-Si在接合界面那一侧)。例如通过化学机械抛光(CMP)对该面进行抛光,以去除与离子物质的植入相关的缺陷并降低层11的粗糙度。

参考图7,在单晶SiC薄层11上执行半绝缘SiC层30的外延生长。半绝缘SiC的多型有利地与供体衬底的SiC的多型相同。

该外延生长在通常高于1500℃的非常高的温度下执行,但是如上所述,接合层21在该温度下是稳定的。此外,由于第一受体衬底的材料与SiC之间的热膨胀系数之差较小,因此堆叠中产生的机械应力被最小化。

存在用于形成半绝缘SiC的各种技术。根据一个实施方式,SiC层在其外延生长期间掺杂有钒。根据另一个实施方式,在外延反应器中使用合适的前体同时沉积硅、碳和钒。

半绝缘SiC层有利地具有大于1μm的厚度,从而以显著的方式有助于最终结构内的散热。该厚度大于使用工业可用设备以Smart Cut

因此,包括转移厚度小于1μm的单晶SiC层、然后通过在所述被转移的层上外延形成单晶SiC的单晶层的方法允许规避工业上可获得的用于执行Smart Cut

参照图8,提供具有高电阻率的第二受体衬底40,并将其结合到半绝缘SiC层30。例如,第二受体衬底可以是电阻率高于或等于100Ω.cm的硅衬底,也具有高于或等于100Ω.cm的电阻率的多晶SiC衬底或多晶AlN衬底。

半绝缘SiC层30的厚度将可能根据第二受体衬底的材料来选择。因此,当第二受体衬底是高电阻率的硅衬底时,半绝缘SiC层30将有利地具有介于1μm至5μm之间的厚度。当第二受体衬底由多晶AlN或多晶SiC制成时,半绝缘SiC层30具有大得多的厚度(可能高达80μm,例如,约50至80μm)以改善最终结构内的热耗将可能是有利的。

接着,去除接合层21中的至少一些,以从结构的其余部分上分离第一受体衬底。在该去除期间,层21必须被充分地破坏以允许从结构上分离。可以采用任何合适的手段。例如,但非限制性地,可以通过化学蚀刻、通过激光剥离和/或施加机械应力来去除接合层。

如图9所示,因此在该分离结束时保留了由第二受体衬底40、半绝缘SiC层30和被转移的单晶SiC薄层11连续组成的结构。通过抛光和/或蚀刻去除接合层21的任何残留物。

参照图10,去除薄层11以露出半绝缘SiC层30。薄层11可以通过任何合适的手段去除,例如,化学或机械蚀刻。

露出的面是半绝缘SiC的硅面,这有利于GaN的外延生长。因此形成了适合于III-N合金外延生长的衬底。

参照图11,在半绝缘SiC层30的自由面上生长GaN层50(或者,如上所述,AlGaN或InGaN)。层50的厚度通常介于1μm至2μm之间。

接着,如图12所示,通过在层50上外延生长与层50不同的III-N合金层60来形成异质结。

因此,可以使用本领域技术人员已知的方法,从该异质结继续制造晶体管,特别是HEMT,晶体管的沟道被形成为与异质结齐平,并且晶体管的源极、漏极和栅极被形成在沟道上。

这样获得的结构是特别有利的,因为它包括相对厚的半绝缘SiC层,该半绝缘SiC层一方面用作III-N合金层的外延生长的晶种,另一方面既良好地散热又限制RF损耗。此外,承载半绝缘SiC层的第二受体衬底与所述层直接接触,使得该结构不包括任何热障。

因此,在这种结构上外延形成的II-N合金层中形成的HEMT或另一种高频、高功率电子器件具有最小化的RF损耗和最大化的散热。

参考文献

[1]Comparative study on stress in AlGaN/GaN HEMT structures grown on6H-SiC,Si and on composite substrates of the 6H-SiC/poly-SiC and Si/poly-SiC,M.Guziewicz et al,Journal of Physics:Conference Series 100(2008)040235。

- 具有(20-2-1)面的半极性氮化镓的外延层及其制造方法

- 适用于AlN衬底的LED外延生长方法

- 生产用于外延生长基于镓的III-N合金层的衬底的方法

- 氮化镓晶体生长方法、氮化镓晶体衬底、外延晶片制造方法和外延晶片