信号同步方法、装置、存储介质和视频处理设备

文献发布时间:2024-01-17 01:17:49

技术领域

本发明涉及视频技术领域,具体而言,涉及一种信号同步方法、装置、存储介质和视频处理设备。

背景技术

目前,大屏控制器主要是集中式设备,该集中式设备内部多接口间通过互联输入输出(IO)来传递参考场同步信号(VSYNC,简称为VS),不同的接口通过参考VS进行信号同步,但这必须在一个机箱内才可以实现信号同步。

而分布式系统因为不同的节点设备间只有网线一种介质,所以想要做到同步,只能通过网口来进行设计,比如,分布式系统的多个节点设备间需要单独连接同步锁相(Genlock)线才能进行信号同步。但是,该方法并未对系统时间进行校准,并且布线繁琐,不利于远距离传输,从而存在信号同步的效率低的技术问题。

针对上述的信号同步的效率低的技术问题,目前尚未提出有效的解决方案。

发明内容

本发明实施例提供了一种信号同步方法、装置、存储介质和视频处理设备,以至少解决信号同步的效率低的技术问题。

根据本发明实施例的一个方面,提供了一种信号同步方法。该方法包括:获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号;获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据;基于偏移数据调整时钟芯片的输出频率。由于本申请的系统时间时校准后的系统时间,基于校准后的系统时间生成可以作为视频信号的同步参考源的参考场同步信号,通过参考场同步信号与视频信号的输出场同步信号之间的偏移数据,来调整时钟芯片的输出频率,避免了繁琐地布线过程,从而在控制成本的前提下,做到了真正的去中心化分布式,达到了提高信号同步的效率的技术效果。

可选地,获取校准后的系统时间,包括:根据第一节点设备中第一目标芯片的硬件时间戳,得到校准后的系统时间。

可选地,根据第一节点设备中第一目标芯片的硬件时间戳,得到校准后的系统时间,包括:根据硬件时间戳,对第一节点设备的系统时间进行校准,得到校准后的系统时间,其中,校准后的系统时间与硬件时间戳相同。由于本申请将主节点设备的系统时间与自己的第一目标芯片的硬件时间戳进行对齐,这样可以保证系统运行的过程中,时间偏差是控制在一定的误差内,从而实现了对主节点设备的系统时间进行有效校准。

可选地,根据第一节点设备中第一目标芯片的硬件时间戳,得到校准后的系统时间,包括:根据第一节点设备中第一目标芯片的硬件时间戳,对第二节点设备的第二目标芯片的硬件时间戳进行校准,得到校准后的第二目标芯片的硬件时间戳;根据校准后的第二目标芯片的硬件时间戳,对第二节点设备的系统时间进行校准,得到校准后的系统时间。由于本申请通过主节点设备的第一目标芯片的硬件时间戳对从节点设备的系统时间进行校准,使得从节点设备的系统时间对齐至第一目标芯片的硬件时间戳,这样可以保证系统运行的过程中,时间偏差是控制在一定的误差内,从而实现了对从节点设备的系统时间进行有效校准。

可选地,基于校准后的系统时间生成视频信号的参考场同步信号,包括:基于校准后的系统时间确定参考场同步信号的多个跳变沿的时间点;基于每个跳变沿的时间点生成参考场同步信号。由于本申请的系统时间是经过校准后的系统时间,基于校准后的系统时间确定多个跳变沿的时间点,进而生成参考场同步信号,提高了参考场同步信号的准确性。

可选地,校准后的系统时间包括校准后的当前时间,基于校准后的系统时间确定参考场同步信号的多个跳变沿的时间点,包括:基于校准后的当前时间和预设时间周期,确定多个跳变沿的时间点,其中,预设时间周期用于表示多个跳变沿中每相邻两个跳变沿之间的时间间隔。由于本申请是利用校准后的当前时间,以及多个跳变沿的预设时间周期来共同确定多个跳变沿的时间点,从而提高了多个跳变沿的时间点的准确性。

可选地,基于校准后的当前时间和预设时间周期,确定多个跳变沿的时间点,包括:基于校准后的当前时间和预设时间周期确定目标时间间隔,其中,目标时间间隔用于表示校准后的当前时间距离多个跳变沿中目标跳变沿的时间点的时长,目标跳变沿为待确定时间点,且距离所述校准后的当前时间最近的一个跳变沿;基于目标时间间隔和校准后的当前时间,确定目标跳变沿的时间点。由于本申请是利用校准后的当前时间,以及预设时间周期来单独确定每个跳变沿的时间点,从而提高了多个跳变沿的时间点的准确性。

可选地,基于每个跳变沿的时间点生成参考场同步信号,包括:当时间达到每个跳变沿的时间点时,基于中断响应函数中断,基于每个跳变沿的时间点对目标电平进行调整,以生成参考场同步信号。由于本申请确定的每个跳变沿的时间点也即中断响应时间,在每个跳变沿的时间点上,基于每个跳变沿的时间点来对目标电平进行及时调整,提高了参考场同步信号生成的有效性。

可选地,该实施例的方法由第一处理端执行,获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据,包括:第一处理端向第二处理端发送参考场同步信号;由第一处理端触发时钟芯片向第二处理端发送第一像素时钟信号,其中,第一像素时钟信号用于将第二处理端的原始输出场同步信号调整至输出场同步信号,参考场同步信号与输出场同步信号之间的偏移数据由第二处理端确定;第一处理端接收由第二处理端发送的偏移数据。由于本申请通过第一像素时钟信号将原始输出场同步信号调整至输出场同步信号,进而得到参考场同步信号与输出场同步信号之间的偏移数据,以达到根据具体的偏移数据对调整时钟芯片的输出频率机芯调整的目的,进而提高了在调节参考场同步信号与输出场同步信号时的调节精度。

可选地,基于偏移数据调整时钟芯片的输出频率,包括:第一处理端基于偏移数据调整时钟芯片的输出频率。

可选地,该方法还包括:获取输出分辨率;根据输出分辨率控制时钟芯片在第一控制模块的触发下产生第一像素时钟信号,达到了为第二处理端产生第一像素时钟信号的目的。

可选地,第一处理端为视频处理设备中的第一处理器,第二处理端为视频处理设备的第二处理器,或者,第一处理端为目标芯片中的处理模块,第二处理端为目标芯片的第三控制模块,从而本申请不仅可以应用于解码器中,还可以应用于目标芯片中,降低了信号同步的局限性。

可选地,输出频率用于生成第二像素时钟信号,第二像素时钟信号用于调整输出场同步信号,以使得参考场同步信号与调整后的输出场同步信号之间的差值处于预设范围,提高了信号同步的准确性。

可选地,基于偏移数据调整时钟芯片的输出频率,包括:基于偏移数据对应的相位调整值获取输出频率。由于本申请通过根据偏移数据确定相位调整值,以及根据相位调整值,得到输出频率,实现了在调节视频信号的输出场同步信号与参考场同步信号时,通过确定具体的相位调整值,得到具体的输出频率,从而提高了调节输出场同步信号与参考场同步信号的调节精度的技术效果。

可选地,该方法还包括:通过比例积分微分PID控制器确定偏移数据对应的相位调整值。

可选地,基于偏移数据对应的相位调整值获取输出频率包括:根据相位调整值,确定频率调整值;根据频率调整值,得到输出频率。由于相位调整值有正负,即表征输出场同步信号相对于参考场同步信号是相位超前还是滞后,频率调整值也对应有正负,以有效地在当前输出频率的基础上确定上述输出频率。

可选地,该方法还包括:从缓存队列中获取视频信号的目标视频帧;将目标视频帧存储至播放准备区,并将目标视频帧的视频时间戳组播至多个子节点设备;获取到每个子节点设备对视频时间戳的应答信息,则对播放准备区的目标视频帧进行组播,实现了主节点设备对目标视频帧进行有效组播的目的。

可选地,获取到每个子节点设备对视频时间戳的应答信息,则对播放准备区的目标视频帧进行组播,包括:获取到每个子节点设备的应答信息中的视频帧号,得到多个视频帧号;确定多个视频帧号与目标视频帧的帧号一致,则对播放准备区的目标视频帧进行组播,从而提高各个子节点设备对视频信号进行同步播放的有效性。

可选地,该方法还包括:基于获取到的视频时间戳从缓存队列中获取对应的目标视频帧,且将目标视频帧存储至预备播放区域;基于播放命令对预备播放区域中的目标视频帧进行播放,实现了从节点设备对目标视频帧进行有效播放的目的。

根据本发明实施例的另一方面,还提供了一种信号同步装置。该装置可以包括:第一获取单元,用于获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号;第二获取单元,用于获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据;调整单元,用于基于偏移数据调整时钟芯片的输出频率。

根据本发明实施例的另一方面,还提供了一种信号同步系统,其特征在于,包括:第一节点设备,用于基于校准后的所述第一节点设备的系统时间生成视频信号的第一参考场同步信号,且基于所述第一参考场同步信号与所述视频信号的第一输出场同步信号之间的偏移数据,调整所述第一节点设备的时钟芯片的输出频率;第二节点设备,与所述第一节点设备相连接,用于基于校准后的所述第二节点设备的系统时间生成所述视频信号的第二参考场同步信号,且基于所述第二参考场同步信号与所述视频信号的第二输出场同步信号之间的偏移数据,调整所述第二节点设备的时钟芯片的输出频率。

可选地,校准后的第二节点设备的系统时间与校准后的第一节点设备的系统时间相同。

根据本发明实施例的另一方面,还提供了一种计算机可读存储介质。该计算机可读存储介质包括存储的程序,其中,在程序被处理器运行时控制存储介质所在设备执行本发明实施例的信号同步方法。

根据本发明实施例的另一方面,还提供了一种视频处理设备,其特征在于,视频处理设备包括第一处理器、时钟芯片以及用于提供硬件时间戳的硬件芯片,第一处理器用于执行本发明实施例的信号同步方法。

在本发明实施例的信号同步方法中,获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号;获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据;基于偏移数据调整时钟芯片的输出频率。也就是说,本申请基于校准后的系统时间生成可以作为视频信号的同步参考源的参考场同步信号,通过参考场同步信号与视频信号的输出场同步信号之间的偏移数据,来调整时钟芯片的输出频率,达到了对时钟芯片的输出频率进行调整的目的,避免了繁琐地布线过程,从而在控制成本的前提下,做到了真正的去中心化分布式,解决了信号同步的效率低大的技术问题,达到了提高信号同步的效率的技术效果。

附图说明

此处所说明的附图用来提供对本发明的进一步理解,构成本申请的一部分,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

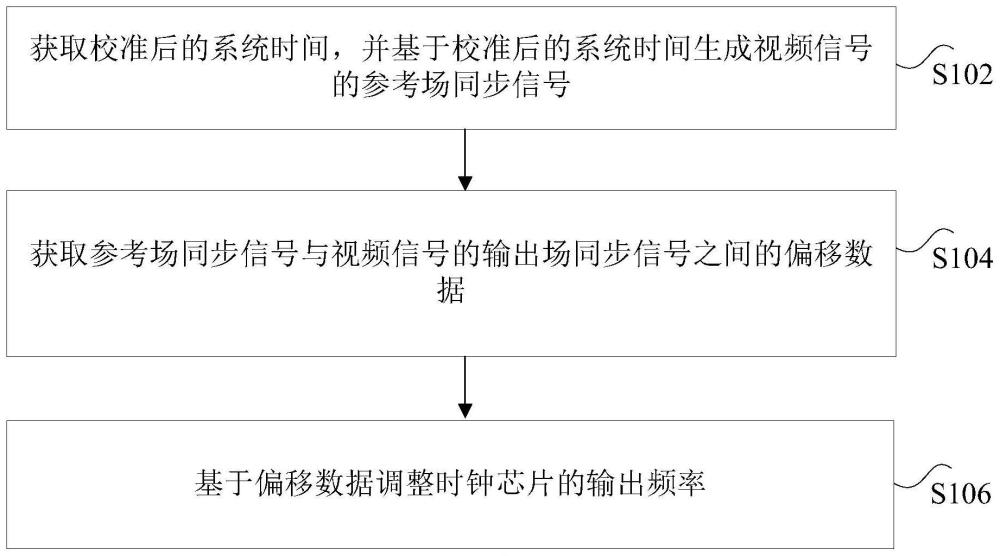

图1是根据本发明实施例的一种信号同步方法的流程图;

图2是根据相关技术中的一种大屏系统的示意图;

图3是根据本发明实施例的一种高精度分布式视频拼接同步系统的示意图;

图4是根据本发明实施例的一种高精度分布式视频拼接同步的软件示意图;

图5是根据本发明实施例的一种同步系统整体的方法的流程图;

图6是根据本发明实施例的一种输出节点设备拓扑结构设计的示意图;

图7是根据本发明实施例的一种大屏间同步相互关系的大概模型的示意图;

图8是根据本发明实施例的一种linuxPTP的时间状态通信方法的流程图;

图9是根据本发明实施例的一种主进程的时间状态通信方法的流程图;

图10是根据本发明实施例的一种通过软件进行控制的示意图;

图11是根据本发明实施例的另一种通过软件进行控制的示意图;

图12是根据本发明实施例的一种信号同步装置的示意图;

图13是根据本发明实施例的一种信号同步系统的示意图。

具体实施方式

为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分的实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

需要说明的是,本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本发明的实施例能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

下面对本申请实施例涉及的术语进行名词解释:

场同步信号,(VSYNC,简称为VS),作用是选择出显示面板上有效场信号区间;

微处理器(Advanced RISC Machines,简称为ARM),为一个32位元精简指令集的处理器架构;

微控制单元(Microcontroller Unit,简称为MCU),是指将中央处理器、只读存储器、随机存取存储器、定时计数器和多种I/O接口集成在一片芯片上,形成芯片级的计算机;

同步锁相(Genlock),可以使一套或多套系统与同一同步源实现同步,例如,可以控制视频处理设备的输出视频信号的时序参数(PCLK、HS、VS),使其与外部参考信号同步,达到输出视频信号与参考信号同步的目的;

帧同步(Framelock),控制设备的输出视频信号的帧频与外部参考信号的帧频同步,达到输出视频信号与参考信号帧频同步的目的,帧同步又称帧级同步,是视频的同步锁相(Genlock)中的一种方法;

比例积分微分控制器(Proportion Integration Differentiation,简称为PID),根据给定值和实际输出值构成控制偏差,一种算法简单、鲁棒性好、可靠性高的控制算法;

现场可编程逻辑门阵列(Field Programmable Gate Array,简称为FPGA)芯片,属于专用集成电路领域中的半定制电路。

实施例1

根据本发明实施例,提供了一种信号同步方法的实施例。需要说明的是,在附图的流程图示出的步骤可以在诸如一组计算机可执行指令的计算机系统中执行,并且,虽然在流程图中示出了逻辑顺序,但是在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤。

可选地,该实施例的信号同步方法可以由视频处理设备执行,其中,该视频处理设备可以包括:处理器、切换器或视频拼接器等用于进行视频处理或控制的设备。需要说明的是,上述视频处理设备可以是多种类型的,例如,可以是用于处理视频信号的终端,也可以是用于执行处理视频信号功能的服务器等。

可选地,该实施例的信号同步方法还可以由处理器执行,该处理器可以包括MCU、ARM或FPGA等用于进行数据处理的器件,可以为上述视频处理设备的处理器;还可以由集控制模块和处理模块的芯片执行。

图1是根据本发明实施例的一种信号同步方法的流程图。如图1所示,该方法可以包括以下步骤:

步骤S102,获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号。

在本发明上述步骤S102提供的技术方案中,可以对解码器或视频处理设备等的系统时间进行校准,得到校准后的系统时间,也即,该实施例可以对解码器或视频处理设备的系统时间进行调整,该调整过程可以是持续不断的调整过程,以保证解码器或视频处理设备所在的系统在运行的过程中,系统时间的偏差控制在一定的误差内,保证校时的准确性,进而可以基于校准后的系统时间生成视频信号的参考场同步信号。

步骤S104,获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据。

在本发明上述步骤S104提供的技术方案中,在基于校准后的系统时间生成视频信号的参考场同步信号之后,可以获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据。

在该实施例中,输出场同步信号(视频输出VS或输出VS)可以用于控制显示屏的显示,比如,控制显示大屏的显示。该实施例可以以参考场同步信号作为同步参考源,对参考场同步信号和输出场同步信号进行比较,得到参考场同步信号和输出场同步信号之间的差值,可以将该差值确定为参考场同步信号和输出场同步信号之间的偏移(offset)数据,其可以称为offset差值。

可选地,该实施例获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据,可以是获取参考场同步信号与视频信号的输出场同步信号之间的相位差,比如,可以接收可编辑逻辑门阵列FPGA发送的上位相位差;或者,通过鉴相器接收参考场同步信号与视频信号的输出场同步信号,并获得参考场同步信号与视频信号的输出场同步信号之间的相位差。通过上述处理,参考场同步信号与视频信号的输出场同步信号的相位差可以直接由FPGA得到,比如,FPGA中具有同步锁相模块(Genlock模块),其可以用于对参考场同步信号和输出场同步信号进行持续比较,得到上述相位差,进而将该相位差确定为上述偏移数据;可选地,参考场同步信号与视频信号的输出场同步信号的相位差也可以直接由鉴相器得到,或者还可以由FPGA芯片和鉴相器两者结合得到(例如,鉴相器集成于FPGA芯片中的情况)。

步骤S106,基于偏移数据调整时钟芯片的输出频率。

在本发明上述步骤S106提供的技术方案中,在获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据之后,可以基于偏移数据调整时钟芯片的输出频率。

在该实施例中,可以根据获取到的偏移数据计算出需要调整的时钟芯片的输出频率,可以是通过同步锁相模型采用控制算法根据偏移数据计算出需要调整的时钟芯片的输出频率,该输出频率可以称为像素时钟频率,其中,控制算法可以为Genlock自动控制算法。由于该输出频率可以是针对时钟芯片而言的,从而该输出频率可以称为时钟芯片输出频率,其可以用于调整输出场同步信号,使得参考场同步信号与调整后的输出场同步信号之间的差值处于预设范围内,比如,该预设范围为+-5us,此处不做具体限制。

可选地,该实施例可以是根据参考场同步信号与输出场同步信号之间的相位差得到输出场同步信号相对于参考场同步信号的变化趋势,从而根据该变化趋势对应调整时钟芯片的输出频率。

在相关技术中,并未对系统时间进行校准,而本申请通过上述步骤S102至步骤S106,获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号;获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据;基于偏移数据调整时钟芯片的输出频率。也就是说,该实施例基于校准后的系统时间生成可以作为视频信号的同步参考源的参考场同步信号,通过参考场同步信号与视频信号的输出场同步信号之间的偏移数据,来调整时钟芯片的输出频率,达到了对时钟芯片的输出频率进行调整的目的,避免了繁琐地布线过程,从而在控制成本的前提下,做到了真正的去中心化分布式,解决了信号同步的效率低的技术问题,达到了提高信号同步的效率的技术效果。

下面对该实施例的上述方法进行进一步地介绍。

作为一种可选的实施方式,获取校准后的系统时间,包括:根据第一节点设备中第一目标芯片的硬件时间戳,得到校准后的系统时间。

在该实施例中,由于网络传输,多个节点设备(主节点设备、至少一个从节点设备)之间存在快慢不一致的问题,如果两个节点设备的系统时钟不同,则节点设备之间没有任何对比,就无法做精准地测算。而该实施例的多个节点设备共同带载拼接显示同一个视频画面,通过对节点设备的系统时间进行校准,可以使得视频信号对应的视频画面同步播放、无撕裂。

在该实施例中,第一节点设备包括第一目标芯片,第一目标芯片为用于为第一节点设备提供硬件时间戳的硬件芯片,可以为接口芯片(PHY),该实施例的第一节点设备或第二节点设备可以根据第一目标芯片的硬件时间戳,来得到校准后的系统时间。可选地,该实施例的第一节点设备可以为主节点设备,第二节点设备可以为从节点设备。

作为一种可选的实施方式,根据第一节点设备中第一目标芯片的硬件时间戳,得到校准后的系统时间,包括:根据硬件时间戳,对第一节点设备的系统时间进行校准,得到校准后的系统时间,其中,校准后的系统时间与硬件时间戳相同。

在该实施例中,第一目标芯片可以为主节点设备(主节点)提供硬件时间戳。在实现获取校准后的系统时间时,对于主节点设备而言,可以是获取主节点设备的系统时间以及第一目标芯片的硬件时间戳。该实施例可以将主节点设备的系统时间,校准至主节点设备的第一目标芯片的硬件时间戳,也即,该实施例只需要将主节点设备的系统时间对齐至主节点设备的第一目标芯片的硬件时间戳,从而得到校准后的系统时间,该校准后的系统时间与硬件时间戳相同,达到了对主节点设备的系统时间进行校准的目的。其中,主节点设备可以为专业视听领域中支持坐席和大屏管理的分布式系统的主节点设备。

由于该实施例将主节点设备的系统时间与自己的第一目标芯片的硬件时间戳进行对齐,这样可以保证系统运行的过程中,时间偏差是控制在一定的误差内,从而实现了对主节点设备的系统时间进行有效校准。

需要说明的是,在执行上述步骤S102之前,可以先判断主节点设备的系统时间与主节点设备的第一目标芯片的硬件时间戳是否相同。如果判断出上述系统时间与上述硬件时间戳不相同,则可以将上述系统时间校准至硬件时间戳,得到校准后的系统时间;如果判断出上述系统时间与上述硬件时间戳相同,则可以不对上述系统时间进行校准,可以直接基于该系统时间生成视频信号的参考场同步信号,获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据,进而基于偏移数据调整时钟芯片的输出频率。也即,该实施例对主节点设备的系统时间进行校准,是在主节点设备的系统时间与主节点设备的第一目标芯片的硬件时间戳不相同的情况下进行的,而并非任何时候都对主节点设备的系统时间进行校准,从而降低信号同步的复杂度,以保证信号同步的效率。

作为一种可选的实施方式,步骤S102,获取校准后的系统时间,包括:根据第一节点设备中第一目标芯片的硬件时间戳,得到校准后的系统时间,包括:根据第一节点设备中第一目标芯片的硬件时间戳,对第二节点设备的第二目标芯片的硬件时间戳进行校准,得到校准后的第二目标芯片的硬件时间戳;根据校准后的第二目标芯片的硬件时间戳,对第二节点设备的系统时间进行校准,得到校准后的系统时间。

在该实施例中,在实现获取校准后的系统时间时,对于从节点设备(从节点)而言,可以通过一个主节点设备来对其它从节点设备的系统时间进行校准,可以根据第一节点设备中第一目标芯片的硬件时间戳,对第二节点设备的第二目标芯片的硬件时间戳进行校准,得到校准后的第二目标芯片的硬件时间戳,也即,获取从节点设备的第二目标芯片的硬件时间戳,将其校准至主节点设备的第一目标芯片的硬件时间戳,其中,第二目标芯片可以为第二节点设备提供硬件时间戳的硬件芯片,可以为接口芯片(PHY),进而根据校准后的第二目标芯片的硬件时间戳,对第二节点设备的系统时间进行校准,得到校准后的系统时间,也即,将从节点设备的系统时间校准至校准后的第二目标芯片的硬件时间戳,这样可以将主节点设备的第一目标芯片的硬件时间戳,作为对从节点设备的系统时间进行校准的参考时间,第一目标芯片的硬件时间戳可以理解为同步时间,上述主节点设备用于发布同步时间,从节点设备用于接收同步时间,其中,从节点设备可以为专业视听领域中支持坐席和大屏管理的分布式系统的从节点设备。该实施例可以对上述从节点设备的系统时间一直进行校准,该过程为动态校准过程。

可选地,该实施例的从节点设备的数量可以为多个,每个从节点设备的系统时间均可以采用上述方法进行,也即,将每个从节点设备的系统时间对齐至主节点设备的第一目标芯片的硬件时间戳,达到了从节点设备的系统时间与主节点设备的系统时间同步的目的,并且各个从节点设备的系统时间的校准过程互不影响,从而能保证每个从节点设备的系统时间的校时的准确性。

在该实施例中,可以利用第一处理端中的linuxPTP通过硬件时间戳校准多个节点设备之间的时间。其中,linuxPTP进程可以是开源的1588协议校时代码,该实施例可以是在开源代码的基础上进行改进,增加同步状态的消息机制和上层业务应该(Application,简称为APP)可以进行状态的同步。可选地,在上述linuxPTP进程中,ptp4l从模式运行,创建消息队列,然后判时间断同步状态是否发生变化,如果判断出时间同步状态有变化,则可以发送时间同步状态消息到上述主进程,然后再判断时间同步状态是否发生变化;如果判断出同步状态没有发生变化,则可以继续判断同步状态是否发生变化。

在该实施例中,当linuxPTP进程的状态变为锁定时钟时,可以通过AXI总线通知第二处理器使用场同步信号或者同步以太网(SyncE)时钟,其可以为参考时钟。

由于该实施例通过主节点设备的第一目标芯片的硬件时间戳对从节点设备的系统时间进行校准,使得从节点设备的系统时间对齐至第一目标芯片的硬件时间戳,这样可以保证系统运行的过程中,时间偏差是控制在一定的误差内,从而实现了对从节点设备的系统时间进行有效校准。

需要说明的是,在执行上述步骤S102之前,可以先判断从节点设备的第二目标芯片的硬件时间戳与主节点设备的第一目标芯片的硬件时间戳是否相同。如果判断出第二目标芯片的硬件时间戳与第一目标芯片的硬件时间戳不相同,则可以将第二目标芯片的硬件时间戳校准至第一目标芯片的硬件时间戳;如果判断出第二目标芯片的硬件时间戳与第一目标芯片的硬件时间戳相同,则可以不将第二目标芯片的硬件时间戳校准至第一目标芯片的硬件时间戳,此时可以判断从节点设备的系统时间是否与第二目标芯片的硬件时间戳是否相同,如果判断出从节点设备的系统时间与第二目标芯片的时间戳也相同,则可以不对从节点设备的系统时间进行校准,可以直接基于该系统时间生成视频信号的参考场同步信号,获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据,进而基于偏移数据调整时钟芯片的输出频率;如果判断出从节点设备的系统时间与第二目标芯片的时间戳不相同,则可以将从节点设备的系统时间校准至第二目标芯片的时间戳。也即,该实施例对从节点设备的系统时间进行校准,是在第二目标芯片的硬件时间戳与第一目标芯片的硬件时间戳不相同,或者,第二目标芯片的硬件时间戳与第一目标芯片的硬件时间戳虽然相同,但从节点设备的系统时间与第二目标芯片的时间戳不相同的情况下进行的,而并非任何时候都对从节点设备的系统时间进行校准,从而降低信号同步的复杂度,以保证信号同步的效率。

作为一种可选的实施方式,步骤S102,基于校准后的系统时间生成视频信号的参考场同步信号,包括:确定参考场同步信号的多个跳变沿的时间点;基于每个跳变沿的时间点生成参考场同步信号,可以是在定时器中,确定参考场同步信号的多个跳变沿的时间点,然后基于每个跳变沿的时间点生成参考场同步信号。

在该实施例中,可以通过定时器使用校准后的系统时间,通过预定算法计算出参考场同步信号的多个跳变沿的时间点,通过该跳变沿的时间点可以实时设置定时器的中段响应时间,比如,将跳变沿的时间点确定为定时器的中段响应时间,并且当时间到达中断响应时间时,可以在中断处理函数中,通过内部总线控制寄存器所关联的输出IO引脚来产生参考场同步信号,比如,通过AXI总线控制寄存器所关联的输出IO引脚,控制指定通用型之输入输出(General-purpose input/output,简称为GPIO)的高低电平(0/1)状态的改变,从而产生参考场同步信号,该参考场同步信号可以为脉冲宽度调制(Pulse WidthModulation,简称为PWM)信号,中断处理函数可以为中断响应函数。

可选地,在实现通过预定算法计算出参考场同步信号的跳变沿的时间点时,可以是当通过锁定时钟(比如,1588锁定时钟)后,如果上层获取到的系统时间的校准状态处于正常状态,也即,从节点设备的校准后的系统时间与主节点设备的校准后的系统时间同步,则可以启用高级定时器(A53),以校准后的系统时间的基准时间(操作系统的基准时间)为参考点,单独计算每个跳变沿的时间点。

由于该实施例的系统时间是经过校准后的系统时间,基于校准后的系统时间确定多个跳变沿的时间点,进而生成参考场同步信号,提高了参考场同步信号的准确性。

下面对该实施例的确定参考场同步信号的多个跳变沿的时间点的方法进行进一步地介绍。

作为一种可选的实施方式,校准后的系统时间包括校准后的当前时间,基于校准后的系统时间确定参考场同步信号的多个跳变沿的时间点,包括:基于校准后的当前时间和预设时间周期,确定多个跳变沿的时间点,其中,预设时间周期用于表示多个跳变沿中每相邻两个跳变沿之间的时间间隔。

在该实施例中,校准后的系统时间可以包括校准后的当前时间,需要说明的是,该当前时间的获取是有基准进行参照的,该基准可以是零点时间,因而校准后的系统时间可以包括零点时间。该实施例可以对当前时间进行动态地实时校准,其中,当当前时间变了,相当于距离目标基准时间的时间间隔就改变了,其中,目标基准时间为系统零点时间,可以为linux系统基准时间。需要说明的是,该实施例的当前时间为以目标基准时间为参照的时间,可以理解为手表的当前的时间距离零点(00:00)的时间,在需要对其进行校准时,则只需要校准当前时间即可,因而,针对于本方案而言,各个节点设备只需要校准当前时间,以使得各个节点设备的校准后的当前时间同步。

该实施例可以结合校准后的当前时间和预设时间周期T,确定每个跳变沿的时间点,其中,预设时间周期为多个跳变沿的时间点的周期,也即,多个跳变沿中相邻两个跳变沿之间的时间间隔,比如,为1/60秒。该实施例针对每个跳变沿单独地、实时地计算其时间点,也即,每个跳变沿的时间点的计算不受已经计算出时间点的跳变沿的影响,可以是先基于校准后的当前时间和预设时间周期T,确定目标公式,该目标公式可以用于表示每个跳变沿的时间点与预设时间周期T、校准后的当前时间之间的映射关系,进而通过该目标公式动态实时地、单独计算出每个跳变沿的时间点,从而得到每个跳变沿的时间点,且避免了累计时间误差。

由于该实施例是利用校准后的系统时间中的校准后的当前时间以及多个跳变沿的预设时间周期,来动态实时地、单独地确定每个跳变沿的时间点,每个跳变沿的时间点的计算不受已经计算出时间点的跳变沿的影响,从而提高了多个跳变沿的时间点的准确性。

下面对基于校准后的当前时间、校准后的目标基准时间和预设时间周期,确定多个跳变沿的时间点的方法进行进一步地介绍。

作为一种可选的实施方式,基于校准后的当前时间和预设时间周期,确定多个跳变沿的时间点,包括:基于校准后的当前时间和预设时间周期确定目标时间间隔,其中,目标时间间隔用于表示校准后的当前时间距离多个跳变沿中目标跳变沿的时间点的时间,目标跳变沿为待确定时间点,且距离校准后的当前时间最近的一个跳变沿;基于目标时间间隔与校准后的当前时间,确定目标跳变沿的时间点。

该实施例可以基于校准后的当前时间和预设时间周期确定目标时间间隔Δt。可选地,该实施例可以获取校准后的当前时间(以目标基准时间为参照的时间)与预设时间周期之间的商,可以通过该商确定校准后的当前时间距离目标跳变沿的时间点的时长,从而得到目标时间间隔,其中,目标跳变沿为待确定时间点,且距离校准后的当前时间最近的一个跳变沿,也即,为相对于校准后的当前时间而言的下一个跳变沿,可以基于目标时间间隔与校准后的当前时间,确定目标跳变沿的时间点,可以是在校准后的当前时间的基础上加上上述目标时间间隔,从而得到目标跳变沿的时间点。

举例而言,校准后的当前时间可以为相对于目标基准时间00:00而言的校准后的当前时间16ms,预设时间周期为16.6ms,则可以确定出目标时间间隔为0.6ms,那么在校准后的当前时间点16ms的基础上加上目标时间间隔0.6ms,则可以得出目标跳变沿的时间点为16.6ms,也即,在距离校准后的当前时间点之后的0.6ms的时间,就为目标跳变沿的时间点。

需要说明的是,如果通过完整周期进行累加的方式来确定跳变沿的时间点,也即,在一个跳变沿的时间点仅仅加上一个周期,来确定下一个跳变沿的时间点,每个跳变沿均是这样处理,由于预设时间周期T为1/60秒不是整除的,无限循环,这样随着每个跳边沿的时间都通过加T的方式确定,就会出现累积误差。然而,该实施例在确定每个跳变沿的时间点时,都是利用校准后的当前时间和预设时间周期来计算出下一个跳边沿的时间点距离校准后的当前时间点的目标时间间隔Δt,从而确定出下一个跳边沿的时间点,也即,由于每个跳边沿的时间点永远都是以相对于系统零点时间而言的校准后的当前时间来计算的,而并非以每个跳变沿的上次跳变沿(比如,上升沿)的时间点为基准进行计算的,这样每个跳变沿的时间点的计算就不会受到前面跳变沿的时间点的累计时间误差的影响,避免了累积每个跳边沿的时间点的误差。由于该实施例是利用校准后的系统时间中的校准后的当前时间,以及预设时间周期来动态实时地、单独确定每个跳变沿的时间点,从而提高了多个跳变沿的时间点的准确性,从而基于每个跳变沿的时间点生成的参考场同步信号也是在一定的范围内前后跳变的,这可以基于示波器显示出。

作为一种可选的实施方式,基于每个跳变沿的时间点生成参考场同步信号,包括:当时间达到每个跳变沿的时间点时,基于中断响应函数中断,基于每个跳变沿的时间点对目标电平进行调整,以生成参考场同步信号。

在该实施例中,在实现基于每个跳变沿的时间点生成参考场同步信号时,可以是在定时器中,当时间达到每个跳变沿的时间点时,则基于中断响应函数中断,从而每个跳变沿的时间点也即触发中断的时间点,进而基于每个跳变沿的时间点对目标电平进行调整,以生产参考场同步信号。

需要说明的是,该实施例可以是基于一个跳变沿的时间点对目标电平进行调整后,通过上述计算跳变沿的时间点的方法,计算出下一个跳变沿的时间点,进而当时间达到下一个跳变沿的时间点时,则基于中断响应函数中断,基于下一个跳变沿的时间点对目标电平进行调整,以生产参考场同步信号。

由于该实施例确定的每个跳变沿的时间点也即中断响应时间,在每个跳变沿的时间点上,基于每个跳变沿的时间点来对目标电平进行及时调整,提高了参考场同步信号生成的有效性。

作为一种可选的实施方式,该实施例的方法由第一处理端执行,步骤S104,获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据,包括:第一处理端向第二处理端发送参考场同步信号;由第一处理端触发时钟芯片向第二处理端发送第一像素时钟信号,其中,第一像素时钟信号用于将第二处理端的原始输出场同步信号调整至输出场同步信号,参考场同步信号与输出场同步信号之间的偏移数据由第二处理端确定;第一处理端接收由第二处理端发送的偏移数据。

在该实施例中,第一处理端可以获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号,将该参考场同步信号发送至第二处理端。该实施例的第一处理端可以通过第一控制模块触发时钟芯片向第二处理端发送第一像素时钟信号,其中,第一控制模块可以为同步锁相模块(Genlock控制模块),第一像素时钟信号对应显示屏的像素点,通过第一像素时钟信号可以对第二处理端的原始输出场同步信号的相位进行调整,从而得到上述输出场同步信号,进而由第二处理端对参考场同步信号和输出场同步信号进行比较,得到参考场同步信号与输出场同步信号之间的偏移数据,将该偏移数据返回至第一处理端,使得第一处理端接收第二处理端发送的偏移数据。

由于该实施例通过第一像素时钟信号将原始输出场同步信号调整至输出场同步信号,进而得到参考场同步信号与输出场同步信号之间的偏移数据,以达到根据具体的偏移数据对调整时钟芯片的输出频率机芯调整的目的,进而提高了在调节参考场同步信号与输出场同步信号时的调节精度。

作为一种可选的实施方式,步骤S106,基于偏移数据调整时钟芯片的输出频率,包括:第一处理端基于偏移数据调整时钟芯片的输出频率。

在该实施例中,在实现基于偏移数据调整时钟芯片的输出频率时,可以是第一处理端利用上述第一控制模块获取偏移数据,根据偏移数据来计算出需要调整的输出频率,该输出频率可以是针对与第一处理端相连的时钟芯片而言的,从而该输出频率可以称为时钟芯片输出频率。

作为一种可选的实施方式,该方法还包括:获取输出分辨率;根据输出分辨率控制时钟芯片在第一控制模块的触发下产生第一像素时钟信号。

在该实施例中,第一处理端可以通过上述第一控制模块获取输出分辨率,该分辨率也可以称为分辨率参数,根据其配置时钟芯片,可以为第二处理端提供对应的第二像素时钟信号,达到了为第二处理端产生第一像素时钟信号的目的。

可选地,该实施例在实现第一处理端获取输出分辨率时,可以是第一处理端先读取配置文件,从该配置文件中获取到上述输出分辨率,进而为第二处理端配置时钟芯片,得到第一像素时钟信号。

可选地,该实施例还可以动态修改输出分辨率,可以判断等待消息队列是否有数据。在判断出等待消息队列有数据的情况下,可以获取修改分辨率命令,基于该修改分辨率命令获取修改后的输出分辨率。

作为一种可选的实施方式,第一处理端为视频处理设备中的第一处理器,第二处理端为视频处理设备的第二处理器,或者,第一处理端为目标芯片中的处理模块,第二处理端为目标芯片的第三控制模块。

在该实施例中,针对视频处理设备而言,上述第一处理端为视频处理设备中的第一处理器,第二处理端为视频处理设备的第二处理器。可选地,上述第一处理端为解码器中的第一处理器,第二处理端为解码器的第二处理器,其中,解码器可以为大屏系统的多个解码器中的任意解码器,多个解码器之间连接的可以只有网线,无其它连接线,从而该实施例的系统架构可以为无线传输分布式系统架构,第一处理器可以为一ARM或MCU,第二处理器可以为FPGA,上述第一处理器与第二处理器之间在连接时可以多一根输入输出(IO)线。可选地,上述第一处理端还可以为目标芯片中的处理模块,比如,为处理模块,第二处理端可以为目标芯片中的第三控制模块,比如,为控制模块,从而该实施例可以应用于视频处理设备中,还可以进一步应用于目标芯片中,降低了信号同步的局限性。

作为一种可选的实施方式,输出频率用于生成第二像素时钟信号,第二像素时钟信号用于调整输出场同步信号,以使得参考场同步信号与调整后的输出场同步信号之间的差值处于预设范围。

在该实施例中,输出频率可以用于生产第二像素时钟信号,该第二像素时钟信号可以用于调整输出场同步信号的相位,以控制参考场同步信号与调整后的输出场同步信号之间的差值处于预设范围,提高了信号同步的准确性,其中,预设范围可以为+-5us,此处不做具体限制。

可选地,在该实施例中,第一处理端可以根据输出频率生成配置信息,向时钟芯片发送配置信息,其中,配置信息用于配置时钟芯片根据输出频率生成第二像素时钟信号。通过上述处理,实现了将输出频率配置给时钟芯片,时钟芯片根据该输出钟频率生成第二像素时钟信号的目的。

作为一种可选的实施方式,第一像素时钟信号用于控制第二处理端通过第二控制模块比较参考场同步信号与输出场同步信号,以得到偏移数据。

在该实施例中,第二处理端可以包括第二控制模块,该第二控制模块可以为同步锁相模块(Genlock控制模块),可以通过该第二控制模块获取第一像素时钟信号以及参考场同步信号,进而在该第二控制模块中比较参考场同步信号与输出场同步信号,以得到偏移数据。

作为一种可选的实施方式,步骤S106,基于偏移数据调整时钟芯片的输出频率,包括:基于偏移数据对应的相位调整值获取输出频率。其中,该方法还包括:通过比例积分微分PID控制器确定偏移数据对应的相位调整值。

在该实施例中,偏移数据可以为参考场同步信号与输出场同步信号之间的相位差,可以通过比例积分微分PID控制器确定相位差对应的相位调整值,也即,将输出场同步信号与参考场同步信号的相位差输入PID控制器,从PID控制器中输出上相位调整值。其中,该比例积分微分PID控制器,包括比例单元(P)、积分单元(I)和微分单元(D),可以根据给定值和实际输出值构成控制偏差,基本上维持变量稳定,是一种算法简单、鲁棒性好、可靠性高的控制器。

在相关技术中,通常在机械控制中应用PID算法,而该实施例针对显示屏的显示控制,通过比例积分微分PID控制器确定偏移数据对应的相位调整值,其中,比例积分微分PID控制器中的比例系数KP可以用于对相位差对应的相位调整值实现比例控制,其使得控制器的输出与输入误差信号成比例关系,当仅有比例控制时系统输出存在稳态误差;上述积分系数KI可以用于对相位差对应的相位调整值进行积分控制,其使得控制器的输出与输入误差信号的积分成正比关系,以消除确定的相位差对应的相位调整值的稳态误差;微分系数KD可以用于对相位差对应的相位调整值实现微分控制,其使得控制器的输出与输入误差信号的微分(即误差的变化率)成正比关系,可加快大惯性系统响应速度以及减弱超调趋势,这可以加快确定对相位差对应的相位调整值的响应速度以及减弱超调趋势。上述比例系数KP、积分系数KI和微分系数KD可以根据确定相位差对应的相位调整值的过程的动态特性进行及时整定,如果过程的动态特性变化,则比例系数KP、积分系数KI和微分系数KD就可以重新整定,以自动演算出最佳的比例系数KP、积分系数KI和微分系数KD,从而确定出可靠性高的相位调整值,进而根据相位调整值来有效调整时钟芯片的输出频率,达到了对时钟芯片的输出频率进行调整的目的,进而提高了信号同步的效率。

由于该实施例通过根据偏移数据确定相位调整值,以及根据相位调整值,得到输出频率,实现了在调节视频信号的输出场同步信号与参考场同步信号时,通过确定具体的相位调整值,得到具体的输出频率,从而提高了调节输出场同步信号与参考场同步信号的调节精度的技术效果。

作为一种可选的实施方式,通过比例积分微分PID控制器确定偏移数据对应的相位调整值,包括:整定PID控制器的控制系数,其中,控制系数包括:比例系数,积分系数和微分系数;通过整定系数后的PID控制器确定偏移数据对应的相位调整值。

在该实施例中,整定PID控制器的控制系数,可以平衡收敛速度和过冲幅度。通过整定系数后的PID控制器确定相位差对应的相位调整值,得到精确的相位调整值,从而为后续根据相位调整值,得到精确的输出频率提供基础。

作为一种可选的实施方式,基于偏移数据对应的相位调整值获取输出频率,包括:根据相位调整值,确定频率调整值;根据频率调整值,得到输出频率。

在通过比例积分微分PID控制器确定偏移数据对应的相位调整值之后,可以根据相位调整值,得到输出频率,可以采用以下方式得到输出频率:先根据相位调整值,得到频率调整值;之后,根据频率调整值,得到输出频率。需要说明的是,由于相位调整值有正负,即表征输出场同步信号相对于参考场同步信号是相位超前还是滞后,所以频率调整值也对应有正负,即在视频信号的当前输出频率的基础上加上还是减去该频率调整值对应的数值,以得到上述输出频率。

可选地,该实施例还可以采用以下方式得到输出频率:先确定相位调整值占N个帧周期的百分比,其中,N为正整数;根据视频信号的当前输出频率,以及百分比,确定输出频率。其中,N个帧周期用于表征视频信号的输出场同步信号的当前相位值。需要说明的是,上述所指的相位调整值以及N个帧周期可以采用单位统一的时间表示,比如,均可以采用秒表示,或者均可以采用纳秒表示。

可选地,该实施例在根据视频信号的当前输出频率,以及百分比,确定输出频率时,可以通过以下方式来确定相位调整值占N个帧周期的百分比:incr_freq_percent=incr_phase/gen_vs_T,其中,incr_freq_percent为百分比,incr_phase为相位调整值,gen_vs_phase为N个帧周期。如上述,该incr_phase和gen_vs_phase可以采用单位统一的时间表示,当单位不统一时,可以在上述公式中加入一个公式转换的数值,例如,当gen_vs_T的单位为秒,而incr_phase的单位为纳秒时,可以将gen_vs_T乘以10的9次方,得到gen_vs_T的单位为纳秒的数值,而后依据公式计算百分比。

需要指出的是,上述通过频率调整值得到输出频率的方式,和通过当前输出频率,以及百分比,确定输出频率的方式,可以根据需要灵活选择,但不管采用上述哪种方式,均有效地利用了相位与频率之间的关系,实现了将相位调整转化为了频率调整,从而能够方便,准确地为后续的时钟生成器配置输出频率。

作为一种可选的实施方式,该方法还包括:从缓存队列中获取视频信号的目标视频帧;将目标视频帧存储至播放准备区,并将目标视频帧的视频时间戳组播至多个子节点设备;获取到每个子节点设备对视频时间戳的应答信息,则对播放准备区的目标视频帧进行组播。

在该实施例中,缓存队列中可以包括视频信号的至少预定数量的视频帧,其可以包括待组播的目标视频帧,主节点设备可以从缓存队列中获取上述目标视频帧,该目标视频帧也即从缓存队列中成功获取到的一帧数据,然后将目标视频帧存储至播放准备区,该播放准备区也即视频播放的预备区,进而将该目标视频帧的视频时间戳(数据帧时间戳)组播至所有的子节点设备。其中,每个子节点设备可以对视频时间戳进行应答,得到应答信息,该应答信息可以包括子节点设备有没有解码出目标视频帧(成功找到目标视频帧)等信息。主节点设备获取到每个子节点设备对视频时间戳的应答信息,如果基于应答信息确定每个子节点设备都解码出目标视频帧,则可以组播一个播放命令,对播放准备区的目标视频帧进行播放,否则,可以舍弃目标视频帧,获取目标视频帧在视频信号中的下一帧视频数据,重复上述步骤,实现了主节点设备对目标视频帧进行有效组播的目的。

可选地,获取到每个子节点设备对视频时间戳的应答信息,则对播放准备区的目标视频帧进行组播,包括:获取到每个子节点设备的应答信息中的视频帧号,得到多个视频帧号;确定多个视频帧号与目标视频帧的帧号一致,则对播放准备区的目标视频帧进行组播。

在该实施例中,每个子节点设备的应答信息可以包括子节点设备解码出的目标视频帧帧号。该实施例可以获取每个子节点设备的应答信息中的视频帧号,得到多个视频帧号,该视频帧号的数量可以与多个子节点设备的数量相同,然后判断多个视频帧号是否与从缓存队列中获取到的目标视频帧的帧号是否一致,比如,目标视频帧的帧号为100,判断多个视频帧号是否也是100,也即,确定多个子节点设备是否都解码出目标视频帧了。如果判断出多个视频帧号与目标视频帧的帧号一致,则说明多个子节点设备都解码出目标视频帧,从而该实施例确保每个子节点设备都解码出目标视频帧,这样才可以对播放准备区的目标视频帧进行组播,从而提高各个子节点设备对视频信号进行同步播放的有效性。

可选地,该方法还包括:确定多个视频帧号与目标视频帧的帧号不全一致,则可以从缓存队列中再次选取出视频帧,比如,将缓存队列中的上述目标视频帧的下一帧选取出,可以将其确定为目标视频帧,进而将目标视频帧存储至播放准备区,并将此次重新选取出的目标视频帧的视频时间戳组播至多个子节点设备,然后获取到每个子节点设备的应答信息中的视频帧号,得到多个视频帧号,判断确定此次多个视频帧号与目标视频帧的帧号是否一致,如果一致,则可以对播放准备区的重新选取出的目标视频帧进行组播,如果不全一致,则可以从缓存队列中再次选取出视频帧,重复上述流程,直至缓存队列中的视频帧都已确定是否进行组播,以提高各个子节点设备对视频信号进行同步播放的有效性。

作为一种可选的实施方式,该方法还包括:基于获取到的视频时间戳从缓存队列中获取对应的目标视频帧,且将目标视频帧存储至预备播放区域;基于播放命令对预备播放区域中的目标视频帧进行播放。

在该实施例中,子节点设备在可以获取到主节点设备发送的视频时间戳之后,可以从缓存队列中获取视频时间戳对应的目标视频帧,并且将获取到的目标视频帧存储至预备播放区域,向主节点设备回复查找目标视频帧成功。如果从缓存队列中未获取视频时间戳对应的目标视频帧,则可以向主节点设备回复查找目标视频帧失败。在子节点设备向主节点设备回复查找目标视频帧成功之后,可以获取到播放命令,进而基于该播放命令从预备播放区域中获取到目标视频帧,并对该目标视频帧进行播放,并向主节点设备返回播放成功消息,实现了从节点设备对目标视频帧进行有效播放的目的。

作为一种可选的示例,可以在主进程中,启动同步线程,判断系统中的节点设备是否为主节点设备,其中,主节点设备上的时钟可以称为主时钟,发布同步时间的端口可以称为主端口。如果判断出系统中的节点设备是主节点设备,则可以读取配置文件,从该配置文件中获取输出分辨率,进而为第二处理端配置时钟芯片,得到像素时钟信号,还可以调用定时器驱动产生参考场同步信号,同步锁定模块可以重新校准场同步信号的相位同步。在重新校准场同步信号的相位同步之后,可以判断等待消息队列是否有数据,在等待消息队列有数据的情况下,获取修改分辨率命令,基于该修改分辨率命令获取修改后的输出分辨率,进而为第二处理端配置时钟芯片,得到像素时钟信号。可选地,该实施例可以调用定时器驱动产生参考场同步信号,同步锁定模块可以重新校准场同步信号的相位同步,然后继续判断等待消息队列是否有数据,重复上述步骤。其中,该实施例还可以通过主节点设备启动ptp4l进程(主模式),组播发送同步命令。

可选地,可以通过上述主节点设备启动校时主(master)端,同时根据时间(timming)数据设置时钟频率和控制产生对应的参考场同步信号。在系统运行过程中可以动态监测用户是否修改了输出分辨率,根据修改后的输出分辨率可以重新设置时钟频率和控制产生参考场同步信号。

作为另一种可选的示例,如果判断出系统中的节点设备不为主节点设备,比如,为从节点设备,则可以读取配置文件,从该配置文件中获取输出分辨率,其中,将接收同步时间的节点设备则称为从节点设备,从节点设备上的时钟可以称为从时钟,接收同步时间的端口可以称为从端口。然后等待时钟同步,进而为第二处理端配置时钟芯片,得到像素时钟信号,还可以调用定时器驱动产生参考场同步信号,同步锁定模块可以重新校准场同步信号的相位同步。在重新校准场同步信号的相位同步之后,可以判断等待消息队列是否有数据,在等待消息队列有数据的情况下,获取修改分辨率命令,基于该修改分辨率命令获取修改后的输出分辨率,进而为第二处理端配置时钟芯片,得到像素时钟信号。可选地,该实施例可以调用定时器驱动产生参考场同步信号,同步锁定模块可以重新校准场同步信号的相位同步,然后继续判断等待消息队列是否有数据,重复上述步骤。在等待消息队列没有数据的情况下,可以获取时钟同步状态变化命令,进而为第二处理端配置时钟芯片,得到像素时钟信号,还可以调用定时器驱动产生参考场同步信号,同步锁定模块可以重新校准场同步信号的相位同步,然后继续判断等待消息队列是否有数据,重复上述步骤。其中,可以通过从节点设备启动ptp4l进程(从模式)尝试与主时钟同步,在时钟同步之后可以通知主进程。

可选地,在该实施例中,上述从节点设备可以启动校时从(slave)端,等待slave端时间和master端同步之后,可以根据timming数据设置时钟频率和控制产生对应的参考场同步信号。在系统运行过程中可以动态监测用户是否修改了输出分辨率,根据修改后的输出分辨率可以重新设置时钟频率和控制产生参考场同步信号。

在该实施例中,第一级交换机的Master端可以是外购高精度的Master端,也可以是设置一个输出节点设备为Master端来推送1588协议和SyncE时钟;系统的节点设备作为主节点设备的精度有限,受温度的影响波动会较大,外购master可以提升整个系统基准时间的精度;当第一级交换机Master的1588协议外接子节点设备超过最大性能后,需要在第二级交换机的节点设备上设置一个S/M节点设备,该S/M节点设备作为从节点设备和第一级主Master对时,同时也作为主节点设备给第二级交换机下的从节点设备做Master服务器。

在该实施例中,在主进程中启动主进程同步线程,然后创建消息队列,判断时间同步状态是否由未锁定变化为锁定,如果时间同步状态由未锁定变化为锁定,则复位第二处理端的时钟模块,继续判断时间同步状态是否由未锁定变化为锁定;如果判断出时间同步状态未由锁定变化为锁定,则继续判断时间同步状态是否由未锁定变化为锁定。

在该实施例中,由于一个大屏系统是可以由多个节点设备共同带载拼接显示同一个视频画面,因而多个节点设备间的视频显示需要做到帧同步,否则就会产生视频画面的撕裂。多个节点设备之间连接的只有网线,无其他连接线,从而在控制成本的前提下,做到了真正的去中心化分布式视频系统,系统安全,稳定可靠,可扩展性强,并且可以解决传统分布式系统无法满足远距离传输,跨地域传输问题,从而解决了信号同步的效率低的技术问题,达到了提高信号同步的效率的技术效果。

实施例2

下面结合优选的实施方式对本发明实施例的上述方法进行进一步地举例说明,具体以第一处理端为解码器中的ARM,第二处理端为解码器中的FPGA进行举例介绍。

图2是根据相关技术中的一种大屏系统的示意图。如图2所示,该分布式系统包括输入节点设备(编码Encoder节点设备)、输出节点设备(解码Decoder节点设备)、交换机、上位机。多个输出节点设备组成一个坐席席位,每个坐席席位设置一套键盘和鼠标;多个输出节点设备组成一个大屏控制器,共同带载显示同一个大屏视频画面(LED大屏、LCD大屏)。该系统主要由坐席系统,大屏管理系统和中控系统三部分组成。

由于一个大屏系统是由多个解码器节点设备共同带载拼接显示同一个视频画面,所以多个节点设备间的视频显示必须做到帧同步,否则就会产生视频画面的撕裂。

由于在分布式系统中,网络传输会节点设备存在快慢不一致的问题,两个节点设备的系统时钟不同,节点设备之间没有任何对比,无法做精准的测算。因而,现有的大屏控制器主要是集中式设备(比如,集中式拼接器),其距离短,走的是铜线,通过电信号传输,设备内通过互联IO来传递参考VS,不同的接口根据参考VS进行帧同步。分布式系统因为不同的节点设备间只有网线一种介质,所以想要做到同步,也只能通过网口来进行设计。

在相关技术中,集中式设备的内部多接口之间可以通过互联IO作为参考VS,进行VS同步。但是其必须在一个机箱内才可以进行同步;而分布式系统的多个节点设备间需要单独连接Genlock线才能进行同步。主要使得布线繁琐,且不利于远距离传输,也不方便升级扩容。

针对上述问题,该实施例可以实现一种高精度分布式视频拼接同步方法。下面对其进行进一步地举例介绍。

图3是根据本发明实施例的一种高精度分布式视频拼接同步系统的示意图。如图3所示,该系统可以包括:显示大屏1、解码器2和交换机3,其中,显示大屏1与解码器2相连接,解码器2与交换机3相连接。

该实施例的解码器2可以支持1588硬件时间戳。如果不用硬件时间戳,使用系统软件时间戳的话,时间同步进度会降低10倍以上。

ARM可以通过硬件时间戳校准解码器2和其它解码器间的时间,此调节过程是持续不断的调整过程,这样在保证系统运行的过程中,解码器2和其它解码器之间的偏差控制在一定的误差内。

另外,系统中每个大屏中用到的节点设备都会有一个节点设备作为主节点设备来校准其他节点设备的时间。多个大屏中的校时过程互不影响,能保证每个主节点设备的校时准确性。

ARM可以使用校准后的系统时间,使用VS生产算法,计算出每个VS跳变的时间点,实时设置中断响应时间,在中断响应函数中,通过内部AXI总线控制寄存器,寄存器关联对应的输出IO引脚产生参考VS。

该实施例可以在FPGA中持续比较参考VS和视频输出VS间的差值,将其确定为ARMoffset数据。

该实施例的ARM可以根据ARM offset数据计算出需要调整的时钟芯片的输出频率,从而控制参考VS和视频输出VS间的差值在

图4是根据本发明实施例的一种高精度分布式视频拼接同步的软件示意图。如图4所示,LinuxPTP进程用于节点设备间的时间同步;参考VS输出模块用于使用Linux高级定时器(hrtimer)产生VS参考信号;Genlock校准模块用于给FPGA产生像素时钟信号,然后在FPGA中校准视频输出VS与参考VS,使得信号相位同步。

图5是根据本发明实施例的一种同步系统整体的方法的流程图。如图5所示,该方法可以包括以下步骤:

步骤S601,在主进程中,启动同步线程。

步骤S602,判断系统中的节点设备是否为主节点设备。

该实施例可以将发布同步时间的节点设备称为主节点设备,主节点设备上的时钟可以称为主时钟,发布同步时间的端口可以称为主端口。

步骤S603,从配置文件中获取输出分辨率。

如果判断出系统中的节点设备是主节点设备,则可以读取配置文件,从该配置文件中获取输出分辨率。

步骤S604,判断等待消息队列是否有数据。

该实施例可以判断等待消息队列是否有数据。

步骤S605,获取修改分辨率命令。

在等待消息队列有数据的情况下,获取修改分辨率命令,通过该修改分辨率命令获取修改后的输出分辨率。

该实施例可以继续判断等待消息队列是否有数据,重复上述步骤,直至循环结束。

步骤S606,从配置文件中获取输出分辨率。

如果判断出系统中的节点设备不为主节点设备,比如,为从节点设备,则可以读取配置文件,从该配置文件中获取输出分辨率。

在该实施例中,将接收同步时间的节点设备则称为从节点设备,从节点设备上的时钟可以称为从时钟,接收同步时间的端口可以称为从端口。

步骤S607,等待时钟同步。

步骤S608,判断等待消息队列是否有数据。

该实施例可以判断等待消息队列是否有数据。

步骤S609,获取修改分辨率命令。

在等待消息队列有数据的情况下,获取修改分辨率命令,基于该修改分辨率命令获取修改后的输出分辨率。

该实施例可以继续判断等待消息队列是否有数据,重复上述步骤,直至循环结束。

步骤S610,获取时钟同步状态变化命令。

在等待消息队列没有数据的情况下,可以获取时钟同步状态变化命令。

该实施例可以继续判断等待消息队列是否有数据,重复上述步骤,直至循环结束。

在该实施例中,对于主节点设备,可以启动校时master端,同时根据timming数据设置时钟频率和控制产生对应的参考VS。在运行过程中,可以动态监测用户是否修改了分辨率,根据修改后的值重新设置时钟频率和控制产生参考VS。

在该实施例中,对于从节点设备,可以启动校时slave端,在等待slave端时间和master同步后,可以根据timming数据设置时钟频率和控制产生对应的参考VS。在运行过程中动态监测用户是否修改了分辨率,根据修改后的值重新设置时钟频率和控制产生参考VS。

图6是根据本发明实施例的一种输出节点设备拓扑结构设计的示意图。如图6所示,输出节点设备1’可以为主节点设备(M),输出节点设备2’、输出节点设备3’、输出节点设备4’和输出节点设备5’为从节点设备(S),通过交换机A进行处理,该交换机可以为外购MASTER。可选地,输出节点设备6’可以为主从节点设备(S/M),输出节点设备7’、输出节点设备8’、输出节点设备9’、输出节点设备n为从节点设备(S),通过交换机B进行处理。

在该实施例中,第一级交换机可以是外购高精度Master,也可以是设置一个输出节点设备为Master来推1588协议和SyncE时钟;系统节点设备作为主节点设备的精度有限,受温度的影响波动会较大,外购master可以提升整个系统基准时间的精度。

当第一级交换机主Master的1588协议外接子节点设备超过最大性能后,需要在第二级交换机的节点设备上设置一个S/M节点设备,该节点设备作为从节点设备和第一级主Master对时,同时也作为主节点设备给第二季交换机下的从节点设备做Master服务器。

图7是根据本发明实施例的一种大屏间同步相互关系的大概模型的示意图。如图7所示,大屏与从节点设备、主节点设备、从节点设备相关联,ptpd控制驱动产生定时器,触发Vs信号。

该实施例可以在Linuxptp模块中,给不同的节点设备发时间戳,进行时钟对比,当握手成功时,可以打印一个时间同步的信号,通过其来计算产生参考VS。在该实施例中,linuxPTP是开源的1588协议校时代码,可以在开源代码的基础上进行改造,增加了时间同步状态的消息机制,和上层业务APP可以进行状态的同步。

图8是根据本发明实施例的一种linuxPTP的时间状态通信方法的流程图。如图8所示,该方法可以包括以下步骤:

步骤S901,ptp4l从模式运行。

步骤S902,创建消息队列。

步骤S903,判断获取的时间同步状态是否发生变化。

步骤S904,发送时间同步状态消息到主进程。

如果判断出获取的时间同步状态发生变化,则发送时间同步状态消息到主进程。

在发送时间同步状态消息到主进程之后,进行下一次判断,判断获取的时间同步状态是否发生变化。

如果判断出获取的时间同步状态未发生变化,则继续判断获取的时间同步状态是否发生变化。

图9是根据本发明实施例的一种主进程的时间状态通信方法的流程图。如图9所示,该方法可以包括以下步骤:

步骤S1001,主进程同步线程。

步骤S1002,创建消息队列。

步骤S1003,判断时间同步状态是否由未锁定状态变为锁定状态。

步骤S1004,复位FPGA时钟模块。

如果判断出时间同步状态由未锁定状态变为锁定状态,则复位FPGA时钟模块。

在复位FPGA时钟模块之后,进行下一次判断,判断时间同步状态是否由未锁定状态变为锁定状态。

如果判断出时间同步状态未由未锁定状态变为锁定状态,则继续判断时间同步状态是否由未锁定状态变为锁定状态。

在该实施例中,可以使用A53产生参考VS。该实施例当ARM通过1588锁定时钟后,如果上层获取到时间校准状态正常,则可以启用A53高级定制器,该高级定时器的触发中断的时间每次单独计算,计算方法可以为以linux系统基准时间为参考点,计算出当前时间点距离下一次VS跳变沿的时间,可以在中断处理函数中驱动GPIO进行电平0/1状态改变,从而输出参考VS,该参考VS可以为PWM波。

在该实施例中,VS信号的产生可以是由hrtimer产生定时器修改指定GPIO的电平,而产生的。图10是根据本发明实施例的一种通过软件进行控制的示意图。如图10所示,在时间同步之后,ptpd控制驱动产生定时器,触发参考VS,并实时上报参考VS和视频输出VS之间的偏移数据,当偏移数据过大时,可以重新生成定时器。

图11是根据本发明实施例的另一种通过软件进行控制的示意图。如图11所示,该实施例可以由软件(ptpd)触发,指定帧率,产生对应定时器,然后由驱动控制定时器,在定时器中断处理函数中,可以通过AXI总线控制FPGA的GPIO高低电平的变化,从而产生参考VS。

可选地,在该实施例中,当linuxPTP的状态变为锁定时钟后,可以通过AXI总线通知FPGA使用VS或者SyncE时钟。

在该实施例中,可以在第一次启动定时器或者每次定时器产生中断后,通过预定短发计算出下一个VS时钟跳变的时刻,然后设置下一次定时器的中断时间。计算的参考基准时间可以为系统的基准时间。

在该实施例中,上述Genlock模块可以根据输出分辨率配置时钟芯片,为FPGA提供对应的像素时钟。当1588时间校准完成时,会通知FPGA使用参考VS作为同步参考源。

在该实施例中,由于一个大屏系统是可以由多个解码器节点设备共同带载拼接显示同一个视频画面,因而多个解码器节点设备间的视频显示需要做到帧同步,否则就会产生视频画面的撕裂。多个解码器节点设备之间连接的只有网线,无其他连接线,从而在控制成本的前提下,做到了真正的去中心化分布式视频系统,系统安全,稳定可靠,可扩展性强,并且可以解决传统分布式系统无法满足远距离传输,跨地域传输问题,从而解决了信号同步的效率低的技术问题,达到了提高信号同步的效率的技术效果。

实施例3

本发明实施例还提供了一种信号同步装置。需要说明的是,该实施例的信号同步装置可以用于执行本发明实施例图1所示的信号同步方法。

图12是根据本发明实施例的一种信号同步装置的示意图。如图12所示,该信号同步装置120可以包括:第一获取单元121、第二获取单元122和调整单元123。

第一获取单元121,用于获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号。

第二获取单元122,用于获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据。

调整单元123,用于基于偏移数据调整时钟芯片的输出频率。

可选地,第一获取单元121包括:第一获取模块,用于根据第一节点设备中第一目标芯片的硬件时间戳,得到校准后的系统时间。

可选地,第一取模块包括:第一校准子模块,用于根据硬件时间戳,对第一节点设备的系统时间进行校准,得到校准后的系统时间,其中,校准后的系统时间与硬件时间戳相同。由于本申请将主节点设备的系统时间与自己的第一目标芯片的硬件时间戳进行对齐,这样可以保证系统运行的过程中,时间偏差是控制在一定的误差内,从而实现了对主节点设备的系统时间进行有效校准。

可选地,第一获取模块包括:第二校准子模块,用于根据第一节点设备中第一目标芯片的硬件时间戳,对第二节点设备的第二目标芯片的硬件时间戳进行校准,得到校准后的第二目标芯片的硬件时间戳;第三校准子模块,用于根据校准后的第二目标芯片的硬件时间戳,对第二节点设备的系统时间进行校准,得到校准后的系统时间。由于本申请通过主节点设备的第一目标芯片的硬件时间戳对从节点设备的系统时间进行校准,使得从节点设备的系统时间对齐至第一目标芯片的硬件时间戳,这样可以保证系统运行的过程中,时间偏差是控制在一定的误差内,从而实现了对从节点设备的系统时间进行有效校准。

可选地,第一获取单元121包括:确定模块,用于基于校准后的系统时间确定参考场同步信号的多个跳变沿的时间点;生成模块,用于基于每个跳变沿的时间点生成参考场同步信号。由于本申请的系统时间是经过校准后的系统时间,基于校准后的系统时间确定多个跳变沿的时间点,进而生成参考场同步信号,提高了参考场同步信号的准确性。

可选地,校准后的系统时间包括校准后的当前时间,确定模块包括:第一确定子模块,用于基于校准后的当前时间和预设时间周期,确定多个跳变沿的时间点,其中,预设时间周期用于表示多个跳变沿中每相邻两个跳变沿之间的时间间隔。由于本申请是利用校准后的系统时间中的校准后的当前时间,以及多个跳变沿的预设时间周期来共同确定多个跳变沿的时间点,从而提高了多个跳变沿的时间点的准确性。

可选地,第一确定子模块用于通过以下步骤来基于校准后的当前时间和预设时间周期,确定多个跳变沿的时间点:基于校准后的当前时间和预设时间周期确定目标时间间隔,其中,目标时间间隔用于表示校准后的当前时间距离多个跳变沿中目标跳变沿的时间点的时长,目标跳变沿为待确定时间点,且距离校准后的当前时间最近的一个跳变沿;基于目标时间间隔与校准后的当前时间,确定目标跳变沿的时间点。由于本申请是利用校准后的系统时间中的校准后的当前时间,以及预设时间周期来单独确定每个跳变沿的时间点,从而提高了多个跳变沿的时间点的准确性。

可选地,生成模块包括:调整子模块,用于当时间达到每个跳变沿的时间点时,基于中断响应函数中断,基于每个跳变沿的时间点对目标电平进行调整,以生成参考场同步信号。由于本申请确定的每个跳变沿的时间点也即中断响应时间,在每个跳变沿的时间点上,基于每个跳变沿的时间点来对目标电平进行及时调整,提高了参考场同步信号生成的有效性。

可选地,该实施例的方法由第一处理端执行,第二获取单元122包括:第一发送模块,用于使第一处理端向第二处理端发送参考场同步信号;第二发送模块,用于使第一处理端触发时钟芯片向第二处理端发送第一像素时钟信号,其中,第一像素时钟信号用于将第二处理端的原始输出场同步信号调整至输出场同步信号,参考场同步信号与输出场同步信号之间的偏移数据由第二处理端确定;接收模块,用于使第一处理端接收由第二处理端发送的偏移数据。由于本申请通过第一像素时钟信号将原始输出场同步信号调整至输出场同步信号,进而得到参考场同步信号与输出场同步信号之间的偏移数据,以达到根据具体的偏移数据对调整时钟芯片的输出频率机芯调整的目的,进而提高了在调节参考场同步信号与输出场同步信号时的调节精度。

可选地,调整单元123包括:调整模块,用于使第一处理端基于偏移数据调整时钟芯片的输出频率。

可选地,该装置还包括:第三获取单元,用于获取输出分辨率;生成单元,用于根据输出分辨率控制时钟芯片在第一控制模块的触发下产生第一像素时钟信号,达到了为第二处理端产生第一像素时钟信号的目的。

可选地,第一处理端为视频处理设备中的第一处理器,第二处理端为视频处理设备的第二处理器,或者,第一处理端为目标芯片中的处理模块,第二处理端为目标芯片的第三控制模块,从而本申请不仅可以应用于解码器中,还可以应用于目标芯片中,降低了信号同步的局限性。

可选地,输出频率用于生成第二像素时钟信号,第二像素时钟信号用于调整输出场同步信号,以使得参考场同步信号与调整后的输出场同步信号之间的差值处于预设范围,提高了信号同步的准确性。

可选地,调整单元123包括:第二获取模块,用于基于偏移数据对应的相位调整值获取输出频率。由于本申请通过根据偏移数据确定相位调整值,以及根据相位调整值,得到输出频率,实现了在调节视频信号的输出场同步信号与参考场同步信号时,通过确定具体的相位调整值,得到具体的输出频率,从而提高了调节输出场同步信号与参考场同步信号的调节精度的技术效果。

可选地,该装置还包括:确定单元,用于通过比例积分微分PID控制器确定偏移数据对应的相位调整值。

可选地,第二获取模块包括:第二确定子模块,用于根据相位调整值,确定频率调整值;根据频率调整值,得到输出频率。由于相位调整值有正负,即表征输出场同步信号相对于参考场同步信号是相位超前还是滞后,频率调整值也对应有正负,以有效地在当前输出频率的基础上确定上述输出频率。

可选地,该装置还包括:第四获取单元,用于从缓存队列中获取视频信号的目标视频帧;第一组播单元,用于将目标视频帧存储至播放准备区,并将目标视频帧的视频时间戳组播至多个子节点设备;第二组播单元,用于获取到每个子节点设备对视频时间戳的应答信息,则对播放准备区的目标视频帧进行组播,实现了主节点设备对目标视频帧进行有效组播的目的。

可选地,第二组播单元包括:第三获取模块,用于获取到每个子节点设备的应答信息中的视频帧号,得到多个视频帧号;组播模块,用于确定多个视频帧号与目标视频帧的帧号一致,则对播放准备区的目标视频帧进行组播,从而提高各个子节点设备对视频信号进行同步播放的有效性。

可选地,该装置还包括:第五获取单元,用于基于获取到的视频时间戳从缓存队列中获取对应的目标视频帧,且将目标视频帧存储至预备播放区域;播放单元,用于基于播放命令对预备播放区域中的目标视频帧进行播放,实现了从节点设备对目标视频帧进行有效播放的目的。

在该实施例的信号同步装置中,通过第一获取单元121获取校准后的系统时间,并基于校准后的系统时间生成视频信号的参考场同步信号;通过第二获取单元122于获取参考场同步信号与视频信号的输出场同步信号之间的偏移数据;通过调整单元123基于偏移数据调整时钟芯片的输出频率。也就是说,该实施例基于校准后的系统时间生成可以作为视频信号的同步参考源的参考场同步信号,通过参考场同步信号与视频信号的输出场同步信号之间的偏移数据,来调整时钟芯片的输出频率,达到了对时钟芯片的输出频率进行调整的目的,避免了繁琐地布线过程,从而在控制成本的前提下,做到了真正的去中心化分布式,解决了信号同步的效率低的技术问题,达到了提高信号同步的效率的技术效果。

实施例4

本发明实施例还提供了一种信号同步系统。

由于网络传输,多个节点设备之间存在快慢不一致的问题,如果两个节点设备的系统时钟不同,则节点设备之间没有任何对比,就无法做精准地测算。而该实施例的多个节点设备共同带载拼接显示同一个视频画面,通过对节点设备的系统时间进行校准,可以使得该视频画面同步播放、无撕裂,下面对该实施例的信号同步系统可以进行进一步介绍。

图13是根据本发明实施例的一种信号同步系统的示意图。如图13所示,该信号同步系统130可以包括:第一节点设备131和第二节点设备132。

第一节点设备131,用于基于校准后的第一节点设备的系统时间生成视频信号的第一参考场同步信号,且基于第一参考场同步信号与视频信号的第一输出场同步信号之间的偏移数据,调整第一节点设备的时钟芯片的输出频率。

在该实施例中,第一节点设备131可以为主节点设备,对系统时间进行校准,以保证系统时间的偏差控制在一定的误差内,进而可以基于校准后的系统时间生成视频信号的第一参考场同步信号。

在该实施例中,第一节点设备131的第一输出场同步信号可以用于控制显示屏的显示。第一节点设备131的系统时间可以以第一参考场同步信号作为同步参考源,对第一参考场同步信号和第一输出场同步信号进行比较,得到偏移数据。第一节点设备131可以根据偏移数据计算出需要调整的时钟芯片的输出频率,该输出频率可以是针对第一节点设备131的时钟芯片而言的,其可以用于调整第一输出场同步信号,使得第一参考场同步信号与调整后的第一输出场同步信号之间的差值处于预设范围内。

第二节点设备132,与第一节点设备131相连接,用于基于校准后的第二节点设备的系统时间生成视频信号的第二参考场同步信号,且基于第二参考场同步信号与视频信号的第二输出场同步信号之间的偏移数据,调整第二节点设备的时钟芯片的输出频率。

在该实施例中,第二节点设备132可以为从节点设备,对系统时间进行校准,以保证系统时间的偏差控制在一定的误差内,校准后的第二节点设备132的系统时间与校准后的第一节点设备131的系统时间相同,从而使得第一节点设备131和第二节点设备132的系统时钟不同,以进行精准地测算。该实施例可以基于校准后的系统时间生成视频信号的第二参考场同步信号,该第二参考场同步信号可以与第一参考场同步信号相同。第二节点设备132的第二输出场同步信号可以用于控制显示屏的显示,第二节点设备132的系统时间可以以第二参考场同步信号作为同步参考源,对第二参考场同步信号和第二输出场同步信号进行比较,得到偏移数据,其中,第二输出场同步信号可以与第一输出场同步信号相同。第二节点设备132可以根据偏移数据计算出需要调整的时钟芯片的输出频率,该输出频率可以是针对第二节点设备131的时钟芯片而言的,其可以用于调整第二输出场同步信号,使得第一参考场同步信号与调整后的第二输出场同步信号之间的差值处于预设范围内,从而该实施例通过对第一节点设备131的系统时间和第二节点设备132的系统时间进行校准,可以使得视频信号对应的视频画面同步播放、无撕裂。

该实施例的信号同步系统中的第一节点设备和第二节点设备,可以基于校准后的系统时间生成可以作为视频信号的同步参考源的参考场同步信号,通过参考场同步信号与视频信号的输出场同步信号之间的偏移数据,来调整时钟芯片的输出频率,达到了对时钟芯片的输出频率进行调整的目的,避免了繁琐地布线过程,从而在控制成本的前提下,做到了真正的去中心化分布式,解决了信号同步的效率低的技术问题,达到了提高信号同步的效率的技术效果。

实施例5

根据本发明实施例,还提供了一种计算机可读存储介质。该计算机可读存储介质包括存储的程序,其中,在程序被处理器运行时控制存储介质所在设备执行本发明实施例的信号同步方法。

实施例6

根据本发明实施例,还提供了一种视频处理设备,其特征在于,视频处理设备包括第一处理器、时钟芯片以及用于提供硬件时间戳的硬件芯片,第一处理器用于执行本发明实施例的信号同步方法。

需要说明的是,上述第一处理器可以部署在视频处理设备中,比如,第一处理器可以为视频处理设备中的ARM或MCU。可选地,上述第一处理器也可以部署在目标芯片中,从而该实施例不仅可以应用于视频处理设备中的ARM或MCU,也可以应用于目标芯片,降低了信号同步应用的局限性。时钟芯片和用于提供硬件时间戳的硬件芯片可以与实施例1中提及的时钟芯片和硬件芯片相同,此处不再一一赘述。

需要说明的是,上述视频处理设备可以是多种类型的,例如,可以是用于处理视频信号的终端,也可以是用于执行处理视频信号功能的服务器等。

上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

在本发明的上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

在本申请所提供的几个实施例中,应该理解到,所揭露的技术内容,可通过其它的方式实现。其中,以上所描述的装置实施例仅仅是示意性的,例如单元的划分,可以为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,单元或模块的间接耦合或通信连接,可以是电性或其它的形式。

作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

另外,在本发明各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

集成的单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可为个人计算机、服务器或者网络设备等)执行本发明各个实施例方法的全部或部分步骤。而前述的存储介质包括:U盘、只读存储器(ROM,Read-Only Memory)、随机存取存储器(RAM,Random Access Memory)、移动硬盘、磁碟或者光盘等各种可以存储程序代码的介质。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 基于双控的存储设备数据同步方法、装置、设备及介质

- 视频处理方法、装置、计算机设备和存储介质

- 视频处理方法、装置、电子设备及存储介质

- 视频处理方法、装置、电子设备及存储介质

- 视频处理方法、装置、电子设备及存储介质

- 一种音视频处理同步方法、装置、电子设备和存储介质

- 基于GPS信号的基站信号同步方法、装置、设备及存储介质