摄像装置

文献发布时间:2023-06-19 09:29:07

技术领域

本公开涉及摄像装置。

背景技术

已知层叠型的摄像装置。在层叠型的摄像装置中,构成了包含半导体基板及光电转换层的层叠构造。

层叠型的摄像装置的一例记载于专利文献1及2。在专利文献1及2的摄像装置中,光电转换层被配置在对置电极与像素电极之间。

在先技术文献

专利文献

专利文献1:国际公开第2013/001809号

专利文献2:日本特开2016-127264号公报

发明内容

本发明所要解决的课题

需要得到分辨率更高的图像的技术。

用于解决课题的手段

本公开的一个方式所涉及的摄像装置具备:

光电转换层,将入射光转换为电荷;

第1像素电极,收集由所述光电转换层生成的电荷;

第2像素电极,收集由所述光电转换层生成的电荷,且在第1方向上与所述第1像素电极相邻;

屏蔽电极,与所述第1像素电极及所述第2像素电极电分离;以及

第1屏蔽过孔,从所述屏蔽电极延伸,且在平面视中位于所述第1像素电极与所述第2像素电极之间。

发明效果

本公开提供得到分辨率高的图像的技术。

附图说明

图1是表示实施方式所涉及的摄像装置的截面构造的图。

图2是表示实施方式所涉及的摄像装置的截面构造的图。

图3是表示实施方式所涉及的摄像装置的平面构造的图。

图4A是表示实施方式所涉及的摄像装置的截面构造的图。

图4B是图4A的部分扩大图。

图4C是表示与图4B的例子不同的例子所涉及的绝缘部的图。

图4D是表示绝缘层及光电转换层的制造方法的示意图。

图4E是表示绝缘层及光电转换层的制造方法的示意图。

图5A是表示实施方式所涉及的摄像装置的截面构造的图。

图5B是图5A的部分扩大图。

图6是表示光电转换层的突出部的图。

图7是表示实施方式所涉及的摄像装置的截面构造的图。

图8是表示实施方式所涉及的摄像装置的平面构造的图。

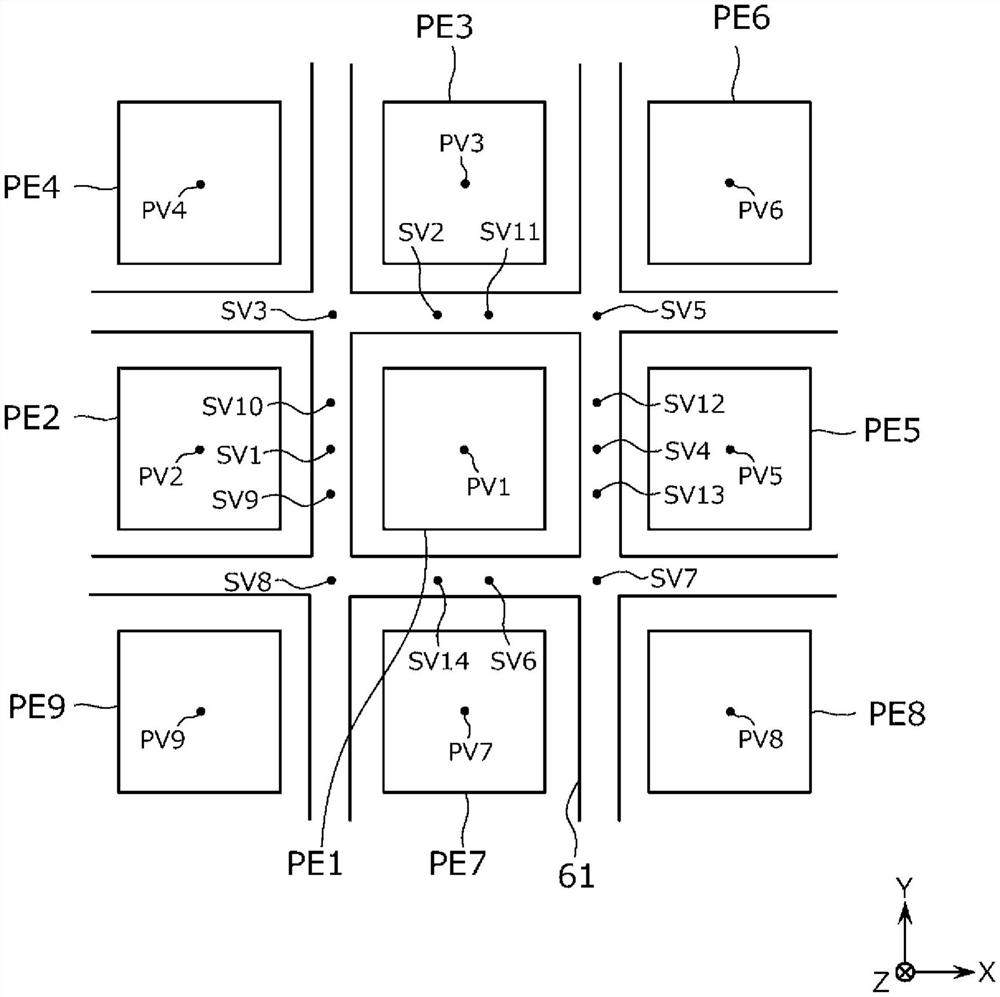

图9A是表示实施方式所涉及的摄像装置的平面构造的图。

图9B是图9A的部分扩大图。

图9C是与图9B的例子不同的例子所涉及的部分扩大图。

图9D是图9A的部分扩大图。

图9E是图9A的部分扩大图。

图10是相机系统的框图。

具体实施方式

(本公开所涉及的一个方式的概要)

本公开的第1方式所涉及的摄像装置具备:

光电转换层,将入射光转换为电荷;

第1像素电极,收集由所述光电转换层生成的电荷;

第2像素电极,收集由所述光电转换层生成的电荷,且在第1方向上与所述第1像素电极相邻;

屏蔽电极,与所述第1像素电极及所述第2像素电极电分离;以及

第1屏蔽过孔,从所述屏蔽电极延伸,且在平面视中位于所述第1像素电极与所述第2像素电极之间。

第1方式适于得到分辨率高的图像。

在本公开的第2方式中,例如,第1方式所涉及的摄像装置也可以还具备:

第3像素电极,收集由所述光电转换层生成的电荷,且在与所述第1方向不同的第2方向上与所述第1像素电极相邻;以及

第2屏蔽过孔,从所述屏蔽电极延伸,且在所述平面视中位于所述第1像素电极与所述第3像素电极之间。

第2方式适于得到分辨率高的图像。

在本公开的第3方式中,例如,第1方式所涉及的摄像装置也可以还具备:

第3像素电极,收集由所述光电转换层生成的电荷,且在与所述第1方向不同的第2方向上与所述第1像素电极相邻;

第4像素电极,收集由所述光电转换层生成的电荷,且在所述第2方向上与所述第2像素电极相邻,在所述第1方向上与所述第3像素电极相邻;以及

第3屏蔽过孔,从所述屏蔽电极延伸,且在所述平面视中位于所述第1像素电极与所述第4像素电极之间。

第3方式适于得到分辨率高的图像。

在本公开的第4方式中,例如,第2方式所涉及的摄像装置也可以还具备:

第4像素电极,收集由所述光电转换层生成的电荷,且在所述第2方向上与所述第2像素电极相邻,在所述第1方向上与所述第3像素电极相邻;以及

第3屏蔽过孔,从所述屏蔽电极延伸,且在所述平面视中位于所述第1像素电极与所述第4像素电极之间。

第4方式适于得到分辨率高的图像。

在本公开的第5方式中,例如,第1至第4方式中任1个所涉及的摄像装置也可以还具备:

第1像素过孔,从所述第1像素电极延伸;以及

第2像素过孔,从所述第2像素电极延伸。

第5方式的第1像素过孔能够将第1像素电极与其他要素电连接。第2像素过孔能够将第2像素电极与其他要素电连接。

在本公开的第6方式中,例如,在第5方式所涉及的摄像装置中,

在所述平面视中,所述第1屏蔽过孔也可以位于所述第1像素过孔与所述第2像素过孔之间。

第6方式适于得到分辨率高的图像。

在本公开的第7方式中,例如,第1至第6方式中任1个所涉及的摄像装置也可以还具备:

第1布线层,

所述第1屏蔽过孔也可以从所述屏蔽电极延伸到所述第1布线层。

第7方式适于得到分辨率高的图像。

在本公开的第8方式中,例如,第1至第7方式中任1个所涉及的摄像装置也可以还具备:

绝缘部,位于所述屏蔽电极与所述光电转换层之间。

第8方式适于抑制由于屏蔽电极引起的摄像装置的灵敏度的降低,并且通过屏蔽电极得到分辨率高的图像。

在本公开的第9方式中,例如,在第8方式所涉及的摄像装置中,

在所述平面视中,所述绝缘部也可以包含与所述屏蔽电极不重合的部分。

第9方式适于得到分辨率高的图像。

本公开的第10方式所涉及的摄像装置具备:

光电转换层,将入射光转换为电荷;

第1像素电极,收集由所述光电转换层生成的电荷;

屏蔽电极,与所述第1像素电极电分离;以及

绝缘部,位于所述屏蔽电极与所述光电转换层之间,

在平面视中,所述绝缘部包含与所述屏蔽电极不重合的部分。

第10方式适于抑制由于屏蔽电极引起的摄像装置的灵敏度的降低,并且通过屏蔽电极得到分辨率高的图像。

在本公开的第11方式中,例如,在第9方式或者第10方式所涉及的摄像装置中,

在所述平面视中,所述绝缘部也可以与所述第1像素电极相离。

第11方式适于通过第1像素电极捕获信号电荷,得到分辨率高的图像。

在本公开的第12方式中,例如,在第8至第11方式中任1个所涉及的摄像装置中,

所述绝缘部也可以具有膜形状,

所述膜形状的厚度也可以是10nm以上。

第12方式适于抑制由于屏蔽电极引起的摄像装置的灵敏度的降低。

在本公开的第13方式中,例如,在第1至第12方式中任1个所涉及的摄像装置中,

所述第1像素电极所具有的面与所述屏蔽电极所具有的面也可以处于同一平面上。

第13方式的摄像装置易于制造。

在本公开的第14方式中,例如,第1至第13方式中任1个所涉及的摄像装置也可以是彩色的图像传感器。

在彩色的图像传感器中,第1方式的技术能够有助于抑制混色。

本公开的第15方式所涉及的摄像装置具备:

光电转换层,将入射光转换为电荷;

第1像素电极,收集由所述光电转换层生成的电荷;

屏蔽电极,与所述第1像素电极电分离;以及

绝缘部,位于所述屏蔽电极与所述光电转换层之间。

在本说明书中,有时使用“过孔(via)”这样的用语。在本说明书中,将导通孔(viahole)及其内部的导体统称为“过孔”。

在本说明书中,有时使用“屏蔽过孔”及“像素过孔”这样的用语。在以下所示的例示性的实施方式中,屏蔽过孔从屏蔽电极延伸。像素过孔从像素电极延伸。屏蔽过孔及像素过孔这样的用语的区分使用是为了说明方便,其目的并不在于限定性地解释过孔的特征。

在本说明书中,有时使用第1、第2、第3……这样的序数词。在对某要素附加序数词的情况下,不必须存在顺序更小的同种的要素。能够根据需要变更序数词的编号。

以下说明的实施方式均表示概括性或者具体性的例子。以下的实施方式中表示的数值、形状、材料、构成要素、构成要素的配置及连接方式、步骤、步骤的顺序等为一例,意图不在于限定本公开。本说明书中说明的各种方式只要不产生矛盾则能够相互组合。此外,关于以下的实施方式中的结构要素之中表示最上位概念的独立权利要求中没有记载的结构要素,作为任意的结构要素而被说明。在以下的说明中,实质上具有相同的功能的构成要素由共通的参照标记表示,关于重复的说明有时省略或者简化。

概括性或者具体性的方式也可以由元件、设备、装置、系统、集成电路、方法或者计算机程序实现。另外,概括性或者具体性的方式也可以通过元件、设备、装置、系统、集成电路、方法及计算机程序的任意的组合实现。所公开的实施方式的追加性的效果及优点根据说明书及附图而明确。效果以及/或者优点通过说明书及附图中公开的各种实施方式或者特征被分别提供,为了得到其1个以上并不是全部都需要。

附图所示的各种要素不过是为了理解本公开而示意性地表示,尺寸比及外观等可以与实物不同。

本公开的一个方式所涉及的摄像装置在上层具有将光转换为电信号即进行光电转换的光电转换层,在下层具有包含将光电转换部中得到的电信号向外部取出的硅基的CMOS(Complementary Metal Oxide Semiconductor:互补金属氧化物半导体)电路的信号处理电路。像这样,在本公开的一个方式所涉及的摄像装置中,光电转换部与信号处理电路层叠,因此能够对它们独立地进行设计。

[实施方式]

在图1及图2中,表示实施方式所涉及的摄像装置100的截面图。

摄像装置100具备半导体基板1和像素部30。像素部30被设置在半导体基板1上。

像素部30包含多个像素电极3、对置电极5和光电转换层4。光电转换层4被配置在像素电极3与对置电极5之间。光电转换层4具有膜形状。

像素部30包含检测电路12。检测电路12的一部分被设置在半导体基板1内。检测电路12对像素电极3的电位进行检测。

像素部30包含绝缘层2。绝缘层2被配置在光电转换层4与半导体基板1之间。

在像素部30中,以跨半导体基板1及绝缘层2的界面的方式构成了检测电路12。具体而言,构成了与多个像素20分别对应的检测电路12。

以下,为了说明方便,有时使用X轴、Y轴及Z轴这样的用语。这些轴是相互正交的轴。另外,为了说明方便,有时将Z轴方向的正侧称为上。有时将Z轴方向的正侧的主面称为上表面。在该例中,上表面是与光的入射侧近的一侧的面。下表面是离光的入射侧远的一侧的面。在该例中,上下方向是与半导体基板1的表面垂直的方向。

在绝缘层2的上表面形成有像素电极3。在像素电极3上,连接着像素过孔13。像素过孔13从像素电极3延伸到第1布线层14。第1布线层14是多个布线层之中的与像素电极3最近的层。像素过孔13将像素电极3、布线层以及与像素电极3对应的检测电路12电连接。

多个像素20各自包含光电转换部11。光电转换部11包含像素电极3、对置电极5和光电转换层4。如上所述,光电转换层4被配置在像素电极3与对置电极5之间。

光电转换层4将入射光转换为电荷。

像素电极3捕集由光电转换层4生成的电荷。

像素电极3的材料的一例是氮化钛(TiN)等金属化合物。像素电极3的材料的其他例是铜(Cu)、钨(W)、钛(Ti)、钽(Ta)、铝(Al)等金属。像素电极3的材料也可以是从这些金属中选择至少2种而形成的化合物或者合金。像素电极3也可以包含从这些金属中选择至少2种而形成的层叠构造。层叠构造例如是TiN/Ti构造。TiN/Ti构造是氮化钛的层与钛的层接合而成的层叠构造。

在一个具体例中,多个像素电极3各自的膜厚是均一的。多个像素电极3各自的上表面是平坦的。

如图1的截面图所示,多个像素电极3位于光电转换层4及半导体基板1之间。

如图3的平面图所示,多个像素电极3以在X轴方向及Y轴方向上扩展的2维方向排列。多个像素电极3被配置在绝缘层2的上表面。

在一个具体例中,多个像素电极3被配置为矩阵状。在此,多个要素被配置为矩阵状的表现,意味着各要素的中心位于格子的交点上。多个像素电极3相互具有一定的间隔。

像素电极3与像素20的配置对应地配置。在一例中,多个像素20被配置为矩阵状。多个像素电极3与多个像素20的配置相应地配置为矩阵状。

再次参照图1。如上所述,在摄像装置100中,构成了与多个像素20中的各个多个像素20对应的检测电路12。检测电路12对由对应的像素电极3捕集的信号电荷进行检测,并输出与电荷相应的信号电压。

检测电路12例如包含MOS(Metal Oxide Semiconductor:金属氧化物半导体)电路、TFT(Thin Film Transistor:薄膜晶体管)电路等。检测电路12例如包含栅极与像素电极3电连接的放大晶体管,放大晶体管输出与信号电荷的量相应的信号电压。检测电路12也可以被在绝缘层2的内部等设置的遮光层遮光。省略遮光层的图示。

像素过孔13将各像素20的像素电极3、布线层以及与像素电极3对应的检测电路12电连接。

像素过孔13的材料的例子是铜(Cu)、钨(W)、钴(Co)等导电性材料。像素过孔13被埋入至绝缘层2。

绝缘层2被形成在半导体基板1上。绝缘层2包含多个构成层2a、2b、2c、2d及2e。

半导体基板1例如由硅(Si)等构成。多个构成层2a、2b、2c、2d及2e例如由二氧化硅(SiO

在各构成层2a、2b、2c、2d及2e中埋入了布线层。布线层具有布线。布线层与布线层被过孔连接。因此,虽然在布线层与布线层之间设置有绝缘层2的绝缘体,但布线层与布线层被过孔电连接。此外,绝缘层2内的构成层的层数能够任意设定,不限定于图1所示的5层的构成层2a、2b、2c、2d及2e的例子。关于布线层的层数也是同样的。

在构成层2e配置有像素电极3。在构成层2e及像素电极3的上表面层叠了光电转换层4。在光电转换层4的上表面,对置电极5、缓冲层6及密封层7按照对置电极5、缓冲层6及密封层7的顺序层叠。在密封层7的上表面,配置有与各像素20对应的透射波段的滤色器8。在滤色器8的上表面配置有平坦化层9。在平坦化层9的上表面配置有微透镜10。此外,在相邻的像素电极3的间隙中插入设置了绝缘层2的构成层。

在该例中,摄像装置100是彩色的图像传感器。但是,也能够省略滤色器8。也就是说,摄像装置100也可以是黑白的图像传感器。

光电转换层4由与接受的光的强度相应地产生电荷的光电转换材料构成。光电转换材料例如是有机半导体材料,包含p型有机半导体及n型有机半导体中的至少一方。在一个具体例中,光电转换层4在像素区域30中膜厚是均一的。在别的具体例中,光电转换层4在像素区域30中具有膜厚相互不同的2个以上的部分。

对置电极5与像素电极3对置。具体而言,对置电极5在像素部30内隔着光电转换层4与多个像素电极3及后述的屏蔽电极61对置。从光电转换层4观察,对置电极5配置在摄像装置100的供光入射的一侧。对置电极5也可以为了使光向光电转换层4入射而具有透光性。作为对置电极5的材料,例示出ITO(Indium Tin Oxide:氧化铟锡)或者IZO(Indium ZincOxide:氧化铟锌)等透明氧化物导电材料。

“第1要素与第2要素隔着第3要素对置”这样的表现,不应该被限定解释为仅指第1要素及第2要素与第3要素相接的方式。例如,“对置电极5与像素电极3及屏蔽电极61隔着光电转换层4对置”这样的表现,包含后述的绝缘部62介于屏蔽电极61与光电转换层4之间且通过其介于而阻止了屏蔽电极61与光电转换层4的接触的方式。

接下来,关于摄像机制进行说明。

从上方入射至摄像装置100的光经过密封层7、缓冲层6及对置电极5,向光电转换层4入射。光电转换层4在被像素电极3和对置电极5施加了适当的偏置电压的状态下,对入射的光进行光电转换,生成电荷。偏置电压是对置电极5与像素电极3之间的电位差。

如上述那样由光电转换层4生成的电荷从像素电极3经由像素过孔13被转送至检测电路12中的积蓄区域,并暂时被积蓄。然后,电荷通过检测电路12中的晶体管元件等的开关动作,适时地作为信号向检测电路12的外部输出。

(屏蔽电极)

在上述的说明所涉及的层叠型的摄像装置100中,光电转换层4被配置在像素电极3与对置电极5之间。如图3所示,在像素电极3与像素电极3之间的区域60中,配置有屏蔽电极61。具体而言,在区域60中,配置有绝缘层2及屏蔽电极61。此外,在图3中,省略了绝缘层2的图示。在图3的例子中,在平面视中,区域60具有格子形状。平面视例如指的是沿着与半导体基板1的表面垂直的方向观察。

假设不存在屏蔽电极61。在该情况下,在平面视中光电转换层4之中的与区域60重合的部分,相比于与像素电极3重合的部分,被施加的电场强度较小。因此,在光电转换层4之中的与区域60重合的部分中,信号电荷从像素电极3受到的电场强度较小。

在上述重合的部分中,也可能存在信号电荷。该信号电荷有可能不是到达本来应该到达的像素电极3,而是到达与其相邻的像素电极3。如果到达了相邻的像素电极3的信号电荷被检测为相邻的像素的像素信号,则分辨率降低。在抑制分辨率的降低的观点上,能够使用屏蔽电极。在摄像装置100是彩色的图像传感器的情况下,通过使用屏蔽电极,能够抑制混色。

以下,关于屏蔽电极,参照附图进行说明。

如图1的截面图所示,屏蔽电极61被配置在光电转换层4及半导体基板1之间。如图3所示,屏蔽电极61与多个像素电极3电分离。

在该例中,在像素电极3与像素电极3之间的区域60中配置有屏蔽电极61。通过配置屏蔽电极61,能够对相互相邻的2个像素电极3之间的区域施加电压。由此,光电转换层4中的在平面视中与区域60重合的部分所产生的信号电荷65被收集至屏蔽电极61。由此,能够抑制本来应该到达某像素电极3的信号电荷65到达相邻的像素电极3。也就是说,能够抑制相邻像素间的信号电荷的混合。由此,能够得到分辨率高的图像。在摄像装置100是彩色的图像传感器的情况下,能够抑制相邻像素间的混色。

作为屏蔽电极61的材料,例示出铜(Cu)、钨(W)、钛(Ti)、钽(Ta)、铝(Al)等金属。屏蔽电极61的材料也可以是从这些金属中选择至少2种而形成的化合物或者合金。屏蔽电极61也可以包含从这些金属中选择至少2种而形成的层叠构造。层叠构造例如是TiN/Ti构造。

在一个具体例中,屏蔽电极61各自的膜厚是均一的。屏蔽电极61各自中的靠光电转换层4一侧的面是平坦的。

在图1及图2所示的例子中,屏蔽电极61所具有的面与像素电极3所具有的面处于同一平面上。具体而言,屏蔽电极61中的与半导体基板1对置的面和像素电极3中的与半导体基板1对置的面处于同一平面上。具有这样的构成的摄像装置易于制造。但是,屏蔽电极61所具有的面与像素电极3所具有的面也可以不处于同一平面上。具体而言,屏蔽电极61中的与半导体基板1对置的面和像素电极3中的与半导体基板1对置的面也可以不处于同一平面上。

屏蔽电极61的材料与像素电极3的材料也可以是相同的。在该情况下,不需要分别的制造工序就能够形成屏蔽电极61和像素电极3。如果像这样,则能够在同一制造工序中而且以同一掩膜形成屏蔽电极61及像素电极3。因此,不需要考虑对位偏差。在此,对位偏差指的是屏蔽电极61及像素电极3的相对性的位置关系从恰当的范围脱离。

像素电极3与屏蔽电极61之间的相离幅度71例如是0.1μm以上且1μm以下。

(屏蔽电极61与光电转换层4之间的绝缘部)

在如图1及图2所示配置了屏蔽电极61的情况下,由光电转换层4产生的信号电荷65的一部分被收集至屏蔽电极61。如果由于该收集而导致能够由像素电极3捕获的信号电荷变少,则有时摄像装置的灵敏度降低。在抑制摄像装置的灵敏度的降低的观点上,也可以在屏蔽电极61与光电转换层4之间设置绝缘部。以下,关于如此设置了绝缘部的构成例,参照图4A、图4B、图4C、图4D、图4E、图5A、图5B及图6进行说明。

在图4A及图4B的例子中,在屏蔽电极61与光电转换层4之间设置了绝缘部62。绝缘部62是绝缘体。通过设置这样的绝缘部62,能够保持相互相邻的2个像素电极3之间的区域与对置电极5之间施加了电场的状态,并且抑制信号电荷向屏蔽电极61流入从而抑制摄像装置的灵敏度的降低。因此,该例适于抑制由于屏蔽电极61引起的摄像装置的灵敏度的降低,且通过屏蔽电极61得到分辨率高的图像。

在图4A及图4B的例子中,绝缘部62覆盖屏蔽电极61。绝缘部62具体而言覆盖屏蔽电极61中的靠光电转换层4一侧的整面。

在图4A及图4B的例子中,绝缘部62与屏蔽电极61相接。绝缘部62具体而言与屏蔽电极61中的靠光电转换层4一侧的整面相接。通过绝缘部62,阻止了屏蔽电极61与光电转换层4的接触。

如图4C所示,在平面视中,绝缘部62也可以包含从屏蔽电极61伸出且与屏蔽电极61不重合的部分。如果像这样,则在平面视中,能够使绝缘部62的轮廓的一部分或者全部成为屏蔽电极61的轮廓的外侧。如果像这样,则能够抑制从屏蔽电极61的端部朝向光电转换层4的斜上方向的电场。这例如在确保屏蔽电极61与像素电极3之间的绝缘性的观点上是有利的。另外,在平面视中绝缘部62从屏蔽电极61伸出,在抑制信号电荷从侧方绕过绝缘部62而向屏蔽电极61流入的观点上是有利的。因此,图4C的方式适于得到分辨率高的图像。

此外,在平面视中绝缘部62从屏蔽电极61伸出,意味着在平面视中绝缘部62包含存在于比屏蔽电极61的轮廓更靠外侧的部分。也可以说在平面视中,屏蔽电极61包含存在于比绝缘部62的轮廓更靠内侧的部分。更详细地说明,在平面视中绝缘部62从屏蔽电极61伸出是如下概念:不仅包含在平面视中绝缘部62的轮廓全部存在于比屏蔽电极61的轮廓更靠外侧的情况,而且包含在平面视中绝缘部62的轮廓的仅一部分存在于比屏蔽电极61的轮廓更靠外侧的情况。在平面视中,既可以是绝缘部62的轮廓全部存在于比屏蔽电极61的轮廓更靠外侧,也可以是绝缘部62的轮廓的仅一部分存在于比屏蔽电极61的轮廓更靠外侧。

在一个具体例中,在平面视中,绝缘部62与各像素电极3相离。如果像这样,则像素电极3对信号电荷的捕获不容易被绝缘部62妨碍。这适于得到分辨率高的图像。

绝缘部62也可以覆盖像素电极3的一部分。

在图4A及图4B的例子中,像素电极3与光电转换层4被电连接。具体而言,像素电极3与光电转换层4相接。但是,也可以在像素电极3与光电转换层4之间设置阻碍层。阻碍层使光电转换层4中通过光电转换而产生的电荷对之中的信号电荷通过,而阻止不是信号电荷的电荷从像素电极3注入。由此,能够有效地将信号电荷向像素电极3输送。阻碍层示出选择性的电荷输送性,因此不相当于绝缘体。

绝缘部62的材料的例子是二氧化硅(SiO

绝缘部62的材料既可以与绝缘层2的材料是相同的,也可以与绝缘层2的材料不同。

典型地,绝缘部62具有膜形状。在该例中,膜形状的厚度方向和与半导体基板1的表面垂直的方向一致。

膜形状的厚度例如是10nm以上。通过使膜形状的厚度大到该程度,能够抑制信号电荷通过隧道效应穿通绝缘部62。因此,能够抑制信号电荷被捕集至屏蔽电极61。因此,将膜形状的厚度设为10nm以上,适于抑制由于屏蔽电极61引起的摄像装置的灵敏度的降低。膜形状的厚度也可以是20nm以上。

膜形状的厚度例如是500nm以下。通过使膜形状的厚度小到该程度,在对屏蔽电极61施加了电压的情况下,易于将信号电荷收集至屏蔽电极61周边。如果在像素电极3间产生的信号电荷被收集至屏蔽电极61附近,则能够抑制信号电荷被期望的像素电极3以外捕集。因此,将膜形状的厚度设为500nm以下,适于通过屏蔽电极61得到分辨率高的图像。膜形状的厚度也可以是300nm以下。

如果将膜形状的厚度调整到恰当的范围,则被屏蔽电极61捕集的信号电荷降低到实质上能够忽略的水平,并且能够将在像素电极间产生的信号电荷收集至屏蔽电极61附近,因此易于抑制信号电荷被期望的像素电极3以外捕集。因此,易于抑制由于屏蔽电极61引起的摄像装置的灵敏度的降低,并且得到分辨率高的图像。

膜形状的厚度能够通过公知的方法确定。膜形状的厚度例如能够如下确定。首先,取得膜形状截面的电子显微镜像。接下来,使用该像,关于膜形状的任意多个测定点(例如5点)测定厚度。采用这多个测定点的厚度的平均值作为膜形状的厚度。

此外,在后述的图5A及图5B的例子中适用上述的例示性的确定方法的情况下,侧面62c的部分被从测定点排除,而在上表面62a的部分设定测定点。

绝缘部62的形成方法不特别限定。

在一例中,绝缘部62如下形成。在屏蔽电极61(典型的是屏蔽电极61的整个上表面)形成绝缘部62的材料的层。接下来,去除该层的一部分。这样,得到绝缘部62。如果像这样,则也能够得到膜形状的绝缘部62。

绝缘部62的材料的层例如能够通过化学气相沉积(CVD)形成。绝缘部62的材料的层的一部分例如能够通过光刻、蚀刻等去除。

在平面视中,绝缘部62也可以覆盖屏蔽电极61的整个上表面、像素电极3与屏蔽电极61之间的绝缘层2的整个上表面、以及像素电极3的一部分。如果像这样,则能够使在绝缘部62的端部形成的阶差的位置成为像素电极3上。关于通过使得阶差的位置成为像素电极3上而得到的优点,参照图4D及图4E进行说明。图4D及图4E是表示绝缘层2及光电转换层4的制造方法的示意图。

在图4D的部分(a)及图4E的部分(a)中,像素电极3及屏蔽电极61被绝缘部62的材料的层62x覆盖。层62x的一部分被掩膜81覆盖。层62x之中的未被掩膜81覆盖的部分通过蚀刻被去除。

此外,在图4D的部分(a)及图4E的部分(a)中,省略了绝缘层2的图示。在与图4D及图4E相关的说明中,设为在像素电极3与屏蔽电极61之间的位置存在绝缘层2。另外,在与图4D及图4E相关的说明中,在蚀刻的实施前,位于上述位置的绝缘层2的上表面设为与像素电极3的上表面及屏蔽电极61的上表面处于同一个面。

在图4D的部分(a)中,掩膜81覆盖屏蔽电极61的整个上表面。但是,掩膜81不覆盖像素电极3与屏蔽电极61之间的绝缘层2的上表面。另外,掩膜81不覆盖像素电极3的上表面。另一方面,在图4E的部分(a)中,掩膜81覆盖屏蔽电极61的整个上表面、以及像素电极3与屏蔽电极61之间的绝缘层2的整个上表面。在图4E的部分(a)中,掩膜81还部分地覆盖像素电极3的上表面。

通过使用图4D的部分(a)的掩膜81进行蚀刻,能够得到仅覆盖屏蔽电极61的整个上表面的绝缘部62。另一方面,通过使用图4E的部分(a)的掩膜81进行蚀刻,能够得到将屏蔽电极61的整个上表面、像素电极3与屏蔽电极61之间的绝缘层2的整个上表面、以及像素电极3的上表面的一部分覆盖的绝缘部62。

图4D的部分(b)及图4E的部分(b)表现了通过蚀刻将层62x之中的未被掩膜81覆盖的部分去除后的情形。通过该去除,层62x被加工为绝缘部62。

在现实中,难以通过蚀刻仅削减层62x。如果像图4D的部分(a)那样配置掩膜81,则未被掩膜81覆盖的像素电极3及绝缘层2也以某种程度被削减。像素电极3与绝缘层2相比,蚀刻速率不同,被削减的程度不同。因此,如图4D的部分(b)的由点线84包围的区域内所示,像素电极3与绝缘层2相比,上表面的高度产生差异。另外,如由点线85包围的区域内所示,绝缘部62与绝缘层2相比,上表面的高度产生差异。该上表面的高度之差在被掩膜81覆盖的部分与未被覆盖的部分的边界处产生。图4D的部分(b)的一点划线82表现了像素电极3及绝缘层2的上表面的位置。

通过掩膜81覆盖屏蔽电极61的整个上表面并部分地覆盖像素电极3与屏蔽电极61之间的绝缘层2的上表面的情况也是同样的。在该情况下,像素电极3与绝缘层2相比,产生由于蚀刻速率的差异引起的上表面的高度之差。另外,在绝缘层2上,绝缘部62所位于的部分与未位于的部分相比,产生上表面的高度之差。该上表面的高度之差在绝缘层2上的绝缘层62x被掩膜81覆盖的部分与未被覆盖的部分的边界处产生。

相对于此,如果像图4E的部分(a)那样配置掩膜81,则如图4E的部分(b)的点线86内所示,在像素电极3上,上表面的高度产生差异。该差异在被掩膜81覆盖的部分与未被覆盖的部分的边界处产生。但是,绝缘层2被绝缘部62完全覆盖,因此在绝缘层2上,上表面的高度不产生差异。因此,与图4D的情况相比,能够减少通过使用掩膜81的蚀刻而形成的上表面上的阶差的数量。

图4D的部分(c)及图4E的部分(c)表现了在通过蚀刻形成的上表面上形成了光电转换层4的情形。如果在通过蚀刻形成的上表面上形成了光电转换层4,则该上表面的形状也被反映于光电转换层4的上表面的形状。图4D及图4E的部分(c)的二点划线83表现了光电转换层4的上表面的位置。

根据以上的说明能够理解,图4E的方式与图4D的方式相比,在使光电转换层4的形状平坦的观点上是有利的。由此,绝缘部62将屏蔽电极61的整个上表面、像素电极3与屏蔽电极61之间的绝缘层2的整个上表面、以及像素电极3的上表面的一部分覆盖的构成可以说在使光电转换层4平坦的观点上是有利的。

在图4A、图4B及图4C所示的具体例中,绝缘部62具有膜形状。如图4B及图4C所示,膜形状具有上表面62a、下表面62b和侧面62c。侧面62c从下表面62b向上表面62a延伸。由上表面62a与侧面62c形成了角62d。在下表面62b与侧面62c之间,形成了角度θ。角度θ较大。具体而言,角度θ是大致90°。因此,角62d尖凸。

在图5A及图5B所示的别的具体例中,绝缘部62具有膜形状。在图5A及图5B的具体例中,与图4A、图4B及图4C的具体例相比,角度θ较小。如果像这样,则角62d的尖凸被缓和,在光电转换层4的形成时不容易在角62d处产生裂纹。由此,光电转换层4不容易在与绝缘部62的接触部中发生劣化。

使角度θ变小或者缓和角62d的尖凸,例如能够如下实现:通过等离子体中的离子将绝缘部的角削减的逆溅射效果、通过CMP(Chemical Mechanical Polishing:化学机械研磨)使绝缘部平坦时将角削减等。

在现实中,如图6所示,在光电转换层4中的在平面视中与绝缘部62重叠的位置处,可能形成突出部4p。在光电转换层4中,突出部4p与突出部4p的周围的部分相比,更向绝缘部62的膜形状的厚度方向突出。

突出部4p的突出幅度PW可能与绝缘部62的膜形状的厚度TH是相同的。但是,如图6所示,能够使突出幅度PW比厚度TH小。如果采用别的说法,能够使光电转换层4中的在平面视中与绝缘部62重叠的部分的厚度比该部分的周围的厚度薄。例如,通过针对光电转换层4实施热处理,能够减小突出幅度PW。此外,突出幅度PW比厚度TH小,是包含突出幅度PW为零的情况的概念。

根据上述的说明能够理解,能够设置绝缘部62,并且实现使得突出部4p的突出幅度PW小或者不存在突出部4p的光电转换层4。如果光电转换层4的上表面具有高的平坦性,则易于制造光电转换层4的上侧的层。

在图6的例子中,光电转换层4中的在平面视中与像素电极3重叠的部分的厚度与光电转换层4中的在平面视中与屏蔽电极61重叠的部分的厚度相比更大。这适于促进前者的部分中的光电转换来通过像素电极3捕获更多的信号电荷,并抑制后者的部分中的光电转换来抑制屏蔽电极61对信号电荷的捕获。

此外,光电转换层4中的突出部4p在绝缘部62是图4B所示的方式的情况下以及在是图4C所示的方式的情况下都可能形成。在这些情况下,都能够设为PW=TH或者PW<TH。在这些情况下,都能够实现不存在突出部4p的光电转换层4。在这些情况下,都能够使光电转换层4中的在平面视中与像素电极3重叠的部分的厚度与光电转换层4中的在平面视中与屏蔽电极61重叠的部分的厚度相比更大。

也能够采用图7所示的具体例。在图7的具体例中,绝缘部62具有膜形状。在该具体例中,从半导体基板1朝向光电转换层4,像素过孔13、像素电极3、过孔68和像素电极69按照像素过孔13、像素电极3、过孔68和像素电极69的顺序被连接。因此,它们被电连接。到达了像素电极69的信号电荷按照过孔68、像素电极3及像素过孔13的顺序流过。

在图7所示的具体例中,绝缘部62在平面视中包围像素电极69。绝缘部62的上表面与像素电极69的上表面处于同一个面。绝缘部62也存在于像素电极3与像素电极69之间。

在图7所示的具体例中,屏蔽电极61的上表面被绝缘部62覆盖。像素电极3的上表面也被绝缘部62覆盖。

如图7的具体例那样设置过孔68及像素电极69,在使光电转换层4的下表面平坦并且在屏蔽电极61与光电转换层4之间设置绝缘部62的观点上是有利的。因此,该构成在抑制光电转换层4中产生裂纹的观点上是有利的。特别是在绝缘部62厚的情况下,在绝缘部62上或者像素电极69上,可能产生由于绝缘部62引起的大的阶差。在该情况下,由于在不平坦的表面上形成光电转换层4,因此在光电转换层4容易产生裂纹。因此,在这种情况下通过使用图7的构成,能够发挥裂纹抑制效果。此外,在图7的具体例中,绝缘部62的膜形状的厚度,指的是绝缘部62之中的在平面视中与屏蔽电极61重合的部分的厚度。上述测定点在该部分中被设定。

在图7的例子中,在像素电极3与屏蔽电极61之间设置了绝缘体67。绝缘体67的材料与绝缘部62的材料既可以是相同的,也可以不同。绝缘体67可以是绝缘层2的绝缘体。此外,在图4B、图4C及图5B中,虽然省略了图示,但作为绝缘体的绝缘层2也位于像素电极3与屏蔽电极61之间。

(基于与屏蔽电极61连接的过孔的屏蔽构造)

在层叠型的摄像装置100中,设置了与光电转换层4不同的电荷的积蓄区域。积蓄区域被设置在检测电路12中的半导体基板1内的部分。由光电转换层4产生的电荷从像素电极3经由像素过孔13向积蓄区域输送。

在层叠型的摄像装置100中,在与某像素电极3连接的像素过孔13和与相邻于该像素电极3的像素电极3连接的像素过孔13之间,有时产生寄生电容。该寄生电容可能成为像素间的串扰的原因。

为了抑制由于寄生电容引起的串扰,考虑将过孔与屏蔽电极61连接,通过该过孔对像素过孔13间进行屏蔽。如果像这样,则能够减小像素过孔13间的寄生电容,因此能够抑制由于寄生电容引起的串扰。

如上所述,摄像装置100具备多个布线层。多个布线层被配置在屏蔽电极与半导体基板1之间。多个布线层在与半导体基板1的表面垂直的方向上处于相互不同的位置。第1布线层14是多个布线层之中的与像素电极3最近的层。与位于比第1布线层14更靠像素电极3一侧的区域相比,在位于比第1布线层14更靠半导体基板1一侧的区域中,更多地配置能够作为抑制串扰的屏蔽发挥功能的布线。因此,基于与屏蔽电极61连接的过孔的屏蔽效果易于在比第1布线层14更靠像素电极3一侧的区域中显现。另外,基于与屏蔽电极61连接的过孔的屏蔽效果易于在像素电极3与第1布线层14的间隔大的情况下显现。

在一例中,摄像装置100是彩色的图像传感器。在彩色的图像传感器的一例中,与RGB对应的像素相邻地配置。也就是说,与不同的颜色对应的像素相邻地配置。因此,如果产生了像素间的串扰,则产生混色。通过对彩色的图像传感器适用屏蔽构造,抑制了串扰,抑制了由于混色引起的画质降低。

以下,关于利用与屏蔽电极61连接的过孔的技术进行说明。以下,有时将从屏蔽电极61延伸的过孔称为屏蔽过孔。

在本实施方式中,根据图1至图7能够理解,在屏蔽电极61上连接着屏蔽过孔63、63C。屏蔽过孔63、63C从屏蔽电极61朝向半导体基板1延伸。具体而言,屏蔽过孔63、63C从屏蔽电极61延伸到第1布线层14。

在比第1布线层14更靠半导体基板1一侧,也可以存在与屏蔽电极61电连接的过孔。

在图3的例子中,在平面视中,各个像素电极3被屏蔽电极61中包含的框状部包围。与屏蔽电极61连接的屏蔽过孔63C被配置在上述框状部的四角。进而,屏蔽过孔63也被配置在四角与四角之间。此外,在图3中,针对包围位于图示中央的像素电极3的框状部的四角处的屏蔽过孔63C赋予标记63C。

也可以使屏蔽过孔63、63C的个数比图3的例子增加。在平面视中包围1个像素电极3的屏蔽过孔63、63C的数量越多,减小串扰的效果越大。也可以设置大量的屏蔽过孔63、63C,且使得相邻的屏蔽过孔63、63C相互相接。也能够将像这样设置的多个屏蔽过孔63、63C的集合称为线过孔。

如以上说明地,通过使屏蔽过孔63、63C与屏蔽电极61连接,并使屏蔽过孔63、63C朝向半导体基板1延伸,能够抑制像素20间的串扰。

在摄像装置100是彩色的图像传感器的情况下,通过如上述那样抑制串扰,能够抑制混色。

作为屏蔽过孔63、63C的材料,例示出铜(Cu)、钨(W)、钴(Co)等导电性材料。

屏蔽过孔63、63C能够通过向绝缘层2埋入而被形成。

也可以在与像素过孔13同一制造工序中形成多个屏蔽过孔63、63C。

也可以在屏蔽电极61与光电转换层4之间不设置绝缘部62,而设置基于与屏蔽电极61连接的屏蔽过孔的屏蔽构造。

以下,参照图8,关于基于屏蔽过孔的屏蔽进一步进行说明。

以下,有时对屏蔽过孔赋予序数词来进行说明。在图8中,作为屏蔽过孔63的第1屏蔽过孔的位置由点P1表现。作为屏蔽过孔63的第2屏蔽过孔的位置由点P2表现。作为屏蔽过孔63的第3屏蔽过孔的位置由点P3表现。作为屏蔽过孔63的第4屏蔽过孔的位置由点P4表现。作为屏蔽过孔63C的第5屏蔽过孔的位置由点P5表现。作为屏蔽过孔63C的第6屏蔽过孔的位置由点P6表现。作为屏蔽过孔63C的第7屏蔽过孔的位置由点P7表现。作为屏蔽过孔63C的第8屏蔽过孔的位置由点P8表现。作为屏蔽过孔63的第9屏蔽过孔的位置由点P9表现。作为屏蔽过孔63的第10屏蔽过孔的位置由点P10表现。作为屏蔽过孔63的第11屏蔽过孔的位置由点P11表现。作为屏蔽过孔63的第12屏蔽过孔的位置由点P12表现。作为屏蔽过孔63的第13屏蔽过孔的位置由点P13表现。作为屏蔽过孔63的第14屏蔽过孔的位置由点P14表现。

以下,有时使用第1部分X1、第2部分X2、第3部分X3、第4部分X4、第5部分X5、第6部分X6、第7部分X7及第8部分X8这样的用语。在图8中,针对这些部分分别附加阴影。此外,在图8中省略绝缘层2的图示。

以下,有时使用平面视这样的用语。平面视例如指的是沿着与半导体基板1的表面垂直的方向观察。

在图8的例子中,多个像素电极3包含第1像素电极3A、第1相邻像素电极3B1、第2相邻像素电极3B2、第3相邻像素电极3B3和第4相邻像素电极3B4。第1相邻像素电极3B1、第2相邻像素电极3B2、第3相邻像素电极3B3及第4相邻像素电极3B4与第1像素电极3A相邻。

另外,在图8的例子中,多个像素电极3包含第1特定像素电极3C1、第2特定像素电极3C2、第3特定像素电极3C3和第4特定像素电极3C4。第1特定像素电极3C1与第1相邻像素电极3B1及第2相邻像素电极3B2相邻。第2特定像素电极3C2与第2相邻像素电极3B2及第3相邻像素电极3B3相邻。第3特定像素电极3C3与第3相邻像素电极3B3及第4相邻像素电极3B4相邻。第4特定像素电极3C4与第4相邻像素电极3B4及第1相邻像素电极3B1相邻。

屏蔽电极61包含第1部分X1、第2部分X2、第3部分X3和第4部分X4。至少1个屏蔽过孔包含第1屏蔽过孔、第2屏蔽过孔、第3屏蔽过孔和第4屏蔽过孔。第1屏蔽过孔从第1部分X1朝向半导体基板1延伸。第2屏蔽过孔从第2部分X2朝向半导体基板1延伸。第3屏蔽过孔从第3部分X3朝向半导体基板1延伸。第4屏蔽过孔从第4部分X4朝向半导体基板1延伸。

在平面视中,第1像素电极3A是第1边S1、第2边S2、第3边S3和第4边S4按照第1边S1、第2边S2、第3边S3和第4边S4的顺序连接而成的四边形Q。在平面视中,第1部分X1位于第1边S1与第1相邻像素电极3B1之间。在平面视中,第2部分X2位于第2边S2与第2相邻像素电极3B2之间。在平面视中,第3部分X3位于第3边S3与第3相邻像素电极3B3之间。在平面视中,第4部分X4位于第4边S4与第4相邻像素电极3B4之间。

在图8的例子中,具体而言,在平面视中,第1边S1隔着第1部分X1与第1相邻像素电极3B1对置。在平面视中,第2边S2隔着第2部分X2与第2相邻像素电极3B2对置。在平面视中,第3边S3隔着第3部分X3与第3相邻像素电极3B3对置。在平面视中,第4边S4隔着第4部分X4与第4相邻像素电极3B4对置。

在图8的例子中,屏蔽电极61包含第5部分X5、第6部分X6、第7部分X7和第8部分X8。至少1个屏蔽过孔包含第5屏蔽过孔、第6屏蔽过孔、第7屏蔽过孔和第8屏蔽过孔。第5屏蔽过孔从第5部分X5朝向半导体基板1延伸。第6屏蔽过孔从第6部分X6朝向半导体基板1延伸。第7屏蔽过孔从第7部分X7朝向半导体基板1延伸。第8屏蔽过孔从第8部分X8朝向半导体基板1延伸。

在平面视中,多个像素电极3隔着包含多个交叉部的格子状区域60相互相离。在平面视中,屏蔽电极61位于格子状区域60。

在平面视中,四边形Q包含第1顶点V1、第2顶点V2、第3顶点V3和第4顶点V4。第1顶点V1是第1边S1与第2边S2相接的顶点。第2顶点V2是第2边S2与第3边S3相接的顶点。第3顶点V3是第3边S3与第4边S4相接的顶点。第4顶点V4是第4边S4与第1边S1相接的顶点。

在平面视中,多个交叉部包含第1交叉部Y1、第2交叉部Y2、第3交叉部Y3和第4交叉部Y4。在平面视中,第1交叉部Y1在多个交叉部中与第1顶点V1最近。在平面视中,第2交叉部Y2在多个交叉部中与第2顶点V2最近。第3交叉部Y3在多个交叉部中与第3顶点V3最近。第4交叉部Y4在多个交叉部中与第4顶点V4最近。

在平面视中,第5部分X5位于第1交叉部Y1。在平面视中,第6部分X6位于第2交叉部Y2。在平面视中,第7部分X7位于第3交叉部Y3。在平面视中,第8部分X8位于第4交叉部Y4。

进而,在图8的例子中,上述至少1个屏蔽过孔包含第9屏蔽过孔、第10屏蔽过孔、第11屏蔽过孔、第12屏蔽过孔、第13屏蔽过孔和第14屏蔽过孔。第9屏蔽过孔及第10屏蔽过孔从第1部分X1朝向半导体基板1延伸。第11屏蔽过孔从第2部分X2朝向半导体基板1延伸。第12屏蔽过孔及第13屏蔽过孔从第3部分X3朝向半导体基板1延伸。第14屏蔽过孔从第4部分X4朝向半导体基板1延伸。

与屏蔽电极61连接的过孔有助于得到分辨率高的图像。具体而言,如果像这样设置第1屏蔽过孔至第14屏蔽过孔,则在平面视中包围1个像素电极3的屏蔽过孔63、63C的数量多,减小串扰的效果变大。另外,还能够减少在倾斜方向上排列的像素间的串扰。因此,易于得到分辨率更高的图像。此外,倾斜方向在图8的例子中是在平面视中四边形Q的对角线延伸的方向。

也可以省略上述的说明所涉及的与屏蔽电极61连接的屏蔽过孔63、63C的一部分。也可以追加从屏蔽电极61朝向半导体基板1延伸的屏蔽过孔63、63C。

在图8的例子中,摄像装置100包含像素过孔13。像素过孔13与第1像素电极3A连接。像素过孔13从第1像素电极3A朝向半导体基板1延伸。在图8中,像素过孔13的位置由点PA表现。此外,虽然省略了图示,但在图8的例子中,不仅从图示中央的像素电极3A,而且从其他8个像素电极3B1至3B4及3C1至3C4,也有像素过孔13朝向半导体基板1延伸。

在这样的摄像装置100中,由于与第1像素电极3A连接的像素过孔13和与相邻像素电极连接的像素过孔之间的寄生电容引起的噪声向与第1像素电极3A连接的像素过孔13中流动的信号电荷的重叠,能够被与屏蔽电极61连接的屏蔽过孔63、63C抑制。因此,这样的摄像装置100适于得到分辨率高的图像。

在一个具体例中,在平面视中,与第1像素电极3A连接的像素过孔13被第1屏蔽过孔、第2屏蔽过孔、第3屏蔽过孔、第4屏蔽过孔和第5屏蔽过孔包围。

具体而言,在平面视中,与第1像素电极3A连接的像素过孔13被第1屏蔽过孔、第2屏蔽过孔、第3屏蔽过孔、第4屏蔽过孔、第5屏蔽过孔、第6屏蔽过孔、第7屏蔽过孔和第8屏蔽过孔包围。

更具体而言,在平面视中,与第1像素电极3A连接的像素过孔13被第1屏蔽过孔、第2屏蔽过孔、第3屏蔽过孔、第4屏蔽过孔、第5屏蔽过孔、第6屏蔽过孔、第7屏蔽过孔、第8屏蔽过孔、第9屏蔽过孔、第10屏蔽过孔、第11屏蔽过孔、第12屏蔽过孔、第13屏蔽过孔和第14屏蔽过孔包围。

在图8的例子中,上述至少1个屏蔽过孔从屏蔽电极61延伸到第1布线层14。像这样适于得到分辨率高的图像。

在图8的例子中,四边形Q是长方形。四边形Q也可以是正方形。

在图8的例子中,在平面视中,第1相邻像素电极3B1、第2相邻像素电极3B2、第3相邻像素电极3B3及第4相邻像素电极3B4是四边形。典型地,在平面视中,第1相邻像素电极3B1、第2相邻像素电极3B2、第3相邻像素电极3B3及第4相邻像素电极3B4具有与四边形Q相同的形状及尺寸。

在图8的例子中,在平面视中,第1相邻像素电极3B1及第3相邻像素电极3B3与第1像素电极3A在第2边S2及第4边S4延伸的方向上相邻。第2相邻像素电极3B2及第4相邻像素电极3B4与第1像素电极3A在第1边S1及第3边S3延伸的方向上相邻。

在图8的例子中,作为单一的导电体的屏蔽电极61对多个像素电极3进行屏蔽。具体而言,单一的导电体在平面视中具有格子形状。但是,也能够采用别的方式。例如,也可以是屏蔽电极61被电分离为多个部分,多个部分分别屏蔽与各自对应的像素电极3。

以下,参照图9A至图9E,说明摄像装置的特征。以下的说明有时与上述的说明重复。也可以将以下的说明内容与上述的说明内容组合。也能够将以下的说明中的用语与上述的说明中的用语相互替换解读。此外,在图9A至图9E中,省略了绝缘层2的图示。

图9A的第1屏蔽过孔SV1对应于图8的点P1处的第1屏蔽过孔。图9A的第2屏蔽过孔SV2对应于图8的点P2处的第2屏蔽过孔。图9A的第3屏蔽过孔SV3对应于图8的点P5处的第5屏蔽过孔。图9A的第4屏蔽过孔SV4对应于图8的点P3处的第3屏蔽过孔。图9A的第5屏蔽过孔SV5对应于图8的点P6处的第6屏蔽过孔。图9A的第6屏蔽过孔SV6对应于图8的点P4处的第4屏蔽过孔。图9A的第7屏蔽过孔SV7对应于图8的点P7处的第7屏蔽过孔。图9A的第8屏蔽过孔SV8对应于图8的点P8处的第8屏蔽过孔。图9A的第9屏蔽过孔SV9对应于图8的点P9处的第9屏蔽过孔。图9A的第10屏蔽过孔SV10对应于图8的点P10处的第10屏蔽过孔。图9A的第11屏蔽过孔SV11对应于图8的点P11处的第11屏蔽过孔。图9A的第12屏蔽过孔SV12对应于图8的点P12处的第12屏蔽过孔。图9A的第13屏蔽过孔SV13对应于图8的点P13处的第13屏蔽过孔。图9A的第14屏蔽过孔SV14对应于图8的点P14处的第14屏蔽过孔。

屏蔽过孔SV1至SV14从屏蔽电极61延伸。具体而言,屏蔽过孔SV1至SV14从屏蔽电极61向从光的入射面远离的方向延伸。屏蔽过孔SV1至SV14也可以说从屏蔽电极61向下方延伸。在该例中,屏蔽过孔SV1至SV14延伸到第1布线层14。

图9A的第1像素电极PE1对应于图8的第1像素电极3A。图9A的第2像素电极PE2对应于图8的第1相邻像素电极3B1。图9A的第3像素电极PE3对应于图8的第2相邻像素电极3B2。图9A的第4像素电极PE4对应于图8的第1特定像素电极3C1。图9A的第5像素电极PE5对应于图8的第3相邻像素电极3B3。图9A的第6像素电极PE6对应于图8的第2特定像素电极3C2。图9A的第7像素电极PE7对应于图8的第4相邻像素电极3B4。图9A的第8像素电极PE8对应于图8的第3特定像素电极3C3。图9A的第9像素电极PE9对应于图8的第4特定像素电极3C4。第1像素电极PE1至第9像素电极PE9收集电荷。第1像素电极PE1至第9像素电极PE9与屏蔽电极61电分离。

第1像素电极PE1与第2像素电极PE2、第3像素电极PE3、第5像素电极PE5及第7像素电极PE7相邻。第4像素电极PE4与第2像素电极PE2及第3像素电极PE3相邻。第6像素电极PE6与第3像素电极PE3及第5像素电极PE5相邻。第8像素电极PE8与第5像素电极PE5及第7像素电极PE7相邻。第9像素电极PE9与第7像素电极PE7及第2像素电极PE2相邻。

具体而言,第1像素电极PE1及第2像素电极PE2在第1方向上相邻。第1像素电极PE1及第3像素电极PE3在第2方向上相邻。第1像素电极PE1及第5像素电极PE5在第1方向上相邻。第1像素电极PE1及第7像素电极PE7在第2方向上相邻。第4像素电极PE4及第2像素电极PE2在第2方向上相邻。第4像素电极PE4及第3像素电极PE3在第1方向上相邻。第6像素电极PE6及第3像素电极PE3在第1方向上相邻。第6像素电极PE6及第5像素电极PE5在第2方向上相邻。第8像素电极PE8及第5像素电极PE5在第2方向上相邻。第8像素电极PE8及第7像素电极PE7在第1方向上相邻。第9像素电极PE9及第7像素电极PE7在第1方向上相邻。第9像素电极PE9及第2像素电极PE2在第2方向上相邻。

在此,第1方向及第2方向是相互不同的方向。在图示的例子中,第1方向及第2方向是相互正交的方向。在图示的例子中,第1方向是行方向。第2方向是列方向。另外,在图示的例子中,第1方向对应于X轴方向。第2方向对应于Y轴方向。

关于第1像素电极PE1与第2像素电极PE2相邻这样的表现,参照图9B及图9C进行说明。该表现意味着,在平面视中,容纳第1像素电极PE1的最小的长方形RT1所具有的边Sj与容纳第2像素电极PE2的最小的长方形RT2所具有的边Sk相互对置。长方形是包含正方形的概念。具体而言,第1像素电极PE1与第2像素电极PE2相邻意味着,在平面视中,边Sj的法线穿过边Sk,而且,边Sk的法线穿过边Sj。边Sj的法线是穿过边Sj中的任一点的线即可。边Sk的法线是穿过边Sk中的任一点的线即可。在一个具体例中,在平面视中,边Sj的垂直二等分线穿过边Sk的中点,而且,边Sk的垂直二等分线穿过边Sj的中点。关于第1像素电极PE1与第3像素电极PE3相邻等与其他像素电极间的相邻相关的表现及其具体例也是同样的。

在图3、图8、图9A及图9B所示的例子中,在平面视中,容纳第1像素电极PE1的最小的长方形RT1与第1像素电极PE1的轮廓是相同的。关于第2像素电极PE2等其他的像素电极也是同样的。

但是,如图9C所示,在平面视中,第1像素电极PE1的轮廓也可以呈现圆角。在图9C的例子中,容纳第1像素电极PE1的最小的长方形RT1与第1像素电极PE1的轮廓不同。第2像素电极PE2等其他像素电极也可以具有图9C所示的形状。在现实中,在像素电极的大小较小的情况下等,像素电极倾向于在平面视中易于呈现圆角。

在图3、图8及图9A所示的例子中,多个像素通过被配置为矩阵状,从而构成了像素阵列。在像这样构成了像素阵列的情况下,某像素电极与别的像素电极相邻,指的是这些像素电极在行方向或者列方向上相邻,而不是指这些像素在相对于行方向及列方向倾斜的倾斜方向上排列。在图3、图8及图9A所示的例子中,行方向对应于左右方向,列方向对应于上下方向。

返回图9A,从第1像素电极PE1延伸出第1像素过孔PV1。图9A的第1像素过孔PV1对应于图8的点PA处的像素过孔13。从第2像素电极PE2延伸出第2像素过孔PV2。从第3像素电极PE3延伸出第3像素过孔PV3。从第4像素电极PE4延伸出第4像素过孔PV4。从第5像素电极PE5延伸出第5像素过孔PV5。从第6像素电极PE6延伸出第6像素过孔PV6。从第7像素电极PE7延伸出第7像素过孔PV7。从第8像素电极PE8延伸出第8像素过孔PV8。从第9像素电极PE9延伸出第9像素过孔PV9。第1像素过孔PV1至第9像素过孔PV9能够将第1像素电极PE1至第9像素电极PE9与其他要素电连接。其他要素的具体例是布线层、检测电路12等。

在平面视中,第1屏蔽过孔SV1位于第1像素电极PE1与第2像素电极PE2之间。在平面视中,第2屏蔽过孔SV2位于第1像素电极PE1与第3像素电极PE3之间。在平面视中,第4屏蔽过孔SV4位于第1像素电极PE1与第5像素电极PE5之间。在平面视中,第6屏蔽过孔SV6位于第1像素电极PE1与第7像素电极PE7之间。在平面视中,第9屏蔽过孔SV9位于第1像素电极PE1与第2像素电极PE2之间。在平面视中,第10屏蔽过孔SV10位于第1像素电极PE1与第2像素电极PE2之间。在平面视中,第11屏蔽过孔SV11位于第1像素电极PE1与第3像素电极PE3之间。在平面视中,第12屏蔽过孔SV12位于第1像素电极PE1与第5像素电极PE5之间。在平面视中,第13屏蔽过孔SV13位于第1像素电极PE1与第5像素电极PE5之间。在平面视中,第14屏蔽过孔SV14位于第1像素电极PE1与第7像素电极PE7之间。在平面视中像这样在2个像素电极间存在屏蔽过孔,适于得到分辨率高的图像。

在平面视中第1屏蔽过孔SV1位于第1像素电极PE1与第2像素电极PE2之间,意味着在平面视中,第1屏蔽过孔SV1存在于以上述边Sj中的任一点作为一端且以上述边Sk中的任一点作为另一端的线段上。在一个具体例中,在平面视中,屏蔽电极61与第1屏蔽过孔SV1的连接部存在于上述线段上。关于在平面视中第2屏蔽过孔SV2位于第1像素电极PE1与第3像素电极PE3之间等、与其他2个相邻的像素电极间的屏蔽过孔的配置相关的表现及其具体例,也是同样的。通过在平面视中屏蔽过孔位于2个相邻的像素电极间,屏蔽过孔能够遮蔽像素电极间的电力线的至少一部分。

在图示的例子中,在平面视中位于第1像素电极PE1与第2像素电极PE2之间的屏蔽过孔的数量,与在平面视中位于第1像素电极PE1与第3像素电极PE3之间的屏蔽过孔的数量不同。在平面视中位于第1像素电极PE1与第3像素电极PE3之间的屏蔽过孔的数量,与在平面视中位于第1像素电极PE1与第5像素电极PE5之间的屏蔽过孔的数量不同。在平面视中位于第1像素电极PE1与第5像素电极PE5之间的屏蔽过孔的数量,与在平面视中位于第1像素电极PE1与第7像素电极PE7之间的屏蔽过孔的数量不同。在平面视中位于第1像素电极PE1与第7像素电极PE7之间的屏蔽过孔的数量,与在平面视中位于第1像素电极PE1与第2像素电极PE2之间的屏蔽过孔的数量不同。

在图示的例子中,在平面视中位于第1像素电极PE1与第2像素电极PE2之间的屏蔽过孔的数量,与在平面视中位于第1像素电极PE1与第5像素电极PE5之间的屏蔽过孔的数量是相同的。在平面视中位于第1像素电极PE1与第3像素电极PE3之间的屏蔽过孔的数量,与在平面视中位于第1像素电极PE1与第7像素电极PE7之间的屏蔽过孔的数量是相同的。

具体而言,在平面视中位于第1像素电极PE1与第2像素电极PE2之间的屏蔽过孔,是第1屏蔽过孔SV1、第9屏蔽过孔SV9及第10屏蔽过孔SV10这3根。在平面视中位于第1像素电极PE1与第3像素电极PE3之间的屏蔽过孔,是第2屏蔽过孔SV2及第11屏蔽过孔SV11这2根。在平面视中位于第1像素电极PE1与第5像素电极PE5之间的屏蔽过孔,是第4屏蔽过孔SV4、第12屏蔽过孔SV12及第13屏蔽过孔SV13这3根。在平面视中位于第1像素电极PE1与第7像素电极PE7之间的屏蔽过孔,是第6屏蔽过孔SV6及第14屏蔽过孔SV14这2根。

在图示的例子中,在平面视中,第3屏蔽过孔SV3位于第1像素电极PE1及第4像素电极PE4之间。在平面视中,第5屏蔽过孔SV5位于第1像素电极PE1及第6像素电极PE6之间。在平面视中,第7屏蔽过孔SV7位于第1像素电极PE1及第8像素电极PE8之间。在平面视中,第8屏蔽过孔SV8位于第1像素电极PE1及第9像素电极PE9之间。如果像这样,还能够减少在倾斜方向上排列的像素间的串扰。因此,易于得到分辨率更高的图像。此外,在图9A的例子中,在平面视中第1像素电极PE1的轮廓是四边形,倾斜方向是该四边形的对角线延伸的方向。

关于在平面视中第3屏蔽过孔SV3位于第1像素电极PE1及第4像素电极PE4之间这样的表现,参照图9D进行说明。该表现意味着,在平面视中,第3屏蔽过孔SV3位于将连结了容纳第1像素电极PE1的最小的长方形RT1的顶点与容纳第4像素电极PE4的最小的长方形RT4的顶点这2个对置的顶点而成的线段作为对角线的正方形Sx2内。2个对置的顶点以正方形Sx2成为最小的方式被选择。在一个具体例中,在平面视中,屏蔽电极61与第3屏蔽过孔SV3的连接部存在于正方形Sx2内。关于在平面视中第5屏蔽过孔SV5位于第1像素电极PE1及第6像素电极PE6之间等、与其他2个像素电极间的屏蔽过孔的配置相关的表现及其具体例也是同样的。通过在平面视中屏蔽过孔位于2个像素电极间,屏蔽过孔能够遮蔽这2个像素电极间的电力线的至少一部分。

在图示的例子中,在平面视中,第3屏蔽过孔SV3位于第1像素电极PE1、第2像素电极PE2、第3像素电极PE3及第4像素电极PE4之间。在平面视中,第5屏蔽过孔SV5位于第1像素电极PE1、第3像素电极PE3、第5像素电极PE5及第6像素电极PE6之间。在平面视中,第7屏蔽过孔SV7位于第1像素电极PE1、第5像素电极PE5、第7像素电极PE7及第8像素电极PE8之间。在平面视中,第8屏蔽过孔SV8位于第1像素电极PE1、第7像素电极PE7、第2像素电极PE2及第9像素电极PE9之间。在平面视中像这样过孔存在于4个像素电极间,适于得到分辨率高的图像。

关于在平面视中第3屏蔽过孔SV3位于第1像素电极PE1、第2像素电极PE2、第3像素电极PE3及第4像素电极PE4之间这样的表现,参照图9E进行说明。该表现意味着,在平面视中,第3屏蔽过孔SV3位于由容纳第1像素电极PE1的最小的长方形RT1的顶点、容纳第2像素电极PE2的最小的长方形RT2的顶点、容纳第3像素电极PE3的最小的长方形RT3的顶点和容纳第4像素电极PE4的最小的长方形RT4的顶点这4个对置的顶点规定的四边形Sx4内。4个对置的顶点以四边形Sx4成为最小的方式被选择。在一个具体例中,在平面视中,屏蔽电极61与第3屏蔽过孔SV3的连接部存在于四边形Sx4内。关于在平面视中第5屏蔽过孔SV5位于第1像素电极PE1、第3像素电极PE3、第4像素电极PE5及第6像素电极PE6之间等、与其他4个像素电极间的屏蔽过孔的配置相关的表现及其具体例也是同样的。通过在平面视中屏蔽过孔位于4个像素电极间,屏蔽过孔能够遮蔽这4个像素电极间的电力线的至少一部分。

图9E的四边形Sx4能够对应于图9D的正方形Sx2。图9D的正方形Sx2及图9E的四边形Sx4能够对应于图8的第1交叉部Y1。使用图9D进行的上述的说明及使用图9E进行的上述的说明,在像图9C那样在平面视中像素电极呈现圆角的情况下也能够成立。

返回图9A,在平面视中,第1屏蔽过孔SV1位于第1像素过孔PV1与第2像素过孔PV2之间。在平面视中,第3屏蔽过孔SV3位于第1像素过孔PV1与第4像素过孔PV4之间。在平面视中,第4屏蔽过孔SV4位于第1像素过孔PV1与第5像素过孔PV5之间。在平面视中,第5屏蔽过孔SV5位于第1像素过孔PV1与第6像素过孔PV6之间。在平面视中,第7屏蔽过孔SV7位于第1像素过孔PV1与第8像素过孔PV8之间。在平面视中,第8屏蔽过孔SV8位于第1像素过孔PV1与第9像素过孔PV9之间。

在平面视中第1屏蔽过孔SV1位于第1像素过孔PV1与第2像素过孔PV2之间,意味着在平面视中,第1屏蔽过孔SV1存在于以第1像素过孔PV1作为一端且以第2像素过孔PV2作为另一端的线段上。在一个具体例中,在平面视中,屏蔽电极61及第1屏蔽过孔SV1的连接部存在于以第1像素电极PE1及第1像素过孔PV1的连接部作为一端且以第2像素电极PE2及第2像素过孔PV2的连接部作为另一端的线段上。关于在平面视中第3屏蔽过孔SV3位于第1像素过孔PV1与第4像素过孔PV4之间等、与其他像素过孔间的过孔的配置相关的表现及其具体例也是同样的。通过在平面视中在像素过孔间配置屏蔽过孔,屏蔽过孔能够遮蔽像素过孔间的电力线的至少一部分。

虽然在图9A中省略了图示,但在平面视中,绝缘部62与第1像素电极PE1、第2像素电极PE2、第3像素电极PE3、第4像素电极PE4、第5像素电极PE5、第6像素电极PE6、第7像素电极PE7、第8像素电极PE8及第9像素电极PE9相离。

在平面视中,屏蔽电极61在第1像素电极PE1及第2像素电极PE2之间延伸。在平面视中,屏蔽电极61在第1像素电极PE1及第3像素电极PE3之间延伸。在平面视中,屏蔽电极61在第1像素电极PE1及第5像素电极PE5之间延伸。在平面视中,屏蔽电极61在第1像素电极PE1及第7像素电极PE7之间延伸。在平面视中,屏蔽电极61在第4像素电极PE4及第2像素电极PE2之间延伸。在平面视中,屏蔽电极61在第4像素电极PE4及第3像素电极PE3之间延伸。在平面视中,屏蔽电极61在第6像素电极PE6及第3像素电极PE3之间延伸。在平面视中,屏蔽电极61在第6像素电极PE6及第5像素电极PE5之间延伸。在平面视中,屏蔽电极61在第8像素电极PE8及第5像素电极PE5之间延伸。在平面视中,屏蔽电极61在第8像素电极PE8及第7像素电极PE7之间延伸。在平面视中,屏蔽电极61在第9像素电极PE9及第7像素电极PE7之间延伸。在平面视中,屏蔽电极61在第9像素电极PE9及第2像素电极PE2之间延伸。

(相机系统)

以下,关于适用了上述的摄像装置100的相机系统,参照图10进行说明。

在图10的例子中,相机系统604具备摄像装置100、光学系统601、相机信号处理部602和系统控制器603。

光学系统601对光进行聚光。光学系统601例如包含透镜。

相机信号处理部602对由摄像装置100摄像的数据进行信号处理,并作为图像或者数据输出。

系统控制器603对摄像装置100及相机信号处理部602进行控制。

工业实用性

本公开所涉及的摄像装置能够利用于数字照相机、医疗用相机、监视用相机、车载用相机、数字单反相机、数字无反射镜单镜头相机等各种相机系统及传感器系统。

以上,关于本公开的摄像装置基于实施方式进行了说明,但本公开所涉及的摄像装置及其制造方法不限定于上述实施方式。通过组合上述实施方式中的任意的构成要素而实现的其他实施方式、针对上述实施方式在不脱离本公开的主旨的范围内实施了本领域技术人员想到的各种变形而得到的变形例、以及内置了本公开的固体摄像装置的各种设备都包含在本公开中。

附图标记说明:

1 半导体基板

2 绝缘层

2a、2b、2c、2d、2e 构成层

3、3A、3B1、3B2、3B3、3B4、3C1、3C2、3C3、3C4、PE1、PE2、PE3、PE4、PE5、PE6、PE7、PE8、PE9、69 像素电极

4 光电转换层

4p 突出部

5 对置电极

6 缓冲层

7 密封层

8 滤色器

9 平坦化层

10 微透镜

11 光电转换部

12 检测电路

13、PV1、PV2、PV3、PV4、PV5、PV6、PV7、PV8、PV9 像素过孔

63、63C、SV1、SV2、SV3、SV4、SV5、SV6、SV7、SV8、SV9、SV10、SV11、SV12、SV13、SV14屏蔽过孔

14 第1布线层

20 像素

30 像素部

60 区域

61 屏蔽电极

62 绝缘部

62a 上表面

62b 下表面

62c 侧面

62d 角

62x 层

65 信号电荷

67 绝缘体

68 过孔

71 相离幅度

81 掩膜

100 摄像装置

601 光学系统

602 相机信号处理部

603 系统控制器

604 相机系统

S1、S2、S3、S4 边

P1、P2、P3、P4、P5、P6、P7、P8、P9、P10、P11、P12、P13、P14、PA 点

Q、Sx4 四边形

Sx2 正方形

RT1、RT2、RT3、RT4 长方形

Sk、Sj 边

V1、V2、V3、V4 顶点

X1、X2、X3、X4、X5、X6、X7、X8 部分

Y1、Y2、Y3、Y4 交叉部。

- 摄像装置的控制装置、摄像装置、摄像装置的控制方法及摄像装置的控制程序

- 摄像装置、包含摄像装置的内窥镜装置、包含摄像装置的移动体、摄像单元和影像处理单元